Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f458t-i-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                       | Pin Number                  |      |      |             |                        | Buffer               |                                                                                                       |

|-------------------------------------------------------|-----------------------------|------|------|-------------|------------------------|----------------------|-------------------------------------------------------------------------------------------------------|

| Pin Name                                              | PIC18F248/258 PIC18F448/458 |      |      | Pin<br>Type | Туре                   | Description          |                                                                                                       |

|                                                       | SPDIP, SOIC                 | PDIP | TQFP | PLCC        |                        |                      |                                                                                                       |

|                                                       |                             | 10   |      | 01          |                        |                      | PORTD is a bidirectional I/O por<br>These pins have TTL input buffe<br>when external memory is enable |

| RD0/PSP0/C1IN+<br>RD0<br>PSP0<br>C1IN+                | _                           | 19   | 38   | 21          | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 1 input.                                      |

| RD1/PSP1/C1IN-<br>RD1<br>PSP1<br>C1IN-                | _                           | 20   | 39   | 22          | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 1 input.                                      |

| RD2/PSP2/C2IN+<br>RD2<br>PSP2<br>C2IN+                | _                           | 21   | 40   | 23          | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 2 input.                                      |

| RD3/PSP3/C2IN-<br>RD3<br>PSP3<br>C2IN-                | _                           | 22   | 41   | 24          | I/O<br>I/O<br>I        | ST<br>TTL<br>Analog  | Digital I/O.<br>Parallel Slave Port data.<br>Comparator 2 input.                                      |

| RD4/PSP4/ECCP1/<br>P1A<br>RD4<br>PSP4<br>ECCP1<br>P1A | _                           | 27   | 2    | 30          | I/O<br>I/O<br>I/O<br>O | ST<br>TTL<br>ST<br>— | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 capture/compare.<br>ECCP1 PWM output A.            |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B                    | _                           | 28   | 3    | 31          | I/O<br>I/O<br>O        | ST<br>TTL<br>—       | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output B.                                      |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C                    | _                           | 29   | 4    | 32          | I/O<br>I/O<br>O        | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output C.                                      |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D                    | _                           | 30   | 5    | 33          | I/O<br>I/O<br>O        | ST<br>TTL            | Digital I/O.<br>Parallel Slave Port data.<br>ECCP1 PWM output D.                                      |

## TABLE 1-2: PIC18FXX8 PINOUT I/O DESCRIPTIONS (CONTINUED)

OD = Open-Drain (no P diode to VDD)

## 3.7 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired, then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-6 and Figure 3-7 depict time-out sequences on power-up. Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately (Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC18FXX8 device operating in parallel.

Table 3-2 shows the Reset conditions for some Special Function Registers, while Table 3-3 shows the Reset conditions for all registers.

#### TABLE 3-1: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator                         | Power-up                 | (2)               | 5 (2)                    | Wake-up from                  |

|------------------------------------|--------------------------|-------------------|--------------------------|-------------------------------|

| Configuration                      | <b>PWRTEN</b> = 0        | <b>PWRTEN</b> = 1 | Brown-out <sup>(2)</sup> | Sleep or<br>Oscillator Switch |

| HS with PLL enabled <sup>(1)</sup> | 72 ms + 1024 Tosc + 2 ms | 1024 Tosc + 2 ms  | 72 ms + 1024 Tosc + 2 ms | 1024 Tosc + 2 ms              |

| HS, XT, LP                         | 72 ms + 1024 Tosc        | 1024 Tosc         | 72 ms + 1024 Tosc        | 1024 Tosc                     |

| EC                                 | 72 ms                    | —                 | 72 ms                    | —                             |

| External RC                        | 72 ms                    |                   | 72 ms                    | _                             |

**Note 1:** 2 ms = Nominal time required for the 4x PLL to lock.

**2:** 72 ms is the nominal Power-up Timer delay.

#### REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

| R/W-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| IPEN  | —   | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |     |     |       |       |       |       | bit 0 |

# TABLE 3-2:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                     | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | BOR | STKFUL | STKUNF |

|-----------------------------------------------|-----------------------|------------------|----|----|----|-----|-----|--------|--------|

| Power-on Reset                                | 0000h                 | 01 110q          | 1  | 1  | 1  | 0   | 0   | u      | u      |

| MCLR Reset during normal operation            | 0000h                 | 00 011q          | u  | u  | u  | u   | u   | u      | u      |

| Software Reset during normal operation        | 0000h                 | 00 011q          | 0  | u  | u  | u   | u   | u      | u      |

| Stack Full Reset during normal operation      | 0000h                 | 00 011q          | u  | u  | u  | 1   | 1   | u      | 1      |

| Stack Underflow Reset during normal operation | 0000h                 | 00 011q          | u  | u  | u  | 1   | 1   | 1      | u      |

| MCLR Reset during Sleep                       | 0000h                 | 00 011q          | u  | 1  | 0  | u   | u   | u      | u      |

| WDT Reset                                     | 0000h                 | 00 011q          | u  | 0  | 1  | u   | u   | u      | u      |

| WDT Wake-up                                   | PC + 2                | 01 101q          | u  | 0  | 0  | u   | u   | u      | u      |

| Brown-out Reset                               | 0000h                 | 01 110q          | 1  | 1  | 1  | u   | 0   | u      | u      |

| Interrupt wake-up from Sleep                  | PC + 2 <sup>(1)</sup> | 01 101q          | u  | 1  | 0  | u   | u   | u      | u      |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (000008h or 000018h).

# 4.10 Access Bank

The Access Bank is an architectural enhancement that is very useful for C compiler code optimization. The techniques used by the C compiler are also useful for programs written in assembly.

This data memory region can be used for:

- · Intermediate computational values

- · Local variables of subroutines

- · Faster context saving/switching of variables

- · Common variables

- Faster evaluation/control of SFRs (no banking)

The Access Bank is comprised of the upper 160 bytes in Bank 15 (SFRs) and the lower 96 bytes in Bank 0. These two sections will be referred to as Access Bank High and Access Bank Low, respectively. Figure 4-6 indicates the Access Bank areas.

A bit in the instruction word specifies if the operation is to occur in the bank specified by the BSR register or in the Access Bank.

When forced in the Access Bank (a = 0), the last address in Access Bank Low is followed by the first address in Access Bank High. Access Bank High maps most of the Special Function Registers so that these registers can be accessed without any software overhead.

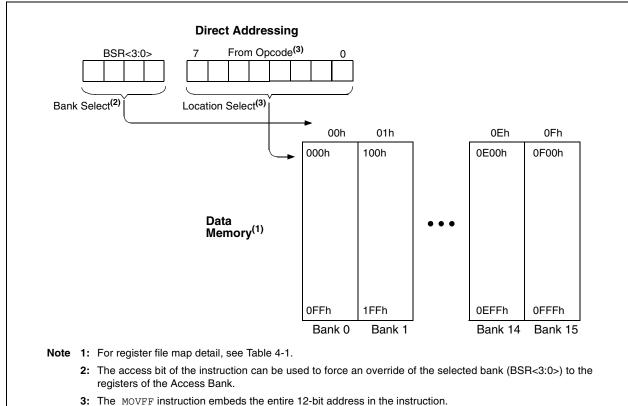

# 4.11 Bank Select Register (BSR)

The need for a large general purpose memory space dictates a RAM banking scheme. The data memory is partitioned into sixteen banks. When using direct addressing, the BSR should be configured for the desired bank.

BSR<3:0> holds the upper 4 bits of the 12-bit RAM address. The BSR<7:4> bits will always read '0's and writes will have no effect.

A MOVLB instruction has been provided in the instruction set to assist in selecting banks.

If the currently selected bank is not implemented, any read will return all '0's and all writes are ignored. The Status register bits will be set/cleared as appropriate for the instruction performed.

Each Bank extends up to FFh (256 bytes). All data memory is implemented as static RAM.

A MOVFF instruction ignores the BSR since the 12-bit addresses are embedded into the instruction word.

Section 4.12 "Indirect Addressing, INDF and FSR Registers" provides a description of indirect addressing, which allows linear addressing of the entire RAM space.

#### \_\_\_\_\_

FIGURE 4-7: DIRECT ADDRESSING

| TER 5-1: | EECON1:         | EEPROM                       | CONTROL                     | . REGISTE      | R 1                                    |              |               |              |

|----------|-----------------|------------------------------|-----------------------------|----------------|----------------------------------------|--------------|---------------|--------------|

|          | R/W-x           | R/W-x                        | U-0                         | R/W-0          | R/W-x                                  | R/W-0        | R/S-0         | R/S-0        |

|          | EEPGD           | CFGS                         | —                           | FREE           | WRERR                                  | WREN         | WR            | RD           |

|          | bit 7           |                              |                             |                |                                        |              |               | bit 0        |

| bit 7    |                 | -                            |                             |                | mory Select                            | bit          |               |              |

|          |                 |                              | ash memory<br>OM memory     |                |                                        |              |               |              |

| bit 6    | CFGS: Fla:      | sh Program/                  | Data EE or                  | Configuratio   | on Select bit                          |              |               |              |

|          |                 | •                            | on registers<br>ash or data |                | nemory                                 |              |               |              |

| bit 5    | Unimplem        | ented: Read                  | <b>d as</b> '0'             |                |                                        |              |               |              |

| bit 4    | FREE: Flas      | sh Row Eras                  | e Enable bi                 | t              |                                        |              |               |              |

|          | (reset b        | y hardware                   | •                           | v addressed    | by TBLPTR                              | on the next  | WR comm       | and          |

| bit 3    | 0 = Perforn     | Vrite Error F                | log bit                     |                |                                        |              |               |              |

| DIL 3    |                 |                              | prematurel                  | v torminator   | 4                                      |              |               |              |

|          | (any M          |                              | WDT Reset                   |                | timed progra                           | mming in no  | ormal operat  | tion)        |

|          | Note:           | When a W                     | •                           |                | GD or FRE                              | E bits are n | ot cleared.   | This allows  |

| bit 2    | WREN: Wr        | ite Enable b                 | it                          |                |                                        |              |               |              |

|          |                 | write cycles<br>write to the | EEPROM o                    | or Flash mer   | nory                                   |              |               |              |

| bit 1    | WR: Write       | Control bit                  |                             |                |                                        |              |               |              |

|          | <u>(Th</u> e op | peration is s                |                             | d the bit is c | or a program<br>leared by ha<br>ware.) |              |               |              |

|          | $0 = Write c_1$ | ycle is comp                 | lete                        |                |                                        |              |               |              |

| bit 0    | RD: Read        |                              |                             |                |                                        |              |               |              |

|          | (Read t         |                              |                             |                | rdware. The<br>PGD = 1.)               | RD bit can o | nly be set (r | not cleared) |

|          | 0 = Does n      | ot initiate ar               | EEPROM                      | read           |                                        |              |               |              |

|          | Logond          |                              |                             |                |                                        |              |               | ]            |

|          | Legend:         |                              |                             |                | Hable bit                              |              |               |              |

| Legend:           |                  |                      |                                    |

|-------------------|------------------|----------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | S = Settable bit     | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |

# REGISTER 5-1: EECON1: EEPROM CONTROL REGISTER 1

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY

| EXAMPLE 6-3:  | WRI            | TING TO FLASH PROG             |                                                          |

|---------------|----------------|--------------------------------|----------------------------------------------------------|

|               | MOVLW          | D'64                           | ; number of bytes in erase block                         |

|               | MOVWF          | COUNTER                        |                                                          |

|               | MOVLW          | high (BUFFER_ADDR)             | ; point to buffer                                        |

|               | MOVWF          | FSROH                          |                                                          |

|               | MOVLW          | low (BUFFER_ADDR)              |                                                          |

|               | MOVWF          | FSROL                          |                                                          |

|               | MOVLW          | upper (CODE_ADDR)              | ; Load TBLPTR with the base                              |

|               | MOVWF<br>MOVLW | TBLPTRU                        | ; address of the memory block                            |

|               | MOVUW<br>MOVWF | high (CODE_ADDR)<br>TBLPTRH    |                                                          |

|               | MOVLW          | low (CODE ADDR)                |                                                          |

|               | MOVWF          | TBLPTRL                        |                                                          |

| READ BLOCK    |                |                                |                                                          |

| —             | TBLRD*+        |                                | ; read into TABLAT, and inc                              |

|               | MOVF           | TABLAT, W                      | ; get data                                               |

|               | MOVWF          | POSTINCO                       | ; store data                                             |

|               | DECFSZ         | COUNTER                        | ; done?                                                  |

|               | BRA            | READ_BLOCK                     | ; repeat                                                 |

| MODIFY_WORD   |                |                                |                                                          |

|               | MOVLW          | DATA_ADDR_HIGH                 | ; point to buffer                                        |

|               | MOVWF          | FSROH                          |                                                          |

|               | MOVLW          | DATA_ADDR_LOW                  |                                                          |

|               | MOVWF<br>MOVLW | FSROL<br>NEW DATA LOW          | ; update buffer word                                     |

|               | MOVUW<br>MOVWF | NEW_DATA_LOW<br>POSTINC0       | ; update buller word                                     |

|               | MOVLW          | NEW DATA HIGH                  |                                                          |

|               | MOVWF          | INDF0                          |                                                          |

| ERASE BLOCK   |                |                                |                                                          |

| _             | MOVLW          | upper (CODE ADDR)              | ; load TBLPTR with the base                              |

|               | MOVWF          | TBLPTRU                        | ; address of the memory block                            |

|               | MOVLW          | high (CODE_ADDR)               |                                                          |

|               | MOVWF          | TBLPTRH                        |                                                          |

|               | MOVLW          | low (CODE_ADDR)                |                                                          |

|               | MOVWF          | TBLPTRL                        |                                                          |

|               | BSF            | EECON1, EEPGD                  | ; point to FLASH program memory                          |

|               | BCF            | EECON1, CFGS                   | ; access FLASH program memory                            |

|               | BSF<br>BSF     | EECON1, WREN<br>EECON1, FREE   | ; enable write to memory<br>; enable Row Erase operation |

|               | BCF            | INTCON, GIE                    | ; disable interrupts                                     |

|               | MOVLW          | 55h                            | , disable incertapes                                     |

| Required      | MOVWF          | EECON2                         | ; write 55H                                              |

| Sequence      | MOVLW          | 0AAh                           | ,                                                        |

| -             | MOVWF          | EECON2                         | ; write AAH                                              |

|               | BSF            | EECON1, WR                     | ; start erase (CPU stall)                                |

|               | NOP            |                                |                                                          |

|               | BSF            | INTCON, GIE                    | ; re-enable interrupts                                   |

|               | TBLRD*-        |                                | ; dummy read decrement                                   |

| WRITE_BUFFER_ |                |                                |                                                          |

|               | MOVLW          | 8                              | ; number of write buffer groups of 8 bytes               |

|               | MOVWF          | COUNTER_HI                     |                                                          |

|               | MOVLW          | high (BUFFER_ADDR)             | ; point to buffer                                        |

|               | MOVWF<br>MOVLW | FSR0H<br>low (BUFFER ADDR)     |                                                          |

|               | MOVLW          | FSROL                          |                                                          |

| PROGRAM LOOP  | 110 4 111      |                                |                                                          |

|               | MOVLW          | 8                              | ; number of bytes in holding register                    |

|               | MOVWF          | COUNTER                        |                                                          |

| WRITE_WORD_TO | HREGS          |                                |                                                          |

|               | MOVFW          | POSTINCO, W                    | ; get low byte of buffer data                            |

|               | MOVWF          | TABLAT                         | ; present data to table latch                            |

|               | TBLWT+*        |                                | ; write data, perform a short write                      |

|               |                |                                | ; to internal TBLWT holding register.                    |

|               |                |                                |                                                          |

|               | DECFSZ<br>BRA  | COUNTER<br>WRITE WORD TO HREGS | ; loop until buffers are full                            |

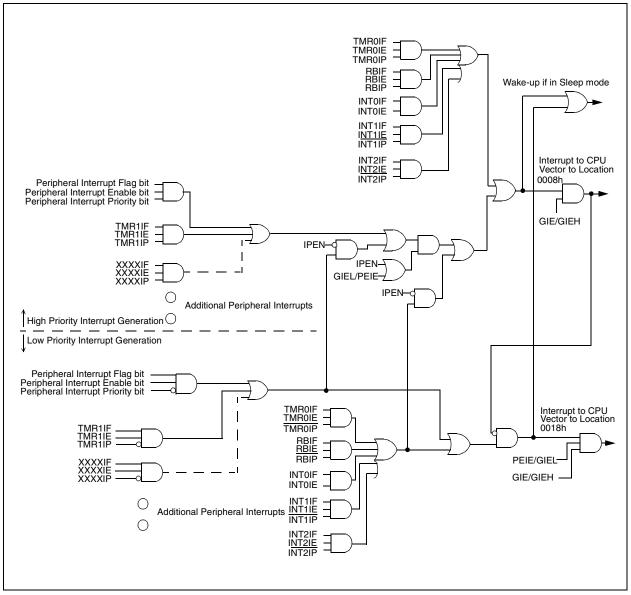

## 8.1 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits. Because of the number of interrupts to be controlled, PIC18FXX8 devices have three INTCON registers. They are detailed in Register 8-1 through Register 8-3.

# Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0      | R/W-0                                                             | R/W-0         | R/W-0        | R/W-0         | R/W-0        | R/W-0        | R/W-x        |

|------------|-------------------------------------------------------------------|---------------|--------------|---------------|--------------|--------------|--------------|

| GIE/GIEF   | PEIE/GIEL                                                         | TMR0IE        | INT0IE       | RBIE          | TMR0IF       | INTOIF       | RBIF         |

| bit 7      | ·                                                                 |               |              |               |              |              | bit 0        |

|            | : Global Interr                                                   | -             | oit          |               |              |              |              |

| 1 = Enable | <u>N (RCON&lt;7&gt;)</u><br>es all unmaske<br>es all interrupt    | ed interrupts | i            |               |              |              |              |

| 1 = Enabl  | <u>N (RCON&lt;7&gt;)</u><br>es all high prio<br>es all priority i | rity interrup | ts           |               |              |              |              |

| PEIE/GIE   | -: Peripheral I                                                   | nterrupt Ena  | able bit     |               |              |              |              |

| 1 = Enable | <u>N (RCON&lt;7&gt;)</u><br>es all unmaske<br>es all peripher     | ed periphera  |              |               |              |              |              |

| 1 = Enable | <u>N (RCON&lt;7&gt;)</u><br>es all low prior<br>es all low prior  | ity periphera |              |               |              |              |              |

| TMR0IE:    | TMR0 Overflov                                                     | w Interrupt E | Enable bit   |               |              |              |              |

|            | es the TMR0 c<br>es the TMR0 o                                    |               | •            |               |              |              |              |

| INTOIE: IN | IT0 External Ir                                                   | nterrupt Ena  | ble bit      |               |              |              |              |

|            | es the INT0 ex<br>es the INT0 ex                                  |               | •            |               |              |              |              |

| RBIE: RB   | Port Change                                                       | Interrupt En  | able bit     |               |              |              |              |

|            | es the RB port<br>es the RB por                                   |               |              |               |              |              |              |

| TMR0IF:    | MR0 Overflov                                                      | v Interrupt F | lag bit      |               |              |              |              |

|            | register has o<br>register did no                                 |               | must be clea | ared in softv | vare)        |              |              |

| INTOIF: IN | IT0 External Ir                                                   | nterrupt Flag | ı bit        |               |              |              |              |

|            | IT0 external in<br>IT0 external in                                |               |              | be cleared i  | n software b | by reading P | ORTB)        |

| RBIF: RB   | Port Change I                                                     | nterrupt Fla  | g bit        |               |              |              |              |

|            | st one of the R<br>of the RB7:RB                                  |               |              |               | be cleared i | n software)  |              |

| Note:      | A mismatch mismatch co                                            |               |              |               |              | g PORTB v    | will end the |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

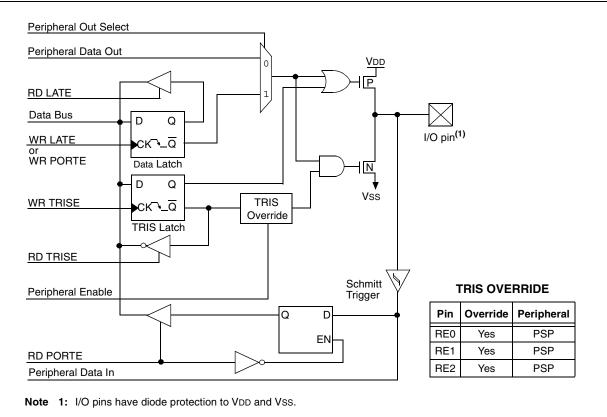

## 9.5 PORTE, TRISE and LATE Registers

| Note: | This | port  | is  | only | available | on | the |

|-------|------|-------|-----|------|-----------|----|-----|

|       | PIC1 | 8F448 | and | PIC1 | 8F458.    |    |     |

PORTE is a 3-bit wide, bidirectional port. PORTE has three pins (RE0/AN5/RD, RE1/AN6/WR/C10UT and RE2/AN7/CS/C20UT) which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

Read-modify-write operations on the LATE register, read and write the latched output value for PORTE.

The corresponding Data Direction register for the port is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

The TRISE register also controls the operation of the Parallel Slave Port through the control bits in the upper half of the register. These are shown in Register 9-1.

When the Parallel Slave Port is active, the PORTE pins function as its control inputs. For additional details, refer to **Section 10.0 "Parallel Slave Port**".

PORTE pins are also multiplexed with inputs for the A/D converter and outputs for the analog comparators. When selected as an analog input, these pins will read as '0's. Direction bits TRISE<2:0> control the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

| EXAMP | LE 9-5: | INITIALIZING PORTE      |

|-------|---------|-------------------------|

| CLRF  | PORTE   | ; Initialize PORTE by   |

|       |         | ; clearing output       |

|       |         | ; data latches          |

| CLRF  | LATE    | ; Alternate method      |

|       |         | ; to clear output       |

|       |         | ; data latches          |

| MOVLW | 03h     | ; Value used to         |

|       |         | ; initialize data       |

|       |         | ; direction             |

| MOVWF | TRISE   | ; Set RE1:RE0 as inputs |

|       |         | ; RE2 as an output      |

|       |         | ; (RE4=0 - PSPMODE Off) |

# FIGURE 9-10: PORTE BLOCK DIAGRAM

# 13.0 TIMER2 MODULE

The Timer2 module timer has the following features:

- 8-bit timer (TMR2 register)

- 8-bit period register (PR2)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR2 match of PR2

SSP module optional use of TMR2 output to generate clock shift

Register 13-1 shows the Timer2 Control register. Timer2 can be shut-off by clearing control bit TMR2ON (T2CON register) to minimize power consumption. Figure 13-1 is a simplified block diagram of the Timer2 module. The prescaler and postscaler selection of Timer2 are controlled by this register.

#### 13.1 **Timer2 Operation**

Timer2 can be used as the PWM time base for the PWM mode of the CCP module. The TMR2 register is readable and writable and is cleared on any device Reset. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits T2CKPS1:T2CKPS0 (T2CON register). The match output of TMR2 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR2 interrupt (latched in flag bit TMR2IF, PIR registers).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · A write to the TMR2 register

- · A write to the T2CON register

- Any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

Timer2 is disabled on POR. Note:

#### REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

|   | U-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0   | R/W-0   |

|---|-------|---------|---------|---------|---------|--------|---------|---------|

| ſ | —     | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

|   | bit 7 |         |         |         |         |        |         | bit 0   |

#### bit

| bit 7   | Unimplemented: Read as '0'                           |

|---------|------------------------------------------------------|

| bit 6-3 | TOUTPS3:TOUTPS0: Timer2 Output Postscale Select bits |

|         | 0000 = 1:1 Postscale                                 |

|         | 0001 = 1:2 Postscale                                 |

|         |                                                      |

|         | •                                                    |

|         | 1111 = 1:16 Postscale                                |

| bit 2   | TMR2ON: Timer2 On bit                                |

|         | 1 = Timer2 is on                                     |

|         | 0 = Timer2 is off                                    |

| bit 1-0 | T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits   |

|         | 00 = Prescaler is 1                                  |

|         | 01 = Prescaler is 4                                  |

|         | 1x = Prescaler is 16                                 |

|         |                                                      |

|         | Legend:                                              |

|         |                                                      |

| Legena:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 15.1 CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

Table 15-1 shows the timer resources of the CCP module modes.

#### TABLE 15-1: CCP1 MODE – TIMER RESOURCE

| CCP1 Mode | Timer Resource   |

|-----------|------------------|

| Capture   | Timer1 or Timer3 |

| Compare   | Timer1 or Timer3 |

| PWM       | Timer2           |

#### 15.2 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16bit value of the TMR1 or TMR3 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR registers), is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 15.2.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

#### 15.2.2 TIMER1/TIMER3 MODE SELECTION

The timers used with the capture feature (either Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer used with each CCP module is selected in the T3CON register.

| CCP1<br>Mode | ECCP1<br>Mode | Interaction                                                                                                                             |  |

|--------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| Capture      | Capture       | TMR1 or TMR3 time base. Time base can be different for each CCP.                                                                        |  |

| Capture      | Compare       | The compare could be configured for the special event trigger which clears either TMR1 or TMR3, depending upon which time base is used. |  |

| Compare      | Compare       | The compare(s) could be configured for the special event trigger which clears TMR1 or TMR3, depending upon which time base is used.     |  |

| PWM          | PWM           | The PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                 |  |

| PWM          | Capture       | None.                                                                                                                                   |  |

| PWM          | Compare       | None.                                                                                                                                   |  |

#### TABLE 15-2: INTERACTION OF CCP1 AND ECCP1 MODULES

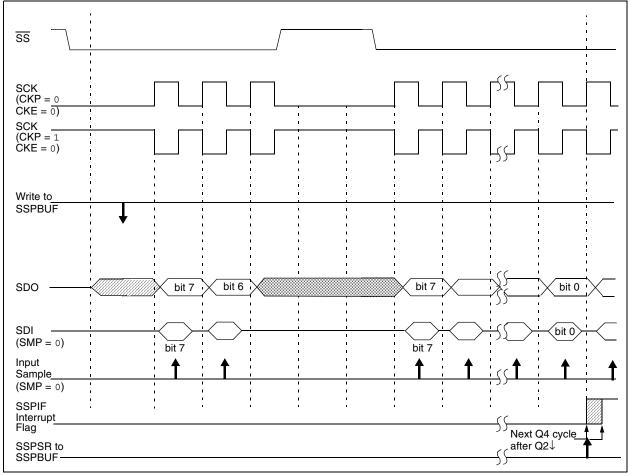

#### 17.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep. Before enabling the module in SPI Slave mode, the clock line must match the proper Idle state. The clock line can be observed by reading the SCK pin. The Idle state is determined by the CKP bit (SSPCON1<4>).

#### 17.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch

must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven, even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When the SPI is in Slave mode with $\overline{SS}$ pin      |

|---------|-------------------------------------------------------------|

|         | control enabled (SSPCON1<3:0> = 0100),                      |

|         | the SPI module will reset if the $\overline{SS}$ pin is set |

|         | to VDD.                                                     |

2: If the SPI is used in Slave mode with CKE set, then the SS pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

### 17.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit BF and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the ninth bit time, if an address match occurred, or if data was received properly. The status of  $\overline{ACK}$  is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 17-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF bit is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 17.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 17.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

## 17.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call) or when the slave has properly received its data.

# 17.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

| Note: | The RCEN bit should be set after the $\overline{ACK}$ |

|-------|-------------------------------------------------------|

|       | sequence is complete or the RCEN bit will             |

|       | be disregarded.                                       |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 17.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 17.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 17.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

| TBL         | RD                                                                           | Table Read                                                                                                                                                           |                                                                                                              |                                                                                                         |                                                                                                     |                                                                                                                                               |                      |

|-------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Synta       | ax:                                                                          | [ label ]                                                                                                                                                            | TBL                                                                                                          | .RD ( *                                                                                                 | ; *+; *                                                                                             | -; +*)                                                                                                                                        |                      |

| Oper        | ands:                                                                        | None                                                                                                                                                                 |                                                                                                              |                                                                                                         |                                                                                                     |                                                                                                                                               |                      |

| Oper        | ation:                                                                       | if TBLRD *,<br>(Prog Mem<br>TBLPTR - N<br>if TBLRD *+<br>(Prog Mem<br>(TBLPTR) +<br>if TBLRD *-,<br>(Prog Mem<br>(TBLPTR) -<br>if TBLRD +<br>(TBLPTR) +<br>(Prog Mem | No C<br>(TBI<br>1 −<br>(TBI<br>1 −                                                                           | Change<br>_PTR)<br>→ TBLI<br>_PTR)<br>→ TBLI<br>→ TBLI                                                  | ) → T,<br>PTR;<br>) → T,<br>PTR;<br>PTR;                                                            | ABLA<br>ABLA                                                                                                                                  | Т;<br>Т;             |

| Statu       | s Affected:                                                                  | None                                                                                                                                                                 |                                                                                                              |                                                                                                         |                                                                                                     |                                                                                                                                               |                      |

| Enco        | oding:                                                                       |                                                                                                                                                                      |                                                                                                              | nn=0 *<br>=1 *+<br>=2 *-                                                                                |                                                                                                     |                                                                                                                                               |                      |

| Desc        | ription:                                                                     | of Program Me<br>Pointer (TBL<br>The TBLPTF<br>byte in the p<br>2-Mbyte add<br>TBLPT<br>TBLPT                                                                        | Merr<br>morr<br>PTF<br>R (a 2<br>rogr<br>Iress<br>R[0]<br>R[0]<br>R[0]<br>instr<br>as fc<br>e<br>emer<br>eme | nory (F<br>y, a por<br>R) is us<br>21-bit<br>am me<br>s range<br>= 0:<br>= 1:<br>uction<br>blows:<br>nt | 2.M.).<br>iinter o<br>sed.<br>pointe<br>emory<br>e.<br>Leas<br>Byte<br>Mem<br>Mosi<br>of Pr<br>Word | inter) points to each<br>ory. TBLPTR has a<br>east Significant<br>tyte of Program<br>femory Word<br>fost Significant Byte<br>f Program Memory |                      |

| Words:      |                                                                              | 1                                                                                                                                                                    |                                                                                                              |                                                                                                         |                                                                                                     |                                                                                                                                               |                      |

| Cycle       | es:                                                                          | 2                                                                                                                                                                    |                                                                                                              |                                                                                                         |                                                                                                     |                                                                                                                                               |                      |

|             | ycle Activity                                                                | <i>'</i> :                                                                                                                                                           |                                                                                                              |                                                                                                         |                                                                                                     |                                                                                                                                               |                      |

|             | Q1                                                                           | Q2                                                                                                                                                                   |                                                                                                              | Q                                                                                                       | 3                                                                                                   |                                                                                                                                               | Q4                   |

|             | Decode                                                                       | No                                                                                                                                                                   |                                                                                                              | N                                                                                                       |                                                                                                     |                                                                                                                                               | No                   |

|             | No                                                                           | operation<br>No operatio                                                                                                                                             | n                                                                                                            | opera<br>No                                                                                             |                                                                                                     |                                                                                                                                               | eration<br>operation |

|             | operation                                                                    | (Read Progra<br>Memory)                                                                                                                                              |                                                                                                              | opera                                                                                                   |                                                                                                     | (                                                                                                                                             | Write<br>ABLAT)      |

| <u>Exar</u> | nple 1:                                                                      | TBLRD                                                                                                                                                                | *+                                                                                                           | ;                                                                                                       |                                                                                                     |                                                                                                                                               |                      |

|             | Before Insti<br>TABL/<br>TBLP<br>MEMO<br>After Instruc<br>TABL/<br>TBLP      | AT<br>FR<br>DRY(0x00A3<br>Ction<br>AT                                                                                                                                | 56)                                                                                                          | =<br>=<br>=                                                                                             | 0x34                                                                                                | )A356<br>1                                                                                                                                    |                      |

| Exan        | nple 2:                                                                      | TBLRD                                                                                                                                                                | +*                                                                                                           | ;                                                                                                       |                                                                                                     |                                                                                                                                               |                      |

|             | Before Instr<br>TABL/<br>TBLP <sup>-</sup><br>MEMC<br>MEMC<br>After Instruct | AT<br>FR<br>DRY(0x01A39<br>DRY(0x01A39<br>ction<br>AT                                                                                                                |                                                                                                              | =<br>=<br>=                                                                                             | 0x12<br>0x34<br>0x34                                                                                | 1 A357<br>2<br>1                                                                                                                              |                      |

|             | TBLP                                                                         | IK                                                                                                                                                                   |                                                                                                              | =                                                                                                       | 0x01                                                                                                | IA358                                                                                                                                         | 3                    |

© 2006 Microchip Technology Inc.

| TBLWT            | Table Write                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] TBLWT ( *; *+; *-; +*)                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |  |

| Operands:        | None                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |  |

| Operation:       | if TBLWT*,<br>(TABLAT) $\rightarrow$ Holding Register;<br>TBLPTR – No Change;<br>if TBLWT*+,<br>(TABLAT) $\rightarrow$ Holding Register;<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>if TBLWT*-,<br>(TABLAT) $\rightarrow$ Holding Register;<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR;<br>if TBLWT+*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;<br>(TABLAT) $\rightarrow$ Holding Register; |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |  |

| Encoding:        | 0000                                                                                                                                                                                                                                                                                                                                                                             | 0000                                                                                                                                                                                                  | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +* |  |

| Description:     | determine wh<br>TABLAT is wr<br>used to progr<br>Memory (P.M<br><b>Program Me</b><br>The TBLPTR<br>byte in the pro<br>2-Mbyte addr<br>TBLPTR sele<br>memory locat<br>TBLPTF                                                                                                                                                                                                      | hich of the a<br>itten to. The<br>am the con-<br>am the con-<br>mory" for<br>(a 21-bit p<br>ogram meness range,<br>bots which f<br>tion to acco<br>R[0] = 0:<br>R[0] = 1:<br>nstruction<br>s follows: | <ul> <li>the 3 LSBs of TBLPTR to<br/>he 8 holding registers the<br/>. The holding registers are<br/>contents of Program<br/>er to Section 6.0 "Flash<br/>for additional details.)<br/>bit pointer) points to each<br/>memory. TBLPTR has a<br/>nge. The LSb of the<br/>ch byte of the program<br/>access.</li> <li>Least Significant Byte<br/>of Program Memory<br/>Word</li> <li>Most Significant Byte<br/>of Program Memory<br/>Word</li> </ul> |                                           |  |

- post-increment

post-decrement

pre-increment

#### TBLWT Table Write (Continued)

| W | 0 | d | s: | 1 |

|---|---|---|----|---|

Cycles: 2

Q Cycle Activity:

| Q1 0 |

|------|

|------|

| Decode          | No<br>operation                  | No<br>operation | No<br>operation                                |

|-----------------|----------------------------------|-----------------|------------------------------------------------|

| No<br>operation | No operation<br>(Read<br>TABLAT) |                 | No operation<br>(Write to Holding<br>Register) |

Q3

Q4

Example 1: TBLWT \*+;

| Before Instruction                                                                                                                                                    |                           |                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------|

| TABLAT                                                                                                                                                                | =                         | 0x55                                                   |

| TBLPTR                                                                                                                                                                | =                         | 0x00A356                                               |

| HOLDING REGISTER                                                                                                                                                      |                           |                                                        |

| (0x00A356)                                                                                                                                                            | =                         | 0xFF                                                   |

| After Instructions (table write                                                                                                                                       | com                       | oletion)                                               |

| TABLAT                                                                                                                                                                | = .                       | 0x55                                                   |

| TBLPTR                                                                                                                                                                | =                         | 0x00A357                                               |

| HOLDING REGISTER                                                                                                                                                      |                           |                                                        |

| (0x00A356)                                                                                                                                                            | =                         | 0x55                                                   |

| Example 2: TBLWT +                                                                                                                                                    | *;                        |                                                        |

| Before Instruction                                                                                                                                                    |                           |                                                        |

|                                                                                                                                                                       |                           |                                                        |

|                                                                                                                                                                       |                           | 004                                                    |

|                                                                                                                                                                       | =                         | 0x34                                                   |

| TBLPTR                                                                                                                                                                | =<br>=                    | 0x34<br>0x01389A                                       |

| TBLPTR<br>HOLDING REGISTER                                                                                                                                            | =                         | 0x01389A                                               |

| TBLPTR<br>HOLDING REGISTER<br>(0x01389A)                                                                                                                              |                           | ••••                                                   |

| TBLPTR<br>HOLDING REGISTER                                                                                                                                            | =                         | 0x01389A                                               |

| TBLPTR<br>HOLDING REGISTER<br>(0x01389A)<br>HOLDING REGISTER<br>(0x01389B)                                                                                            | =<br>=<br>=               | 0x01389A<br>0xFF<br>0xFF                               |

| TBLPTR<br>HOLDING REGISTER<br>(0x01389A)<br>HOLDING REGISTER<br>(0x01389B)<br>After Instruction (table write o                                                        | =<br>=<br>=<br>compl      | 0x01389A<br>0xFF<br>0xFF<br>etion)                     |