Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 5x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf248t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

#### 6.1 **Table Reads and Table Writes**

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 6-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in Section 6.5 "Writing to Flash Program Memory". Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

# Instruction: TBLRD\* Program Memory Table Pointer<sup>(1)</sup> Table Latch (8-bit) TBLPTRH TBLPTRU TBLPTRL TABLAT Program Memory (TBLPTR) Note 1: Table Pointer points to a byte in program memory.

#### FIGURE 6-1: **TABLE READ OPERATION**

| <b>REGISTER 8-5:</b> | PIR2: PE                                                                                                                                                          | RIPHERAL                                      | INTERRU         | JPT REQU           | EST (FLA     | G) REGIS     | TER 2      |                        |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------|--------------------|--------------|--------------|------------|------------------------|

|                      | U-0                                                                                                                                                               | R/W-0                                         | U-0             | R/W-0              | R/W-0        | R/W-0        | R/W-0      | R/W-0                  |

|                      |                                                                                                                                                                   | CMIF <sup>(1)</sup>                           | —               | EEIF               | BCLIF        | LVDIF        | TMR3IF     | ECCP1IF <sup>(1)</sup> |

|                      | bit 7                                                                                                                                                             |                                               |                 |                    |              |              |            | bit 0                  |

|                      |                                                                                                                                                                   |                                               |                 |                    |              |              |            |                        |

| bit 7                |                                                                                                                                                                   | nented: Rea                                   |                 | (1)                |              |              |            |                        |

| bit 6                |                                                                                                                                                                   | mparator Inte                                 |                 |                    |              |              |            |                        |

|                      |                                                                                                                                                                   | arator input l<br>arator input l              |                 |                    |              |              |            |                        |

| bit 5                | Unimplen                                                                                                                                                          | nented: Rea                                   | <b>d as</b> '0' |                    |              |              |            |                        |

| bit 4                | EEIF: EEF                                                                                                                                                         | PROM Write                                    | Operation       | Interrupt Fla      | g bit        |              |            |                        |

|                      |                                                                                                                                                                   | operation is operation is                     |                 |                    | red in softw | are)         |            |                        |

| bit 3                | BCLIF: B                                                                                                                                                          | us Collision I                                | nterrupt Fla    | ag bit             |              |              |            |                        |

|                      |                                                                                                                                                                   | collision occ<br>s collision oc               | •               | t be cleared       | in software  | )            |            |                        |

| bit 2                | LVDIF: Lo                                                                                                                                                         | w-Voltage D                                   | etect Interr    | upt Flag bit       |              |              |            |                        |

|                      | <ul> <li>1 = A low-voltage condition occurred (must be cleared in software)</li> <li>0 = The device voltage is above the Low-Voltage Detect trip point</li> </ul> |                                               |                 |                    |              |              |            |                        |

| bit 1                | TMR3IF:                                                                                                                                                           | TMR3 Overfl                                   | ow Interrup     | t Flag bit         |              |              |            |                        |

|                      | <ul> <li>1 = TMR3 register overflowed (must be cleared in software)</li> <li>0 = TMR3 register did not overflow</li> </ul>                                        |                                               |                 |                    |              |              |            |                        |

| bit 0                | ECCP1IF:                                                                                                                                                          | ECCP1 Inte                                    | errupt Flag     | bit <sup>(1)</sup> |              |              |            |                        |

|                      | <u>Capture mode:</u><br>1 = A TMR1 (TMR3) register capture occurred (must be cleared in software)<br>0 = No TMR1 (TMR3) register capture occurred                 |                                               |                 |                    |              |              |            |                        |

|                      |                                                                                                                                                                   | <u>mode:</u><br>R1 register c<br>/R1 register |                 |                    |              | leared in sc | oftware)   |                        |

|                      | <u>PWM moo</u><br>Unused in                                                                                                                                       | <u>de:</u><br>ı this mode.                    |                 |                    |              |              |            |                        |

|                      | Note 1:                                                                                                                                                           | This bit is                                   | only availal    | ble on PIC1        | 8F4X8 devi   | ces. For PI  | C18F2X8 de | evices, this bit       |

# Note 1: This bit is only available on PIC18F4X8 devices. For PIC18F2X8 devices, this bit is unimplemented and reads as '0'.

| Legend:           |                  |                              |            |

|-------------------|------------------|------------------------------|------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read  | as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit | is unknown |

|       | U-0                      | R/W-1                                 | U-0             | R/W-1                 | R/W-1 | R/W-1 | R/W-1  | R/W-1                  |

|-------|--------------------------|---------------------------------------|-----------------|-----------------------|-------|-------|--------|------------------------|

|       | —                        | CMIP <sup>(1)</sup>                   | _               | EEIP                  | BCLIP | LVDIP | TMR3IP | ECCP1IP <sup>(1)</sup> |

|       | bit 7                    | · · · · · · · · · · · · · · · · · · · |                 |                       |       |       |        | bit 0                  |

| bit 7 | Unimplem                 | nented: Rea                           | <b>d as</b> '0' |                       |       |       |        |                        |

| bit 6 | CMIP: Cor                | mparator Inte                         | errupt Priori   | ty bit <sup>(1)</sup> |       |       |        |                        |

|       | 1 = High p<br>0 = Low pr |                                       |                 |                       |       |       |        |                        |

| bit 5 | Unimplem                 | nented: Rea                           | <b>d as</b> '0' |                       |       |       |        |                        |

| bit 4 | EEIP: EEF                | PROM Write                            | Interrupt Pr    | iority bit            |       |       |        |                        |

|       | 1 = High p<br>0 = Low pr | ,                                     |                 |                       |       |       |        |                        |

| bit 3 | BCLIP: Bu                | us Collision I                        | nterrupt Prie   | ority bit             |       |       |        |                        |

|       | 1 = High p<br>0 = Low pr | •                                     |                 |                       |       |       |        |                        |

| bit 2 | LVDIP: Lo                | w-Voltage D                           | etect Interru   | upt Priority b        | bit   |       |        |                        |

|       | 1 = High p<br>0 = Low pr | ,                                     |                 |                       |       |       |        |                        |

| bit 1 | TMR3IP: 1                | MR3 Overflo                           | ow Interrup     | t Priority bit        |       |       |        |                        |

|       | 1 = High p<br>0 = Low pr | •                                     |                 |                       |       |       |        |                        |

| bit 0 | ECCP1IP:                 | ECCP1 Inte                            | rrupt Priorit   | y bit <sup>(1)</sup>  |       |       |        |                        |

|       | 1 = High p<br>0 = Low pr |                                       |                 |                       |       |       |        |                        |

# REGISTER 8-11: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

Note 1: This bit is only available on PIC18F4X8 devices. For PIC18F2X8 devices, this bit is unimplemented and reads as '0'.

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

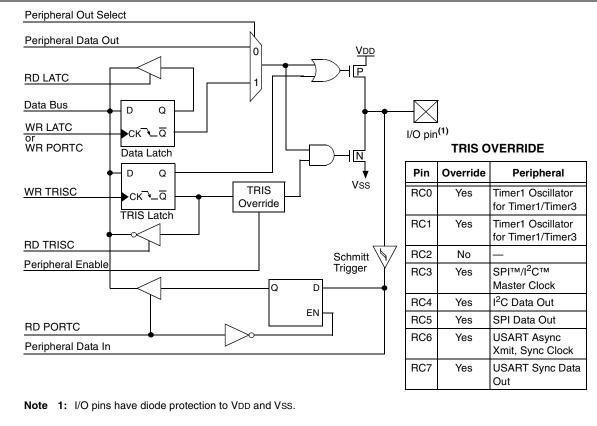

# 9.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATC register, read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 9-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register, without concern due to peripheral overrides.

| Ε | ХАМР  | LE 9-3: | INITIALIZING PORTC      |

|---|-------|---------|-------------------------|

| ( | CLRF  | PORTC   | ; Initialize PORTC by   |

|   |       |         | ; clearing output       |

|   |       |         | ; data latches          |

| ( | CLRF  | LATC    | ; Alternate method      |

|   |       |         | ; to clear output       |

|   |       |         | ; data latches          |

| ľ | MOVLW | 0CFh    | ; Value used to         |

|   |       |         | ; initialize data       |

|   |       |         | ; direction             |

| ľ | MOVWF | TRISC   | ; Set RC3:RC0 as inputs |

|   |       |         | ; RC5:RC4 as outputs    |

|   |       |         | ; RC7:RC6 as inputs     |

# FIGURE 9-8: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

# PIC18FXX8

NOTES:

# 15.0 CAPTURE/COMPARE/PWM (CCP) MODULES

The CCP (Capture/Compare/PWM) module contains a 16-bit register that can operate as a 16-bit Capture register, as a 16-bit Compare register or as a PWM Duty Cycle register.

The operation of the CCP module is identical to that of the ECCP module (discussed in detail in Section 16.0 "Enhanced Capture/Compare/PWM (ECCP) Module") with two exceptions. The CCP module has a Capture special event trigger that can be used as a message received time-stamp for the CAN module (refer to **Section 19.0 "CAN Module**" for CAN operation) which the ECCP module does not. The ECCP module, on the other hand, has Enhanced PWM functionality and auto-shutdown capability. Aside from these, the operation of the module described in this section is the same as the ECCP.

The control register for the CCP module is shown in Register 15-1. Table 15-2 (following page) details the interactions of the CCP and ECCP modules.

## REGISTER 15-1: CCP1CON: CCP1 CONTROL REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| _     | —   | DC1B1 | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

- bit 7-6 Unimplemented: Read as '0'

- bit 5-4 DCxB1:DCxB0: PWM Duty Cycle bit 1 and bit 0

| Capture mode: |

|---------------|

| Unused.       |

| Compare mode: |

| Unused.       |

|               |

PWM mode:

These bits are the two LSbs (bit 1 and bit 0) of the 10-bit PWM duty cycle. The upper eight bits (DCx9:DCx2) of the duty cycle are found in CCPRxL.

#### bit 3-0 CCPxM3:CCPxM0: CCPx Mode Select bits

- 0000 = Capture/Compare/PWM off (resets CCPx module)

- 0001 = Reserved

- 0010 = Compare mode, toggle output on match (CCPxIF bit is set)

- 0011 = Capture mode, CAN message received (CCP1 only)

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, initialize CCP pin low, on compare match force CCP pin high (CCPIF bit is set)

- 1001 = Compare mode, initialize CCP pin high, on compare match force CCP pin low (CCPIF bit is set)

- 1010 = Compare mode, CCP pin is unaffected (CCPIF bit is set)

- 1011 = Compare mode, trigger special event (CCP1IF bit is set; CCP resets TMR1 or TMR3 and starts an A/D conversion if the A/D module is enabled)

- 11xx = PWM mode

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 16.2 **Capture Mode**

The Capture mode of the ECCP module is virtually identical in operation to that of the standard CCP module as discussed in Section 15.1 "CCP1 Module". The differences are in the registers and port pins involved:

- The 16-bit Capture register is ECCPR1 (ECCPR1H and ECCPR1L);

- The capture event is selected by control bits ECCP1M3:ECCP1M0 (ECCP1CON<3:0>);

- The interrupt bits are ECCP1IE (PIE2<0>) and ECCP1IF (PIR2<0>); and

- The capture input pin is RD4 and its corresponding direction control bit is TRISD<4>.

Other operational details, including timer selection, output pin configuration and software interrupts, are exactly the same as the standard CCP module.

#### 16.2.1 CAN MESSAGE TIME-STAMP

**TABLE 16-4:**

The special capture event for the reception of CAN messages (Section 15.2.5 "CAN Message Time-Stamp") is not available with the ECCP module.

TIMER1 AND TIMER3

#### 16.3 **Compare Mode**

The Compare mode of the ECCP module is virtually identical in operation to that of the standard CCP module as discussed in Section 15.2 "Capture Mode". The differences are in the registers and port pins as described in Section 16.2 "Capture Mode". All other details are exactly the same.

#### 16.3.1 SPECIAL EVENT TRIGGER

Except as noted below, the special event trigger output of ECCP1 functions identically to that of the standard CCP module. It may be used to start an A/D conversion if the A/D module is enabled.

The special event trigger from the ECCP1 Note: module will not set the Timer1 or Timer3 interrupt flag bits.

| Name     | Bit 7                                                                       | Bit 6            | Bit 5       | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0    | Value on<br>POR, BOI | allo      | ie on<br>other<br>sets |

|----------|-----------------------------------------------------------------------------|------------------|-------------|---------------|---------------|---------------|---------------|----------|----------------------|-----------|------------------------|

| INTCON   | GIE/GIEH                                                                    | PEIE/GIEL        | TMR0IE      | INT0IE        | RBIE          | TMR0IF        | INTOIF        | RBIF     | 0000 000             | x 0000    | 000u                   |

| PIR2     | _                                                                           | CMIF             | _           | EEIF          | BCLIF         | LVDIF         | <b>TMR3IF</b> | ECCP1IF  | -0-0 000             | 0 - 0 - 0 | 0000                   |

| PIE2     | _                                                                           | CMIE             | —           | EEIE          | BCLIE         | LVDIE         | TMR3IE        | ECCP1IE  | -0-0 000             | 0 - 0 - 0 | 0000                   |

| IPR2     | _                                                                           | CMIP             | —           | EEIP          | BCLIP         | LVDIP         | TMR3IP        | ECCP1IP  | -1-1 111             | 1 -1-1    | 1111                   |

| TMR1L    | Holding Reg                                                                 | gister for the l | Least Signi | ficant Byte o | of the 16-bit | TMR1 Regi     | ster          |          | XXXX XXX             | x uuuu    | uuuu                   |

| TMR1H    | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |                  |             |               |               |               | XXXX XXX      | x uuuu   | uuuu                 |           |                        |

| T1CON    | RD16                                                                        | _                | T1CKPS1     | T1CKPS0       | T1OSCEN       | T1SYNC        | TMR1CS        | TMR10N   | 0-00 000             | 0 u-uu    | uuuu                   |

| TMR3L    | Holding Register for the Least Significant Byte of the 16-bit TMR3 Register |                  |             |               |               |               |               |          | XXXX XXX             | x uuuu    | uuuu                   |

| TMR3H    | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register  |                  |             |               |               |               |               | XXXX XXX | x uuuu               | uuuu      |                        |

| T3CON    | RD16                                                                        | T3ECCP1          | T3CKPS1     | T3CKPS0       | T3CCP1        | <b>T3SYNC</b> | TMR3CS        | TMR3ON   | 0000 000             | 0 uuuu    | uuuu                   |

| TRISD    | SD PORTD Data Direction Register                                            |                  |             |               |               |               |               | 1111 111 | 1 1111               | 1111      |                        |

| ECCPR1L  | CPR1L Capture/Compare/PWM Register1 (LSB)                                   |                  |             |               |               |               | XXXX XXX      | x uuuu   | uuuu                 |           |                        |

| ECCPR1H  | CPR1H Capture/Compare/PWM Register1 (MSB)                                   |                  |             |               |               |               |               | XXXX XXX | x uuuu               | uuuu      |                        |

| ECCP1CON | EPWM1M1                                                                     | EPWM1M0          | EDC1B1      | EDC1B0        | ECCP1M3       | ECCP1M2       | ECCP1M1       | ECCP1M0  | 0000 000             | 0 0000    | 0000                   |

**REGISTERS ASSOCIATED WITH ENHANCED CAPTURE, COMPARE,**

x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the ECCP module and Timer1. Leaend:

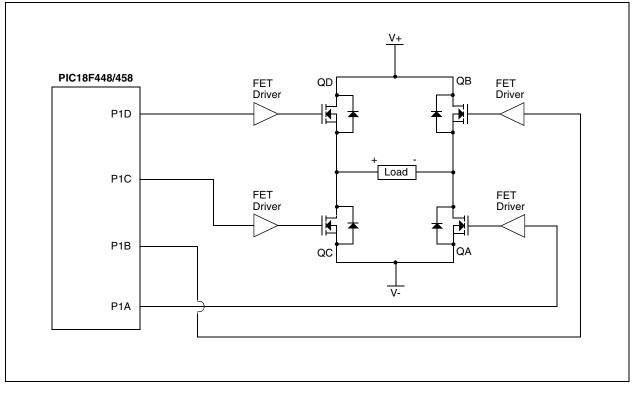

## 16.5.3.1 Direction Change in Full-Bridge Mode

In the Full-Bridge Output mode, the EPWM1M1 bit in the ECCP1CON register allows the user to control the forward/reverse direction. When the application firmware changes this direction control bit, the ECCP1 module will assume the new direction on the next PWM cycle. The current PWM cycle still continues, however, the non-modulated outputs, P1A and P1C signals, will transition to the new direction Tosc, 4 Tosc or 16 Tosc earlier (for T2CKRS<1:0> = 00, 01 or 1x, respectively) before the end of the period. During this transition cycle, the modulated outputs, P1B and P1D, will go to the inactive state (Figure 16-7).

Note that in the Full-Bridge Output mode, the ECCP module does not provide any dead-band delay. In general, since only one output is modulated at all times, dead-band delay is not required. However, there is a situation where a dead-band delay might be required. This situation occurs when all of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn-off time of the power switch, including the power device and driver circuit, is greater than turn-on time.

Figure 16-8 shows an example where the PWM direction changes from forward to reverse at a near 100% duty cycle. At time t1, the outputs P1A and P1D become inactive, while output P1C becomes active. In this example, since the turn-off time of the power devices is longer than the turn-on time, a shoot-through current flows through power devices QB and QD (see Figure 16-6) for the duration of 't'. The same phenomenon will occur to power devices QA and QC for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, one of the following requirements must be met:

- 1. Avoid changing PWM output direction at or near 100% duty cycle.

- 2. Use switch drivers that compensate the slow turn off of the power devices. The total turn-off time  $(t_{off})$  of the power device and the driver must be less than the turn-on time  $(t_{on})$ .

#### 17.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 17.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.3.10 BUS MODE COMPATIBILITY

Table 17-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | <b>Control Bits State</b> |     |  |  |  |

|-------------------|---------------------------|-----|--|--|--|

| Terminology       | СКР                       | CKE |  |  |  |

| 0, 0              | 0                         | 1   |  |  |  |

| 0, 1              | 0                         | 0   |  |  |  |

| 1, 0              | 1                         | 1   |  |  |  |

| 1, 1              | 1                         | 0   |  |  |  |

There is also an SMP bit which controls when the data is sampled.

| Name    | Bit 7                                                          | Bit 6          | Bit 5    | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------------------------------------------------|----------------|----------|--------|--------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH                                                       | PEIE/GIEL      | TMR0IE   | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1    | PSPIF <sup>(1)</sup>                                           | ADIF           | RCIF     | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| PIE1    | PSPIE <sup>(1)</sup>                                           | ADIE           | RCIE     | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| IPR1    | PSPIP <sup>(1)</sup>                                           | ADIP           | RCIP     | TXIP   | SSPIP  | CCP1IP | TMR2IP | TMR1IP    | 1111 1111            | 1111 1111                       |

| TRISC   | PORTC Da                                                       | ta Direction F | Register |        |        |        |        |           | 1111 1111            | 1111 1111                       |

| TRISA   | —                                                              | TRISA6         | TRISA5   | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0    | -111 1111            | -111 1111                       |

| SSPBUF  | SPBUF Synchronous Serial Port Receive Buffer/Transmit Register |                |          |        |        |        |        | xxxx xxxx | uuuu uuuu            |                                 |

| SSPCON1 | WCOL                                                           | SSPOV          | SSPEN    | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0     | 0000 0000            | 0000 0000                       |

| SSPSTAT | SMP                                                            | CKE            | D/A      | Р      | S      | R/W    | UA     | BF        | 0000 0000            | 0000 0000                       |

#### TABLE 17-2: REGISTERS ASSOCIATED WITH SPI™ OPERATION

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI<sup>TM</sup> mode.**Note 1:**These registers or register bits are not implemented on the PIC18F248 and PIC18F258 and read as '0's.

## 17.4.3.2 Reception

When the R/W bit of the address byte is clear and an address match occurs, the R/W bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON1<4>). See **Section 17.4.4** "**Clock Stretching**" for more detail.

#### 17.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low regardless of SEN (see Section 17.4.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then, pin RC3/ SCK/SCL should be enabled by setting bit CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 17-9).

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

# PIC18FXX8

#### REGISTER 19-23: RXFnEIDH: RECEIVE ACCEPTANCE FILTER n EXTENDED IDENTIFIER, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0

EID15:EID8: Extended Identifier Filter bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 19-24: RXFnEIDL: RECEIVE ACCEPTANCE FILTER n EXTENDED IDENTIFIER, LOW BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 EID7:EID0: Extended Identifier Filter bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 19-25: RXMnSIDH: RECEIVE ACCEPTANCE MASK n STANDARD IDENTIFIER MASK, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 SID10:SID3: Standard Identifier Mask bits or Extended Identifier Mask bits EID28:EID21

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## 19.7.1 TIME QUANTA

As already mentioned, the time quanta is a fixed unit derived from the oscillator period and baud rate prescaler. Its relationship to TBIT and the nominal bit rate is shown in Example 19-2.

#### EXAMPLE 19-2: CALCULATING TQ, NOMINAL BIT RATE AND NOMINAL BIT TIME

$TQ (\mu s) = (2 * (BRP + 1))/FOSC (MHz)$

TBIT ( $\mu$ s) = TQ ( $\mu$ s) \* number of TQ per bit interval Nominal Bit Rate (bits/s) = 1/TBIT

## CASE 1:

For Fosc = 16 MHz, BRP<5:0> = 00h and Nominal Bit Time = 8 Tq:

$TQ = (2 * 1)/16 = 0.125 \,\mu s \,(125 \,ns)$

TBIT =  $8 * 0.125 = 1 \ \mu s \ (10^{-6} s)$

Nominal Bit Rate =  $1/10^{-6} = 10^{6}$  bits/s (1 Mb/s)

## CASE 2:

For Fosc = 20 MHz, BRP<5:0> = 01h and Nominal Bit Time = 8 Tq:

$Tq = (2 * 2)/20 = 0.2 \ \mu s \ (200 \ ns)$

TBIT =  $8 * 0.2 = 1.6 \,\mu s \,(1.6 * 10^{-6} s)$

Nominal Bit Rate =  $1/1.6 * 10^{-6}$ s = 625,000 bits/s (625 Kb/s)

## CASE 3:

For FOSC = 25 MHz, BRP<5:0> = 3Fh and Nominal Bit Time = 25 TQ:  $TQ = (2 * 64)/25 = 5.12 \ \mu s$ TBIT = 25 \* 5.12 = 128 \ \mu s (1.28 \* 10<sup>-4</sup>s) Nominal Bit Rate = 1/1.28 \* 10<sup>-4</sup> = 7813 bits/s (7.8 Kb/s)

The frequencies of the oscillators in the different nodes must be coordinated in order to provide a system wide specified nominal bit time. This means that all oscillators must have a Tosc that is an integral divisor of TQ. It should also be noted that although the number of TQ is programmable from 4 to 25, the usable minimum is 8 TQ. A bit time of less than 8 TQ in length is not ensured to operate correctly.

# 19.7.2 SYNCHRONIZATION SEGMENT

This part of the bit time is used to synchronize the various CAN nodes on the bus. The edge of the input signal is expected to occur during the sync segment. The duration is 1 Tq.

# 19.7.3 PROPAGATION SEGMENT

This part of the bit time is used to compensate for physical delay times within the network. These delay times consist of the signal propagation time on the bus line and the internal delay time of the nodes. The length of the Propagation Segment can be programmed from 1 TQ to 8 TQ by setting the PRSEG2:PRSEG0 bits.

## 19.7.4 PHASE BUFFER SEGMENTS

The phase buffer segments are used to optimally locate the sampling point of the received bit within the nominal bit time. The sampling point occurs between Phase Segment 1 and Phase Segment 2. These segments can be lengthened or shortened by the resynchronization process. The end of Phase Segment 1 determines the sampling point within a bit time. Phase Segment 1 is programmable from 1 Tq to 8 Tq in duration. Phase Segment 2 provides delay before the next transmitted data transition and is also programmable from 1 Tq to 8 Tq in duration. However, due to IPT requirements, the actual minimum length of Phase Segment 2 is 2 Tq or it may be defined to be equal to the greater of Phase Segment 1 or the Information Processing Time (IPT).

## 19.7.5 SAMPLE POINT

The sample point is the point of time at which the bus level is read and the value of the received bit is determined. The sampling point occurs at the end of Phase Segment 1. If the bit timing is slow and contains many TQ, it is possible to specify multiple sampling of the bus line at the sample point. The value of the received bit is determined to be the value of the majority decision of three values. The three samples are taken at the sample point and twice before, with a time of TQ/2 between each sample.

# 19.7.6 INFORMATION PROCESSING TIME

The Information Processing Time (IPT) is the time segment, starting at the sample point, that is reserved for calculation of the subsequent bit level. The CAN specification defines this time to be less than or equal to 2 Tq. The PIC18FXX8 defines this time to be 2 Tq. Thus, Phase Segment 2 must be at least 2 Tq long.

## 21.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from Sleep mode when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators, CM<2:0> = 111, before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

# 21.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators will be powered down during the Reset interval.

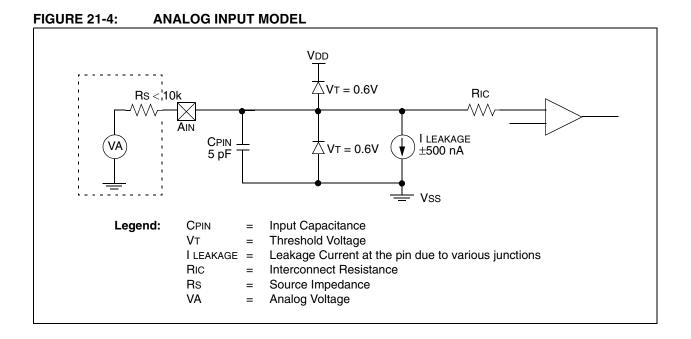

# 21.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 21-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

| Name   | Bit 7              | Bit 6               | Bit 5               | Bit 4                  | Bit 3 | Bit 2  | Bit 1  | Bit 0                  |         | alue on All other POR Reset |         | ther |

|--------|--------------------|---------------------|---------------------|------------------------|-------|--------|--------|------------------------|---------|-----------------------------|---------|------|

| CMCON  | C2OUT              | C1OUT               | C2INV               | C1INV                  | CIS   | CM2    | CM1    | CM0                    | 0000    | 0000                        | 0000    | 0000 |

| CVRCON | CVREN              | CVROE               | CVRR                | CVRSS                  | CVR3  | CVR2   | CVR1   | CVR0                   | 0000    | 0000                        | 0000    | 0000 |

| INTCON | GIE/<br>GIEH       | PEIE/<br>GIEL       | TMR0IE              | INTOIE                 | RBIE  | TMR0IF | INTOIF | RBIF                   | 0000    | 000x                        | 0000    | 000u |

| PIR2   | _                  | CMIF <sup>(1)</sup> | _                   | EEIF                   | BCLIF | LVDIF  | TMR3IF | ECCP1IF <sup>(1)</sup> | - 0 - 0 | 0000                        | - 0 - 0 | 0000 |

| PIE2   | _                  | CMIE <sup>(1)</sup> | _                   | EEIE                   | BCLIE | LVDIE  | TMR3IE | ECCP1IE <sup>(1)</sup> | - 0 - 0 | 0000                        | - 0 - 0 | 0000 |

| IPR2   | Ι                  | CMIP <sup>(1)</sup> | _                   | EEIP                   | BCLIP | LVDIP  | TMR3IP | ECCP1IP <sup>(1)</sup> | -1-1    | 1111                        | -1-1    | 1111 |

| PORTD  | RD7                | RD6                 | RD5                 | RD4                    | RD3   | RD2    | RD1    | RD0                    | xxxx    | xxxx                        | uuuu    | uuuu |

| LATD   | LATD7              | LATD6               | LATD5               | LATD4                  | LATD3 | LATD2  | LATD1  | LATD0                  | xxxx    | xxxx                        | uuuu    | uuuu |

| TRISD  | PORTD              | Data Dire           | ection Reg          | gister                 |       |        |        |                        | 1111    | 1111                        | 1111    | 1111 |

| PORTE  | —                  | —                   | —                   |                        | _     | RE2    | RE1    | RE0                    |         | -xxx                        |         | -000 |

| LATE   | _                  | _                   | —                   |                        | _     | LATE2  | LATE1  | LATE0                  |         | -xxx                        |         | -uuu |

| TRISE  | IBF <sup>(1)</sup> | OBF <sup>(1)</sup>  | IBOV <sup>(1)</sup> | PSPMODE <sup>(1)</sup> | _     | TRISE2 | TRISE1 | TRISE0                 | 0000    | -111                        | 0000    | -111 |

## TABLE 21-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'

Note 1: These bits are reserved on PIC18F2X8 devices; always maintain these bits clear.

#### TABLE 25-2: PIC18FXXX INSTRUCTION SET

| Mnemo   | onic,                           | Description                           | Cycles     | 16-E | Bit Instr    | uction W | /ord | Status           | Notes      |

|---------|---------------------------------|---------------------------------------|------------|------|--------------|----------|------|------------------|------------|

| Opera   | nds                             | Description                           | Cycles     | MSb  |              |          | LSb  | Affected         | notes      |

| BYTE-OR | IENTED                          | FILE REGISTER OPERATIONS              | 6          |      |              |          |      |                  |            |

| ADDWF   | f, d, a                         | Add WREG and f                        | 1          | 0010 | 01da         | ffff     | ffff | C, DC, Z, OV, N  |            |

| ADDWFC  | f, d, a                         | Add WREG and Carry bit to f           | 1          | 0010 | 00da         | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| ANDWF   | f, d, a                         | AND WREG with f                       | 1          | 0001 | 01da         | ffff     | ffff | Z, N             | 1,2        |

| CLRF    | f, a                            | Clear f                               | 1          | 0110 | 101a         | ffff     | ffff | Z                | 2          |

| COMF    | f, d, a                         | Complement f                          | 1          | 0001 | 11da         | ffff     | ffff | Z, N             | 1, 2       |

| CPFSEQ  | f, a                            | Compare f with WREG, skip =           | 1 (2 or 3) | 0110 | 001a         | ffff     | ffff | None             | 4          |

| CPFSGT  | f, a                            | Compare f with WREG, skip >           | 1 (2 or 3) | 0110 | 010a         | ffff     | ffff | None             | 4          |

| CPFSLT  | f, a                            | Compare f with WREG, skip <           | 1 (2 or 3) | 0110 | 000a         | ffff     | ffff | None             | 1, 2       |

| DECF    | f, d, a                         | Decrement f                           | 1 .        | 0000 | 01da         | ffff     | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| DECFSZ  | f, d, a                         | Decrement f, Skip if 0                | 1 (2 or 3) | 0010 | 11da         | ffff     | ffff | None             | 1, 2, 3, 4 |

| DCFSNZ  | f, d, a                         | Decrement f, Skip if Not 0            | 1 (2 or 3) |      | 11da         | ffff     | ffff | None             | 1, 2       |

| INCF    | f, d, a                         | Increment f                           | 1 ΄        | 0010 | 10da         | ffff     | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| INCFSZ  |                                 | Increment f, Skip if 0                | 1 (2 or 3) |      | 11da         | ffff     | ffff | None             | 4          |

| INFSNZ  | f, d, a                         | Increment f, Skip if Not 0            | 1 (2 or 3) |      | 10da         | ffff     | ffff | None             | 1,2        |

| IORWF   | f, d, a                         | Inclusive OR WREG with f              | 1          |      | 00da         | ffff     | ffff |                  | 1, 2       |

| MOVF    | f, d, a                         | Move f                                | 1          |      | 00da         | ffff     |      | Z, N             | 1          |

| MOVFF   | f <sub>s</sub> , f <sub>d</sub> |                                       | 2          |      | ffff         | ffff     |      | None             | •          |

| movi i  | 's, 'a                          | f <sub>d</sub> (destination) 2nd word | -          |      | ffff         | ffff     | ffff |                  |            |

| MOVWF   | f, a                            | Move WREG to f                        | 1          |      | 111a         | ffff     | ffff | None             |            |

| MULWF   | f, a                            | Multiply WREG with f                  | 1          |      | 001a         | ffff     |      | None             |            |

| NEGF    | f, a                            | Negate f                              | 1          |      | 110a         | ffff     | ffff | C, DC, Z, OV, N  | 12         |

| RLCF    | f, d, a                         | Rotate Left f through Carry           | 1          |      | 01da         | ffff     | ffff | C, Z, N          | 1, 2       |

| RLNCF   |                                 | Rotate Left f (No Carry)              | 1          |      | 01da<br>01da | ffff     | ffff |                  | 1, 2       |

| RRCF    | f, d, a                         | Rotate Right f through Carry          | 1          |      | 01da<br>00da | ffff     | ffff | C, Z, N          | 1, 2       |

| RRNCF   | f, d, a                         | Rotate Right f (No Carry)             | 1          |      | 00da<br>00da | ffff     | ffff |                  |            |

| SETF    | f, a                            | Set f                                 | 1          |      | 100a         | ffff     |      | None             |            |

| SUBFWB  |                                 | Subtract f from WREG with             | 1          |      |              | ffff     | ffff | C, DC, Z, OV, N  | 1 0        |

| SUBEWB  | f, d, a                         | borrow                                | 1          | 0101 | 01da         | LLLL     | LLLL | C, DC, Z, OV, N  | 1, 2       |

| SUBWF   | f, d, a                         | Subtract WREG from f                  | 1          | 0101 | 11da         | ffff     | ffff | C, DC, Z, OV, N  |            |

|         | f, d, a                         | Subtract WREG from f with             | 1          |      | 10da         | ffff     | ffff | C, DC, Z, OV, N  | 12         |

| 0001110 | i, a, a                         | borrow                                |            | 0101 | Toda         |          |      | 0, 20, 2, 01, 11 | •, –       |

| SWAPF   | f, d, a                         | Swap nibbles in f                     | 1          | 0011 | 10da         | ffff     | ffff | None             | 4          |

| TSTFSZ  | f, a                            | Test f, skip if 0                     | 1 (2 or 3) |      | 100a<br>011a | ffff     |      | None             | 4<br>1, 2  |

| XORWF   | f, d, a                         | Exclusive OR WREG with f              | 1          |      | 10da         | ffff     |      | Z, N             | 1, 2       |

| -       |                                 |                                       | 1          | 0001 | IUda         | LLLL     | LLLL | Ζ, Ν             |            |

|         |                                 |                                       | 4          | 1005 |              |          |      | Nere             | 1.0        |

| BCF     | f, b, a                         | Bit Clear f                           | 1          |      | bbba         | ffff     | ffff | None             | 1,2        |

| BSF     | , .,                            | Bit Set f                             | 1          |      | bbba         | ffff     | ffff | None             | 1,2        |

| BTFSC   |                                 | Bit Test f, Skip if Clear             | 1 (2 or 3) |      | bbba         | ffff     |      | None             | 3, 4       |

| BTFSS   |                                 | Bit Test f, Skip if Set               | 1 (2 or 3) |      | bbba         | ffff     | ffff | None             | 3, 4       |

| BTG     | f, d, a                         | Bit Toggle f                          | 1          | 0111 | bbba         | ffff     | ffff | None             | 1, 2       |

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

# PIC18FXX8

| TSTR                     | sz                                                | Test f, Skij                                                              | o if O                                                                                                                                                                                                                                                                                                       |        |          |  |  |  |

|--------------------------|---------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|--|--|--|

| Synta                    | ax:                                               | [ label ]                                                                 | ISTFSZ                                                                                                                                                                                                                                                                                                       | f [,a] |          |  |  |  |

| Oper                     | ands:                                             | $0 \le f \le 255$                                                         |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

|                          |                                                   | a ∈ [0,1]                                                                 |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

| Oper                     | ation:                                            | skip if f = 0                                                             |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

| Statu                    | s Affected:                                       | None                                                                      |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

| Enco                     | ding:                                             | 0110                                                                      | 0110 011a fff                                                                                                                                                                                                                                                                                                |        |          |  |  |  |

| Desc                     | ription:                                          | during the<br>is discarde<br>making this<br>is '0', the A<br>overriding t | If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a two-cycle instruction. If 'a'<br>is '0', the Access Bank will be selected,<br>overriding the BSR value. If 'a' is '1',<br>then the bank will be selected as per |        |          |  |  |  |

| Word                     | ls:                                               | 1                                                                         |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

| Cycle                    | es:                                               | 1(2)                                                                      |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

| - )                      |                                                   | Note: 3 c                                                                 | Note: 3 cycles if skip and followed                                                                                                                                                                                                                                                                          |        |          |  |  |  |

| by a 2-word instruction. |                                                   |                                                                           |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

| QC                       | ycle Activity:                                    |                                                                           |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

|                          | Q1<br>Decode                                      | Q2<br>Read                                                                | Q3<br>Proce                                                                                                                                                                                                                                                                                                  |        | Q4<br>No |  |  |  |

|                          | Decode                                            | register 'f'                                                              | Data                                                                                                                                                                                                                                                                                                         |        | peration |  |  |  |

| lf sk                    | ip:                                               |                                                                           |                                                                                                                                                                                                                                                                                                              |        |          |  |  |  |

|                          | Q1                                                | Q2                                                                        | Q                                                                                                                                                                                                                                                                                                            | 3      | Q4       |  |  |  |

|                          | No                                                | No                                                                        | No                                                                                                                                                                                                                                                                                                           |        | No       |  |  |  |

|                          | operation                                         | operation                                                                 | operat                                                                                                                                                                                                                                                                                                       |        | peration |  |  |  |

| IT SK                    | ip and followe<br>Q1                              | a by 2-wora ir<br>Q2                                                      | Istruction<br>Q3                                                                                                                                                                                                                                                                                             |        | Q4       |  |  |  |

|                          | No                                                | No                                                                        | No                                                                                                                                                                                                                                                                                                           |        | No<br>No |  |  |  |

|                          | operation                                         | operation                                                                 | operat                                                                                                                                                                                                                                                                                                       |        | peration |  |  |  |

|                          | No                                                | No                                                                        | No                                                                                                                                                                                                                                                                                                           |        | No       |  |  |  |

|                          | operation                                         | operation                                                                 | operat                                                                                                                                                                                                                                                                                                       | tion o | peration |  |  |  |

| <u>Exan</u>              | <u>nple:</u>                                      | HERE<br>NZERO<br>ZERO :                                                   | NZERO :                                                                                                                                                                                                                                                                                                      |        |          |  |  |  |

|                          | Before Instruc<br>PC                              |                                                                           | ddress (                                                                                                                                                                                                                                                                                                     | HERE)  |          |  |  |  |

|                          | After Instruction<br>If CNT<br>PC<br>If CNT<br>PC | on<br>= 0><br>= Ao<br>≠ 0>                                                | :00,                                                                                                                                                                                                                                                                                                         | ZERO)  |          |  |  |  |

| XORLW               | Exclusiv            | Exclusive OR Literal with W |      |               |  |  |  |  |

|---------------------|---------------------|-----------------------------|------|---------------|--|--|--|--|

| Syntax:             | [ label ]           | [ <i>label</i> ] XORLW k    |      |               |  |  |  |  |

| Operands:           | $0 \le k \le 25$    | 5                           |      |               |  |  |  |  |

| Operation:          | (W) .XOF            | $k \to W$                   |      |               |  |  |  |  |

| Status Affected:    | N, Z                |                             |      |               |  |  |  |  |

| Encoding:           | 0000                | 1010                        | kkkk | kkkk          |  |  |  |  |

| Description:        |                     | ents of W<br>iteral 'k'. T  |      |               |  |  |  |  |

| Words:              | 1                   |                             |      |               |  |  |  |  |

| Cycles:             | 1                   | 1                           |      |               |  |  |  |  |

| Q Cycle Activity:   |                     |                             |      |               |  |  |  |  |

| Q1                  | Q2                  | Q3                          |      | Q4            |  |  |  |  |

| Decode              | Read<br>literal 'k' | Proces<br>Data              |      | Vrite to<br>W |  |  |  |  |

| Example:            | XORLW               | 0xAF                        |      |               |  |  |  |  |

| Before Instruc<br>W | tion<br>= 0xB5      |                             |      |               |  |  |  |  |

After Instruction W =

= 0x1A

# 27.2 DC Characteristics: PIC18FXX8 (Industrial, Extended) PIC18LFXX8 (Industrial)

| DC CH        | ARACTE | RISTICS                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |        |                                               |  |  |

|--------------|--------|--------------------------------------------|------------------------------------------------------|--------------------|--------|-----------------------------------------------|--|--|

| Param<br>No. | Symbol | Characteristic/<br>Device                  | Min                                                  | Мах                | Units  | Conditions                                    |  |  |

|              | VIL    | Input Low Voltage                          |                                                      |                    |        |                                               |  |  |

|              |        | I/O ports:                                 |                                                      |                    |        |                                               |  |  |

| D030         |        | with TTL buffer                            | Vss                                                  | 0.15 Vdd           | V      | VDD < 4.5V                                    |  |  |

| D030A        |        |                                            | —                                                    | 0.8                | V      | $4.5V \le VDD \le 5.5V$                       |  |  |

| D031         |        | with Schmitt Trigger buffer<br>RC3 and RC4 | Vss<br>Vss                                           | 0.2 Vdd<br>0.3 Vdd | V<br>V |                                               |  |  |

| D032         |        | MCLR                                       | Vss                                                  | 0.2 Vdd            | V      |                                               |  |  |

| D032A        |        | OSC1 (in XT, HS and LP modes) and T1OSI    | Vss                                                  | 0.3 Vdd            | V      |                                               |  |  |

| D033         |        | OSC1 (in RC mode) <sup>(1)</sup>           | Vss                                                  | 0.2 Vdd            | v      |                                               |  |  |

|              | Viн    | Input High Voltage                         |                                                      |                    |        |                                               |  |  |

|              |        | I/O ports:                                 |                                                      |                    |        |                                               |  |  |

| D040         |        | with TTL buffer                            | 0.25 VDD + 0.8V                                      | Vdd                | V      | VDD < 4.5V                                    |  |  |

| D040A        |        |                                            | 2.0                                                  | Vdd                | V      | $4.5V \le V$ DD $\le 5.5V$                    |  |  |

| D041         |        | with Schmitt Trigger buffer<br>RC3 and RC4 | 0.8 Vdd<br>0.7 Vdd                                   | Vdd<br>Vdd         | V<br>V |                                               |  |  |

| D042         |        | MCLR                                       | 0.8 Vdd                                              | Vdd                | V      |                                               |  |  |

| D042A        |        | OSC1 (in XT, HS and LP modes) and T1OSI    | 0.7 Vdd                                              | Vdd                | V      |                                               |  |  |

| D043         |        | OSC1 (RC mode) <sup>(1)</sup>              | 0.9 Vdd                                              | Vdd                | v      |                                               |  |  |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>     |                                                      |                    |        |                                               |  |  |

| D060         |        | I/O ports                                  | —                                                    | ±1                 | μA     | $Vss \le VPIN \le VDD,$ Pin at high-impedance |  |  |

| D061         |        | MCLR                                       | —                                                    | ±5                 | μA     | $Vss \le VPIN \le VDD$                        |  |  |

| D063         |        | OSC1                                       | —                                                    | ±5                 | μΑ     | $Vss \le VPIN \le VDD$                        |  |  |

|              | IPU    | Weak Pull-up Current                       |                                                      |                    |        |                                               |  |  |

| D070         | IPURB  | PORTB weak pull-up current                 | 50                                                   | 450                | μA     | VDD = 5V, VPIN = VSS                          |  |  |

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the PICmicro<sup>®</sup> device be driven with an external clock while in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

## 27.3.2 TIMING CONDITIONS