Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1.5К х 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 5x10b                                                                   |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf258t-i-sog |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **TO OUR VALUED CUSTOMERS**

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### TABLE 4-1: SPECIAL FUNCTION REGISTER MAP (CONTINUED)

| Address | Name                    | Address | Name                      | Address | Name                      | Address | Name     |

|---------|-------------------------|---------|---------------------------|---------|---------------------------|---------|----------|

| F7Fh    | —                       | F5Fh    |                           | F3Fh    | _                         | F1Fh    | RXM1EIDL |

| F7Eh    |                         | F5Eh    | CANSTATRO1 <sup>(4)</sup> | F3Eh    | CANSTATRO3 <sup>(4)</sup> | F1Eh    | RXM1EIDH |

| F7Dh    |                         | F5Dh    | RXB1D7                    | F3Dh    | TXB1D7                    | F1Dh    | RXM1SIDL |

| F7Ch    |                         | F5Ch    | RXB1D6                    | F3Ch    | TXB1D6                    | F1Ch    | RXM1SIDH |

| F7Bh    | —                       | F5Bh    | RXB1D5                    | F3Bh    | TXB1D5                    | F1Bh    | RXM0EIDL |

| F7Ah    | —                       | F5Ah    | RXB1D4                    | F3Ah    | TXB1D4                    | F1Ah    | RXM0EIDH |

| F79h    | —                       | F59h    | RXB1D3                    | F39h    | TXB1D3                    | F19h    | RXM0SIDL |

| F78h    | —                       | F58h    | RXB1D2                    | F38h    | TXB1D2                    | F18h    | RXM0SIDH |

| F77h    | —                       | F57h    | RXB1D1                    | F37h    | TXB1D1                    | F17h    | RXF5EIDL |

| F76h    | TXERRCNT                | F56h    | RXB1D0                    | F36h    | TXB1D0                    | F16h    | RXF5EIDH |

| F75h    | RXERRCNT                | F55h    | RXB1DLC                   | F35h    | TXB1DLC                   | F15h    | RXF5SIDL |

| F74h    | COMSTAT                 | F54h    | RXB1EIDL                  | F34h    | TXB1EIDL                  | F14h    | RXF5SIDH |

| F73h    | CIOCON                  | F53h    | RXB1EIDH                  | F33h    | TXB1EIDH                  | F13h    | RXF4EIDL |

| F72h    | BRGCON3                 | F52h    | RXB1SIDL                  | F32h    | TXB1SIDL                  | F12h    | RXF4EIDH |

| F71h    | BRGCON2                 | F51h    | RXB1SIDH                  | F31h    | TXB1SIDH                  | F11h    | RXF4SIDL |

| F70h    | BRGCON1                 | F50h    | RXB1CON                   | F30h    | TXB1CON                   | F10h    | RXF4SIDH |

| F6Fh    | CANCON                  | F4Fh    | _                         | F2Fh    |                           | F0Fh    | RXF3EIDL |

| F6Eh    | CANSTAT                 | F4Eh    | CANSTATRO2 <sup>(4)</sup> | F2Eh    | CANSTATRO4 <sup>(4)</sup> | F0Eh    | RXF3EIDH |

| F6Dh    |                         | F4Dh    | TXB0D7                    | F2Dh    | TXB2D7                    | F0Dh    | RXF3SIDL |

| F6Ch    |                         | F4Ch    | TXB0D6                    | F2Ch    | TXB2D6                    | F0Ch    | RXF3SIDH |

| F6Bh    | RXB0D5 <sup>(3)</sup>   | F4Bh    | TXB0D5                    | F2Bh    | TXB2D5                    | F0Bh    | RXF2EIDL |

| F6Ah    | RXB0D4 <sup>(3)</sup>   | F4Ah    | TXB0D4                    | F2Ah    | TXB2D4                    | F0Ah    | RXF2EIDH |

| F69h    | RXB0D3 <sup>(3)</sup>   | F49h    | TXB0D3                    | F29h    | TXB2D3                    | F09h    | RXF2SIDL |

| F68h    | RXB0D2 <sup>(3)</sup>   | F48h    | TXB0D2                    | F28h    | TXB2D2                    | F08h    | RXF2SIDH |

| F67h    | RXB0D1 <sup>(3)</sup>   | F47h    | TXB0D1                    | F27h    | TXB2D1                    | F07h    | RXF1EIDL |

| F66h    | RXB0D0 <sup>(3)</sup>   | F46h    | TXB0D0                    | F26h    | TXB2D0                    | F06h    | RXF1EIDH |

| F65h    | RXB0DLC <sup>(3)</sup>  | F45h    | TXB0DLC                   | F25h    | TXB2DLC                   | F05h    | RXF1SIDL |

| F64h    | RXB0EIDL <sup>(3)</sup> | F44h    | TXB0EIDL                  | F24h    | TXB2EIDL                  | F04h    | RXF1SIDH |

| F63h    | RXB0EIDH <sup>(3)</sup> | F43h    | TXB0EIDH                  | F23h    | TXB2EIDH                  | F03h    | RXF0EIDL |

| F62h    | RXB0SIDL <sup>(3)</sup> | F42h    | TXB0SIDL                  | F22h    | TXB2SIDL                  | F02h    | RXF0EIDH |

| F61h    | RXB0SIDH <sup>(3)</sup> | F41h    | TXB0SIDH                  | F21h    | TXB2SIDH                  | F01h    | RXF0SIDL |

| F60h    | RXB0CON <sup>(3)</sup>  | F40h    | TXB0CON                   | F20h    | TXB2CON                   | F00h    | RXF0SIDH |

Note: Shaded registers are available in Bank 15, while the rest are in Access Bank low.

**Note 1:** Unimplemented registers are read as '0'.

- 2: This is not a physical register.

- 3: Contents of register are dependent on WIN2:WIN0 bits in the CANCON register.

- 4: CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the CANSTAT register due to the Microchip header file requirement.

- 5: These registers are not implemented on the PIC18F248 and PIC18F258.

#### 6.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

#### 6.1 **Table Reads and Table Writes**

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 6-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in Section 6.5 "Writing to Flash Program Memory". Figure 6-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

## Instruction: TBLRD\* Program Memory Table Pointer<sup>(1)</sup> Table Latch (8-bit) TBLPTRH TBLPTRU TBLPTRL TABLAT Program Memory (TBLPTR) Note 1: Table Pointer points to a byte in program memory.

#### FIGURE 6-1: **TABLE READ OPERATION**

#### 8.1 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits. Because of the number of interrupts to be controlled, PIC18FXX8 devices have three INTCON registers. They are detailed in Register 8-1 through Register 8-3.

# Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0      | R/W-0                                                             | R/W-0         | R/W-0        | R/W-0         | R/W-0        | R/W-0        | R/W-x        |

|------------|-------------------------------------------------------------------|---------------|--------------|---------------|--------------|--------------|--------------|

| GIE/GIEF   | PEIE/GIEL                                                         | TMR0IE        | INT0IE       | RBIE          | TMR0IF       | INTOIF       | RBIF         |

| bit 7      | ·                                                                 |               |              |               |              |              | bit 0        |

|            | : Global Interr                                                   | -             | oit          |               |              |              |              |

| 1 = Enable | <u>N (RCON&lt;7&gt;)</u><br>es all unmaske<br>es all interrupt    | ed interrupts | i            |               |              |              |              |

| 1 = Enabl  | <u>N (RCON&lt;7&gt;)</u><br>es all high prio<br>es all priority i | rity interrup | ts           |               |              |              |              |

| PEIE/GIE   | -: Peripheral I                                                   | nterrupt Ena  | able bit     |               |              |              |              |

| 1 = Enable | <u>N (RCON&lt;7&gt;)</u><br>es all unmaske<br>es all peripher     | ed periphera  |              |               |              |              |              |

| 1 = Enable | <u>N (RCON&lt;7&gt;)</u><br>es all low prior<br>es all low prior  | ity periphera |              |               |              |              |              |

| TMR0IE:    | TMR0 Overflov                                                     | w Interrupt E | Enable bit   |               |              |              |              |

|            | es the TMR0 c<br>es the TMR0 (                                    |               | •            |               |              |              |              |

| INTOIE: IN | IT0 External Ir                                                   | nterrupt Ena  | ble bit      |               |              |              |              |

|            | es the INT0 ex<br>es the INT0 ex                                  |               | •            |               |              |              |              |

| RBIE: RB   | Port Change                                                       | Interrupt En  | able bit     |               |              |              |              |

|            | es the RB port<br>es the RB por                                   |               |              |               |              |              |              |

| TMR0IF:    | MR0 Overflov                                                      | v Interrupt F | lag bit      |               |              |              |              |

|            | register has o<br>register did no                                 |               | must be clea | ared in softv | vare)        |              |              |

| INTOIF: IN | IT0 External Ir                                                   | nterrupt Flag | ı bit        |               |              |              |              |

|            | IT0 external in<br>IT0 external in                                |               |              | be cleared i  | n software b | by reading P | ORTB)        |

| RBIF: RB   | Port Change I                                                     | nterrupt Fla  | g bit        |               |              |              |              |

|            | st one of the R<br>of the RB7:RB                                  |               |              |               | be cleared i | n software)  |              |

| Note:      | A mismatch mismatch co                                            |               |              |               |              | g PORTB v    | will end the |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| Name             | Bit#  | Buffer Type           | Function                                                                                                           |

|------------------|-------|-----------------------|--------------------------------------------------------------------------------------------------------------------|

| RE0/AN5/RD       | bit 0 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input or read control input in Parallel Slave Port mode.                             |

| RE1/AN6/WR/C1OUT | bit 1 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input, write control input in Parallel Slave Port mode or Comparator 1 output.       |

| RE2/AN7/CS/C2OUT | bit 2 | ST/TTL <sup>(1)</sup> | Input/output port pin, analog input, chip select control input in Parallel Slave Port mode or Comparator 2 output. |

#### TABLE 9-9: PORTE FUNCTIONS

**Legend:** ST = Schmitt Trigger input, TTL = TTL input

**Note 1:** Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port mode.

|  | TABLE 9-10: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTE |

|--|-------------|--------------------------------------------|

|--|-------------|--------------------------------------------|

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2                 | Bit 1                    | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|---------|-------|-----------------------|--------------------------|--------|----------------------|---------------------------------|

| TRISE  | IBF   | OBF   | IBOV  | PSPMODE | _     | TRISE2                | TRISE1                   | TRISE0 | 0000 -111            | 0000 -111                       |

| PORTE  | _     |       |       | _       | Ι     | Read POF<br>Write POF | RTE pin/<br>RTE Data La  | atch   | xxx                  | uuu                             |

| LATE   | —     | _     | _     | —       | _     | Read POF<br>Write POF | RTE Data L<br>RTE Data L |        | xxx                  | uuu                             |

| ADCON1 | ADFM  | ADCS2 |       | —       | PCFG3 | PCFG2                 | PCFG1                    | PCFG0  | 00 0000              | 00 0000                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by PORTE.

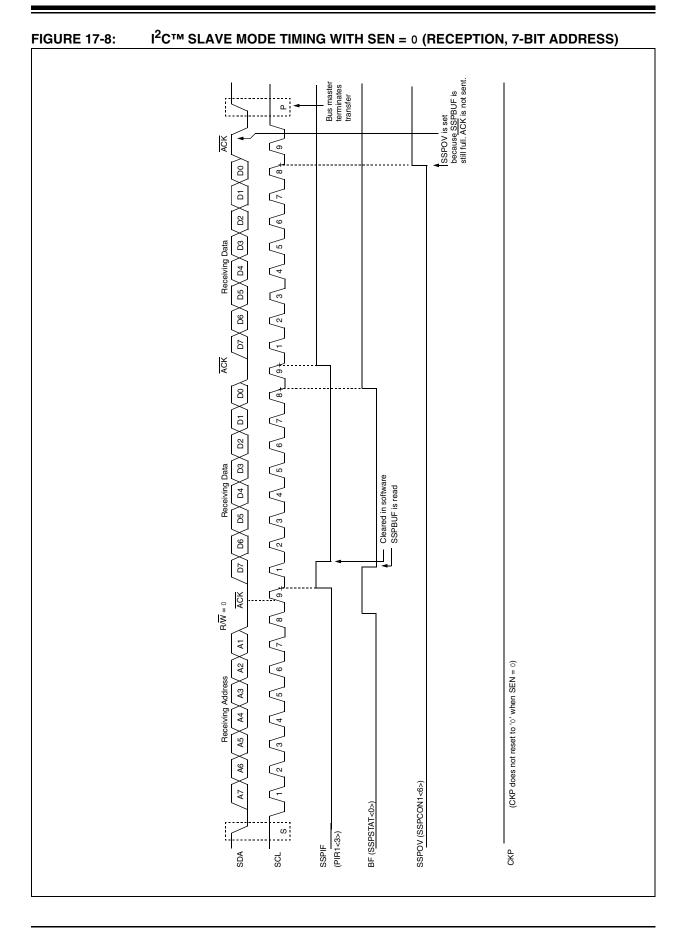

#### 17.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 17.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

#### 17.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit BF is set.

- 3. An ACK pulse is generated.

- MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated if enabled) on the falling edge of the ninth SCL pulse.

In 10-bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and bit UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit UA.

- 6. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (bits SSPIF and BF are set).

- 9. Read the SSPBUF register (clears bit BF) and clear flag bit SSPIF.

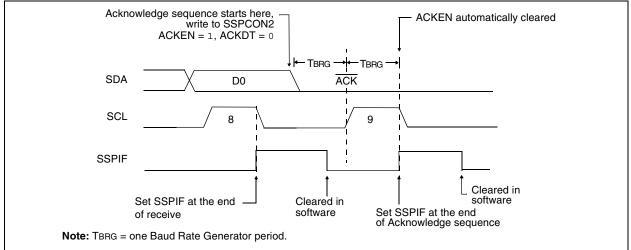

#### 17.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 17-23).

#### 17.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

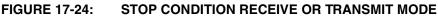

#### 17.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 17-24).

#### 17.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 17-23: ACKNOWLEDGE SEQUENCE WAVEFORM

NOTES:

#### REGISTER 19-2: CANSTAT: CAN STATUS REGISTER

|   | R-1     | R-0     | R-0     | U-0 | R-0    | R-0    | R-0    | U-0   |

|---|---------|---------|---------|-----|--------|--------|--------|-------|

|   | OPMODE2 | OPMODE1 | OPMODE0 |     | ICODE2 | ICODE1 | ICODE0 | _     |

| - | bit 7   |         |         |     |        |        |        | bit 0 |

bit 7-5

#### 5 **OPMODE2:OPMODE0:** Operation Mode Status bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = Configuration mode

- 011 = Listen Only mode

- 010 = Loopback mode

- 001 = Disable mode

- 000 = Normal mode

Note: Before the device goes into Sleep mode, select Disable mode.

#### bit 4 Unimplemented: Read as '0'

#### bit 3-1 ICODE2:ICODE0: Interrupt Code bits

When an interrupt occurs, a prioritized coded interrupt value will be present in the ICODE2:ICODE0 bits. These codes indicate the source of the interrupt. The ICODE2:ICODE0 bits can be copied to the WIN2:WIN0 bits to select the correct buffer to map into the Access Bank area. See Example 19-1 for code example.

- 111 = Wake-up on interrupt

- 110 = RXB0 interrupt

- 101 = RXB1 interrupt

- 100 = TXB0 interrupt

- 011 = TXB1 interrupt

- 010 = TXB2 interrupt

- 001 = Error interrupt

- 000 = No interrupt

- bit 0

Unimplemented: Read as '0'

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| ГER 19-3: | COMSTAT: C                                     | OMMUNI       | CATION S     | STATUS R     | EGISTER  |               |              |             |

|-----------|------------------------------------------------|--------------|--------------|--------------|----------|---------------|--------------|-------------|

|           | R/C-0                                          | R/C-0        | R-0          | R-0          | R-0      | R-0           | R-0          | R-0         |

|           | RXB0OVFL RX                                    | (B1OVFL      | ТХВО         | TXBP         | RXBP     | TXWARN        | RXWARN       | EWARN       |

|           | bit 7                                          |              |              |              |          |               |              | bit 0       |

|           |                                                |              |              |              |          |               |              |             |

| bit 7     | RXB0OVFL: Re                                   | eceive Buffe | er 0 Overflo | ow bit       |          |               |              |             |

|           | 1 = Receive But<br>0 = Receive But             |              |              | ved          |          |               |              |             |

| bit 6     | RXB1OVFL: Re                                   | eceive Buffe | er 1 Overflo | ow bit       |          |               |              |             |

|           | 1 = Receive But<br>0 = Receive But             |              |              | red          |          |               |              |             |

| bit 5     | TXBO: Transmi                                  | tter Bus-Of  | f bit        |              |          |               |              |             |

|           | 1 = Transmit Er<br>0 = Transmit Er             |              |              |              |          |               |              |             |

| bit 4     | TXBP: Transmit                                 | tter Bus Pa  | ssive bit    |              |          |               |              |             |

|           | 1 = Transmissio<br>0 = Transmissio             |              |              |              |          |               |              |             |

| bit 3     | RXBP: Receive                                  | r Bus Pass   | ive bit      |              |          |               |              |             |

|           | 1 = Receive Err<br>0 = Receive Err             |              |              |              |          |               |              |             |

| bit 2     | TXWARN: Tran                                   | smitter Wa   | rning bit    |              |          |               |              |             |

|           | $1 = 127 \ge Trans$<br>0 = Transmit Er         |              |              | 5            |          |               |              |             |

| bit 1     | RXWARN: Rec                                    | eiver Warni  | ng bit       |              |          |               |              |             |

|           | $1 = 127 \ge \text{Receit}$<br>0 = Receive Err |              |              | 5            |          |               |              |             |

| bit 0     | EWARN: Error                                   | Warning bit  |              |              |          |               |              |             |

|           | This bit is a flag                             | of the RXV   | VARN and     | TXWARN b     | its.     |               |              |             |

|           | 1 = The RXWA<br>0 = Neither the                |              |              |              | e set    |               |              |             |

|           | Legend:                                        |              |              |              |          |               |              |             |

|           | R = Readable bi                                | it W = V     | Vritable bit | C = Cleara   | able bit | U = Unimple   | emented bit, | read as '0' |

|           | -n = Value at PC                               | )R '1' = E   | lit is set   | '0' = Bit is | cleared  | x = Bit is un | known        |             |

## REGISTER 19-3: COMSTAT: COMMUNICATION STATUS REGISTER

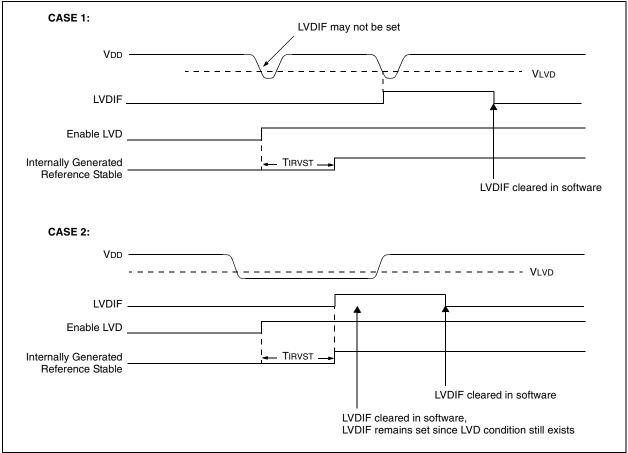

#### 23.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- Write the value to the LVDL3:LVDL0 bits (LVDCON register) which selects the desired LVD trip point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- 5. Clear the LVD interrupt flag, which may have falsely become set, until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 23-4 shows typical waveforms that the LVD module may be used to detect.

## FIGURE 23-4: LOW-VOLTAGE DETECT WAVEFORMS

NOTES:

#### TABLE 25-2: PIC18FXXX INSTRUCTION SET

| Mnemo   | onic,                           | Description                           | Cycles     | 16-E | Bit Instr    | uction W | /ord | Status           | Notes      |

|---------|---------------------------------|---------------------------------------|------------|------|--------------|----------|------|------------------|------------|

| Opera   | nds                             | Description                           | Cycles     | MSb  |              |          | LSb  | Affected         | notes      |

| BYTE-OR | IENTED                          | FILE REGISTER OPERATIONS              | 6          |      |              |          |      |                  |            |

| ADDWF   | f, d, a                         | Add WREG and f                        | 1          | 0010 | 01da         | ffff     | ffff | C, DC, Z, OV, N  |            |

| ADDWFC  | f, d, a                         | Add WREG and Carry bit to f           | 1          | 0010 | 00da         | ffff     | ffff | C, DC, Z, OV, N  | 1, 2       |

| ANDWF   | f, d, a                         | AND WREG with f                       | 1          | 0001 | 01da         | ffff     | ffff | Z, N             | 1,2        |

| CLRF    | f, a                            | Clear f                               | 1          | 0110 | 101a         | ffff     | ffff | Z                | 2          |

| COMF    | f, d, a                         | Complement f                          | 1          | 0001 | 11da         | ffff     | ffff | Z, N             | 1, 2       |

| CPFSEQ  | f, a                            | Compare f with WREG, skip =           | 1 (2 or 3) | 0110 | 001a         | ffff     | ffff | None             | 4          |

| CPFSGT  | f, a                            | Compare f with WREG, skip >           | 1 (2 or 3) | 0110 | 010a         | ffff     | ffff | None             | 4          |

| CPFSLT  | f, a                            | Compare f with WREG, skip <           | 1 (2 or 3) | 0110 | 000a         | ffff     | ffff | None             | 1, 2       |

| DECF    | f, d, a                         | Decrement f                           | 1 .        | 0000 | 01da         | ffff     | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| DECFSZ  | f, d, a                         | Decrement f, Skip if 0                | 1 (2 or 3) | 0010 | 11da         | ffff     | ffff | None             | 1, 2, 3, 4 |

| DCFSNZ  | f, d, a                         | Decrement f, Skip if Not 0            | 1 (2 or 3) |      | 11da         | ffff     | ffff | None             | 1, 2       |

| INCF    | f, d, a                         | Increment f                           | 1 ΄        | 0010 | 10da         | ffff     | ffff | C, DC, Z, OV, N  | 1, 2, 3, 4 |

| INCFSZ  |                                 | Increment f, Skip if 0                | 1 (2 or 3) |      | 11da         | ffff     | ffff | None             | 4          |

| INFSNZ  | f, d, a                         | Increment f, Skip if Not 0            | 1 (2 or 3) |      | 10da         | ffff     | ffff | None             | 1, 2       |

| IORWF   | f, d, a                         | Inclusive OR WREG with f              | 1          |      | 00da         | ffff     | ffff |                  | 1, 2       |

| MOVF    | f, d, a                         | Move f                                | 1          |      | 00da         | ffff     |      | Z, N             | 1          |

| MOVFF   | f <sub>s</sub> , f <sub>d</sub> |                                       | 2          |      | ffff         | ffff     |      | None             | •          |

| movi i  | 's, 'a                          | f <sub>d</sub> (destination) 2nd word | -          |      | ffff         | ffff     | ffff |                  |            |

| MOVWF   | f, a                            | Move WREG to f                        | 1          |      | 111a         | ffff     | ffff | None             |            |

| MULWF   | f, a                            | Multiply WREG with f                  | 1          |      | 001a         | ffff     |      | None             |            |

| NEGF    | f, a                            | Negate f                              | 1          |      | 110a         | ffff     | ffff | C, DC, Z, OV, N  | 12         |

| RLCF    | f, d, a                         | Rotate Left f through Carry           | 1          |      | 01da         | ffff     | ffff | C, Z, N          | 1, 2       |

| RLNCF   |                                 | Rotate Left f (No Carry)              | 1          |      | 01da<br>01da | ffff     | ffff |                  | 1, 2       |

| RRCF    | f, d, a                         | Rotate Right f through Carry          | 1          |      | 01da<br>00da | ffff     | ffff | C, Z, N          | 1, 2       |

| RRNCF   | f, d, a                         | Rotate Right f (No Carry)             | 1          |      | 00da<br>00da | ffff     | ffff |                  |            |

| SETF    | f, a                            | Set f                                 | 1          |      | 100a         | ffff     |      | None             |            |

| SUBFWB  |                                 | Subtract f from WREG with             | 1          |      |              | ffff     | ffff | C, DC, Z, OV, N  | 1 0        |

| SUBEWB  | f, d, a                         | borrow                                | 1          | 0101 | 01da         | LLLL     | LLLL | C, DC, Z, OV, N  | 1, 2       |

| SUBWF   | f, d, a                         | Subtract WREG from f                  | 1          | 0101 | 11da         | ffff     | ffff | C, DC, Z, OV, N  |            |

|         | f, d, a                         | Subtract WREG from f with             | 1          |      | 10da         | ffff     | ffff | C, DC, Z, OV, N  | 12         |

| 0001110 | i, a, a                         | borrow                                |            | 0101 | Toda         |          |      | 0, 20, 2, 01, 11 | •, –       |

| SWAPF   | f, d, a                         | Swap nibbles in f                     | 1          | 0011 | 10da         | ffff     | ffff | None             | 4          |

| TSTFSZ  | f, a                            | Test f, skip if 0                     | 1 (2 or 3) |      | 100a<br>011a | ffff     |      | None             | 4<br>1, 2  |

| XORWF   | f, d, a                         | Exclusive OR WREG with f              | 1          |      | 10da         | ffff     |      | Z, N             | 1, 2       |

| -       |                                 |                                       | 1          | 0001 | IUda         | LLLL     | LLLL | Ζ, Ν             |            |

|         |                                 |                                       | 4          | 1005 |              |          |      | Nere             | 1.0        |

| BCF     | f, b, a                         | Bit Clear f                           | 1          |      | bbba         | ffff     | ffff | None             | 1,2        |

| BSF     | , .,                            | Bit Set f                             | 1          |      | bbba         | ffff     | ffff | None             | 1,2        |

| BTFSC   |                                 | Bit Test f, Skip if Clear             | 1 (2 or 3) |      | bbba         | ffff     |      | None             | 3, 4       |

| BTFSS   |                                 | Bit Test f, Skip if Set               | 1 (2 or 3) |      | bbba         | ffff     | ffff | None             | 3, 4       |

| BTG     | f, d, a                         | Bit Toggle f                          | 1          | 0111 | bbba         | ffff     | ffff | None             | 1, 2       |

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| Mnemo   | onic, | Description                    | Cycles | 16-E | Bit Instr | uction V | Vord | Status    | Notes |

|---------|-------|--------------------------------|--------|------|-----------|----------|------|-----------|-------|

| Opera   | nds   | Description                    | Cycles | MSb  |           |          | LSb  | Affected  | Notes |

| CONTROL | OPER  | ATIONS                         |        |      |           |          |      |           |       |

| BC      | n     | Branch if Carry                | 1 (2)  | 1110 | 0010      | nnnn     | nnnn | None      |       |

| BN      | n     | Branch if Negative             | 1 (2)  | 1110 | 0110      | nnnn     | nnnn | None      |       |

| BNC     | n     | Branch if Not Carry            | 1 (2)  | 1110 | 0011      | nnnn     | nnnn | None      |       |

| BNN     | n     | Branch if Not Negative         | 1 (2)  | 1110 | 0111      | nnnn     | nnnn | None      |       |

| BNOV    | n     | Branch if Not Overflow         | 1 (2)  | 1110 | 0101      | nnnn     | nnnn | None      |       |

| BNZ     | n     | Branch if Not Zero             | 2      | 1110 | 0001      | nnnn     | nnnn | None      |       |

| BOV     | n     | Branch if Overflow             | 1 (2)  | 1110 | 0100      | nnnn     | nnnn | None      |       |

| BRA     | n     | Branch Unconditionally         | 1 (2)  | 1101 | 0nnn      | nnnn     | nnnn | None      |       |

| BZ      | n     | Branch if Zero                 | 1 (2)  | 1110 | 0000      | nnnn     | nnnn | None      |       |

| CALL    | n, s  | Call subroutine1st word        | 2      | 1110 | 110s      | kkkk     | kkkk | None      |       |

|         |       | 2nd word                       |        | 1111 | kkkk      | kkkk     | kkkk |           |       |

| CLRWDT  |       | Clear Watchdog Timer           | 1      | 0000 | 0000      | 0000     | 0100 | TO, PD    |       |

| DAW     | —     | Decimal Adjust WREG            | 1      | 0000 | 0000      | 0000     | 0111 | С         |       |

| GOTO    | n     | Go to address 1st word         | 2      | 1110 | 1111      | kkkk     | kkkk | None      |       |

|         |       | 2nd word                       |        | 1111 | kkkk      | kkkk     | kkkk |           |       |

| NOP     | —     | No Operation                   | 1      | 0000 | 0000      | 0000     | 0000 | None      |       |

| NOP     | —     | No Operation                   | 1      | 1111 | xxxx      | xxxx     | xxxx | None      | 4     |

| POP     |       | Pop top of return stack (TOS)  | 1      | 0000 | 0000      | 0000     | 0110 | None      |       |

| PUSH    | —     | Push top of return stack (TOS) | 1      | 0000 | 0000      | 0000     | 0101 | None      |       |

| RCALL   | n     | Relative Call                  | 2      | 1101 | 1nnn      | nnnn     | nnnn | None      |       |

| RESET   |       | Software device Reset          | 1      | 0000 | 0000      | 1111     | 1111 | All       |       |

| RETFIE  | S     | Return from interrupt enable   | 2      | 0000 | 0000      | 0001     | 000s | GIE/GIEH, |       |

|         |       |                                |        |      |           |          |      | PEIE/GIEL |       |

| RETLW   | k     | Return with literal in WREG    | 2      | 0000 | 1100      | kkkk     | kkkk | None      |       |

| RETURN  | S     | Return from Subroutine         | 2      | 0000 | 0000      | 0001     | 001s | None      |       |

| SLEEP   |       | Go into Standby mode           | 1      | 0000 | 0000      | 0000     | 0011 | TO, PD    |       |

#### TABLE 25-2: PIC18FXXX INSTRUCTION SET (CONTINUED)

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| SLEEP Enter Sleep                             |                     |                                        | ep Mode        |                                  | SUBFWB                    | Subtract f from W with Borrow                                                                                                                                           |                                                                                                                                                                  |                      |  |  |  |

|-----------------------------------------------|---------------------|----------------------------------------|----------------|----------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Syntax:                                       |                     | [ label ]                              | SLEEP          |                                  | Syntax:                   | [ <i>label</i> ] SUBFWB f [,d [,a]]                                                                                                                                     |                                                                                                                                                                  |                      |  |  |  |

| Operands: None                                |                     |                                        | Operands:      |                                  |                           |                                                                                                                                                                         |                                                                                                                                                                  |                      |  |  |  |

| Operation:                                    |                     | $00h \rightarrow WI$                   |                |                                  |                           | $d \in [0,1]$                                                                                                                                                           |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        | postscaler,    |                                  | Oneration                 |                                                                                                                                                                         | $a \in [0,1]$<br>(W) – (f) – ( $\overline{C}$ ) $\rightarrow$ dest                                                                                               |                      |  |  |  |

|                                               |                     | $1 \rightarrow TO, 0 \rightarrow PD$   |                |                                  | Operation:                |                                                                                                                                                                         |                                                                                                                                                                  |                      |  |  |  |

| Status Affected:                              |                     | TO, PD                                 |                |                                  | Status Affected:          |                                                                                                                                                                         | N, OV, C, DC, Z                                                                                                                                                  |                      |  |  |  |

| Encoding:                                     |                     | 0000 0000 0000 0011                    |                |                                  | Encoding:                 | 0101                                                                                                                                                                    |                                                                                                                                                                  | ff ffff              |  |  |  |

| Description:                                  |                     | The Powe<br>cleared. T                 | r-Down status  | s bit (PD) is<br>status bit (TO) | Description:              | Subtract register 'f' and Carry flag<br>(borrow) from W (2's complement<br>method). If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored in |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     | postscaler<br>The proce<br>with the os | are cleared.   | o Sleep mode                     |                           | register 'f<br>Access B<br>overriding                                                                                                                                   | register 'f' (default). If 'a' is '0', the<br>Access Bank will be selected,<br>overriding the BSR value. If 'a' is '1',<br>then the bank will be selected as per |                      |  |  |  |

| Word                                          |                     | 1                                      |                |                                  |                           |                                                                                                                                                                         | value (default)                                                                                                                                                  |                      |  |  |  |

| Cycle                                         |                     | 1                                      |                |                                  | Words:                    | 1                                                                                                                                                                       |                                                                                                                                                                  |                      |  |  |  |

| QC                                            | ycle Activity:      | Q2                                     | Q3             | Q4                               | Cycles:                   | 1                                                                                                                                                                       |                                                                                                                                                                  |                      |  |  |  |

|                                               | Q1<br>Decode        | No                                     | Process        | Go to                            | Q Cycle Activity:         |                                                                                                                                                                         |                                                                                                                                                                  |                      |  |  |  |

|                                               | 200000              | operation                              | Data           | Sleep                            | Q1                        | Q2                                                                                                                                                                      | Q3                                                                                                                                                               | Q4                   |  |  |  |

| Exan                                          | nple:               | SLEEP                                  |                |                                  | Decode                    | Read<br>register 'f'                                                                                                                                                    | Process<br>Data                                                                                                                                                  | Write to destination |  |  |  |

|                                               | Before Instruc      |                                        |                |                                  | Example 1:                | SUBFWB                                                                                                                                                                  | REG                                                                                                                                                              |                      |  |  |  |

|                                               | TO =                | ?                                      |                |                                  | Before Instruc            | Before Instruction                                                                                                                                                      |                                                                                                                                                                  |                      |  |  |  |

| PD = ?<br>After Instruction<br>TO = 1 †       |                     |                                        |                |                                  | REG<br>W<br>C             | = 0x03<br>= 0x02<br>= 0x01                                                                                                                                              | 0x02                                                                                                                                                             |                      |  |  |  |

|                                               | $\frac{10}{PD} = 0$ |                                        |                | After Instructi<br>REG           | on<br>= 0xFF              |                                                                                                                                                                         |                                                                                                                                                                  |                      |  |  |  |

| † If WDT causes wake-up, this bit is cleared. |                     |                                        |                |                                  | W<br>C<br>Z               | = 0x02<br>= 0x00<br>= 0x00                                                                                                                                              |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        |                |                                  | Ν                         | = 0x01                                                                                                                                                                  | ; result is neo                                                                                                                                                  | gative               |  |  |  |

|                                               |                     |                                        |                |                                  | Example 2:                | SUBFWB                                                                                                                                                                  | REG, 0,                                                                                                                                                          | 0                    |  |  |  |

|                                               |                     |                                        |                |                                  | Before Instruc<br>REG     | ction<br>= 2                                                                                                                                                            |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        |                |                                  | W<br>C<br>After Instructi | = 5<br>= 1                                                                                                                                                              |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        |                |                                  | REG<br>W                  | = 2<br>= 3                                                                                                                                                              |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        |                |                                  | C<br>Z<br>N               | = 1 = 0 = 0                                                                                                                                                             | ; result is pos                                                                                                                                                  | itive                |  |  |  |

|                                               |                     |                                        |                |                                  | Example 3:                | SUBFWB                                                                                                                                                                  | REG, 1,                                                                                                                                                          | 0                    |  |  |  |

|                                               |                     |                                        | Before Instruc | ction                            |                           |                                                                                                                                                                         |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        |                |                                  | REG<br>W<br>C             | = 1<br>= 2<br>= 0                                                                                                                                                       |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        |                |                                  | After Instructi           | on                                                                                                                                                                      |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        |                |                                  | REG<br>W                  | = 0<br>= 2                                                                                                                                                              |                                                                                                                                                                  |                      |  |  |  |

|                                               |                     |                                        |                |                                  | C<br>Z<br>N               | = 1<br>= 1                                                                                                                                                              | ; result is zero                                                                                                                                                 | 0                    |  |  |  |

|                                               |                     |                                        |                |                                  | IN                        | = 0                                                                                                                                                                     |                                                                                                                                                                  |                      |  |  |  |

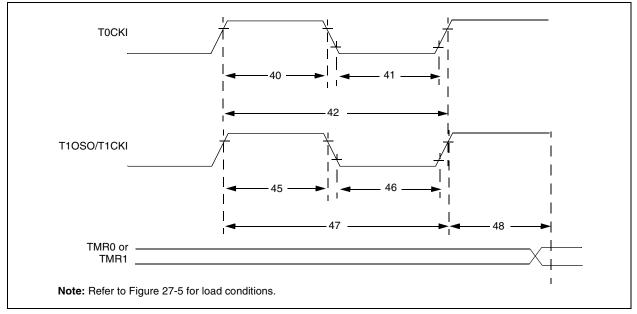

#### FIGURE 27-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| Param<br>No. | Symbol    |                                       | Characteristic              | C                   | Min                                          | Max | Units | Conditions                            |

|--------------|-----------|---------------------------------------|-----------------------------|---------------------|----------------------------------------------|-----|-------|---------------------------------------|

| 40           | Tt0H      | T0CKI High I                          | Pulse Width                 | No prescaler        | 0.5 TCY + 20                                 | _   | ns    |                                       |

|              |           |                                       |                             | With prescaler      | 10                                           | _   | ns    |                                       |

| 41           | Tt0L      | T0CKI Low Pulse Width                 |                             | No prescaler        | 0.5 TCY + 20                                 | _   | ns    |                                       |

|              |           |                                       |                             | With prescaler      | 10                                           | _   | ns    |                                       |

| 42           | Tt0P      | T0CKI Period                          |                             | No prescaler        | Tcy + 10                                     | _   | ns    |                                       |

|              |           |                                       |                             | With prescaler      | Greater of:<br>20 ns or <u>TCY + 40</u><br>N | _   | ns    | N = prescale value<br>(1, 2, 4,, 256) |

| 45           | Tt1H      | T1CKI<br>High Time                    | Synchronous, no prescaler   |                     | 0.5 TCY + 20                                 | _   | ns    |                                       |

|              |           |                                       | Synchronous, with prescaler | PIC18FXX8           | 10                                           | _   | ns    |                                       |

|              |           |                                       |                             | PIC18 <b>LF</b> XX8 | 25                                           | _   | ns    |                                       |

|              |           |                                       | Asynchronous                | PIC18 <b>F</b> XX8  | 30                                           | _   | ns    |                                       |

|              |           |                                       |                             | PIC18 <b>LF</b> XX8 | 50                                           | —   | ns    |                                       |

| 46           | Tt1L      | T1CKI<br>Low Time                     | Synchronous, no prescaler   |                     | 0.5 TCY + 5                                  | _   | ns    |                                       |

|              |           |                                       | Synchronous, with prescaler | PIC18 <b>F</b> XX8  | 10                                           | —   | ns    |                                       |

|              |           |                                       |                             | PIC18 <b>LF</b> XX8 | 25                                           | —   | ns    |                                       |

|              |           |                                       | Asynchronous                | PIC18 <b>F</b> XX8  | 30                                           | —   | ns    |                                       |

|              |           |                                       |                             | PIC18 <b>LF</b> XX8 | TBD                                          | TBD | ns    |                                       |

| 47           | Tt1P      | T1CKI<br>Input Period<br>Asynchronous |                             |                     | Greater of:<br>20 ns or <u>TCY + 40</u><br>N | _   | ns    | N = prescale value<br>(1, 2, 4, 8)    |

|              |           |                                       |                             |                     | 60                                           | _   | ns    |                                       |

|              | Ft1       | T1CKI Oscill                          | ator Input Frequ            | DC                  | 50                                           | kHz |       |                                       |

| 48           | Tcke2tmrl | Delay from E<br>Timer Increm          | xternal T1CKI C<br>nent     | 2 Tosc              | 7 Tosc                                       | _   |       |                                       |

**Legend:** TBD = To Be Determined

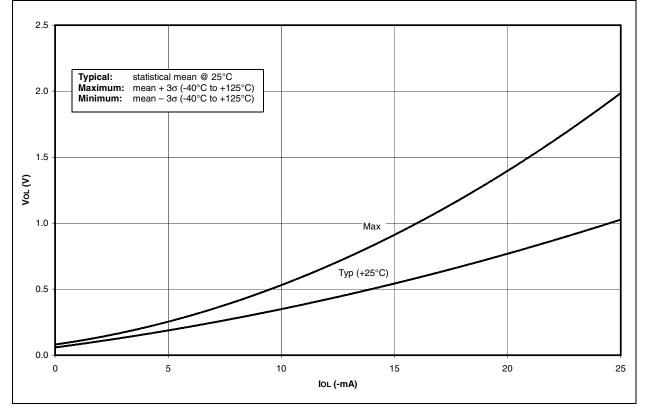

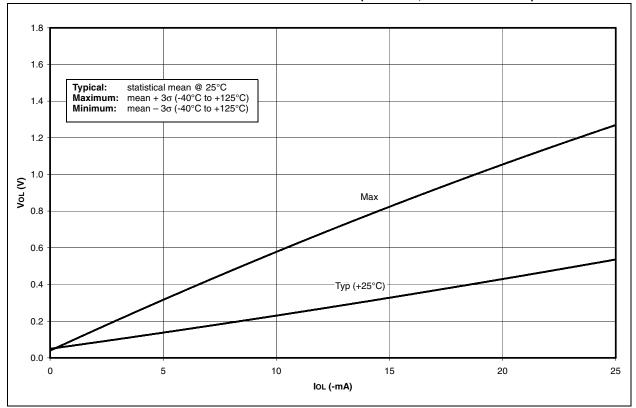

#### FIGURE 28-23: TYPICAL AND MAXIMUM Vol vs. lol (VDD = 5V, -40°C TO +125°C)