#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf448-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.7 Time-out Sequence

On power-up, the time-out sequence is as follows: First, PWRT time-out is invoked after the POR time delay has expired, then OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 3-3, Figure 3-4, Figure 3-5, Figure 3-6 and Figure 3-7 depict time-out sequences on power-up. Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Bringing MCLR high will begin execution immediately (Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC18FXX8 device operating in parallel.

Table 3-2 shows the Reset conditions for some Special Function Registers, while Table 3-3 shows the Reset conditions for all registers.

#### TABLE 3-1: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator                         | Power-up                 | (2)               | 5 (2)                    | Wake-up from                  |  |

|------------------------------------|--------------------------|-------------------|--------------------------|-------------------------------|--|

| Configuration                      | <b>PWRTEN</b> = 0        | <b>PWRTEN</b> = 1 | Brown-out <sup>(2)</sup> | Sleep or<br>Oscillator Switch |  |

| HS with PLL enabled <sup>(1)</sup> | 72 ms + 1024 Tosc + 2 ms | 1024 Tosc + 2 ms  | 72 ms + 1024 Tosc + 2 ms | 1024 Tosc + 2 ms              |  |

| HS, XT, LP                         | 72 ms + 1024 Tosc        | 1024 Tosc         | 72 ms + 1024 Tosc        | 1024 Tosc                     |  |

| EC                                 | 72 ms                    | —                 | 72 ms                    | —                             |  |

| External RC                        | 72 ms                    |                   | 72 ms                    | _                             |  |

**Note 1:** 2 ms = Nominal time required for the 4x PLL to lock.

**2:** 72 ms is the nominal Power-up Timer delay.

#### REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

| R/W-0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| IPEN  | —   | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |     |     |       |       |       |       | bit 0 |

### TABLE 3-2:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                     | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | BOR | STKFUL | STKUNF |

|-----------------------------------------------|-----------------------|------------------|----|----|----|-----|-----|--------|--------|

| Power-on Reset                                | 0000h                 | 01 110q          | 1  | 1  | 1  | 0   | 0   | u      | u      |

| MCLR Reset during normal operation            | 0000h                 | 00 011q          | u  | u  | u  | u   | u   | u      | u      |

| Software Reset during normal operation        | 0000h                 | 00 011q          | 0  | u  | u  | u   | u   | u      | u      |

| Stack Full Reset during normal operation      | 0000h                 | 00 011q          | u  | u  | u  | 1   | 1   | u      | 1      |

| Stack Underflow Reset during normal operation | 0000h                 | 00 011q          | u  | u  | u  | 1   | 1   | 1      | u      |

| MCLR Reset during Sleep                       | 0000h                 | 00 011q          | u  | 1  | 0  | u   | u   | u      | u      |

| WDT Reset                                     | 0000h                 | 00 011q          | u  | 0  | 1  | u   | u   | u      | u      |

| WDT Wake-up                                   | PC + 2                | 01 101q          | u  | 0  | 0  | u   | u   | u      | u      |

| Brown-out Reset                               | 0000h                 | 01 110q          | 1  | 1  | 1  | u   | 0   | u      | u      |

| Interrupt wake-up from Sleep                  | PC + 2 <sup>(1)</sup> | 01 101q          | u  | 1  | 0  | u   | u   | u      | u      |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (000008h or 000018h).

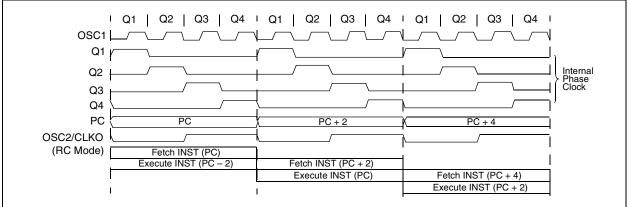

#### 4.5 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the Program Counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 4-4.

### 4.6 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), two cycles are required to complete the instruction (Example 4-2).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### 4.7 Instructions in Program Memory

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB = 0). Figure 4-3 shows an example of how instruction words are stored in the program memory. To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 4.4 "PCL, PCLATH and PCLATU").

The CALL and GOTO instructions have an absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Example 4-3 shows how the instruction "GOTO 00006h" is encoded in the program memory. Program branch instructions that encode a relative address offset operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions by which the PC will be offset. Section 25.0 "Instruction Set Summary" provides further details of the instruction set.

| <b>REGISTER 8-2:</b> | INTCON2: INTERRUPT CONTROL REGISTER 2 |                                                                              |                 |              |               |           |              |        |  |  |  |  |

|----------------------|---------------------------------------|------------------------------------------------------------------------------|-----------------|--------------|---------------|-----------|--------------|--------|--|--|--|--|

|                      | R/W-1                                 | R/W-1                                                                        | R/W-1           | U-0          | U-0           | R/W-1     | U-0          | R/W-1  |  |  |  |  |

|                      | RBPU                                  | INTEDG0                                                                      | INTEDG1         | _            | _             | TMR0IP    |              | RBIP   |  |  |  |  |

|                      | bit 7                                 |                                                                              |                 |              |               |           |              | bit 0  |  |  |  |  |

|                      |                                       |                                                                              |                 |              |               |           |              |        |  |  |  |  |

| bit 7                | RBPU: PO                              | RTB Pull-up                                                                  | Enable bit      |              |               |           |              |        |  |  |  |  |

|                      |                                       | RTB pull-ups<br>3 pull-ups are                                               |                 |              | oort latch va | lues      |              |        |  |  |  |  |

| bit 6                | INTEDG0:                              | External Inte                                                                | errupt 0 Edg    | e Select bit |               |           |              |        |  |  |  |  |

|                      |                                       | ot on rising e                                                               | 0               |              |               |           |              |        |  |  |  |  |

|                      |                                       | ot on falling e                                                              | •               |              |               |           |              |        |  |  |  |  |

| bit 5                |                                       | NTEDG1: External Interrupt 1 Edge Select bit<br>_ = Interrupt on rising edge |                 |              |               |           |              |        |  |  |  |  |

|                      |                                       | ot on rising e<br>ot on falling e                                            | •               |              |               |           |              |        |  |  |  |  |

| bit 4-3              |                                       | ented: Read                                                                  | •               |              |               |           |              |        |  |  |  |  |

| bit 2                | -                                     | MR0 Overflo                                                                  |                 | Priority bit |               |           |              |        |  |  |  |  |

|                      | 1 = High pi                           |                                                                              |                 |              |               |           |              |        |  |  |  |  |

|                      | 0 = Low pr                            | •                                                                            |                 |              |               |           |              |        |  |  |  |  |

| bit 1                | Unimplem                              | ented: Read                                                                  | <b>d as</b> '0' |              |               |           |              |        |  |  |  |  |

| bit 0                | RBIP: RB                              | Port Change                                                                  | Interrupt Pr    | iority bit   |               |           |              |        |  |  |  |  |

|                      | 1 = High p                            | •                                                                            |                 |              |               |           |              |        |  |  |  |  |

|                      | 0 = Low pr                            | riority                                                                      |                 |              |               |           |              |        |  |  |  |  |

|                      |                                       |                                                                              |                 |              |               |           |              |        |  |  |  |  |

|                      | Legend:                               |                                                                              |                 |              |               |           |              |        |  |  |  |  |

|                      | R = Reada                             | ble bit                                                                      | W = W           | ritable bit  | U = Unin      | plemented | bit, read as | ʻ0'    |  |  |  |  |

|                      | -n = Value                            | at POR                                                                       | '1' = B         | it is set    | '0' = Bit i   | s cleared | x = Bit is u | nknown |  |  |  |  |

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows software polling.

#### SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C MODE) REGISTER 17-3: R/W-0 R-0 R/W-0 R-0 R-0 R-0 R-0 R-0 SMP CKE D/A Ρ S R/W UA ΒF bit 7 bit 0 bit 7 SMP: Slew Rate Control bit In Master or Slave mode: 1 = Slew rate control disabled for Standard Speed mode (100 kHz and 1 MHz) 0 = Slew rate control enabled for High-Speed mode (400 kHz) bit 6 CKE: SMBus Select bit In Master or Slave mode: 1 = Enable SMBus specific inputs 0 = Disable SMBus specific inputs D/A: Data/Address bit bit 5 In Master mode: Reserved. In Slave mode: 1 = Indicates that the last byte received or transmitted was data 0 = Indicates that the last byte received or transmitted was address bit 4 P: Stop bit 1 = Indicates that a Stop bit has been detected last 0 = Stop bit was not detected last This bit is cleared on Reset and when SSPEN is cleared. Note: bit 3 S: Start bit 1 = Indicates that a Start bit has been detected last 0 = Start bit was not detected last Note: This bit is cleared on Reset and when SSPEN is cleared. R/W: Read/Write Information bit (I<sup>2</sup>C mode only) bit 2 In Slave mode: 1 = Read0 = Write Note: This bit holds the R/W bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit or not ACK bit. In Master mode: 1 = Transmit is in progress 0 = Transmit is not in progress ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSP is Note: in Idle mode. bit 1 **UA:** Update Address bit (10-bit Slave mode only) 1 = Indicates that the user needs to update the address in the SSPADD register 0 = Address does not need to be updated bit 0 BF: Buffer Full Status bit In Transmit mode: 1 = Receive complete, SSPBUF is full 0 = Receive not complete, SSPBUF is empty In Receive mode: 1 = Data transmit in progress (does not include the ACK and Stop bits), SSPBUF is full 0 = Data transmit complete (does not include the ACK and Stop bits), SSPBUF is empty I egend:

| Legena:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### 17.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition, or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz I<sup>2</sup>C operation. See **Section 17.4.7 "Baud Rate Generator**" for more details.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. Address is shifted out the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out the SDA pin until all 8 bits are transmitted.

- 9. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit PEN (SSPCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

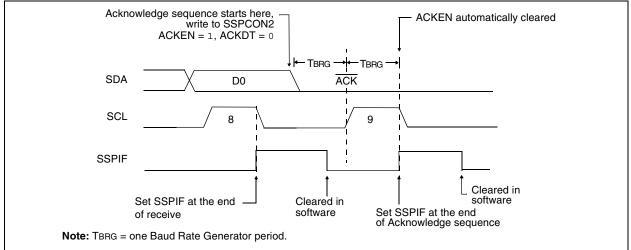

#### 17.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 17-23).

#### 17.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

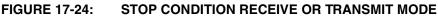

#### 17.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 17-24).

#### 17.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 17-23: ACKNOWLEDGE SEQUENCE WAVEFORM

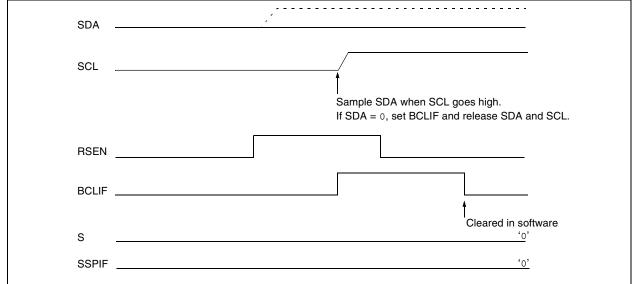

### 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 17-29). If SDA is sampled high, the BRG is reloaded and begins

counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

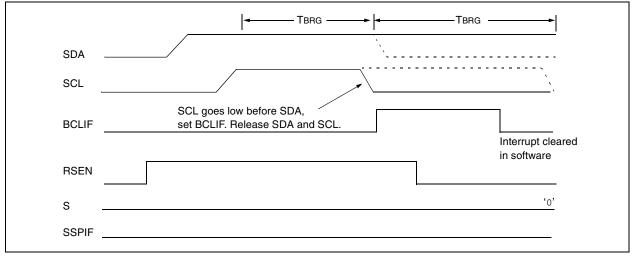

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (Figure 17-30).

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 17-30: BUS COLLISION DURING A REPEATED START CONDITION (CASE 2)

| TABLE          | : 18-3: | BAUL       | RATES              | FURS   | INCHR      |                    | NODE    |            |                    |         |            |                    |

|----------------|---------|------------|--------------------|--------|------------|--------------------|---------|------------|--------------------|---------|------------|--------------------|

| BAUD<br>RATE   | Fosc =  | 40 MHz     | SPBRG<br>value     | 33     | MHz        | SPBRG<br>value     | 25      | MHz        | SPBRG<br>value     | 20      | MHz        | SPBRG<br>value     |

| (Kbps)         | KBAUD   | %<br>ERROR | (decimal)          | KBAUD  | %<br>ERROR | (decimal)          | KBAUD   | %<br>ERROR | (decimal)          | KBAUD   | %<br>ERROR | (decimal)          |

| 0.3            | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 1.2            | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 2.4            | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 9.6            | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 19.2           | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 76.8           | 76.92   | +0.16      | 129                | 77.10  | +0.39      | 106                | 77.16   | +0.47      | 80                 | 76.92   | +0.16      | 64                 |

| 96             | 96.15   | +0.16      | 103                | 95.93  | -0.07      | 85                 | 96.15   | +0.16      | 64                 | 96.15   | +0.16      | 51                 |

| 300            | 303.03  | +1.01      | 32                 | 294.64 | -1.79      | 27                 | 297.62  | -0.79      | 20                 | 294.12  | -1.96      | 16                 |

| 500            | 500     | 0          | 19                 | 485.30 | -2.94      | 16                 | 480.77  | -3.85      | 12                 | 500     | 0          | 9                  |

| HIGH           | 10000   | -          | 0                  | 8250   | -          | 0                  | 6250    | -          | 0                  | 5000    | -          | 0                  |

| LOW            | 39.06   | -          | 255                | 32.23  | -          | 255                | 24.41   | -          | 255                | 19.53   | -          | 255                |

| BAUD           | Fosc =  | 16 MHz     | SPBRG              | 10     | MHz        | SPBRG              | 7.1590  | 9 MHz      | SPBRG              | 5.068   | 8 MHz      | SPBRG              |

| RATE           |         | %          | value              |        | %          | value              |         | %          | value              |         | %          | value              |

| (Kbps)         | KBAUD   | ERROR      | (decimal)          | KBAUD  | ERROR      | (decimal)          | KBAUD   | ERROR      | (decimal)          | KBAUD   | ERROR      | (decimal)          |

| 0.3            | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 1.2            | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 2.4            | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  |

| 9.6            | NA      | -          | -                  | NA     | -          | -                  | 9.62    | +0.23      | 185                | 9.60    | 0          | 131                |

| 19.2           | 19.23   | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24   | +0.23      | 92                 | 19.20   | 0          | 65                 |

| 76.8           | 76.92   | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82   | +1.32      | 22                 | 74.54   | -2.94      | 16                 |

| 96             | 95.24   | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20   | -1.88      | 18                 | 97.48   | +1.54      | 12                 |

| 300            | 307.70  | +2.56      | 12                 | 312.50 | +4.17      | 7                  | 298.35  | -0.57      | 5                  | 316.80  | +5.60      | 3                  |

| 500            | 500     | 0          | 7                  | 500    | 0          | 4                  | 447.44  | -10.51     | 3                  | 422.40  | -15.52     | 2                  |

| HIGH           | 4000    | -          | 0                  | 2500   | -          | 0                  | 1789.80 | -          | 0                  | 1267.20 | -          | 0                  |

| LOW            | 15.63   | -          | 255                | 9.77   | -          | 255                | 6.99    | -          | 255                | 4.95    | -          | 255                |

| BAUD           | Fosc =  | 4 MHz      | SPBRG              | 3.5795 | 45 MHz     | SPBRG              | 1 M     | 1Hz        | SPBRG              | 32.76   | 8 kHz      | SPBRG              |

| RATE<br>(Kbps) |         | %<br>EDDOD | value<br>(decimal) |        | %<br>50000 | value<br>(decimal) | KRAUD   | %<br>50000 | value<br>(decimal) | KRAUD   | %<br>EDBOD | value<br>(decimal) |

|                | KBAUD   | ERROR      |                    | KBAUD  | ERROR      |                    | KBAUD   | ERROR      |                    | KBAUD   | ERROR      |                    |

| 0.3            | NA      | -          | -                  | NA     | -          | -                  | NA      | -          | -                  | 0.30    | +1.14      | 26                 |

| 1.2            | NA      | -          | -                  | NA     | -          | -                  | 1.20    | +0.16      | 207                | 1.17    | -2.48      | 6                  |

| 2.4            | NA      | -          | -                  | NA     | -          | -                  | 2.40    | +0.16      | 103                | 2.73    | +13.78     | 2                  |

| 9.6            | 9.62    | +0.16      | 103                | 9.62   | +0.23      | 92                 | 9.62    | +0.16      | 25                 | 8.20    | -14.67     | 0                  |

| 19.2           | 19.23   | +0.16      | 51                 | 19.04  | -0.83      | 46                 | 19.23   | +0.16      | 12                 | NA      | -          | -                  |

| 76.8           | 76.92   | +0.16      | 12                 | 74.57  | -2.90      | 11                 | 83.33   | +8.51      | 2                  | NA      | -          | -                  |

| 96             | 1000    | +4.17      | 9                  | 99.43  | +3.57      | 8                  | 83.33   | -13.19     | 2                  | NA      | -          | -                  |

| 300            | 333.33  | +11.11     | 2                  | 298.30 | -0.57      | 2                  | 250     | -16.67     | 0                  | NA      | -          | -                  |

| 500            | 500     | 0          | 1                  | 447.44 | -10.51     | 1                  | NA      | -          | -                  | NA      | -          | -                  |

| HIGH           | 1000    | -          | 0                  | 894.89 | -          | 0                  | 250     | -          | 0                  | 8.20    | -          | 0                  |

| LOW            | 3.91    | -          | 255                | 3.50   | -          | 255                | 0.98    | -          | 255                | 0.03    | -          | 255                |

#### TABLE 18-3 BAUD BATES FOR SYNCHRONOUS MODE

| IABLE          | 18-5:  | BAUD       | RAIES F            | OR AS   | INCHR      | ONOUS              | MODE (  | BRGH       | = 1)               |        |            |                    |

|----------------|--------|------------|--------------------|---------|------------|--------------------|---------|------------|--------------------|--------|------------|--------------------|

| BAUD<br>RATE   | Fosc = | 40 MHz     | SPBRG<br>value     | 33      | MHz        | SPBRG<br>value     | 25      | MHz        | SPBRG<br>value     | 20     | MHz        | SPBRG<br>value     |

| (Kbps)         | KBAUD  | %<br>ERROR | (decimal)          | KBAUD   | %<br>ERROR | (decimal)          | KBAUD   | %<br>ERROR | (decimal)          | KBAUD  | %<br>ERROR | (decimal)          |

| 0.3            | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  | NA     | -          | -                  |

| 1.2            | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  | NA     | -          | -                  |

| 2.4            | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  | NA     | -          | -                  |

| 9.6            | NA     | -          | -                  | 9.60    | -0.07      | 214                | 9.59    | -0.15      | 162                | 9.62   | +0.16      | 129                |

| 19.2           | 19.23  | +0.16      | 129                | 19.28   | +0.39      | 106                | 19.30   | +0.47      | 80                 | 19.23  | +0.16      | 64                 |

| 76.8           | 75.76  | -1.36      | 32                 | 76.39   | -0.54      | 26                 | 78.13   | +1.73      | 19                 | 78.13  | +1.73      | 15                 |

| 96             | 96.15  | +0.16      | 25                 | 98.21   | +2.31      | 20                 | 97.66   | +1.73      | 15                 | 96.15  | +0.16      | 12                 |

| 300            | 312.50 | +4.17      | 7                  | 294.64  | -1.79      | 6                  | 312.50  | +4.17      | 4                  | 312.50 | +4.17      | 3                  |

| 500            | 500    | 0          | 4                  | 515.63  | +3.13      | 3                  | 520.83  | +4.17      | 2                  | 416.67 | -16.67     | 2                  |

| HIGH           | 2500   | -          | 0                  | 2062.50 | -          | 0                  | 1562.50 | -          | 0                  | 1250   | -          | 0                  |

| LOW            | 9.77   | -          | 255                | 8,06    | -          | 255                | 6.10    | -          | 255                | 4.88   | -          | 255                |

|                |        |            |                    |         |            |                    |         |            |                    |        |            |                    |

| BAUD SPBRG     |        | 10 1       | 10 MHz SPBRG       |         |            | 9 MHz              | SPBRG   | 5.068      | 8 MHz              | SPBRG  |            |                    |

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  | NA     | -          | -                  |

| 1.2            | NA     | -          | -                  | NA      | -          | -                  | NA      | -          | -                  | NA     | -          | -                  |

| 2.4            | NA     | -          | -                  | NA      | -          | -                  | 2.41    | +0.23      | 185                | 2.40   | 0          | 131                |

| 9.6            | 9.62   | +0.16      | 103                | 9.62    | +0.16      | 64                 | 9.52    | -0.83      | 46                 | 9.60   | 0          | 32                 |

| 19.2           | 19.23  | +0.16      | 51                 | 18.94   | -1.36      | 32                 | 19.45   | +1.32      | 22                 | 18.64  | -2.94      | 16                 |

| 76.8           | 76.92  | +0.16      | 12                 | 78.13   | +1.73      | 7                  | 74.57   | -2.90      | 5                  | 79.20  | +3.13      | 3                  |

| 96             | 100    | +4.17      | 9                  | 89.29   | -6.99      | 6                  | 89.49   | -6.78      | 4                  | 105.60 | +10.00     | 2                  |

| 300            | 333.33 | +11.11     | 2                  | 312.50  | +4.17      | 1                  | 447.44  | +49.15     | 0                  | 316.80 | +5.60      | 0                  |

| 500            | 500    | 0          | 1                  | 625     | +25.00     | 0                  | 447.44  | -10.51     | 0                  | NA     | -          | -                  |

| HIGH           | 1000   | -          | 0                  | 625     | -          | 0                  | 447.44  | -          | 0                  | 316.80 | -          | 0                  |

| LOW            | 3.91   | -          | 255                | 2.44    | -          | 255                | 1.75    | -          | 255                | 1.24   | -          | 255                |

|                |        |            |                    |         |            |                    |         |            |                    |        |            |                    |

| BAUD           | Fosc = | 4 MHz      | SPBRG              | 3.5795  | 45 MHz     | SPBRG              | 1 N     | 1Hz        | SPBRG              | 32.76  | 8 kHz      | SPBRG              |

| RATE<br>(Kbps) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA     | -          | -                  | NA      | -          | -                  | 0.30    | +0.16      | 207                | 0.29   | -2.48      | 6                  |

| 1.2            | 1.20   | +0.16      | 207                | 1.20    | +0.23      | 185                | 1.20    | +0.16      | 51                 | 1.02   | -14.67     | 1                  |

| 2.4            | 2.40   | +0.16      | 103                | 2.41    | +0.23      | 92                 | 2.40    | +0.16      | 25                 | 2.05   | -14.67     | 0                  |

| 9.6            | 9.62   | +0.16      | 25                 | 9.73    | +1.32      | 22                 | 8.93    | -6.99      | 6                  | NA     | -          | -                  |

| 19.2           | 19.23  | +0.16      | 12                 | 18.64   | -2.90      | 11                 | 20.83   | +8.51      | 2                  | NA     | -          | -                  |

| 76.8           | NA     | -          | -                  | 74.57   | -2.90      | 2                  | 62.50   | -18.62     | 0                  | NA     | -          | -                  |

|                |        |            |                    |         |            |                    |         |            |                    |        |            |                    |

#### TABLE 18-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

96

300

500

HIGH

LOW

NA

NA

NA

250

0.98

-

-

-

-

-

-

-

-

0

255

111.86

223.72

NA

55.93

0.22

+16.52

-25.43

-

-

-

1

0

-

0

255

NA

NA

NA

62.50

0.24

-

-

-

-

-

-

-

-

0

255

NA

NA

NA

2.05

0.008

-

-

-

-

-

-

-

-

0

255

#### REGISTER 19-2: CANSTAT: CAN STATUS REGISTER

| R-1     | R-0     | R-0     | U-0 | R-0    | R-0    | R-0    | U-0   |

|---------|---------|---------|-----|--------|--------|--------|-------|

| OPMODE2 | OPMODE1 | OPMODE0 |     | ICODE2 | ICODE1 | ICODE0 | _     |

| bit 7   |         |         |     |        |        |        | bit 0 |

bit 7-5 **OPMODE2:OPMODE0:** Operation Mode Status bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = Configuration mode

- 011 = Listen Only mode

- 010 = Loopback mode

- 001 = Disable mode

- 000 = Normal mode

Note: Before the device goes into Sleep mode, select Disable mode.

#### bit 4 Unimplemented: Read as '0'

#### bit 3-1 ICODE2:ICODE0: Interrupt Code bits

When an interrupt occurs, a prioritized coded interrupt value will be present in the ICODE2:ICODE0 bits. These codes indicate the source of the interrupt. The ICODE2:ICODE0 bits can be copied to the WIN2:WIN0 bits to select the correct buffer to map into the Access Bank area. See Example 19-1 for code example.

- 111 = Wake-up on interrupt

- 110 = RXB0 interrupt

- 101 = RXB1 interrupt

- 100 = TXB0 interrupt

- 011 = TXB1 interrupt

- 010 = TXB2 interrupt

- 001 = Error interrupt

- 000 = No interrupt

- bit 0

Unimplemented: Read as '0'

| Legend:           |                  |                                        |      |

|-------------------|------------------|----------------------------------------|------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'     |      |

| -n = Value at POR | '1' = Bit is set | 0' = Bit is cleared x = Bit is unknown | iown |

#### REGISTER 19-23: RXFnEIDH: RECEIVE ACCEPTANCE FILTER n EXTENDED IDENTIFIER, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID15 | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0

EID15:EID8: Extended Identifier Filter bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### REGISTER 19-24: RXFnEIDL: RECEIVE ACCEPTANCE FILTER n EXTENDED IDENTIFIER, LOW BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 EID7:EID0: Extended Identifier Filter bits

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 19-25: RXMnSIDH: RECEIVE ACCEPTANCE MASK n STANDARD IDENTIFIER MASK, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### bit 7-0 SID10:SID3: Standard Identifier Mask bits or Extended Identifier Mask bits EID28:EID21

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

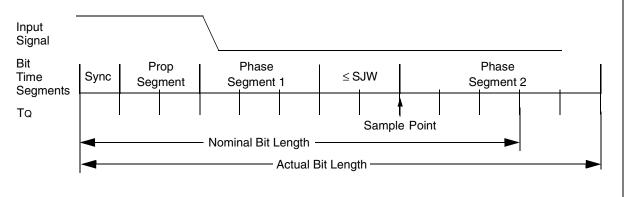

### 19.8 Synchronization

To compensate for phase shifts between the oscillator frequencies of each of the nodes on the bus, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. When an edge in the transmitted data is detected, the logic will compare the location of the edge to the expected time (Sync\_Seg). The circuit will then adjust the values of Phase Segment 1 and Phase Segment 2, as necessary. There are two mechanisms used for synchronization.

#### 19.8.1 HARD SYNCHRONIZATION

Hard synchronization is only done when there is a recessive to dominant edge during a bus Idle condition, indicating the start of a message. After hard synchronization, the bit time counters are restarted with Sync\_Seg. Hard synchronization forces the edge which has occurred to lie within the synchronization segment of the restarted bit time. Due to the rules of synchronization, if a hard synchronization occurs, there will not be a resynchronization within that bit time.

#### 19.8.2 RESYNCHRONIZATION

As a result of resynchronization, Phase Segment 1 may be lengthened or Phase Segment 2 may be shortened. The amount of lengthening or shortening of the phase buffer segments has an upper bound given by the Synchronization Jump Width (SJW). The value of the SJW will be added to Phase Segment 1 (see Figure 19-8) or subtracted from Phase Segment 2 (see Figure 19-9). The SJW is programmable between 1 Tq and 4 Tq.

Clocking information will only be derived from recessive to dominant transitions. The property, that only a fixed maximum number of successive bits have the same value, ensures resynchronization to the bit stream during a frame. The phase error of an edge is given by the position of the edge relative to Sync\_Seg, measured in Tq. The phase error is defined in magnitude of Tq as follows:

- e = 0 if the edge lies within Sync\_Seg.

- e > 0 if the edge lies before the sample point.

- e < 0 if the edge lies after the sample point of the previous bit.

If the magnitude of the phase error is less than or equal to the programmed value of the synchronization jump width, the effect of a resynchronization is the same as that of a hard synchronization.

If the magnitude of the phase error is larger than the synchronization jump width and if the phase error is positive, then Phase Segment 1 is lengthened by an amount equal to the synchronization jump width.

If the magnitude of the phase error is larger than the resynchronization jump width and if the phase error is negative, then Phase Segment 2 is shortened by an amount equal to the synchronization jump width.

#### 19.8.3 SYNCHRONIZATION RULES

- Only one synchronization within one bit time is allowed.

- An edge will be used for synchronization only if the value detected at the previous sample point (previously read bus value) differs from the bus value immediately after the edge.

- All other recessive to dominant edges, fulfilling rules 1 and 2, will be used for resynchronization with the exception that a node transmitting a dominant bit will not perform a resynchronization as a result of a recessive to dominant edge with a positive phase error.

### FIGURE 19-8: LENGTHENING A BIT PERIOD (ADDING SJW TO PHASE SEGMENT 1)

### 22.0 COMPARATOR VOLTAGE REFERENCE MODULE

| Note: | The compa | arator | voltage reference is o |           |     |  |  |

|-------|-----------|--------|------------------------|-----------|-----|--|--|

|       | available | on     | the                    | PIC18F448 | and |  |  |

|       | PIC18F45  | 8.     |                        |           |     |  |  |

This module is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The CVRCON register controls the operation of the reference, as shown in Register 22-1. The block diagram is shown in Figure 22-1.

The comparator and reference supply voltage can come from either VDD and Vss, or the external VREF+ and VREF-, that are multiplexed with RA3 and RA2. The comparator reference supply voltage is controlled by the CVRSS bit.

#### 22.1 Configuring the Comparator Voltage Reference

The comparator voltage reference can output 16 distinct voltage levels for each range. The equations used to calculate the output of the comparator voltage reference are as follows.

#### EQUATION 22-1:

If CVRR = 1:  $CVREF = (CVR < 3:0 > /24) \times CVRSRC$ where: CVRSS = 1, CVRSRC = (VREF+) - (VREF-)CVRSS = 0, CVRSRC = AVDD - AVSS

#### EQUATION 22-2:

If CVRR = 0: CVREF = (CVRSRC x 1/4) + (CVR<3:0>/32) x CVRSRC where: CVRSS = 1, CVRSRC = (VREF+) - (VREF-) CVRSS = 0, CVRSRC = AVDD - AVSS

The settling time of the Comparator Voltage Reference must be considered when changing the RA0/AN0/ CVREF output (see Table 27-4 in **Section 27.2** "**DC Characteristics**").

#### REGISTER 22-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

|         | 011100111  |                                 |             |             | Enerioe        | 0011110    |                |        |

|---------|------------|---------------------------------|-------------|-------------|----------------|------------|----------------|--------|

|         | R/W-0      | R/W-0                           | R/W-0       | R/W-0       | R/W-0          | R/W-0      | R/W-0          | R/W-0  |

|         | CVREN      | CVROE                           | CVRR        | CVRSS       | CVR3           | CVR2       | CVR1           | CVR0   |

|         | bit 7      |                                 |             |             |                |            |                | bit 0  |

|         |            |                                 |             |             |                |            |                |        |

| bit 7   | CVREN: C   | omparator V                     | oltage Refe | rence Enab  | le bit         |            |                |        |

|         |            | circuit power                   |             |             |                |            |                |        |

|         |            | circuit power                   |             |             |                |            |                |        |

| bit 6   |            | omparator V                     | •           |             |                |            |                |        |

|         |            | voltage level<br>voltage is dis |             |             |                |            |                |        |

| bit 5   |            | mparator VRE                    |             |             |                |            |                |        |

| 0.110   |            | VRSRC to 0.6                    | •           |             | c/24 step si   | 78         |                |        |

|         |            | VRSRC to 0.7                    |             |             |                |            |                |        |

| bit 4   | CVRSS: C   | omparator Vi                    | REF Source  | Selection b | it             |            |                |        |

|         |            | rator referen                   | ,           | · ·         | , (            | REF-)      |                |        |

|         |            | rator referen                   | ,           |             |                |            |                |        |

| bit 3-0 |            | : Comparato                     | r VREF Valu | e Selection | $0 \le CVR3:C$ | VR0 ≤ 15 b | its            |        |

|         | When CVF   |                                 |             | 220)        |                |            |                |        |

|         |            | CVR3:CVR0/                      | 24) ● (CVR: | SRC)        |                |            |                |        |

|         | When CVF   | <u>1H = 0:</u><br>/4 ● (CVRSRC  | + (CVB3)    | CVB0/32) •  | (CVBSBC)       |            |                |        |

|         |            |                                 | , (00110.   | 0 1110/02)  |                |            |                |        |

|         | Legend:    |                                 |             |             |                |            |                |        |

|         | R = Reada  | ble bit                         | W = W       | ritable bit | U = Unim       | plemented  | bit, read as ' | 0'     |

|         | -n = Value | at POR                          | '1' = Bi    | t is set    | '0' = Bit is   | cleared    | x = Bit is u   | nknown |

|         |            |                                 |             |             |                |            |                |        |

#### **GENERAL FORMAT FOR INSTRUCTIONS** FIGURE 25-1: Byte-oriented file register operations **Example Instruction** 10 9 8 7 15 0 OPCODE f (FILE #) ADDWF MYREG, W, B d а d = 0 for result destination to be WREG register d = 1 for result destination to be file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Byte to Byte move operations (2-word) 15 12 11 0 OPCODE f (Source FILE #) MOVFF MYREG1, MYREG2 15 12 11 0 f (Destination FILE #) 1111 f = 12-bit file register address Bit-oriented file register operations 15 12 11 987 0 OPCODE b (BIT #) f (FILE #) а BSF MYREG, bit, B b = 3-bit position of bit in file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Literal operations 15 8 7 0 OPCODE k (literal) MOVLW 0x7F k = 8-bit immediate value **Control** operations CALL, GOTO and Branch operations 15 8 7 0 OPCODE n<7:0> (literal) GOTO Label 15 12 11 0 1111 n<19:8> (literal) n = 20-bit immediate value 15 8 7 0 CALL MYFUNC OPCODE S n<7:0> (literal) 15 12 11 0 n<19:8> (literal) S = Fast bit 15 11 10 0 OPCODE BRA MYFUNC n<10:0> (literal) 15 8 7 0 OPCODE n<7:0> (literal) BC MYFUNC

| MULLW                                  | Multiply Literal with          | w                   | MULWF                                                                                                                                                                                                                                                                                                                         | Multiply W with f                                         |                                  |                              |  |

|----------------------------------------|--------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------|------------------------------|--|

| Syntax:                                | [ label ] MULLW                |                     | Syntax:                                                                                                                                                                                                                                                                                                                       | [label] M                                                 | ULWF f[,a]                       |                              |  |

| Operands:                              | $0 \le k \le 255$              |                     | Operands:                                                                                                                                                                                                                                                                                                                     | $0 \leq f \leq 255$                                       |                                  |                              |  |

| Operation:                             | (W) x k $\rightarrow$ PRODH:PF | RODL                |                                                                                                                                                                                                                                                                                                                               | a ∈ [0,1]                                                 |                                  |                              |  |

| Status Affected:                       | None                           |                     | Operation:                                                                                                                                                                                                                                                                                                                    | (W) x (f) $\rightarrow$ I                                 | PRODH:PRO                        | DL                           |  |

| Encoding:                              | 0000 1101                      | kkkk kkkk           | Status Affected:                                                                                                                                                                                                                                                                                                              | None                                                      |                                  |                              |  |

| Description:                           | An unsigned multiplica         | tion is carried out | Encoding:                                                                                                                                                                                                                                                                                                                     | 0000                                                      | 001a fff                         | f ffff                       |  |

|                                        |                                | Description:        | Description:<br>An unsigned multiplication is carrie<br>between the contents of W and th<br>register file location 'f'. The 16-bit<br>is stored in the PRODH:PRODL<br>register pair. PRODH contains the<br>byte.<br>Both W and 'f' are unchanged.<br>None of the status flags are affect<br>Note that neither Overflow nor Ca |                                                           |                                  |                              |  |

| Words:                                 | 1                              |                     |                                                                                                                                                                                                                                                                                                                               | •                                                         | •                                | A Zero result                |  |

| Cycles:                                | 1                              |                     |                                                                                                                                                                                                                                                                                                                               | •                                                         | out not detect<br>Bank will be s | ed. If 'a' is '0',           |  |

| Q Cycle Activity:                      |                                |                     |                                                                                                                                                                                                                                                                                                                               |                                                           |                                  | If 'a' = 1, then             |  |

| Q1                                     | Q2 Q3                          | Q4                  |                                                                                                                                                                                                                                                                                                                               | the bank will be selected as per the BSR value (default). |                                  |                              |  |

| Decode                                 | Read Process                   |                     | Words:                                                                                                                                                                                                                                                                                                                        | 1                                                         | uerauit).                        |                              |  |

|                                        | literal 'k' Data               | registers<br>PRODH: |                                                                                                                                                                                                                                                                                                                               |                                                           |                                  |                              |  |

|                                        |                                | PRODL               | Cycles:                                                                                                                                                                                                                                                                                                                       | 1                                                         |                                  |                              |  |

|                                        |                                |                     | Q Cycle Activity:<br>Q1                                                                                                                                                                                                                                                                                                       | Q2                                                        | Q3                               | Q4                           |  |

| Example:                               | MULLW 0xC4                     |                     | Decode                                                                                                                                                                                                                                                                                                                        | Read                                                      | Process                          | Write                        |  |

| Before Instru<br>W<br>PRODH<br>PRODL   | = 0xE2<br>= ?<br>= ?           |                     |                                                                                                                                                                                                                                                                                                                               | register 'f'                                              | Data                             | registers<br>PRODH:<br>PRODL |  |

| After Instructi<br>W<br>PRODH<br>PRODL | = 0xE2                         |                     | Example:<br>Before Instruc<br>W<br>REG<br>PRODH<br>PRODL                                                                                                                                                                                                                                                                      | ction<br>= 0x0<br>= 0xE<br>= ?                            |                                  |                              |  |

After Instruction

W REG PRODH PRODL 0xC4 0xB5 0x8A 0x94

= = =

| XORWF                                                       | Exclusive                                                                                                                   | Exclusive OR W with f                                                                  |                                                         |                                              |                                                |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------|------------------------------------------------|--|--|

| Syntax:                                                     | [label]                                                                                                                     | XORWF                                                                                  | f [,d                                                   | [,a]]                                        |                                                |  |  |

| Operands:                                                   | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                       | d ∈ [0,1]                                                                              |                                                         |                                              |                                                |  |  |

| Operation:                                                  | (W) .XOR.                                                                                                                   | (f) $\rightarrow$ des                                                                  | st                                                      |                                              |                                                |  |  |

| Status Affected:                                            | N, Z                                                                                                                        |                                                                                        |                                                         |                                              |                                                |  |  |

| Encoding:                                                   | 0001                                                                                                                        | 10da                                                                                   | fff                                                     | f                                            | ffff                                           |  |  |

| Description:                                                | Exclusive C<br>register 'f'.<br>in W. If 'd' is<br>in register '<br>Access Bal<br>overriding t<br>then the ba<br>the BSR va | If 'd' is 'o'<br>s '1', the r<br>if' (defaul<br>nk will be<br>the BSR v<br>ank will be | , the result<br>t). If 'a<br>selec<br>value.<br>e selec | esult<br>is sto<br>i' is '<br>ted,<br>If 'a' | is stored<br>bred back<br>0', the<br>' is '1', |  |  |

| Words:                                                      | 1                                                                                                                           |                                                                                        |                                                         |                                              |                                                |  |  |

| Cycles:                                                     | 1                                                                                                                           |                                                                                        |                                                         |                                              |                                                |  |  |

| Q Cycle Activity:                                           |                                                                                                                             |                                                                                        |                                                         |                                              |                                                |  |  |

| Q1                                                          | Q2                                                                                                                          | Q3                                                                                     | 6                                                       |                                              | Q4                                             |  |  |

| Decode                                                      | Read<br>register 'f'                                                                                                        | Proce<br>Data                                                                          |                                                         |                                              | /rite to<br>stination                          |  |  |

| Example:                                                    | XORWF                                                                                                                       | REG                                                                                    |                                                         |                                              |                                                |  |  |

| Before Instruct<br>REG<br>W<br>After Instructio<br>REG<br>W | = 0xAF<br>= 0xB5                                                                                                            |                                                                                        |                                                         |                                              |                                                |  |  |

| vv                                                          | - 0,05                                                                                                                      |                                                                                        |                                                         |                                              |                                                |  |  |

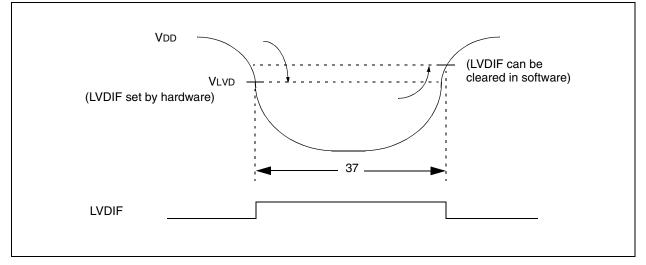

| Low-Vol      | tage Dete | ct Characteristics | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq Ta \leq +85^\circ C \mbox{ for industrial} \\ & -40^\circ C \leq Ta \leq +125^\circ C \mbox{ for extended} \end{array}$ |      |      |      |       |                     |  |

|--------------|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|---------------------|--|

| Param<br>No. | Symbol    | Characteristi      | c                                                                                                                                                                                                                                                           | Min  | Тур  | Max  | Units | Conditions          |  |

| D420         | Vlvd      | LVD Voltage        | LVV = 0001                                                                                                                                                                                                                                                  | 1.96 | 2.06 | 2.16 | V     | $T \ge 25^{\circ}C$ |  |

|              |           |                    | LVV = 0010                                                                                                                                                                                                                                                  | 2.16 | 2.27 | 2.38 | V     | T ≥ 25°C            |  |

|              |           |                    | LVV = 0011                                                                                                                                                                                                                                                  | 2.35 | 2.47 | 2.59 | V     | $T \ge 25^{\circ}C$ |  |

|              |           |                    | LVV = 0100                                                                                                                                                                                                                                                  | 2.43 | 2.58 | 2.69 | V     |                     |  |

|              |           |                    | LVV = 0101                                                                                                                                                                                                                                                  | 2.64 | 2.78 | 2.92 | V     |                     |  |

|              |           |                    | LVV = 0110                                                                                                                                                                                                                                                  | 2.75 | 2.89 | 3.03 | V     |                     |  |

|              |           |                    | LVV = 0111                                                                                                                                                                                                                                                  | 2.95 | 3.1  | 3.26 | V     |                     |  |

|              |           |                    | LVV = 1000                                                                                                                                                                                                                                                  | 3.24 | 3.41 | 3.58 | V     |                     |  |

|              |           |                    | LVV = 1001                                                                                                                                                                                                                                                  | 3.43 | 3.61 | 3.79 | V     |                     |  |

|              |           |                    | LVV = 1010                                                                                                                                                                                                                                                  | 3.53 | 3.72 | 3.91 | V     |                     |  |