Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

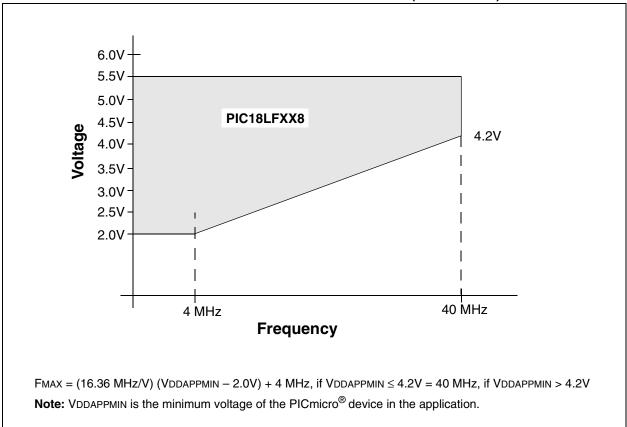

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf458t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 4-1: | SPECIAL FUNCTION REGISTER MAP |

|------------|-------------------------------|

|------------|-------------------------------|

| Address | Name                    | Address | Name                    | Address | Name                    | Address | Name                 |

|---------|-------------------------|---------|-------------------------|---------|-------------------------|---------|----------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(2)</sup>    | FBFh    | CCPR1H                  | F9Fh    | IPR1                 |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(2)</sup> | FBEh    | CCPR1L                  | F9Eh    | PIR1                 |

| FFDh    | TOSL                    | FDDh    | POSTDEC2(2)             | FBDh    | CCP1CON                 | F9Dh    | PIE1                 |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(2)</sup>  | FBCh    | ECCPR1H <sup>(5)</sup>  | F9Ch    |                      |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(2)</sup>   | FBBh    | ECCPR1L <sup>(5)</sup>  | F9Bh    | _                    |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | ECCP1CON <sup>(5)</sup> | F9Ah    | _                    |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    |                         | F99h    | _                    |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    |                         | F98h    | —                    |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP1DEL <sup>(5)</sup> | F97h    | —                    |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | ECCPAS <sup>(5)</sup>   | F96h    | TRISE <sup>(5)</sup> |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | CVRCON <sup>(5)</sup>   | F95h    | TRISD <sup>(5)</sup> |

| FF4h    | PRODH                   | FD4h    | —                       | FB4h    | CMCON <sup>(5)</sup>    | F94h    | TRISC                |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | TMR3H                   | F93h    | TRISB                |

| FF2h    | INTCON                  | FD2h    | LVDCON                  | FB2h    | TMR3L                   | F92h    | TRISA                |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | T3CON                   | F91h    | —                    |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | _                       | F90h    | —                    |

| FEFh    | INDF0 <sup>(2)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                   | F8Fh    | —                    |

| FEEh    | POSTINC0 <sup>(2)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG                   | F8Eh    |                      |

| FEDh    | POSTDEC0 <sup>(2)</sup> | FCDh    | T1CON                   | FADh    | TXREG                   |         | LATE <sup>(5)</sup>  |

| FECh    | PREINC0 <sup>(2)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA                   | F8Ch    | LATD <sup>(5)</sup>  |

| FEBh    | PLUSW0(2)               | FCBh    | PR2                     | FABh    | RCSTA                   | F8Bh    | LATC                 |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | —                       | F8Ah    | LATB                 |

| FE9h    | FSR0L                   | FC9h    | SSPBUF                  | FA9h    | EEADR                   | F89h    | LATA                 |

| FE8h    |                         | FC8h    | SSPADD                  | FA8h    | EEDATA                  | F88h    | —                    |

| FE7h    | INDF1 <sup>(2)</sup>    | FC7h    | SSPSTAT                 | FA7h    | EECON2                  | F87h    | —                    |

| FE6h    | POSTINC1 <sup>(2)</sup> | FC6h    | SSPCON1                 | FA6h    | EECON1                  | F86h    | —                    |

| FE5h    | POSTDEC1 <sup>(2)</sup> | FC5h    | SSPCON2                 | FA5h    | IPR3                    | F85h    | —                    |

| FE4h    | PREINC1 <sup>(2)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3                    | F84h    | PORTE <sup>(5)</sup> |

| FE3h    | PLUSW1 <sup>(2)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3                    | F83h    | PORTD <sup>(5)</sup> |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                    | F82h    | PORTC                |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                    | F81h    | PORTB                |

| FE0h    | BSR                     | FC0h    |                         | FA0h    | PIE2                    | F80h    | PORTA                |

Note 1: Unimplemented registers are read as '0'.

- 2: This is not a physical register.

- 3: Contents of register are dependent on WIN2:WIN0 bits in the CANCON register.

- **4:** CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the CANSTAT register due to the Microchip header file requirement.

- 5: These registers are not implemented on the PIC18F248 and PIC18F258.

# 9.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

Read-modify-write operations on the LATB register, read and write the latched output value for PORTB.

EXAMPLE 9-2: INITIALIZING PORTB

|       | LL J-2. |                         |

|-------|---------|-------------------------|

| CLRF  | PORTB   | ; Initialize PORTB by   |

|       |         | ; clearing output       |

|       |         | ; data latches          |

| CLRF  | LATB    | ; Alternate method      |

|       |         | ; to clear output       |

|       |         | ; data latches          |

| MOVLW | 0CFh    | ; Value used to         |

|       |         | ; initialize data       |

|       |         | ; direction             |

| MOVWF | TRISB   | ; Set RB3:RB0 as inputs |

|       |         | ; RB5:RB4 as outputs    |

|       |         | ; RB7:RB6 as inputs     |

| 1     |         |                         |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (INTCON2 register). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB7:RB4) have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit RBIF (INTCON register). This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF instruction). This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

- Note 1: While in Low-Voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin and should not be held low during normal operation to protect against inadvertent ICSP mode entry.

- 2: When using Low-Voltage ICSP Programming (LVP), the pull-up on RB5 becomes disabled. If TRISB bit 5 is cleared, thereby setting RB5 as an output, LATB bit 5 must also be cleared for proper operation.

#### 17.3.8 SLEEP OPERATION

In Master mode, all module clocks are halted and the transmission/reception will remain in that state until the device wakes from Sleep. After the device returns to normal mode, the module will continue to transmit/ receive data.

In Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device from Sleep.

#### 17.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.3.10 BUS MODE COMPATIBILITY

Table 17-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

There is also an SMP bit which controls when the data is sampled.

| Name    | Bit 7                                                    | Bit 6          | Bit 5    | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------------------------------------------|----------------|----------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH                                                 | PEIE/GIEL      | TMR0IE   | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1    | PSPIF <sup>(1)</sup>                                     | ADIF           | RCIF     | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1    | PSPIE <sup>(1)</sup>                                     | ADIE           | RCIE     | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1    | PSPIP <sup>(1)</sup>                                     | ADIP           | RCIP     | TXIP   | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 1111 1111            | 1111 1111                       |

| TRISC   | PORTC Da                                                 | ta Direction F | Register |        |        |        |        |        | 1111 1111            | 1111 1111                       |

| TRISA   | —                                                        | TRISA6         | TRISA5   | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | -111 1111            | -111 1111                       |

| SSPBUF  | Synchronous Serial Port Receive Buffer/Transmit Register |                |          |        |        |        |        |        |                      | uuuu uuuu                       |

| SSPCON1 | WCOL                                                     | SSPOV          | SSPEN    | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 0000 0000            | 0000 0000                       |

| SSPSTAT | SMP                                                      | CKE            | D/A      | Р      | S      | R/W    | UA     | BF     | 0000 0000            | 0000 0000                       |

#### TABLE 17-2: REGISTERS ASSOCIATED WITH SPI™ OPERATION

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI<sup>TM</sup> mode.**Note 1:**These registers or register bits are not implemented on the PIC18F248 and PIC18F258 and read as '0's.

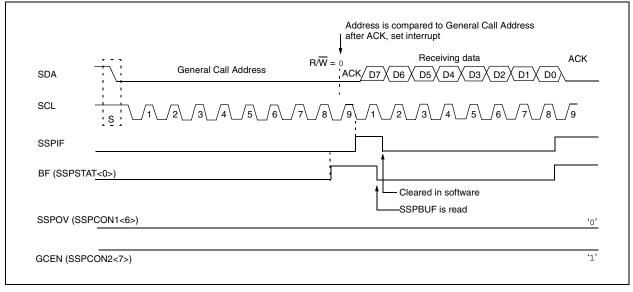

#### 17.4.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPSR and the address is compared against the SSPADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPSR is transferred to the SSPBUF, the BF flag bit is set (eighth bit) and on the falling edge of the ninth bit (ACK bit), the SSPIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPBUF. The value can be used to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-bit Address mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 17-15).

#### FIGURE 17-15: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT ADDRESS MODE)

# PIC18FXX8

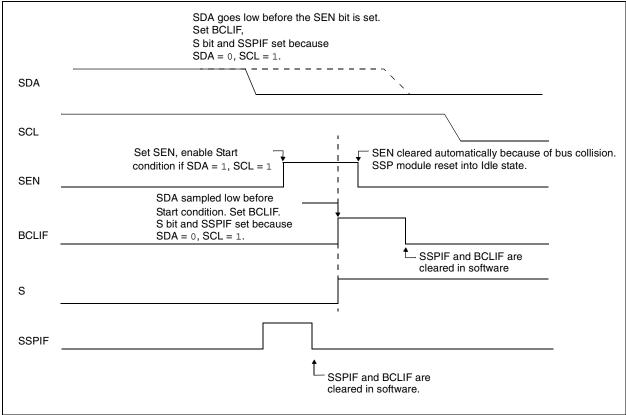

#### 17.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 17-26).

- b) SCL is sampled low before SDA is asserted low (Figure 17-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 17-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 17-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 17-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

| TABLE          | E 18-4: | BAUD       | RATES              | FOR A  | SYNCH      | RONOUS             | MODE   | (BRGH      | = 0)               |        |            |                    |

|----------------|---------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|

| BAUD           | Fosc =  | 40 MHz     | SPBRG              | 33     | MHz        | SPBRG              | 25     | MHz        | SPBRG              | 20     | MHz        | SPBRG              |

| RATE<br>(Kbps) | KBAUD   | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) |

| 0.3            | NA      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 1.2            | NA      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 2.4            | NA      | -          | -                  | 2.40   | -0.07      | 214                | 2.40   | -0.15      | 162                | 2.40   | +0.16      | 129                |

| 9.6            | 9.62    | +0.16      | 64                 | 9.55   | -0.54      | 53                 | 9.53   | -0.76      | 40                 | 9.47   | -1.36      | 32                 |

| 19.2           | 18.94   | -1.36      | 32                 | 19.10  | -0.54      | 26                 | 19.53  | +1.73      | 19                 | 19.53  | +1.73      | 15                 |

| 76.8           | 78.13   | +1.73      | 7                  | 73.66  | -4.09      | 6                  | 78.13  | +1.73      | 4                  | 78.13  | +1.73      | 3                  |

| 96             | 89.29   | -6.99      | 6                  | 103.13 | +7.42      | 4                  | 97.66  | +1.73      | 3                  | 104.17 | +8.51      | 2                  |

| 300            | 312.50  | +4.17      | 1                  | 257.81 | -14.06     | 1                  | NA     | -          | -                  | 312.50 | +4.17      | 0                  |

| 500            | 625     | +25.00     | 0                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| HIGH           | 625     | -          | 0                  | 515.63 | -          | 0                  | 390.63 | -          | 0                  | 312.50 | -          | 0                  |

| LOW            | 2.44    | -          | 255                | 2.01   | -          | 255                | 1.53   | -          | 255                | 1.22   | -          | 255                |

| BAUD           | Fosc =  | 16 MHz     | SPBRG              | 10     | MHz        | SPBRG              | 7.1590 | 9 MHz      | SPBRG              | 5.068  | 8 MHz      | SPBRG              |

| RATE           |         | %          | value              |        | %          | value              |        | %          | value              |        | %          | value              |

| (Kbps)         | KBAUD   | ERROR      | (decimal)          | KBAUD  | ERROR      | (decimal)          | KBAUD  | ERROR      | (decimal)          | KBAUD  | ERROR      | (decimal)          |

| 0.3            | NA      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 1.2            | 1.20    | +0.16      | 207                | 1.20   | +0.16      | 129                | 1.20   | +0.23      | 92                 | 1.20   | 0          | 65                 |

| 2.4            | 2.40    | +0.16      | 103                | 2.40   | +0.16      | 64                 | 2.38   | -0.83      | 46                 | 2.40   | 0          | 32                 |

| 9.6            | 9.62    | +0.16      | 25                 | 9.77   | +1.73      | 15                 | 9.32   | -2.90      | 11                 | 9.90   | +3.13      | 7                  |

| 19.2           | 19.23   | +0.16      | 12                 | 19.53  | +1.73      | 7                  | 18.64  | -2.90      | 5                  | 19.80  | +3.13      | 3                  |

| 76.8           | 83.33   | +8.51      | 2                  | 78.13  | +1.73      | 1                  | 111.86 | +45.65     | 0                  | 79.20  | +3.13      | 0                  |

| 96             | 83.33   | -13.19     | 2                  | 78.13  | -18.62     | 1                  | NA     | -          | -                  | NA     | -          | -                  |

| 300            | 250     | -16.67     | 0                  | 156.25 | -47.92     | 0                  | NA     | -          | -                  | NA     | -          | -                  |

| 500            | NA      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| HIGH           | 250     | -          | 0                  | 156.25 | -          | 0                  | 111.86 | -          | 0                  | 79.20  | -          | 0                  |

| LOW            | 0.98    | -          | 255                | 0.61   | -          | 255                | 0.44   | -          | 255                | 0.31   | -          | 255                |

| BAUD<br>RATE   | Fosc :  | = 4 MHz    | SPBRG<br>value     | 3.5795 | 645 MHz    | SPBRG<br>value     | 11     | MHz        | SPBRG<br>value     | 32.76  | 8 kHz      | SPBRG<br>value     |

| (Kbps)         | KBAUD   | %<br>ERROR | (decimal)          | KBAUD  | %<br>ERROR | (decimal)          | KBAUD  | %<br>ERROR | (decimal)          | KBAUD  | %<br>ERROR | (decimal)          |

| 0.3            | 0.30    | -0.16      | 207                | 0.30   | +0.23      | 185                | 0.30   | +0.16      | 51                 | 0.26   | -14.67     | 1                  |

| 1.2            | 1.20    | +1.67      | 51                 | 1.19   | -0.83      | 46                 | 1.20   | +0.16      | 12                 | NA     | -          | -                  |

| 2.4            | 2.40    | +1.67      | 25                 | 2.43   | +1.32      | 22                 | 2.23   | -6.99      | 6                  | NA     | -          | -                  |

| 9.6            | 8.93    | -6.99      | 6                  | 9.32   | -2.90      | 5                  | 7.81   | -18.62     | 1                  | NA     | -          | -                  |

| 19.2           | 20.83   | +8.51      | 2                  | 18.64  | -2.90      | 2                  | 15.63  | -18.62     | 0                  | NA     | -          | -                  |

| 76.8           | 62.50   | -18.62     | 0                  | 55.93  | -27.17     | 0                  | NA     | -          | -                  | NA     | -          | -                  |

| 96             | NA      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 300            | NA      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

| 500            | NA      | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA     | -          | -                  |

|                | 1       |            |                    | 1      |            |                    | 1      |            |                    | I      |            |                    |

0

255

15.63

0.06

-

-

-

-

0

255

0.51

0.002

**BAUD BATES FOR ASYNCHRONOUS MODE (BRGH = 0) TABLE 18-4**:

0

255

55.93

0.22

-

-

HIGH

LOW

62.50

0.24

0

255

\_

# 18.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA register). In addition, enable bit SPEN (RCSTA register) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA register).

#### 18.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 18-1. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register (TXREG). The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCY), the TXREG is empty and interrupt bit TXIF (PIR1 register) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1 register). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in

software. It will reset only when new data is loaded into the TXREG register. While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA register), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 18.1 "USART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

Note: TXIF is not cleared immediately upon loading data into the transmit buffer TXREG. The flag bit becomes valid in the second instruction cycle following the load instruction.

| Name   | Bit 7                           | Bit 6         | Bit 5  | Bit 4         | Bit 3 | Bit 2  | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------------------------------|---------------|--------|---------------|-------|--------|---------------|--------|----------------------|---------------------------------|

| INTCON | GIE/GIEH                        | PEIE/GIEL     | TMR0IE | <b>INTOIE</b> | RBIE  | TMR0IF | <b>INT0IF</b> | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>            | ADIF          | RCIF   | TXIF          | SSPIF | CCP1IF | TMR2IF        | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>            | ADIE          | RCIE   | TXIE          | SSPIE | CCP1IE | TMR2IE        | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>            | ADIP          | RCIP   | TXIP          | SSPIP | CCP1IP | TMR2IP        | TMR1IP | 1111 1111            | 1111 1111                       |

| RCSTA  | SPEN                            | RX9           | SREN   | CREN          | ADDEN | FERR   | OERR          | RX9D   | 0000 000x            | 0000 000u                       |

| TXREG  | USART Trai                      | nsmit Registe | er     |               |       |        |               |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                            | TX9           | TXEN   | SYNC          | _     | BRGH   | TRMT          | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | RG Baud Rate Generator Register |               |        |               |       |        |               |        | 0000 0000            | 0000 0000                       |

# TABLE 18-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: These registers or register bits are not implemented on the PIC18F248 and PIC18F258 and read as '0's.

# 19.0 CAN MODULE

### 19.1 Overview

The Controller Area Network (CAN) module is a serial interface, useful for communicating with other peripherals or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments.

The CAN module is a communication controller, implementing the CAN 2.0 A/B protocol as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- · Complies with ISO CAN Conformance Test

- Implementation of the CAN protocol CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Support for remote frames

- Double-buffered receiver with two prioritized received message storage buffers

- 6 full (standard/extended identifier) acceptance filters, 2 associated with the high priority receive buffer and 4 associated with the low priority receive buffer

- 2 full acceptance filter masks, one each associated with the high and low priority receive buffers

- Three transmit buffers with application specified prioritization and abort capability

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to timer module for time-stamping and network synchronization

- Low-power Sleep mode

# 19.1.1 OVERVIEW OF THE MODULE

The CAN bus module consists of a protocol engine and message buffering and control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the 2 receive registers.

The CAN module supports the following frame types:

- Standard Data Frame

- Extended Data Frame

- Remote Frame

- Error Frame

- Overload Frame Reception

- Interframe Space

CAN module uses RB3/CANRX and RB2/CANTX/INT2 pins to interface with CAN bus. In order to configure CANRX and CANTX as CAN interface:

- bit TRISB<3> must be set;

- bit TRISB<2> must be cleared.

#### 19.1.2 TRANSMIT/RECEIVE BUFFERS

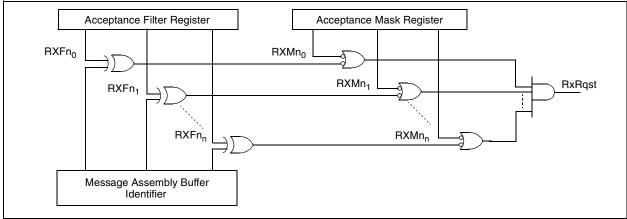

The PIC18FXX8 has three transmit and two receive buffers, two acceptance masks (one for each receive buffer) and a total of six acceptance filters. Figure 19-1 is a block diagram of these buffers and their connection to the protocol engine.

# 19.2.3.1 Message Acceptance Filters and Masks

This subsection describes the message acceptance filters and masks for the CAN receive buffers.

#### REGISTER 19-21: RXFnSIDH: RECEIVE ACCEPTANCE FILTER n STANDARD IDENTIFIER FILTER, HIGH BYTE REGISTERS

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SID10 | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7-0 SID10:SID3: Standard Identifier Filter bits if EXIDEN = 0 or Extended Identifier Filter bits EID28:EID21 if EXIDEN = 1

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 19-22: RXFnSIDL: RECEIVE ACCEPTANCE FILTER n STANDARD IDENTIFIER FILTER, LOW BYTE REGISTERS

|         | R/W-x                                        | R/W-x       | R/W-x           | U-0                              | R/W-x  | U-0 | R/W-x | R/W-x |  |  |

|---------|----------------------------------------------|-------------|-----------------|----------------------------------|--------|-----|-------|-------|--|--|

|         | SID2                                         | SID1        | SID0            | _                                | EXIDEN | _   | EID17 | EID16 |  |  |

|         | bit 7                                        |             |                 |                                  |        |     |       | bit 0 |  |  |

| bit 7-5 |                                              |             |                 | er bits if EXII<br>0:EID18 if EX |        |     |       |       |  |  |

| bit 4   | Unimplem                                     | ented: Read | <b>d as</b> '0' |                                  |        |     |       |       |  |  |

| bit 3   | EXIDEN: E                                    | xtended Ide | ntifier Filter  | Enable bit                       |        |     |       |       |  |  |

|         |                                              | •           | •               | ID message<br>ID message         |        |     |       |       |  |  |

| bit 2   | Unimplem                                     | ented: Read | <b>d as</b> '0' |                                  |        |     |       |       |  |  |

| bit 1-0 | EID17:EID16: Extended Identifier Filter bits |             |                 |                                  |        |     |       |       |  |  |

|         |                                              |             |                 |                                  |        |     |       |       |  |  |

|         | Legend:                                      |             |                 |                                  |        |     |       |       |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

### 19.6 Message Acceptance Filters and Masks

The message acceptance filters and masks are used to determine if a message in the message assembly buffer should be loaded into either of the receive buffers. Once a valid message has been received into the MAB, the identifier fields of the message are compared to the filter values. If there is a match, that message will be loaded into the appropriate receive buffer. The filter masks are used to determine which bits in the identifier are examined with the filters. A truth table is shown below in Table 19-2 that indicates how each bit in the identifier is compared to the masks and filters to determine if a message should be loaded into a receive buffer. The mask essentially determines which bits to apply the acceptance filters to. If any mask bit is set to a zero, then that bit will automatically be accepted regardless of the filter bit.

| Mask<br>bit n | Filter bit n | Message<br>Identifier<br>bit n001 | Accept or<br>Reject<br>bit n |

|---------------|--------------|-----------------------------------|------------------------------|

| 0             | х            | x                                 | Accept                       |

| 1             | 0            | 0                                 | Accept                       |

| 1             | 0            | 1                                 | Reject                       |

| 1             | 1            | 0                                 | Reject                       |

| 1             | 1            | 1                                 | Accept                       |

TABLE 19-2: FILTER/MASK TRUTH TABLE

**Legend:** x = don't care

As shown in the receive buffer block diagram (Figure 19-4), acceptance filters RXF0 and RXF1 and filter mask RXM0 are associated with RXB0. Filters RXF2, RXF3, RXF4 and RXF5 and mask RXM1 are associated with RXB1. When a filter matches and a message is loaded into the receive buffer, the filter number that enabled the message reception is loaded into the FILHIT bit(s).

For RXB1, the RXB1CON register contains the FILHIT<2:0> bits. They are coded as follows:

- 101 = Acceptance Filter 5 (RXF5)

- 100 = Acceptance Filter 4 (RXF4)

- 011 = Acceptance Filter 3 (RXF3)

- 010 = Acceptance Filter 2 (RXF2)

- 001 = Acceptance Filter 1 (RXF1)

- 000 = Acceptance Filter 0 (RXF0)

Note: '000' and '001' can only occur if the RXB0DBEN bit is set in the RXB0CON register allowing RXB0 messages to rollover into RXB1.

The coding of the RXB0DBEN bit enables these three bits to be used similarly to the FILHIT bits and to distinguish a hit on filter RXF0 and RXF1, in either RXB0, or after a rollover into RXB1.

- 111 = Acceptance Filter 1 (RXF1)

- 110 = Acceptance Filter 0 (RXF0)

- 001 = Acceptance Filter 1 (RXF1)

- 000 = Acceptance Filter 0

If the RXB0DBEN bit is clear, there are six codes corresponding to the six filters. If the RXB0DBEN bit is set, there are six codes corresponding to the six filters plus two additional codes corresponding to RXF0 and RXF1 filters that rollover into RXB1.

If more than one acceptance filter matches, the FILHIT bits will encode the binary value of the lowest numbered filter that matched. In other words, if filter RXF2 and filter RXF4 match, FILHIT will be loaded with the value for RXF2. This essentially prioritizes the acceptance filters with a lower number filter having higher priority. Messages are compared to filters in ascending order of filter number.

The mask and filter registers can only be modified when the PIC18FXX8 is in Configuration mode. The mask and filter registers cannot be read outside of Configuration mode. When outside of Configuration mode, all mask and filter registers will be read as '0'.

#### FIGURE 19-6: MESSAGE ACCEPTANCE MASK AND FILTER OPERATION

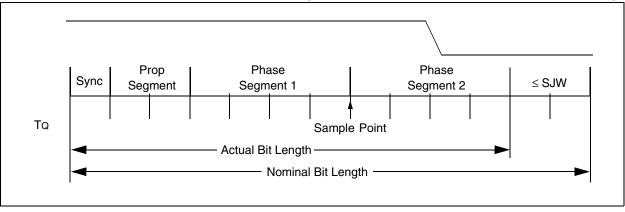

# 19.9 Programming Time Segments

Some requirements for programming of the time segments:

- Prop Seg + Phase Seg 1 ≥ Phase Seg 2

- Phase Seg 2 ≥ Sync Jump Width

For example, assume that a 125 kHz CAN baud rate is desired using 20 MHz for Fosc. With a Tosc of 50 ns, a baud rate prescaler value of 04h gives a TQ of 500 ns. To obtain a nominal bit rate of 125 kHz, the nominal bit time must be 8  $\mu$ s or 16 TQ.

Using 1 TQ for the Sync Segment, 2 TQ for the Propagation Segment and 7 TQ for Phase Segment 1 would place the sample point at 10 TQ after the transition. This leaves 6 TQ for Phase Segment 2.

By the rules above, the Sync Jump Width could be the maximum of 4 Tq. However, normally a large SJW is only necessary when the clock generation of the different nodes is inaccurate or unstable, such as using ceramic resonators. Typically, an SJW of 1 is enough.

#### 19.10 Oscillator Tolerance

As a rule of thumb, the bit timing requirements allow ceramic resonators to be used in applications with transmission rates of up to 125 Kbit/sec. For the full bus speed range of the CAN protocol, a quartz oscillator is required. A maximum node-to-node oscillator variation of 1.7% is allowed.

# 19.11 Bit Timing Configuration Registers

The Configuration registers (BRGCON1, BRGCON2, BRGCON3) control the bit timing for the CAN bus interface. These registers can only be modified when the PIC18FXX8 is in Configuration mode.

# 19.11.1 BRGCON1

The BRP bits control the baud rate prescaler. The SJW < 1:0 > bits select the synchronization jump width in terms of multiples of Tq.

#### 19.11.2 BRGCON2

The PRSEG bits set the length of the Propagation Segment in terms of TQ. The SEG1PH bits set the length of Phase Segment 1 in TQ. The SAM bit controls how many times the RXCAN pin is sampled. Setting this bit to a '1' causes the bus to be sampled three times; twice at TQ/2 before the sample point and once at the normal sample point (which is at the end of Phase Segment 1). The value of the bus is determined to be the value read during at least two of the samples. If the SAM bit is set to a '0', then the RXCAN pin is sampled only once at the sample point. The SEG2PHTS bit controls how the length of Phase Segment 2 is determined. If this bit is set to a '1', then the length of Phase Segment 2 is determined by the SEG2PH bits of BRGCON3. If the SEG2PHTS bit is set to a '0', then the length of Phase Segment 2 is the greater of Phase Segment 1 and the information processing time (which is fixed at 2 TQ for the PIC18FXX8).

#### 19.11.3 BRGCON3

The PHSEG2<2:0> bits set the length (in TQ) of Phase Segment 2 if the SEG2PHTS bit is set to a '1'. If the SEG2PHTS bit is set to a '0', then the PHSEG2<2:0> bits have no effect.

# **19.12 Error Detection**

The CAN protocol provides sophisticated error detection mechanisms. The following errors can be detected.

#### 19.12.1 CRC ERROR

With the Cyclic Redundancy Check (CRC), the transmitter calculates special check bits for the bit sequence, from the start of a frame until the end of the data field. This CRC sequence is transmitted in the CRC field. The receiving node also calculates the CRC sequence using the same formula and performs a comparison to the received sequence. If a mismatch is detected, a CRC error has occurred and an error frame is generated. The message is repeated.

#### 19.12.2 ACKNOWLEDGE ERROR

In the Acknowledge field of a message, the transmitter checks if the Acknowledge slot (which was sent out as a recessive bit) contains a dominant bit. If not, no other node has received the frame correctly. An Acknowledge Error has occurred; an error frame is generated and the message will have to be repeated.

#### 19.12.3 FORM ERROR

If a node detects a dominant bit in one of the four segments, including end of frame, interframe space, Acknowledge delimiter or CRC delimiter, then a Form Error has occurred and an error frame is generated. The message is repeated.

#### 19.12.4 BIT ERROR

A Bit Error occurs if a transmitter sends a dominant bit and detects a recessive bit, or if it sends a recessive bit and detects a dominant bit, when monitoring the actual bus level and comparing it to the just transmitted bit. In the case where the transmitter sends a recessive bit and a dominant bit is detected during the arbitration field and the Acknowledge slot, no Bit Error is generated because normal arbitration is occurring.

#### 19.12.5 STUFF BIT ERROR

If, between the start of frame and the CRC delimiter, six consecutive bits with the same polarity are detected, the bit stuffing rule has been violated. A Stuff Bit Error occurs and an error frame is generated. The message is repeated.

#### 19.12.6 ERROR STATES

Detected errors are made public to all other nodes via error frames. The transmission of the erroneous message is aborted and the frame is repeated as soon as possible. Furthermore, each CAN node is in one of the three error states "error-active", "error-passive" or "bus-off" according to the value of the internal error counters. The error-active state is the usual state, where the bus node can transmit messages and activate error frames (made of dominant bits) without any restrictions. In the error-passive state, messages and passive error frames (made of recessive bits) may be transmitted. The bus-off state makes it temporarily impossible for the station to participate in the bus communication. During this state, messages can neither be received nor transmitted.

#### 19.12.7 ERROR MODES AND ERROR COUNTERS

The PIC18FXX8 contains two error counters: the Receive Error Counter (RXERRCNT) and the Transmit Error Counter (TXERRCNT). The values of both counters can be read by the MCU. These counters are incremented or decremented in accordance with the CAN bus specification.

The PIC18FXX8 is error-active if both error counters are below the error-passive limit of 128. It is errorpassive if at least one of the error counters equals or exceeds 128. It goes to bus-off if the transmit error counter equals or exceeds the bus-off limit of 256. The device remains in this state until the bus-off recovery sequence is received. The bus-off recovery sequence consists of 128 occurrences of 11 consecutive recessive bits (see Figure 19-10). Note that the CAN module, after going bus-off, will recover back to erroractive without any intervention by the MCU if the bus remains Idle for 128 x 11 bit times. If this is not desired, the error Interrupt Service Routine should address this. The current error mode of the CAN module can be read by the MCU via the COMSTAT register.

Additionally, there is an Error State Warning flag bit, EWARN, which is set if at least one of the error counters equals or exceeds the error warning limit of 96. EWARN is reset if both error counters are less than the error warning limit.

# PIC18FXX8

NOTES:

#### REGISTER 24-11: DEVID1: DEVICE ID REGISTER 1 FOR PIC18FXX8 DEVICES (BYTE ADDRESS 3FFFFEh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-5 **DEV2:DEV0:** Device ID bits These bits are used with the DEV<10:3> bits in the Device ID Register 2 to identify the part number.

000 = PIC18F248

001 = PIC18F448

010 = PIC18F258

011 = PIC18F458

bit 4-0 REV4:REV0: Revision ID bits

These bits are used to indicate the device revision.

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

#### REGISTER 24-12: DEVID2: DEVICE ID REGISTER 2 FOR PIC18FXX8 DEVICES (BYTE ADDRESS 3FFFFFh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0 DEV10:DEV3: Device ID bits

These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.

00001000 = PIC18FXX8

| Legend:               |                      |                                     |

|-----------------------|----------------------|-------------------------------------|

| R = Readable bit      | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

# PIC18FXX8

| DEC                | FSZ                    | Decrement                                                                                                                                                | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                       |  |

|--------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|--|

| Synta              | ax:                    | [label] DE                                                                                                                                               | ECFSZ f[,o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | d [,a]] |                       |  |

| Oper               | ands:                  | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                      | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                       |  |

| Oper               | ation:                 | (f) – 1 $\rightarrow$ de skip if resul                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                       |  |

| Statu              | is Affected:           | None                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                       |  |

| Enco               | oding:                 | 0010                                                                                                                                                     | 11da f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | fff     | ffff                  |  |

| Desc               | ription:               | decremente<br>placed in W<br>placed back<br>If the result<br>which is alru<br>and a NOP i<br>it a two-cycl<br>Access Bar<br>overriding th<br>then the ba | The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If the result is '0', the next instruction<br>which is already fetched is discarded<br>and a NOP is executed instead, making<br>it a two-cycle instruction. If 'a' is '0', the<br>Access Bank will be selected,<br>overriding the BSR value. If 'a' = 1,<br>then the bank will be selected as per<br>the BSR value (default). |         |                       |  |

| Word               | ls:                    | 1                                                                                                                                                        | · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                       |  |

| Cycle              | es:                    |                                                                                                                                                          | vcles if skip<br>a 2-word ins                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |                       |  |

| QC                 | ycle Activity:         |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                       |  |

|                    | Q1                     | Q2                                                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | Q4                    |  |

|                    | Decode                 | Read<br>register 'f'                                                                                                                                     | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -       | Vrite to<br>stination |  |

| lf sl              | kip:                   |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                       |  |

|                    | Q1                     | Q2                                                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | Q4                    |  |

|                    | No<br>operation        | No<br>operation                                                                                                                                          | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | or      | No<br>peration        |  |

| lf sk              |                        | d by 2-word in                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0       |                       |  |

|                    | Q1                     | Q2                                                                                                                                                       | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | Q4                    |  |

|                    | No                     | No                                                                                                                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | No                    |  |

|                    | operation              | operation                                                                                                                                                | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | op      | peration              |  |

|                    | No                     | No                                                                                                                                                       | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | No                    |  |

|                    | operation              | operation                                                                                                                                                | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | op      | peration              |  |

| <u>Example:</u>    |                        | HERE<br>CONTINUE                                                                                                                                         | GOTO LOOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                       |  |

| Before Instruction |                        |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                       |  |

|                    |                        | = Address                                                                                                                                                | S (HERE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                       |  |

|                    | CNT                    | = CNT                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                       |  |

|                    | If CNT<br>PC<br>If CNT | = 0;<br>= Address<br>≠ 0;                                                                                                                                | G (CONTIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | UE)     |                       |  |

|                    | PC                     | = Address                                                                                                                                                | S (HERE +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2)      |                       |  |

| DCFSNZ Decrement f, Skip if not 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |                                                     |                 |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------|-----------------|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | [label] D                               | CFSNZ f[,d                                          | [,a]]           |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]   | d ∈ [0,1]                                           |                 |  |  |

| Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (f) – 1 $\rightarrow$ d<br>skip if resu |                                                     |                 |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | None                                    |                                                     |                 |  |  |

| Encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0100                                    | 11da ff                                             | ff ffff         |  |  |

| Description: The contents of register 'f' are<br>decremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If the result is not '0', the next<br>instruction which is already fetched is<br>discarded and a NOP is executed<br>instead, making it a two-cycle<br>instruction. If 'a' is '0', the Access Bank<br>will be selected, overriding the BSR<br>value. If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |                                         |                                                     |                 |  |  |

| Words:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                       |                                                     |                 |  |  |

| Cycles:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1(2)                                    |                                                     |                 |  |  |