Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

|                            |                                                                         |

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, UART/USART                                   |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 40                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 512 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 7x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p80c554sfbd-157 |

|                            |                                                                         |

80C51 8-bit microcontroller – 6-clock operation 16K/512 OTP/ROMless, 7 channel 10 bit A/D, I<sup>2</sup>C, PWM, capture/compare, high I/O, 64L LQFP

80C554/87C554

#### ORDERING INFORMATION

| OTP/EPROM   | ROMIess     | TEMPERATURE °C AND PACKAGE                | FREQ.<br>(MHz) | DRAWING<br>NUMBER |

|-------------|-------------|-------------------------------------------|----------------|-------------------|

| P87C554SBBD | P80C554SBBD | 0 to +70, Low Profile Quad Flat Package   | 16             | SOT314-2          |

| P87C554SFBD | P80C554SFBD | -40 to +85, Low Profile Quad Flat Package | 16             | SOT314-2          |

## PART NUMBER DERIVATION

| DEVICE NUMBER   | OPERATING FREQUENCY MAX | TEMPERATURE RANGE                    | PACKAGE     |

|-----------------|-------------------------|--------------------------------------|-------------|

| P87C554 OTP     | S = 16 MHz              | B= 0°C to 70°C                       | BD=64L LQFP |

| P80C554 ROMless | 3 = 10 MINZ             | $F = -40^{\circ}C$ to $+85^{\circ}C$ | DD=04L LQFP |

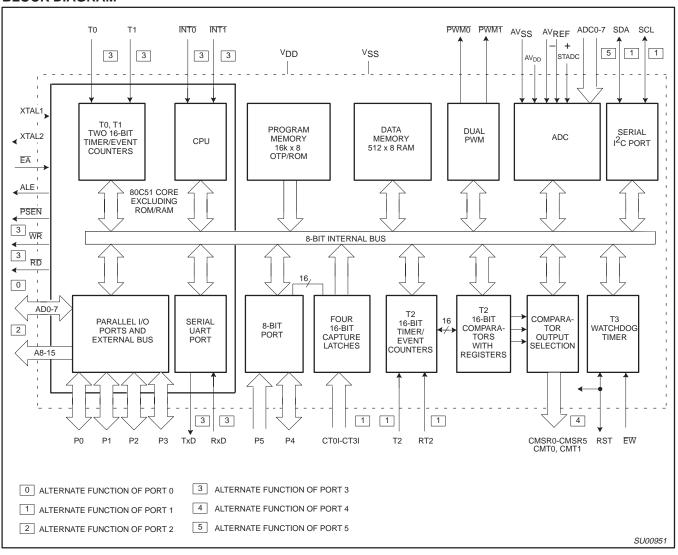

## **BLOCK DIAGRAM**

80C554/87C554

| SYMBOL                                     | DESCRIPTION                                                                | DIRECT<br>ADDRESS                      | MSB    | ВІТ   | ADDRESS, S | SYMBOL, OR | ALTERNATIV | E PORT FUN | ICTION | LSB          | RESET<br>VALUE                  |

|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|--------|-------|------------|------------|------------|------------|--------|--------------|---------------------------------|

| P1M1                                       | Port 1 output mode 1                                                       | 92H                                    |        |       |            |            |            |            |        |              | xx000000B                       |

| P1M2                                       | Port 1 output mode 2                                                       | 93H                                    |        |       |            |            |            |            |        |              | xx000000B                       |

| P2M1                                       | Port 2 output mode 1                                                       | 94H                                    |        |       |            |            |            |            |        |              | 00H                             |

| P2M2                                       | Port 2 output mode 2                                                       | 95H                                    |        |       |            |            |            |            |        |              | 00H                             |

| P3M1                                       | Port 3 output mode 1                                                       | 9AH                                    |        |       |            |            |            |            |        |              | 00H                             |

| P3M2                                       | Port 3 output mode 2                                                       | 9BH                                    |        |       |            |            |            |            |        |              | 00H                             |

| P4M1                                       | Port 4 output mode 1                                                       | 9CH                                    |        |       |            |            |            |            |        |              | 00H                             |

| P4M2                                       | Port 4 output mode 2                                                       | 9DH                                    |        |       |            |            |            |            | _      |              | 00H                             |

| PCON                                       | Power control                                                              | 87H                                    | SMOD1  | SMOD0 | POF        | WLE        | GF1        | GFO        | PD     | IDL          | 00x00000B                       |

| PSW                                        | Program status word                                                        | D0H                                    | CY     | AC    | FO         | RS1        | RS0        | OV         | F1     | Р            | 00H                             |

| PWMP#                                      | PWM prescaler                                                              | FEH                                    |        |       |            | -          | -          | -          | -      |              | 00H                             |

| PWM1#                                      | PWM register 1                                                             | FDH                                    |        |       |            |            |            |            |        |              | 00H                             |

| PWM0#                                      | PWM register 0                                                             | FCH                                    |        |       |            |            |            |            |        |              | 00H                             |

| RTE#                                       | Reset/toggle enable                                                        | EFH                                    | TP47   | TP46  | RP45       | RP44       | RP43       | RP42       | RP41   | RP40         | 00H                             |

| S0ADDR                                     | Serial 0 slave address                                                     | F9H                                    |        |       |            | -          | -          |            |        |              | 00H                             |

| S0ADEN                                     | Slave address mask                                                         | В9Н                                    |        |       |            |            |            |            |        |              | 00H                             |

| S0BUF                                      | Serial 0 data buffer                                                       | 99H                                    |        |       |            |            |            |            |        |              | xxxxxxxxB                       |

|                                            |                                                                            |                                        | 9F     | 9E    | 9D         | 9C         | 9B         | 9A         | 99     | 98           |                                 |

| S0CON*                                     | Serial 0 control                                                           | 98H                                    | SM0/FE | SM1   | SM2        | REN        | TB8        | RB8        | TI     | RI           | 00H                             |

| S1ADR#                                     | Serial 1 address                                                           | DBH                                    |        |       | SL         | AVE ADDRE  | SS         |            |        | GC           | 00H                             |

| SIDAT#                                     | Serial 1 data                                                              | DAH                                    |        |       |            |            |            |            |        | •            | 00H                             |

| S1STA#                                     | Serial 1 status                                                            | D9H                                    | SC4    | SC3   | SC2        | SC1        | SC0        | 0          | 0      | 0            | F8H                             |

|                                            |                                                                            |                                        | DF     | DE    | DD         | DC         | DB         | DA         | D9     | D8           | 1                               |

| SICON#*                                    | Serial 1 control                                                           | D8H                                    | CR2    | ENS1  | STA        | ST0        | SI         | AA         | CR1    | CR0          | 00H                             |

| SP                                         | Stack pointer                                                              | 81H                                    |        |       |            |            |            |            |        |              | 07H                             |

| STE#                                       | Set enable                                                                 | EEH                                    | TG47   | TG46  | SP45       | SP44       | SP43       | SP42       | SP41   | SP40         | C0H                             |

| TH1<br>TH0<br>TL1<br>TL0<br>TMH2#<br>TML2# | Timer high 1 Timer high 0 Timer low 1 Timer low 0 Timer high 2 Timer low 2 | 8DH<br>8CH<br>8BH<br>8AH<br>EDH<br>ECH |        |       |            |            |            |            |        |              | 00H<br>00H<br>00H<br>00H<br>00H |

| TMOD                                       | Timer mode                                                                 | 89H                                    | GATE   | C/T   | M1         | MO         | GATE       | C/T        | M1     | M0           | 00H                             |

|                                            |                                                                            |                                        | 8F     | 8E    | 8D         | 8C         | 8B         | 8A         | 89     | 88           | 1                               |

| TCON*                                      | Timer control                                                              | 88H                                    | TF1    | TR1   | TF0        | TR0        | IE1        | IT1        | IE0    | IT0          | 00H                             |

| TM2CON#                                    | Timer 2 control                                                            | EAH                                    | T2IS1  | T2IS0 | T2ER       | T2B0       | T2P1       | T2P0       | T2MS1  | T2MS0        | 00H                             |

|                                            |                                                                            |                                        | CF     | CE    | CD         | CC         | СВ         | CA         | C9     | C8           | 1                               |

| TM2IR#*                                    | Timer 2 int flag reg                                                       | C8H                                    | T20V   | CMI2  | CMI1       | CMI0       | CTI3       | CTI2       | CTI1   | CTI0         | 00H                             |

| T3#                                        | Timer 3                                                                    | FFH                                    |        | =     | =          | -          | -          | -          | -      | <del>-</del> | 00H                             |

<sup>\*</sup> SFRs are bit addressable.

<sup>#</sup> SFRs are modified from or added to the 80C51 SFRs.

80C51 8-bit microcontroller – 6-clock operation 16K/512 OTP/ROMless, 7 channel 10 bit A/D, I<sup>2</sup>C, PWM, capture/compare, high I/O, 64L LQFP

80C554/87C554

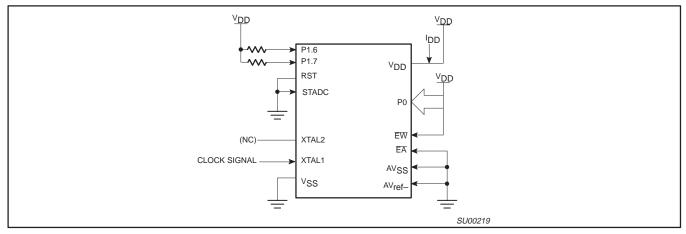

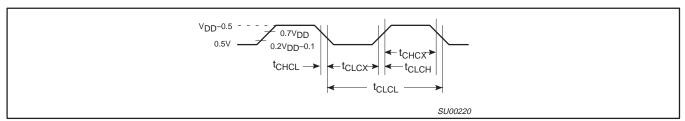

#### OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator, as shown in the logic symbol.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. The minimum and maximum high and low times specified in the data sheet must be observed.

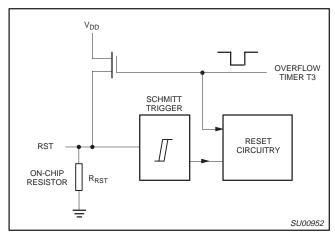

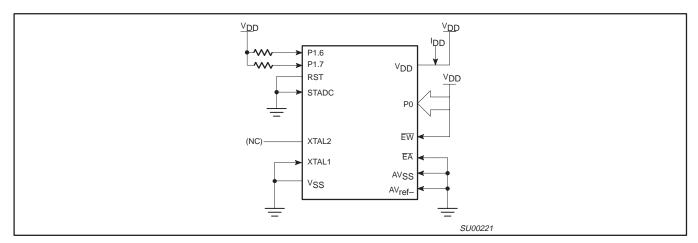

## **RESET**

A reset is accomplished by either (1) externally holding the RST pin high for at least two machine cycles (12 oscillator periods) or (2) internally by an on-chip power-on detect (POD) circuit which detects  $V_{CC}$  ramping up from 0 V.

To insure a good external power-on reset, the RST pin must be high long enough for the oscillator to start up (normally a few milliseconds) plus two machine cycles. The voltage on  $V_{DD}$  and the RST pin must come up at the same time for a proper startup.

For a successful internal power-on reset, the  $V_{\rm CC}$  voltage must ramp up from 0 V smoothly at a ramp rate greater than 5 V/100 ms.

The RST line can also be pulled HIGH internally by a pull-up transistor activated by the watchdog timer T3. The length of the output pulse from T3 is 3 machine cycles. A pulse of such short duration is necessary in order to recover from a processor or system fault as fast as possible.

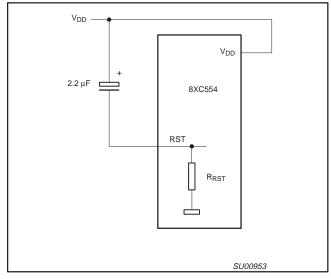

Note that the short reset pulse from Timer T3 cannot discharge the power-on reset capacitor (see Figure 2). Consequently, when the watchdog timer is also used to set external devices, this capacitor arrangement should not be connected to the RST pin, and a different circuit should be used to perform the power-on reset operation. A timer T3 overflow, if enabled, will force a reset condition to the 8xC554 by an internal connection, independent of the level of the RST pin.

A reset may be performed in software by setting the software reset bit, SRST (AUXR1.5).

Figure 1. On-Chip Reset Configuration

Figure 2. Power-On Reset

### **LOW POWER MODES**

### **Stop Clock Mode**

The static design enables the clock speed to be reduced down to 0 MHz (stopped). When the oscillator is stopped, the RAM and Special Function Registers retain their values. This mode allows step-by-step utilization and permits reduced system power consumption by lowering the clock frequency down to any value. For lowest power consumption the Power Down mode is suggested.

## **Idle Mode**

In the idle mode (see Table 2), the CPU puts itself to sleep while some of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

#### **Power-Down Mode**

To save even more power, a Power Down mode (see Table 2) can be invoked by software. In this mode, the oscillator is stopped and the instruction that invoked Power Down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values down to 2.0 V and care must be taken to return  $V_{CC}$  to the minimum specified operating voltages before the Power Down Mode is terminated.

Either a hardware reset or external interrupt can be used to exit from Power Down. The Wake-up from Power-down bit, WUPD (AUXR1.3) must be set in order for an external interrupt to cause a wake-up from power-down. Reset redefines all the SFRs but does not change the on-chip RAM. An external interrupt allows both the SFRs and the on-chip RAM to retain their values.

To properly terminate Power Down the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize (normally less than 10 ms).

80C51 8-bit microcontroller – 6-clock operation 16K/512 OTP/ROMless, 7 channel 10 bit A/D, I<sup>2</sup>C, PWM, capture/compare, high I/O, 64L LQFP

80C554/87C554

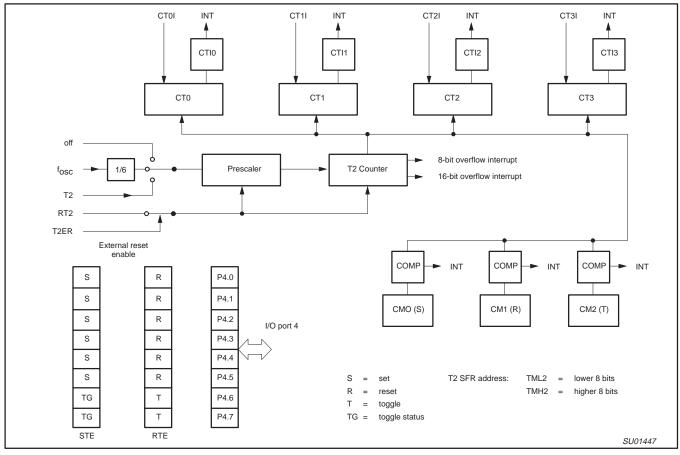

Figure 13. Block Diagram of Timer 2

Capture Logic: The four 16-bit capture registers that Timer T2 is connected to are: CT0, CT1, CT2, and CT3. These registers are loaded with the contents of Timer T2, and an interrupt is requested upon receipt of the input signals CT0I, CT1I, CT2I, or CT3I. These input signals are shared with port 1. The four interrupt flags are in the Timer T2 interrupt register (TM2IR special function register). If the capture facility is not required, these inputs can be regarded as additional external interrupt inputs.

Using the capture control register CTCON (see Figure 14), these inputs may capture on a rising edge, a falling edge, or on either a rising or falling edge. The inputs are sampled during S1P1 of each cycle. When a selected edge is detected, the contents of Timer T2 are captured at the end of the cycle.

**Measuring Time Intervals Using Capture Registers:** When a recurring external event is represented in the form of rising or falling edges on one of the four capture pins, the time between two events

can be measured using Timer T2 and a capture register. When an event occurs, the contents of Timer T2 are copied into the relevant capture register and an interrupt request is generated. The interrupt service routine may then compute the interval time if it knows the previous contents of Timer T2 when the last event occurred. With a 12-MHz oscillator, Timer T2 can be programmed to overflow every 524 ms. When event interval times are shorter than this, computing the interval time is simple, and the interrupt service routine is short. For longer interval times, the Timer T2 extension routine may be used.

Compare Logic: Each time Timer T2 is incremented, the contents of the three 16-bit compare registers CM0, CM1, and CM2 are compared with the new counter value of Timer T2. When a match is found, the corresponding interrupt flag in TM2IR is set at the end of the following cycle. When a match with CM0 occurs, the controller sets bits 0-5 of port 4 if the corresponding bits of the set enable register STE are at logic 1.

80C51 8-bit microcontroller – 6-clock operation 16K/512 OTP/ROMless, 7 channel 10 bit A/D, I<sup>2</sup>C, PWM, capture/compare, high I/O, 64L LQFP

80C554/87C554

Reset Value = 00H

During the early stages of software development/debugging, the watchdog may be disabled by tying the  $\overline{EW}$  pin high. At a later stage,  $\overline{EW}$  may be tied low to complete the debugging process.

**Watchdog Software Example:** The following example shows how watchdog operation might be handled in a user program.

;at the program start:

T3 EQU 0FFH ;address of watchdog timer T3

PCON EQU 087H ;address of PCON SFR

WATCH-INTV EQU 156 ;watchdog interval (e.g., 100 ms)

;to be inserted at each watchdog reload location within ;the user program:

LCALL WATCHDOG

;watchdog service routine:

WATCHDOG: ORL PCON,#10H ;set condition flag (PCON.4)

MOV T3,WATCH-INV ;load T3 with watchdog interval

RET

If it is possible for this subroutine to be called in an erroneous state, then the condition flag WLE should be set at different parts of the main program.

#### Serial I/O

The 8xC554 is equipped with two independent serial ports: SIO0 and SIO1. SIO0 is a full duplex UART port and is similar to the Enhanced UART serial port. SIO1 accommodates the I<sup>2</sup>C bus.

**SIO0:** SIO0 is a full duplex serial I/O port identical to that of the Enhanced UART except Time 2 cannot be used as a baud rate generator. Its operation is the same, including the use of timer 1 as a baud rate generator.

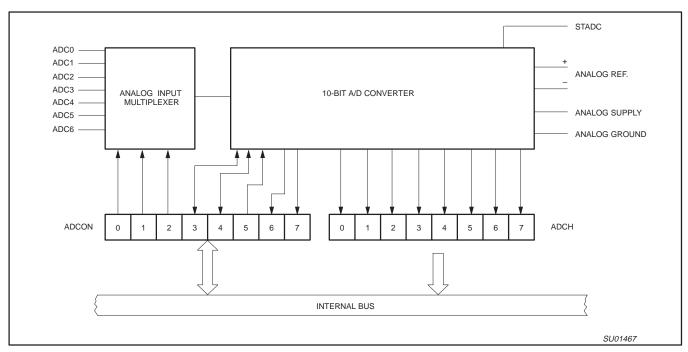

## Port 5 Operation

Port 5 may be used to input up to 8 analog signals to the ADC. Unused ADC inputs may be used to input digital inputs. These inputs have an inherent hysteresis to prevent the input logic from drawing excessive current from the power lines when driven by analog signals. Channel to channel crosstalk (Ct) should be taken into consideration when both analog and digital signals are simultaneously input to Port 5 (see, D.C. characteristics in data sheet)

Port 5 is not bidirectional and may not be configured as an output port. All six ports are multifunctional, and their alternate functions are listed in the Pin Descriptions section of this datasheet.

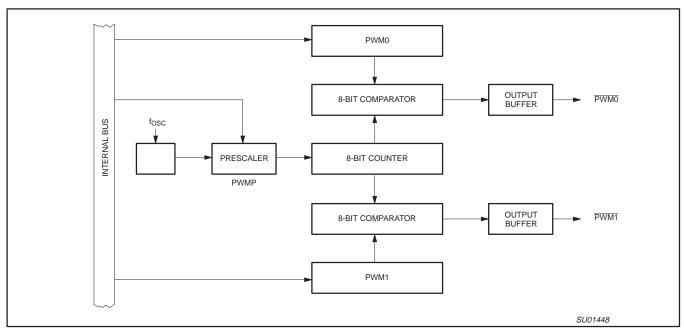

## **Pulse Width Modulated Outputs**

The 8xC554 contains two pulse width modulated output channels (see Figure 19). These channels generate pulses of programmable length and interval. The repetition frequency is defined by an 8-bit prescaler PWMP, which supplies the clock for the counter. The prescaler and counter are common to both PWM channels. The 8-bit counter counts modulo 255, i.e., from 0 to 254 inclusive. The value of the 8-bit counter is compared to the contents of two registers: PWM0 and PWM1. Provided the contents of either of these registers is greater than the counter value, the corresponding PWM0 or PWM1 output is set LOW. If the contents of these registers are equal to, or less than the counter value, the output will be HIGH. The pulse-width-ratio is therefore defined by the contents of the registers PWM0 and PWM1. The pulse-width-ratio is in the range of 0 to 1 and may be programmed in increments of 1/255.

Buffered PWM outputs may be used to drive DC motors. The rotation speed of the motor would be proportional to the contents of PWMn. The PWM outputs may also be configured as a dual DAC. In this application, the PWM outputs must be integrated using conventional operational amplifier circuitry. If the resulting output voltages have to be accurate, external buffers with their own analog supply should be used to buffer the PWM outputs before they are integrated. The repetition frequency f<sub>PWM</sub>, at the PWMn outputs is give by:

$$f_{PWM} = \frac{f_{OSC}}{(1 + PWMP) \times 255}$$

This gives a repetition frequency range of 246 Hz to 62.8 kHz ( $f_{OSC} = 16$  MHz). At  $f_{OSC} = 24$  MHz, the frequency range is 368 Hz to 83.4 Hz. By loading the PWM registers with either 00H or FFH, the PWM channels will output a constant HIGH or LOW level, respectively. Since the 8-bit counter counts modulo 255, it can never actually reach the value of the PWM registers when they are loaded with FFH.

When a compare register (PWM0 or PWM1) is loaded with a new value, the associated output is updated immediately. It does not have to wait until the end of the current counter period. Both  $\overline{\text{PWMn}}$  output pins are driven by push-pull drivers. These pins are not used for any other purpose.

Prescaler frequency control register PWMP Reset Value = 00H

| PWMP (FEH) | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|------------|-----|---|---|---|---|---|---|-----|

|            | MSB |   |   |   |   |   |   | LSB |

PWMP.0-7 Prescaler division factor = PWMP + 1.

Reading PWMP gives the current reload value. The actual count of the prescaler cannot be read.

PWM0 (FCH) 7 6 5 4 3 2 1 0

MSB LSB

PWM0/1.0-7} Low/high ratio of

$$\overline{PWMn} = \frac{(PWMn)}{255 - (PWMn)}$$

#### **Analog-to-Digital Converter**

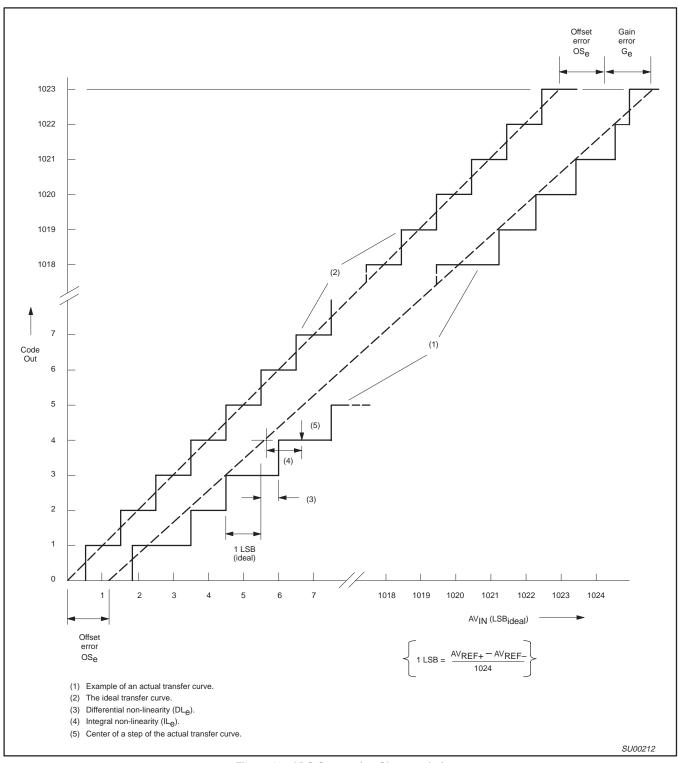

The analog input circuitry consists of an 8-input analog multiplexer and a 10-bit, straight binary, successive approximation ADC. The A/D can also be operated in 8-bit mode with faster conversion times by setting bit ADC8 (AUXR1.7). The 8-bit results will be contained in the ADCH register. The analog reference voltage and analog power supplies are connected via separate input pins. For 10-bit accuracy, the conversion takes 50 machine cycles, i.e., 18.75  $\mu s$  at an oscillator frequency of 16 MHz, 12.5  $\mu s$  at an oscillator frequency of 24 MHz. For the 8-bit mode, the conversion takes 24 machine cycles. Input voltage swing is from 0 V to +5 V. Because the internal DAC employs a ratiometric potentiometer, there are no discontinuities in the converter characteristic. Figure 20 shows a functional diagram of the analog input circuitry.

The ADC has the option of either being powered off in idle mode for reduced power consumption or being active in idle mode for reducing internal noise during the conversion. This option is selected by the AIDL bit of AUXR1 register (AUXR1.6). With the AIDL bit set, the ADC is active in the idle mode, and with the AIDL bit cleared, the ADC is powered off in idle mode.

80C554/87C554

Figure 19. Functional Diagram of Pulse Width Modulated Outputs

Figure 20. Functional Diagram of Analog Input Circuitry

10-Bit Analog-to-Digital Conversion: Figure 21 shows the elements of a successive approximation (SA) ADC. The ADC contains a DAC which converts the contents of a successive approximation register to a voltage (VDAC) which is compared to the analog input voltage (Vin). The output of the comparator is fed to the successive approximation control logic which controls the successive approximation register. A conversion is initiated by setting ADCS in the ADCON register. ADCS can be set by software only or by either hardware or software.

The software only start mode is selected when control bit ADCON.5 (ADEX) = 0. A conversion is then started by setting control bit ADCON.3 (ADCS). The hardware or software start mode is selected when ADCON.5 = 1, and a conversion may be started by setting ADCON.3 as above or by applying a rising edge to external pin STADC. When a conversion is started by applying a rising edge, a low level must be applied to STADC for at least one machine cycle followed by a high level for at least one machine cycle.

80C554/87C554

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                          | 5                          | 4        | 3         | 2                            | 1                                                                                | 0            | Reset Value = xx00 000 |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------|-----------|------------------------------|----------------------------------------------------------------------------------|--------------|------------------------|--|

|                               | ADCON (                                                                                                                                                                                                                                                                                                                                                                                                                | (C5H)                                                                                                                                                                                                                                  | ADC.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ADC.0                      | ADEX                       | ADCI     | ADCS      | AADR2                        | AADR1                                                                            | AADR0        |                        |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                        | (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |                            |          |           | '                            |                                                                                  | (LSB)        |                        |  |

| Bit                           | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                 | Fun                                                                                                                                                                                                                                    | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |                            |          |           |                              |                                                                                  |              |                        |  |

| ADCON.7<br>ADCON.6<br>ADCON.5 | ADC.0                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 0 d<br>Enabl<br>0 = C                                                                                                                                                                                                              | of ADC resof ADC resof aDC resof aDC resofred on the contract of the contract of the contract on the contract of the contract on the contract of the contract | ult<br>start of c          | arted by                   | y softwa | re only ( |                              |                                                                                  | edge on STA  | .DC)                   |  |

| ADCON.4                       | ADCI                                                                                                                                                                                                                                                                                                                                                                                                                   | invok                                                                                                                                                                                                                                  | NDC interrupt flag: this flag is set when an A/D conversion result is ready to be read. An interrupt is novoked if it is enabled. The flag may be cleared by the interrupt service routine. While this flag is set, the ADC cannot start a new conversion. ADCI cannot be set by software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |                            |          |           |                              |                                                                                  |              |                        |  |

| ADCON.3                       | DN.3 ADCS ADC start and status: setting this bit starts an A/D conversion. It may be set by software or by the external signal STADC. The ADC logic ensures that this signal is HIGH while the ADC is busy. On completion of the conversion, ADCS is reset immediately after the interrupt flag has been set. ADCS cannot be reset by software. A new conversion may not be started while either ADCS or ADCI is high. |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                            |          |           |                              |                                                                                  |              |                        |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                        | ADCI ADCS ADC Status                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                            |          |           |                              |                                                                                  |              |                        |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 ADC not busy; a conversion can be started 0 1 ADC busy; start of a new conversion is blocked 1 0 Conversion completed; start of a new conversion requires ADCI=0 1 1 Conversion completed; start of a new conversion requires ADCI=0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                            |          |           |                              |                                                                                  |              | on requires ADCI=0     |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                        | same                                                                                                                                                                                                                                   | CI is clear<br>channel r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | number m                   | nay be s                   | tarted.  |           |                              | ,                                                                                | a new A/D co | onversion with the     |  |

| ADCON.2<br>ADCON.1<br>ADCON.0 | AADR1                                                                                                                                                                                                                                                                                                                                                                                                                  | eight                                                                                                                                                                                                                                  | gue input analogue panged whe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ort bits o                 | f P5 to                    | be input | to the c  | onverter.                    |                                                                                  | /            |                        |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                        | AADR2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AADR1                      | AAD                        | R0       | Se        | ected An                     | alog Cha                                                                         | nnel         |                        |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                        | 0<br>0<br>0<br>0<br>1<br>1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1 |          |           | ADC1<br>ADC3<br>ADC4<br>ADC4 | 0 (P5.0)<br>1 (P5.1)<br>2 (P5.2)<br>3 (P5.3)<br>4 (P5.4)<br>5 (P5.5)<br>6 (P5.6) |              |                        |  |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                            |          |           |                              |                                                                                  |              | SU01468                |  |

Figure 23. ADC Control Register (ADCON)

80C51 8-bit microcontroller – 6-clock operation 16K/512 OTP/ROMless, 7 channel 10 bit A/D, I<sup>2</sup>C, PWM, capture/compare, high I/O, 64L LQFP

80C554/87C554

If the STA and STO bits are both set, the a STOP condition is transmitted to the I<sup>2</sup>C bus if SIO1 is in a master mode (in a slave mode, SIO1 generates an internal STOP condition which is not transmitted). SIO1 then transmits a START condition.

STO = "0": When the STO bit is reset, no STOP condition will be generated.

SI, THE SERIAL INTERRUPT FLAG

SI = "1": When the SI flag is set, then, if the EA and ES1 (interrupt enable register) bits are also set, a serial interrupt is requested. SI is set by hardware when one of 25 of the 26 possible SIO1 states is entered. The only state that does not cause SI to be set is state F8H, which indicates that no relevant state information is available.

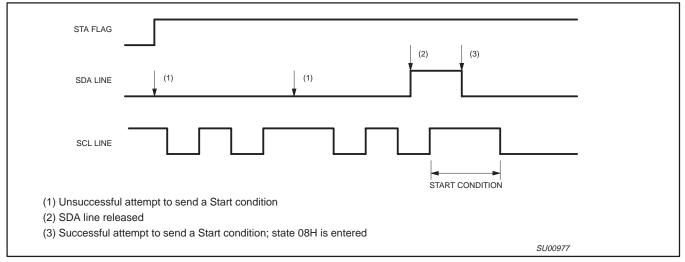

While SI is set, the low period of the serial clock on the SCL line is stretched, and the serial transfer is suspended. A high level on the SCL line is unaffected by the serial interrupt flag. SI must be reset by software.

SI = "0": When the SI flag is reset, no serial interrupt is requested, and there is no stretching of the serial clock on the SCL line.

AA, THE ASSERT ACKNOWLEDGE FLAG

AA = "1": If the AA flag is set, an acknowledge (low level to SDA) will be returned during the acknowledge clock pulse on the SCL line when:

- The "own slave address" has been received

- The general call address has been received while the general call bit (GC) in S1ADR is set

- A data byte has been received while SIO1 is in the master receiver mode

- A data byte has been received while SIO1 is in the addressed slave receiver mode

AA = "0": if the AA flag is reset, a not acknowledge (high level to SDA) will be returned during the acknowledge clock pulse on SCL when:

- A data has been received while SIO1 is in the master receiver mode

- A data byte has been received while SIO1 is in the addressed slave receiver mode

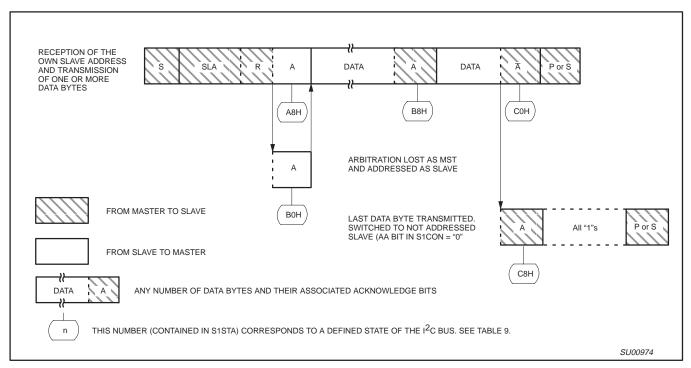

When SIO1 is in the addressed slave transmitter mode, state C8H will be entered after the last serial is transmitted (see Figure 43). When SI is cleared, SIO1 leaves state C8H, enters the not addressed slave receiver mode, and the SDA line remains at a high level. In state C8H, the AA flag can be set again for future address recognition.

When SIO1 is in the not addressed slave mode, its own slave address and the general call address are ignored. Consequently, no acknowledge is returned, and a serial interrupt is not requested. Thus, SIO1 can be temporarily released from the I<sup>2</sup>C bus while the bus status is monitored. While SIO1 is released from the bus, START and STOP conditions are detected, and serial data is shifted in. Address recognition can be resumed at any time by setting the AA flag. If the AA flag is set when the part's own slave address or the general call address has been partly received, the address will be recognized at the end of the byte transmission.

CR0, CR1, AND CR2, THE CLOCK RATE BITS

These three bits determine the serial clock frequency when SIO1 is in a master mode. The various serial rates are shown in Table 5.

A 12.5 kHz bit rate may be used by devices that interface to the  $\rm I^2C$  bus via standard I/O port lines which are software driven and slow. 100 kHz is usually the maximum bit rate and can be derived from a 8 MHz, 6 MHz, or a 3-MHz oscillator. A variable bit rate (0.24 kHz to 62.5 kHz) may also be used if Timer 1 is not required for any other purpose while SIO1 is in a master mode.

The frequencies shown in Table 5 are unimportant when SIO1 is in a slave mode. In the slave modes, SIO1 will automatically synchronize with any clock frequency up to 100 kHz.

The Status Register, S1STA: S1STA is an 8-bit read-only special function register. The three least significant bits are always zero. The five most significant bits contain the status code. There are 26 possible status codes. When S1STA contains F8H, no relevant state information is available and no serial interrupt is requested. All other S1STA values correspond to defined SIO1 states. When each of these states is entered, a serial interrupt is requested (SI = "1"). A valid status code is present in S1STA one machine cycle after SI is set by hardware and is still present one machine cycle after SI has been reset by software.

Table 5. Serial Clock Rates

|     |     |     |                        | BIT FREC               |                        |                        |                        |                                                                        |

|-----|-----|-----|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------------------------------------------------------|

| CR2 | CR1 | CR0 | 3 MHz                  | 6 MHz                  | 8 MHz                  | 12 MHz <sup>2</sup>    | 15 MHz <sup>2</sup>    | f <sub>OSC</sub> DIVIDED BY                                            |

| 0   | 0   | 0   | 23                     | 47                     | 62.5                   | 94                     | 117 <sup>1</sup>       | 128                                                                    |

| 0   | 0   | 1   | 27                     | 54                     | 71                     | 107 <sup>1</sup>       | 134 <sup>1</sup>       | 112                                                                    |

| 0   | 1   | 0   | 31                     | 63                     | 83.3                   | 125 <sup>1</sup>       | 156 <sup>1</sup>       | 96                                                                     |

| 0   | 1   | 1   | 37                     | 75                     | 100                    | 150 <sup>1</sup>       | 188 <sup>1</sup>       | 80                                                                     |

| 1 1 | 0   | 0   | 6.25                   | 12.5                   | 17                     | 25                     | 31                     | 48                                                                     |

| 1 1 | 0   | 1   | 50                     | 100                    | 133 <sup>1</sup>       | 200 <sup>1</sup>       | 250 <sup>1</sup>       | 60                                                                     |

| 1   | 1   | 0   | 100                    | 200                    | 267 <sup>1</sup>       | 400 <sup>1</sup>       | 500 <sup>1</sup>       | 30                                                                     |

| 1   | 1   | 1   | 0.24 < 62.5<br>0 < 255 | 0.49 < 62.5<br>0 < 254 | 0.65 < 55.6<br>0 < 253 | 0.98 < 50.0<br>0 < 251 | 1.22 < 52.1<br>0 < 250 | 48 × (256 – (reload value Timer 1))<br>Reload value Timer 1 in Mode 2. |

#### NOTES

- 1. These frequencies exceed the upper limit of 100 kHz of the I<sup>2</sup>C-bus specification and cannot be used in an I<sup>2</sup>C-bus application.

- 2. At f<sub>OSC</sub> = 12 MHz/15 MHz the maximum I<sup>2</sup>C bus rate of 100 kHz cannot be realized due to the fixed divider rates.

80C554/87C554

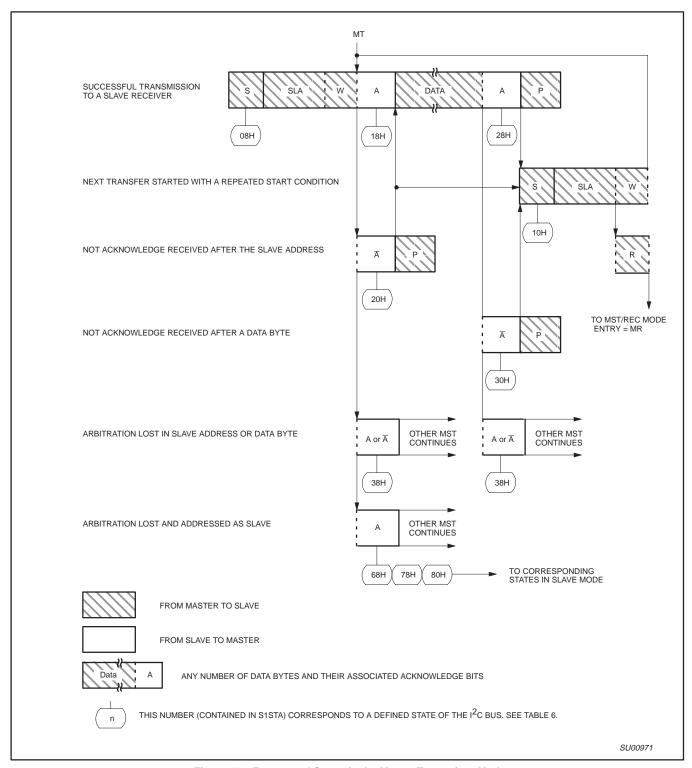

Figure 40. Format and States in the Master Transmitter Mode

80C554/87C554

Figure 43. Format and States of the Slave Transmitter Mode

80C51 8-bit microcontroller – 6-clock operation 16K/512 OTP/ROMless, 7 channel 10 bit A/D,  $I^2C$ , PWM, capture/compare, high I/O, 64L LQFP

80C554/87C554

Table 7. Master Receiver Mode