Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SPI                                                                  |

| Peripherals                | PWM, WDT                                                             |

| Number of I/O              | 13                                                                   |

| Program Memory Size        | 1.5KB (1.5K x 8)                                                     |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 128 x 8                                                              |

| RAM Size                   | 128 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                            |

| Data Converters            | A/D 5x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 16-SOIC (0.154", 3.90mm Width)                                       |

| Supplier Device Package    | 16-SO                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fl09y0mae |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 10.6    |                                                                                         | 40         |

|---------|-----------------------------------------------------------------------------------------|------------|

| 11 ON-0 | CHIP PERIPHERALS                                                                        | 42         |

| 11.1    | LITE TIMER (LT)                                                                         | 42         |

| 11.2    | 12-BIT AUTORELOAD TIMER (AT)                                                            | 47         |

| 11.3    | SERIAL PERIPHERAL INTERFACE (SPI)                                                       | 53         |

| 11.4    | 8-BIT A/D CONVERTER (ADC)                                                               | 63         |

| 12 INST | RUCTION SET                                                                             | 67         |

| 12.1    | ST7 ADDRESSING MODES                                                                    | •          |

| 12.2    | INSTRUCTION GROUPS                                                                      | 70         |

| 13 ELE  |                                                                                         | -          |

| 13.1    | PARAMETER CONDITIONS                                                                    | -          |

| 13.2    | ABSOLUTE MAXIMUM RATINGS                                                                |            |

| 13.3    | OPERATING CONDITIONS                                                                    |            |

| 13.4    | SUPPLY CURRENT CHARACTERISTICS                                                          | 78         |

| 13.5    | CLOCK AND TIMING CHARACTERISTICS                                                        | 8.         |

| 13.6    | MEMORY CHARACTERISTICS                                                                  | 81         |

| 13.7    |                                                                                         |            |

| 13.8    | I/O PORT PIN CHARACTERISTICS                                                            |            |

|         | CONTROL PIN CHARACTERISTICS                                                             |            |

|         | COMMUNICATION INTERFACE CHARACTERISTICS                                                 |            |

|         | 1 8-BIT ADC CHARACTERISTICS                                                             |            |

|         |                                                                                         |            |

|         | PACKAGE MECHANICAL DATA                                                                 |            |

|         | THERMAL CHARACTERISTICS                                                                 |            |

|         | SOLDERING INFORMATION                                                                   |            |

| 15 DEV  | ICE CONFIGURATION AND ORDER IN IC INFORMATION                                           |            |

| 15.1    |                                                                                         |            |

| 15.2    | OPTION BYTES                                                                            | 96         |

|         | FLASH DEVICE CAL'EFING INFORMATION                                                      |            |

| 15.4    |                                                                                         | 98         |

| 16 DEV  | ELOPMENT TOOLS                                                                          |            |

| 16.1    |                                                                                         |            |

| 16.2    |                                                                                         |            |

| 16.3    | P ROGRAMMING TOOLS                                                                      | 101        |

|         | ORDER CODES FOR DEVELOPMENT AND PROGRAMMING TOOLS                                       |            |

|         | ST7 APPLICATION NOTES                                                                   |            |

|         | WN LIMITATIONS                                                                          |            |

|         | EXECUTION OF BTJX INSTRUCTION                                                           |            |

| 17.2    | IN-CIRCUIT PROGRAMMING OF DEVICES PREVIOUSLY PROGRAMMED WITH HA<br>WARE WATCHDOG OPTION | RD-<br>102 |

| 17.3    | IN-CIRCUIT DEBUGGING WITH HARDWARE WATCHDOG                                             | 102        |

| 17.4    | CLEARING ACTIVE INTERRUPTS OUTSIDE INTERRUPT ROUTINE                                    | 102        |

| 18 REV  | ISION HISTORY                                                                           | 103        |

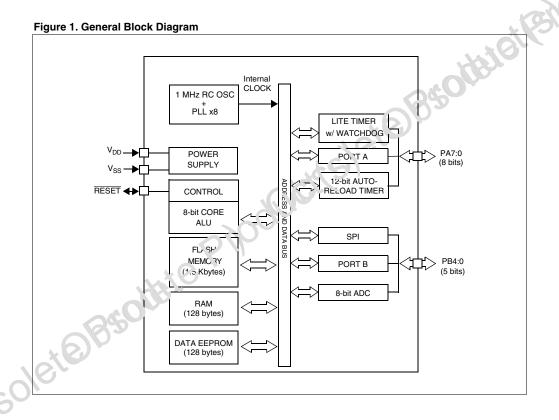

## **1 DESCRIPTION**

57

The ST7L0x is a member of the ST7 microcontroller family suitable for automotive applications. All ST7 devices are based on a common industrystandard 8-bit core, featuring an enhanced instruction set.

The ST7L0x features Flash memory with byte-bybyte In-Circuit Programming (ICP) and In-Application Programming (IAP) capability.

Under software control, the ST7L0x devices can be placed in WAIT, SLOW, or HALT mode, reducing power consumption when the application is in idle or standby state. The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 micro-controllers feature true bit manipulation, 8 x 8 unsigned multiplication and indirect addressing modes.

For easy reference, all parametric data is found in Section 13 on page 73.

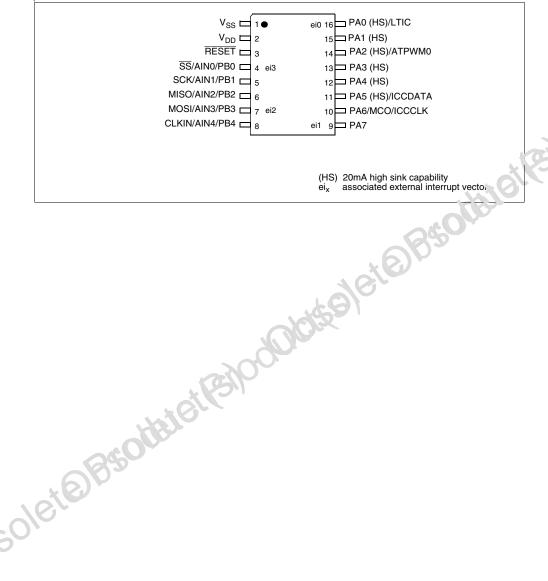

## **2 PIN DESCRIPTION**

## Figure 2. 16-Pin Package Pinout (150mil)

## CPU REGISTERS (Cont'd) CONDITION CODE REGISTER (CC)

Read/Write

Reset Value: 111x1xxx

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | н | I | Ν | z | С |

The 8-bit Condition Code register contains the interrupt mask and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### Bit 4 = H Half carry

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instruction. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 3 = I Interrupt mask

This bit is set by hardware when entering in intrarupt or by software to disable all interrupts covept the TRAP software interrupt. This bit is c' a ed by software.

0: Interrupts are enabled.

1: Interrupts are disabled.

$\nabla$

This bit is controlled by the Ri, 4, sIM and IRET instructions and is tested by the JRM and JRNM instructions.

**Note:** Interrupts requested while I is set are latcher and can be processed when I is cleared. By de ault in interrupt routine is not interruptible

because the I bit is set by hardware at the start of the routine and reset by the IRET instruction at the end of the routine. If the I bit is cleared by software in the interrupt routine, pending interrupts are serviced regardless of the priority level of the current interrupt routine.

## Bit 2 = N Negative

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It is a copy of the  $7^{th}$ bit of the result.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative (that is, the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

#### Bit 1 = Z Zero

This bit is set and cleared by hard ware. This bit indicates that the result of the last arithmetic, logical or data manipulation is  $z_i$  ro.

- 0: The result of the lact operation is different from zero.

- 1: The regult of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

## Bit 0 = C Carry/borrow

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation. 0: No overflow or underflow has occurred. 1: An overflow or underflow has occurred

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

## SUPPLY, RESET AND CLOCK MANAGEMENT (Cont'd)

## 7.3 REGISTER DESCRIPTION

#### MAIN CLOCK CONTROL/STATUS REGISTER (MCCSR)

Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |  |

|---|---|---|---|---|---|-----|-----|--|

| 0 | 0 | 0 | 0 | 0 | 0 | мсо | SMS |  |

Bits 7:2 = Reserved, must be kept cleared.

#### Bit 1 = MCO Main Clock Out enable

This bit is read/write by software and cleared by hardware after a reset. This bit allows to enable the MCO output clock.

0: MCO clock disabled. I/O port free for general purpose I/O.

1: MCO clock enabled.

#### Bit 0 = SMS Slow Mode select

This bit is read/write by software and cleared by hardware after a reset. This bit selects the input clock  $f_{OSC}$  or  $f_{OSC}/32$ . 0: Normal mode ( $f_{CPU} = f_{OSC}$ )

1: Slow mode ( $f_{CPU} = f_{OSC}/32$ )

## RC CONTROL REGISTER (RCCR)

Read / Write Reset Value: 1111 1111 (FFh)

| 7   |     |     |      |             | 5   |     | 0   |

|-----|-----|-----|------|-------------|-----|-----|-----|

| CR7 | CR6 | CR5 | Gr.4 | <u></u> СН3 | CR2 | CR1 | CR0 |

## Table J. C. X. Register Map and Reset Values

#### Bits 7:0 = CR[7:0] RC Oscillator Frequency Adiustment Bits

These bits must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. The application can store the correct value for each voltage range in EEPROM and write it to this register at start-up. 00h = maximum available frequency

FFh = lowest available frequency

Note: To tune the oscillator, write a series of different values in the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

## SYSTEM INTEGRITY (SI) CONTROL/STATUS **REGISTER (SICSR)**

Read/Write

Reset Value: 0000 0x00 (0v)

| 7 | ×0,0  |            |   |   |   |  |  |

|---|-------|------------|---|---|---|--|--|

| 0 | 0 0 0 | LOCK<br>ED | 0 | 0 | 0 |  |  |

$B^{i+s}$  7:4 = Reserved, must be kept cleared.

## Bit 3 = LOCKED PLL Locked Flag

This bit is set and cleared by hardware. It is set automatically when the PLL reaches its operating frequency. 0: PLL not locked

57

1: PLL locked

Bits 2:0 = Reserved, must be kept cleared.

| Address<br>(Hex.) | Register<br>Label    | 7        | 6        | 5        | 4        | 3           | 2        | 1        | 0        |

|-------------------|----------------------|----------|----------|----------|----------|-------------|----------|----------|----------|

| 0038h             | MCCSR<br>Reset Value | 0        | 0        | 0        | 0        | 0           | 0        | MCO<br>0 | SMS<br>0 |

| 0039h             | RCCR<br>Reset Value  | CR7<br>1 | CR6<br>1 | CR5<br>1 | CR4<br>1 | CR3<br>1    | CR2<br>1 | CR1<br>1 | CR0<br>1 |

| 003Ah             | SICSR<br>Reset Value | 0        | 0        | 0        | 0        | LOCKED<br>0 | 0        | 0        | 0        |

## SUPPLY, RESET AND CLOCK MANAGEMENT (Cont'd)

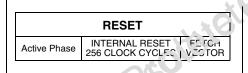

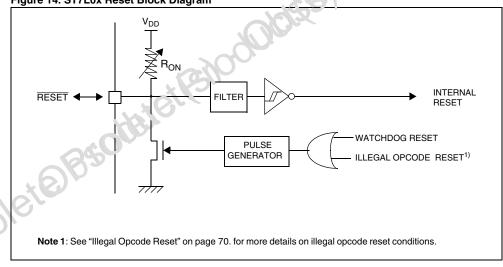

## 7.4 RESET SEQUENCE MANAGER (RSM)

## 7.4.1 Introduction

The reset sequence manager includes two RE-SET sources as shown in Figure 14:

- External RESET source pulse

- Internal WATCHDOG RESET

**Note:** A reset can also be triggered following the detection of an illegal opcode or prebyte code. Refer to Section 12.2.1 on page 70 for further details.

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

The basic RESET sequence consists of three phases as shown in Figure 13:

- Active Phase depending on the RESET source

- 256 CPU clock cycle delay

- RESET vector fetch

**Caution**: When the ST7 is unprogrammed or fully erased, the Flash is blank and the RESET vector is not programmed. For this reason, it is recommended to keep the RESET pin in low state until

## Figure 14. ST7L0x Reset Block Diagram

programming mode is entered, in order to avoidunwanted behavior.

The 256 CPU clock cycle delay allows the oscillator to stabilize and ensures that recovery has taken place from the Reset state.

The RESET vector fetch phase duration is two clock cycles.

If the PLL is enabled by option byte, it outputs the clock after an additional delay of  $t_{\text{STARTUP}}$  (see Figure 11).

## Figure 13. RESET Sequence Phases

**۲/ک**

## POWER SAVING MODES (Cont'd)

#### 9.4.2.1 HALT Mode Recommendations

- Make sure that an external event is available to wake up the microcontroller from Halt mode.

- When using an external interrupt to wake up the microcontroller, reinitialize the corresponding I/O as "Input Pull-up with Interrupt" before executing the HALT instruction. The main reason for this is that the I/O may be wrongly configured due to external interference or by an unforeseen logical condition.

- For the same reason, reinitialize the level sensi-

- The opcode for the HALT instruction is 0x8E. To avoid an unexpected HALT instruction due to a program counter failure, it is advised to clear all occurrences of the data value 0x8E from memory. For example, avoid defining a constant in ROM with the value 0x8E.

- As the HALT instruction clears the I bit in the CC register to allow interrupts, the user may choose to clear all pending interrupt bits before executing the HALT instruction. This avoids entering oletaBrothitetRanocoletaBletaBrothitetRanocoletaBrothitetRanocoletaBrothitetRanocoletaBrothitetBalance other peripheral interrupt routines after executing the external interrupt routine corresponding to

register

57

select rising edge

reset the interrupt mask with the RIM instruction (in cases where a pin level change could occur)

## 10.2.2 Output Modes

The output configuration is selected by setting the corresponding DDR register bit. In this case, writing the DR register applies this digital value to the I/O pin through the latch. Then reading the DR register returns the previously stored value.

Two different output modes can be selected by software through the OR register: Output push-pull and open-drain.

DR register value and output pin status:

| DR | Push-pull       | Open-drain |

|----|-----------------|------------|

| 0  | V <sub>SS</sub> | Vss        |

| 1  | V <sub>DD</sub> | Floating   |

ust be Note: When switching from input to output mode. the DR register must be written first to drive the

## 10.2.3 Alternate Functions

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over the standard I/O programming under the following conditions:

- When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

- When the signal is going to an on-chip peripheral, the I/O pin must be configured in floating input mode. In this case, the pin state is also digitally readable by addressing the DR register.

#### Notes:

- Input pull-up configuration can cause unexpect ed value at the input of the alternate peripheral input.

- When an on-chip peripheral uses a rin as input and output, this pin must be configured in input

### 12-BIT AUTORELOAD TIMER (Cont'd) AUTORELOAD REGISTER (ATRH) Read / Write

Reset Value: 0000 0000 (00h)

| 15 |   |   |   |       |       |      | 8    |

|----|---|---|---|-------|-------|------|------|

| 0  | 0 | 0 | 0 | ATR11 | ATR10 | ATR9 | ATR8 |

## AUTORELOAD REGISTER (ATRL)

Read / Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ATR7 | ATR6 | ATR5 | ATR4 | ATR3 | ATR2 | ATR1 | ATR0 |

Bits 15:12 = Reserved, must be kept cleared.

Bits 11:0 = **ATR[11:0]** Autoreload Register

This is a 12-bit register which is written by software. The ATR register value is automatically loaded into the upcounter when an overflow occurs. The register value is used to set the PWM frequency.

## PWM0 DUTY CYCLE REGISTER HIGH (DCR0H)

Read / Write

Reset Value: 0000 0000 (00h)

15

|   | 0 | 0 | 0  | 0               | DCR11 | DCR10 DCR9 | DCR8 |

|---|---|---|----|-----------------|-------|------------|------|

|   |   |   | 24 | ,o <sup>t</sup> | 3     |            |      |

|   | e | 0 | 0. |                 |       |            |      |

| 9 |   |   |    |                 |       |            |      |

## PWM0 DUTY CYCLE REGISTER LOW (DCR0L)

Read / Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| DCR7 | DCR6 | DCR5 | DCR4 | DCR3 | DCR2 | DCR1 | DCR0 |

Bits 15:12 = Reserved, must be kept cleared.

Bits 11:0 = **DCR[11:0]** *PWMx Duty Cycle Value* This 12-bit value is written by software. The high register must be written first.

In PWM mode (OE0 = 1 in the PWMCR register) the DCR[11:0] bits define the duty cycla (f are PWM0 output signal (see Figure 29). In Output Compare mode, (OE0 = 0 in the PW1(C5 register) they define the value to be compare 1 with the 12-bit upcounter value.

| (PWM0CSR)<br>Read / Write |                 | REGISTER |

|---------------------------|-----------------|----------|

| Reset Value:              | 2000 0000 (00h) | 0        |

|   |   |   |   |   |   |     | -     |

|---|---|---|---|---|---|-----|-------|

| 0 | 0 | 0 | 0 | 0 | 0 | OP0 | CMPF0 |

Bit 7:2 = Reserved, must be kept cleared.

## Bit 1 = **OP0** *PWM0 Output Polarity*

This bit is read/write by software and cleared by hardware after a reset. This bit selects the polarity of the PWM0 signal.

0: The PWM0 signal is not inverted.

1: The PWM0 signal is inverted.

## Bit 0 = CMPF0 PWM0 Compare Flag.

This bit is set by hardware and cleared by software by reading the PWM0CSR register. It indicates that the upcounter value matches the DCR0 register value.

0: Upcounter value does not match DCR value.

1: Upcounter value matches DCR value.

## SERIAL PERIPHERAL INTERFACE (Cont'd)

## 11.3.3.1 Functional Description

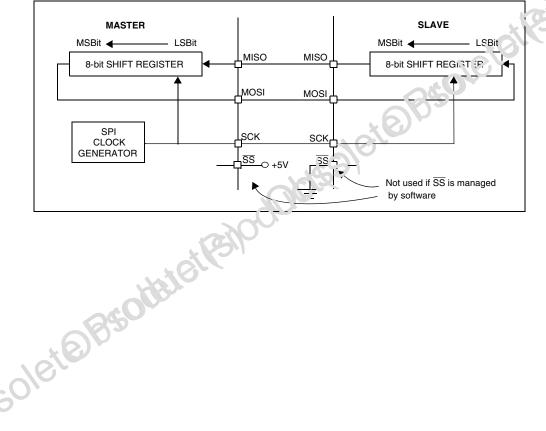

A basic example of interconnections between a single master and a single slave is illustrated in Figure 32.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device re-

Figure 32. Single Master/ Single Slave Application

sponds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 35) but master and slave must be programmed with the same timing mode.

**ل ۲**۸

## SERIAL PERIPHERAL INTERFACE (Cont'd) 11.3.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the MCU is woken up<br>by an interrupt with "exit from HALT mode"<br>capability. The data received is subsequent-<br>ly read from the SPIDR register when the<br>software is running (interrupt vector fetch-<br>ing). If data is received before the wake-up<br>event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the device. |

# 11.3.6.1 Using the SPI to wakeup the MCU from Halt mode

In slave configuration, the SPI is able to wakeup the ST7 device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

Note: When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the

oleteBsothietes

SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the ST7 from Halt mode only if the Slave Select signal (external  $\overline{SS}$ pin or the SSI bit in the SPICSR register) is low when the ST7 enters Halt mode. So if Slave selection is configured as external (see Section 11.3.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

## 11.3.7 Interrupts

| Interrupt Event                | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Trans-<br>fer Event | SPIF          |                          |                      | Yes                  |

| Master Mode Fault<br>Event     | MODF          | SPIE                     | Yes                  | 5                    |

| Overrun Error                  | OVR           |                          |                      |                      |

Note: The SPI interrupt events are connected to the same interrupt vector (core interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

47/

## ST7 ADDRESSING MODES (Cont'd)

## 12.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two submodes:

## Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

## Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

#### Table 19. Instructions Supporting Direct, Indexed. Indirect Indirect Indexed and Addressing Modes

| Long and Short<br>Instructions | Function                                        |

|--------------------------------|-------------------------------------------------|

| LD                             | Load                                            |

| CP                             | Compare                                         |

| AND, OR, XOR                   | Logical Operations                              |

| ADC, ADD, SUB, SBC             | Arithmetic Addition/subtrac-<br>tion operations |

| BCP                            | Bit Compare                                     |

| Short Instructions Only    | Function                          |

|----------------------------|-----------------------------------|

| CLR                        | Cleai                             |

| INC, DEC                   | I. crr ment/Decrement             |

| TNZ                        | i est Negative or Zero            |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET BRE3                  | Bit Operations                    |

| BTJT, BIJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations       |

| SWAP                       | Swap Nibbles                      |

| CALL, JP                   | Call or Jump subroutine           |

57

## 12.1.7 Relative Mode (Direct, Indirect)

This addressing mode is used to modify the PC register value by adding an 8-bit signed offset to it.

| Available Relative Direct/<br>Indirect Instructions | Function         |

|-----------------------------------------------------|------------------|

| JRxx                                                | Conditional Jump |

| CALLR                                               | Call Relative    |

The relative addressing mode consists of two submodes:

## Relative (Direct)

The offset follows the opcode.

## Relative (Indirect)

uch tł htrac-occhesie chilasofi chi The offset is defined in memory, of which the ad-

## **INSTRUCTION GROUPS** (Cont'd)

| Mnemo | Description            | Function/Example                   | Dst     | Src     |   | н | I | Ν  | Z     | С |

|-------|------------------------|------------------------------------|---------|---------|---|---|---|----|-------|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=                        |         |         |   |   |   |    |       |   |

| LD    | Load                   | dst <= src                         | reg, M  | M, reg  |   |   |   | Ν  | Z     |   |

| MUL   | Multiply               | X,A = X * A                        | A, X, Y | X, Y, A |   | 0 |   |    |       | 0 |

| NEG   | Negate (2's compl)     | neg \$10                           | reg, M  |         |   |   |   | Ν  | Z     | С |

| NOP   | No Operation           |                                    |         |         |   |   |   |    |       |   |

| OR    | OR operation           | A = A + M                          | А       | М       |   |   |   | Ν  | Z     |   |

| POP   | Pop from the Stack     | pop reg                            | reg     | М       |   |   |   |    |       |   |

|       |                        | pop CC                             | сс      | м       |   | Н | Ι | Ν  | Z     | С |

| PUSH  | Push onto the Stack    | push Y                             | М       | reg, CC |   |   |   |    |       |   |

| RCF   | Reset carry flag       | C = 0                              |         |         |   |   |   |    |       | 2 |

| RET   | Subroutine Return      |                                    |         |         |   |   |   |    |       | M |

| RIM   | Enable Interrupts      | l = 0                              |         |         |   |   | 0 |    | j 🗁 🕇 |   |

| RLC   | Rotate left true C     | C <= Dst <= C                      | reg, M  |         |   |   |   | iN | Z     | С |

| RRC   | Rotate right true C    | C => Dst => C                      | reg, M  |         | G |   | 7 | Ν  | Z     | С |

| RSP   | Reset Stack Pointer    | S = Max allowed                    |         |         | K |   |   |    |       |   |

| SBC   | Subtract with Carry    | A = A - M - C                      | А       | N.      |   |   |   | Ν  | Z     | С |

| SCF   | Set carry flag         | C = 1                              |         |         |   |   |   |    |       | 1 |

| SIM   | Disable Interrupts     | I=1                                | CX      | -       |   |   | 1 |    |       |   |

| SLA   | Shift left Arithmetic  | C <= Dst <= 0                      | reg, M  |         |   |   |   | Ν  | Z     | С |

| SLL   | Shift left Logic       | C <= Dst := u                      | reg, M  |         |   |   |   | Ν  | Z     | С |

| SRL   | Shift right Logic      | $L \Rightarrow Js_1 \Rightarrow C$ | reg, M  |         |   |   |   | 0  | Z     | С |

| SRA   | Shift right Arithmetic | Dst.' => Dst => C                  | reg, M  |         |   |   |   | Ν  | Z     | С |

| SUB   | Subtraction            | A = A - M                          | А       | М       |   |   |   | Ν  | Z     | С |

| SWAP  | SWAP nibhio            | Dst[74] <=> Dst[30]                | reg, M  |         |   |   |   | Ν  | Z     |   |

| TNZ   | Test fur Ning & Zero   | tnz lbl1                           |         |         |   |   |   | Ν  | Z     |   |

| TRAP  | `/\V †rap              | S/W interrupt                      |         |         |   |   | 1 |    |       |   |

| WFI   | Vait for Interrupt     |                                    |         |         |   |   | 0 |    |       |   |

| XOR   | Exclusive OR           | A = A XOR M                        | А       | М       | 1 |   |   | Ν  | Z     |   |

57

## **13.7 EMC CHARACTERISTICS**

Susceptibility tests are performed on a sample basis during product characterization.

# 13.7.1 Functional EMS (Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to resume. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

# 13.7.1.1 Designing Hardened Software to Avoid Noise Problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the DE-SET pin or the Oscillator pins for 1 scourd.

To complete these trials, ESD s ress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the soft ware can be hardened to prevent unrecoverable errors occurring (see application note AN101F).

| Symbol            | Parameter                                                                                                                                           | Conditions                                                                       | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                      | $V_{DD} = 5V$ , $T_A = 25^{\circ}C$ , $f_{OSC} = 8$ MHz conforms to IEC 1000-4-2 | 2B              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be $a_1$ plik 1 through 100pF on V <sub>DD</sub> and V <sub>DD</sub> pins o in tube a functional disturbance | $V_{DD} = 5V$ , $T_A = 25^{\circ}C$ , $f_{OSC} = 8$ MHz conforms to IEC 1000-4-4 | 3B              |

## 13.7.2 Electro Magnetic Interference (EMI)

Based on a simple application unning on the product (toggling two LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/ 3 which specifics he board and the loading of each pin.

| ĺ | Symbo            | Parameter                | Conditions                                          | Monitored         | Max vs [f | osc/f <sub>CPU</sub> ] | Unit |

|---|------------------|--------------------------|-----------------------------------------------------|-------------------|-----------|------------------------|------|

|   | Symbol           | Farameter                | contaitions                                         | Frequency Band    | 1/4 MHz   | 1/8 MHz                | onne |

| N | 9                |                          |                                                     | 0.1 MHz to 30 MHz | 8         | 14                     |      |

|   | S <sub>EMI</sub> | Peak lovel <sup>1)</sup> | $V_{DD} = 5V$ , $T_A = 25^{\circ}C$ , SO16 package, | 30 MHz to 130 MHz | 27        | 32                     | dBµV |

|   | JEWI             | I Carlevel               | conforming to SAE J 1752/3                          | 130 MHz to 1 GHz  | 26        | 28                     |      |

|   |                  |                          |                                                     | SAE EMI Level     | 3.5       | 4                      | -    |

#### Notes:

1. Data based on characterization results, not tested in production.

## COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

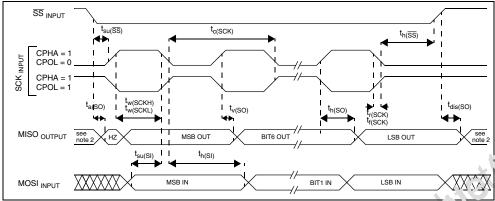

## Figure 66. SPI Slave Timing Diagram with CPHA = 1<sup>1)</sup>

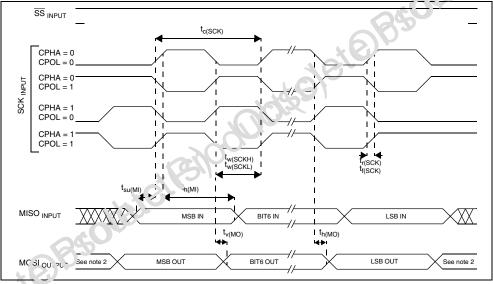

## Figure 67. SPI Master Timing Diagram<sup>1)</sup>

## Notes:

1. Measurement points are done at CMOS levels: 0.3xV<sub>DD</sub> and 0.7xV<sub>DD</sub>.

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

## ADC CHARACTERISTICS (Cont'd)

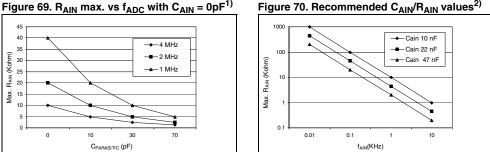

## Figure 69. $R_{AIN}$ max. vs $f_{ADC}$ with $C_{AIN} = 0 p F^{1}$

#### Notes:

1.C<sub>PARASITIC</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad ca pacitance (3pF). A high C<sub>PARASITIC</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> must be reduced. 2. This graph shows that depending on the input signal variation ( $f_{AIN}$ ),  $C_{AIN}$  can be increased for stabilization and tr a pw the use of a larger serial resistor ( $R_{AIN}$ ). It is valid for all  $f_{ADC}$  frequencies  $\leq 4$  MHz.

## 13.11.0.1 General PCB Design Guidelines

To obtain best results, some general design and layout rules must be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

ioletelesothietelesioonick Properly place components and route the signal

Analog signals paths should run ore me analog ground plane and be as short as no sible. Isolate analog signals from ligital signals that may switch while the an arow in ou is are being sampled by the A/D conve ter. I to not toggle digital outputs on the same I/C port as the A/D input being converted

## **14 PACKAGE CHARACTERISTICS**

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at www.st.com.

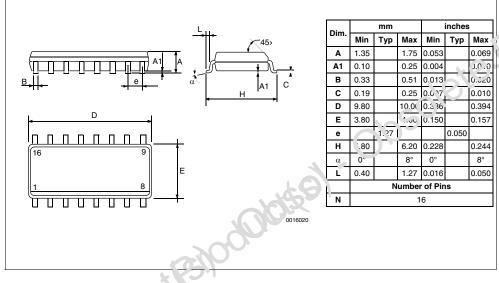

## **14.1 PACKAGE MECHANICAL DATA**

#### Figure 72. 16-Pin Plastic Small Outline Package, 150-mil Width

## 14.2 THERMAL CHARACTER STICS

| Symbol             | Ratings                                           | Value | Unit |

|--------------------|---------------------------------------------------|-------|------|

| R <sub>thJA</sub>  | Hauttage thermal resistance (junction to ambient) | 95    | °C/W |

| T <sub>Jmax</sub>  | Maximum junction temperature <sup>1)</sup>        | 150   | °C   |

| P <sub>nr. v</sub> | Power dissipation <sup>2)</sup>                   | 500   | mW   |

#### Notes:

1. The maximum chip-junction temperature is based on technology characteristics.

2. The maximum power dissipation is obtained from the formula  $P_D = (T_J - T_A) / R_{thJA}$ . The power dissipation of an application can be defined by the user with the formula:  $P_D = P_{INT} + P_{PORT}$  where  $P_{INT}$  is the chip internal power ( $I_{DD} \times V_{DD}$ ) and  $P_{PORT}$  is the port power dissipation depending on the ports used in the application.

## PACKAGE CHARACTERISTICS (Cont'd)

## 14.3 SOLDERING INFORMATION

47/

In accordance with the RoHS European directive. all STMicroelectronics packages have been converted to lead-free technology named ECO-PACK™.

- ECOPACK<sup>™</sup> packages are qualified according to the JEDEC STD-020C compliant soldering profile.

- Detailed information on the STMicroelectronics ECOPACK<sup>™</sup> transition program is available on www.st.com/stonline/leadfree/, with specific technical application notes covering the main aspects related to lead-free technical conversion (AN2033, AN2034, AN2035, and AN2036).

## Forward compatibility

ECOPACK<sup>™</sup> SO packages are fully compatible with a lead (Pb) containing soldering process (see application note AN2034).

## Table 22. Soldering Compatibility (Wave and Reflow Soldering Process)

| Package         | ng Compatibility (Wave and Reflow S Plating material | Pb solder paste | I h free solder paste |

|-----------------|------------------------------------------------------|-----------------|-----------------------|

| SO              | NiPdAu (Nickel-Palladium-Gold)                       | Yes             | Yes                   |

|                 |                                                      |                 |                       |

|                 |                                                      | 36              |                       |

|                 |                                                      |                 |                       |

|                 |                                                      | 12              |                       |

|                 | 1. N                                                 |                 |                       |

|                 |                                                      |                 |                       |

|                 |                                                      |                 |                       |

|                 |                                                      |                 |                       |

|                 | (B)                                                  |                 |                       |

|                 | atemp                                                |                 |                       |

|                 | Lietenou                                             |                 |                       |

|                 | Haiotespoo                                           |                 |                       |

|                 | othieitestestoc                                      |                 |                       |

|                 | othietester                                          |                 |                       |

|                 | othicitespoo                                         |                 |                       |

| (B <sup>f</sup> | othieteste                                           |                 |                       |

## DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

## **OPTION BYTE 1**

Bit 7 = Reserved, must always be 1

Bit 6 = PLLOFF PLL disabled 0: PLL enabled 1: PLL disabled (by-passed)

Bit 4 = OSC RC Oscillator selection 0: BC oscillator on 1: RC oscillator off

Note: If the RC oscillator is selected, then to improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the  $V_{DD}$  and  $V_{SS}$  pins as close as possible to the ST7 device.

Bit 5 = Reserved, must always be 1

## Table 23. List of Valid Option Combinations

| Operating conditions  |                 |     |                      | Option Bits |        |  |

|-----------------------|-----------------|-----|----------------------|-------------|--------|--|

| V <sub>DD</sub> range | Clock Source    | PLL | Typ f <sub>CPU</sub> | OSC         | PLLOFF |  |

|                       | Internal RC 1%  | off | 1 MHz @ 5V           | 0           | 1      |  |

| 3.6 to 5.5V           | Internal HC 1/8 | x8  | 8 MHz @ 5V           | 0           | 0      |  |

| 3.0 10 5.5 V          | External clock  | off | 0 to 8 MHz           | 1           |        |  |

|                       | External clock  | x8  | 8 MHz                |             | 0      |  |

Note: See Clock Management Block diagram in Figure 12.

Bits 3:2 = Reserved

Bit 1 = WDG SW Hardware or software watchdog This option bit selects the watchdog type. 0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

Bit 0 = WDG HALT Waichdog Reset on Halt This option bit determines if a RESET is generated when enturing HALT mode while the Watchdog is active

0. No East generation when entering Halt mode Reset generation when entering Halt mode

|                    |     |        |               | -    |                       |          |      |            |      |       |      |      |           |             |

|--------------------|-----|--------|---------------|------|-----------------------|----------|------|------------|------|-------|------|------|-----------|-------------|

|                    |     | OPTION | BYTE          | n    | $\mathbf{\mathbf{y}}$ |          |      |            | 0    | PTION | BYTE | 1    |           |             |

| 7                  |     |        |               | 9    |                       | 0        | 7    |            |      |       |      |      |           | 0           |

|                    | Res | served | ि <b>EC</b> 1 | SEC0 | FMP<br>R              | FMP<br>W | Res. | PLL<br>OFF | Res. | osc   | Res. | Res. | WDG<br>SW | WDG<br>HALT |

| Default<br>Value 1 | 1   |        | 1             | 1    | 0                     | 0        | 1    | 1          | 1    | 0     | 1    | 1    | 1         | 1           |

|                    | 24  | 0      |               |      |                       |          |      |            |      |       |      |      |           | 1           |

| 6                  | 0.  | /      |               |      |                       |          |      |            |      |       |      |      |           |             |

| at C               |     |        |               |      |                       |          |      |            |      |       |      |      |           |             |

| 0                  |     |        |               |      |                       |          |      |            |      |       |      |      |           |             |

|                    |     |        |               |      |                       |          |      |            |      |       |      |      |           |             |

## DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

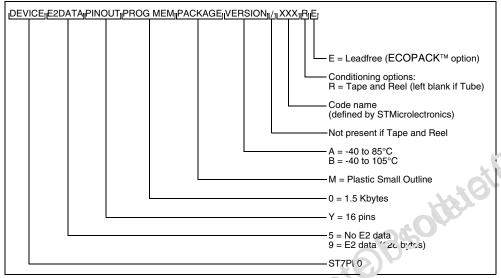

## Figure 74. FASTROM Commercial Product Code Structure

## Table 25. FASTROM Factory Coded Device Types

57

| Part Number | Program Memory<br>(Bytes) | Data EEPROM<br>(Bytes) | ytes)ھَنَ} R.∖M | Temp. Range    | Package |

|-------------|---------------------------|------------------------|-----------------|----------------|---------|

| ST7PL05Y0MA |                           |                        |                 | -40 to +85°C   |         |

| ST7PL09Y0MA | 1.5K FASTROM              | 129                    | 128             | -40 10 +65 C   | SO16    |

| ST7PL05Y0MB | 1.5K FASTHOW              |                        | 120             | -40 to +105°C  | 3016    |

| ST7PL09Y0MB |                           | 128                    |                 | -40 10 +105 °C |         |

| 0           |                           |                        |                 |                |         |