Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | 27648                                                         |

| Number of I/O                  | 37                                                            |

| Number of Gates                | 90000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 108-WFQFN                                                     |

| Supplier Device Package        | 108-QFN (8x8)                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs090-1qng108 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Fusion Device Family Overview

The FlashPoint tool in the Fusion development software solutions, Libero SoC and Designer, has extensive support for flash memory blocks and FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using the Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

#### SRAM and FIFO

Fusion devices have embedded SRAM blocks along the north and south sides of the device. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be written through a 4-bit port and read as a single bitstream. The SRAM blocks can be initialized from the flash memory blocks or via the device JTAG port (ROM emulation mode), using the UJTAG macro.

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and Almost Full (AFULL) flags in addition to the normal EMPTY and FULL flags. The embedded FIFO control unit contains the counters necessary for the generation of the read and write address pointers. The SRAM/FIFO blocks can be cascaded to create larger configurations.

## **Clock Resources**

## PLLs and Clock Conditioning Circuits (CCCs)

Fusion devices provide designers with very flexible clock conditioning capabilities. Each member of the Fusion family contains six CCCs. In the two larger family members, two of these CCCs also include a PLL; the smaller devices support one PLL.

The inputs of the CCC blocks are accessible from the FPGA core or from one of several inputs with dedicated CCC block connections.

The CCC block has the following key features:

- Wide input frequency range (f<sub>IN CCC</sub>) = 1.5 MHz to 350 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz to 350 MHz

- Clock phase adjustment via programmable and fixed delays from –6.275 ns to +8.75 ns

- · Clock skew minimization (PLL)

- Clock frequency synthesis (PLL)

- · On-chip analog clocking resources usable as inputs:

- 100 MHz on-chip RC oscillator

- Crystal oscillator

#### Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°

- Output duty cycle = 50% ± 1.5%

- Low output jitter. Samples of peak-to-peak period jitter when a single global network is used:

- 70 ps at 350 MHz

- 90 ps at 100 MHz

- 180 ps at 24 MHz

- Worst case < 2.5% × clock period</li>

- Maximum acquisition time = 150 μs

- Low power consumption of 5 mW

1-7 Revision 6

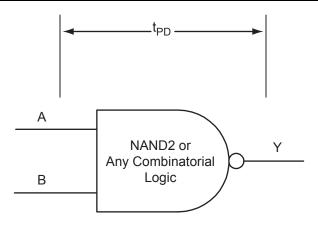

$t_{PD} = \text{MAX}(t_{PD(RR)},\,t_{PD(RF)},\,t_{PD(FF)},\,t_{PD(FR)})$  where edges are applicable for the particular combinatorial cell

Figure 2-4 • Combinatorial Timing Model and Waveforms

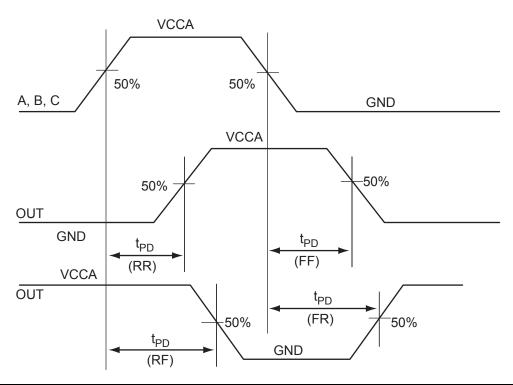

Figure 2-10 • Very-Long-Line Resources

## **CCC and PLL Characteristics**

## **Timing Characteristics**

## Table 2-12 • Fusion CCC/PLL Specification

| Parameter                                                          | Min.                        | Тур.             | Max.                         | Unit |

|--------------------------------------------------------------------|-----------------------------|------------------|------------------------------|------|

| Clock Conditioning Circuitry Input Frequency f <sub>IN_CCC</sub>   | 1.5                         |                  | 350                          | MHz  |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub> | 0.75                        |                  | 350                          | MHz  |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>      |                             | 160 <sup>3</sup> |                              | ps   |

| Number of Programmable Values in Each Programmable Delay Block     |                             |                  | 32                           |      |

| Input Period Jitter                                                |                             |                  | 1.5                          | ns   |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | Max Pea                     | k-to-Peak Po     | eriod Jitter                 |      |

|                                                                    | 1 Global<br>Network<br>Used |                  | 3 Global<br>Networks<br>Used |      |

| 0.75 MHz to 24 MHz                                                 | 1.00%                       |                  | 1.00%                        |      |

| 24 MHz to 100 MHz                                                  | 1.50%                       |                  | 1.50%                        |      |

| 100 MHz to 250 MHz                                                 | 2.25%                       |                  | 2.25%                        |      |

| 250 MHz to 350 MHz                                                 | 3.50%                       |                  | 3.50%                        |      |

| Acquisition Time LockControl = 0                                   |                             |                  | 300                          | μs   |

| LockControl = 1                                                    |                             |                  | 6.0                          | ms   |

| Tracking Jitter <sup>4</sup> LockControl = 0                       |                             |                  | 1.6                          | ns   |

| LockControl = 1                                                    |                             |                  | 0.8                          | ns   |

| Output Duty Cycle                                                  | 48.5                        |                  | 51.5                         | %    |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>         | 0.6                         |                  | 5.56                         | ns   |

| Delay Range in Block: Programmable Delay 2 1, 2                    | 0.025                       |                  | 5.56                         | ns   |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                  |                             | 2.2              |                              | ns   |

#### Notes:

- 1. This delay is a function of voltage and temperature. See Table 3-7 on page 3-9 for deratings.

- 2.  $T_J = 25^{\circ}C$ , VCC = 1.5 V

- 3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help associated with the core for more information.

- 4. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by period jitter parameter.

# **Embedded Memories**

Fusion devices include four types of embedded memory: flash block, FlashROM, SRAM, and FIFO.

# **Flash Memory Block**

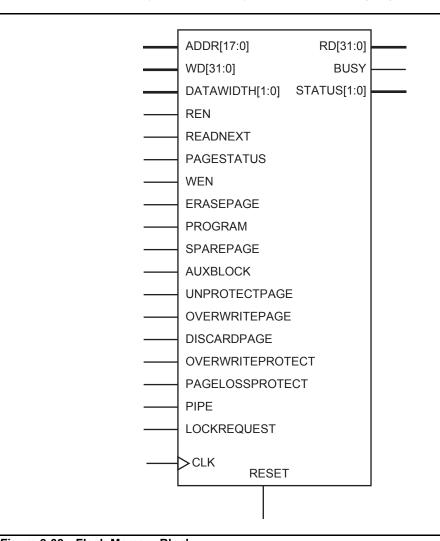

Fusion is the first FPGA that offers a flash memory block (FB). Each FB block stores 2 Mbits of data. The flash memory block macro is illustrated in Figure 2-32. The port pin name and descriptions are detailed on Table 2-19 on page 2-40. All flash memory block signals are active high, except for CLK and active low RESET. All flash memory operations are synchronous to the rising edge of CLK.

Figure 2-32 • Flash Memory Block

2-39 Revision 6

Table 2-25 • Flash Memory Block Timing (continued)

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                  | Description                                                            | -2     | -1    | Std.  | Units |

|----------------------------|------------------------------------------------------------------------|--------|-------|-------|-------|

| t <sub>SUPGLOSSPRO</sub>   | Page Loss Protect Setup Time for the Control Logic                     | 1.69   | 1.93  | 2.27  | ns    |

| t <sub>HDPGLOSSPRO</sub>   | Page Loss Protect Hold Time for the Control Logic                      | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SUPGSTAT</sub>      | Page Status Setup Time for the Control Logic                           | 2.49   | 2.83  | 3.33  | ns    |

| t <sub>HDPGSTAT</sub>      | Page Status Hold Time for the Control Logic                            | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SUOVERWRPG</sub>    | Over Write Page Setup Time for the Control Logic                       | 1.88   | 2.14  | 2.52  | ns    |

| t <sub>HDOVERWRPG</sub>    | Over Write Page Hold Time for the Control Logic                        | 0.00   | 0.00  | 0.00  | ns    |

| tsulockrequest             | Lock Request Setup Time for the Control Logic                          | 0.87   | 0.99  | 1.16  | ns    |

| t <sub>HDLOCKREQUEST</sub> | Lock Request Hold Time for the Control Logic                           | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>RECARNVM</sub>      | Reset Recovery Time                                                    | 0.94   | 1.07  | 1.25  | ns    |

| t <sub>REMARNVM</sub>      | Reset Removal Time                                                     | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>MPWARNVM</sub>      | Asynchronous Reset Minimum Pulse Width for the Control Logic           | 10.00  | 12.50 | 12.50 | ns    |

| t <sub>MPWCLKNVM</sub>     | Clock Minimum Pulse Width for the Control Logic                        | 4.00   | 5.00  | 5.00  | ns    |

| +                          | Maximum Frequency for Clock for the Control Logic – for AFS1500/AFS600 | 80.00  | 80.00 | 80.00 | MHz   |

| <sup>T</sup> FMAXCLKNVM    | Maximum Frequency for Clock for the Control Logic – for AFS250/AFS090  | 100.00 | 80.00 | 80.00 | MHz   |

#### **FlashROM**

Fusion devices have 1 kbit of on-chip nonvolatile flash memory that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core (Figure 2-45).

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports a synchronous read and can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank that is being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

The maximum FlashROM access clock is given in Table 2-26 on page 2-54. Figure 2-46 shows the timing behavior of the FlashROM access cycle—the address has to be set up on the rising edge of the clock for DOUT to be valid on the next falling edge of the clock.

If the address is unchanged for two cycles:

- D0 becomes invalid t<sub>CK2Q</sub> ns after the second rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the second falling edge.

If the address unchanged for three cycles:

- D0 becomes invalid t<sub>CK2O</sub> ns after the second rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the second falling edge.

- D0 becomes invalid t<sub>CK2Q</sub> ns after the third rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the third falling edge.

2-53 Revision 6

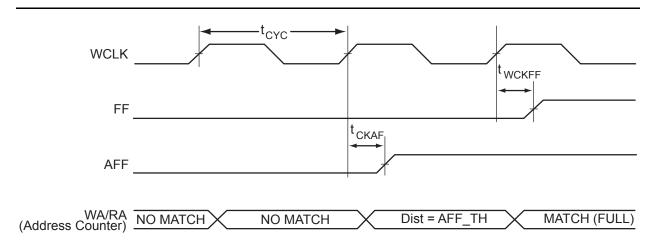

Figure 2-61 • FIFO FULL and AFULL Flag Assertion

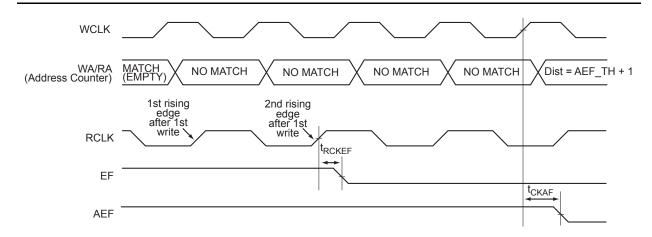

Figure 2-62 • FIFO EMPTY Flag and AEMPTY Flag Deassertion

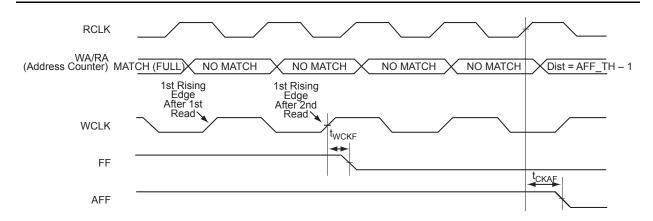

Figure 2-63 • FIFO FULL Flag and AFULL Flag Deassertion

# ADC Terminology

#### **Conversion Time**

Conversion time is the interval between the release of the hold state (imposed by the input circuitry of a track-and-hold) and the instant at which the voltage on the sampling capacitor settles to within one LSB of a new input value.

#### **DNL - Differential Non-Linearity**

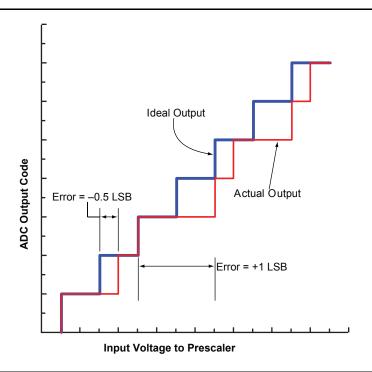

For an ideal ADC, the analog-input levels that trigger any two successive output codes should differ by one LSB (DNL = 0). Any deviation from one LSB in defined as DNL (Figure 2-83).

Figure 2-83 • Differential Non-Linearity (DNL)

## **ENOB – Effective Number of Bits**

ENOB specifies the dynamic performance of an ADC at a specific input frequency and sampling rate. An ideal ADC's error consists only of quantization of noise. As the input frequency increases, the overall noise (particularly in the distortion components) also increases, thereby reducing the ENOB and SINAD (also see "Signal-to-Noise and Distortion Ratio (SINAD)".) ENOB for a full-scale, sinusoidal input waveform is computed using EQ 12.

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

EQ 12

#### FS Error - Full-Scale Error

Full-scale error is the difference between the actual value that triggers that transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error.

# **ADC Interface Timing**

Table 2-48 • ADC Interface Timing

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                | Description                                    | -2     | -1     | Std.   | Units |

|--------------------------|------------------------------------------------|--------|--------|--------|-------|

| t <sub>SUMODE</sub>      | Mode Pin Setup Time                            | 0.56   | 0.64   | 0.75   | ns    |

| t <sub>HDMODE</sub>      | Mode Pin Hold Time                             | 0.26   | 0.29   | 0.34   | ns    |

| t <sub>sutvc</sub>       | Clock Divide Control (TVC) Setup Time          | 0.68   | 0.77   | 0.90   | ns    |

| t <sub>HDTVC</sub>       | Clock Divide Control (TVC) Hold Time           | 0.32   | 0.36   | 0.43   | ns    |

| t <sub>sustc</sub>       | Sample Time Control (STC) Setup Time           | 1.58   | 1.79   | 2.11   | ns    |

| t <sub>HDSTC</sub>       | Sample Time Control (STC) Hold Time            | 1.27   | 1.45   | 1.71   | ns    |

| t <sub>SUVAREFSEL</sub>  | Voltage Reference Select (VAREFSEL) Setup Time | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>HDVAREFSEL</sub>  | Voltage Reference Select (VAREFSEL) Hold Time  | 0.67   | 0.76   | 0.89   | ns    |

| tsuchnum                 | Channel Select (CHNUMBER) Setup Time           | 0.90   | 1.03   | 1.21   | ns    |

| t <sub>HDCHNUM</sub>     | Channel Select (CHNUMBER) Hold Time            | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>SUADCSTART</sub>  | Start of Conversion (ADCSTART) Setup Time      | 0.75   | 0.85   | 1.00   | ns    |

| t <sub>HDADCSTART</sub>  | Start of Conversion (ADCSTART) Hold Time       | 0.43   | 0.49   | 0.57   | ns    |

| t <sub>CK2QBUSY</sub>    | Busy Clock-to-Q                                | 1.33   | 1.51   | 1.78   | ns    |

| t <sub>CK2QCAL</sub>     | Power-Up Calibration Clock-to-Q                | 0.63   | 0.71   | 0.84   | ns    |

| t <sub>CK2QVAL</sub>     | Valid Conversion Result Clock-to-Q             | 3.12   | 3.55   | 4.17   | ns    |

| t <sub>CK2QSAMPLE</sub>  | Sample Clock-to-Q                              | 0.22   | 0.25   | 0.30   | ns    |

| t <sub>CK2QRESULT</sub>  | Conversion Result Clock-to-Q                   | 2.53   | 2.89   | 3.39   | ns    |

| t <sub>CLR2QBUSY</sub>   | Busy Clear-to-Q                                | 2.06   | 2.35   | 2.76   | ns    |

| t <sub>CLR2QCAL</sub>    | Power-Up Calibration Clear-to-Q                | 2.15   | 2.45   | 2.88   | ns    |

| t <sub>CLR2QVAL</sub>    | Valid Conversion Result Clear-to-Q             | 2.41   | 2.74   | 3.22   | ns    |

| t <sub>CLR2QSAMPLE</sub> | Sample Clear-to-Q                              | 2.17   | 2.48   | 2.91   | ns    |

| t <sub>CLR2QRESULT</sub> | Conversion result Clear-to-Q                   | 2.25   | 2.56   | 3.01   | ns    |

| t <sub>RECCLR</sub>      | Recovery Time of Clear                         | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>REMCLR</sub>      | Removal Time of Clear                          | 0.63   | 0.72   | 0.84   | ns    |

| t <sub>MPWSYSCLK</sub>   | Clock Minimum Pulse Width for the ADC          | 4.00   | 4.00   | 4.00   | ns    |

| t <sub>FMAXSYSCLK</sub>  | Clock Maximum Frequency for the ADC            | 100.00 | 100.00 | 100.00 | MHz   |

Fusion Family of Mixed Signal FPGAs

Table 2-57 details the settings available to control the prescaler values of the AV, AC, and AT pins. Note that the AT pin has a reduced number of available prescaler values.

Table 2-57 • Prescaler Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines<br>Bx[2:0] | Scaling<br>Factor, Pad to<br>ADC Input | LSB for an<br>8-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>10-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>12-Bit<br>Conversion <sup>1</sup><br>(mV) | Full-Scale<br>Voltage in<br>10-Bit<br>Mode <sup>2</sup> | Range Name |

|--------------------------|----------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|------------|

| 000 <sup>3</sup>         | 0.15625                                | 64                                                     | 16                                                     | 4                                                      | 16.368 V                                                | 16 V       |

| 001                      | 0.3125                                 | 32                                                     | 8                                                      | 2                                                      | 8.184 V                                                 | 8 V        |

| 010 <sup>3</sup>         | 0.625                                  | 16                                                     | 4                                                      | 1                                                      | 4.092 V                                                 | 4 V        |

| 011                      | 1.25                                   | 8                                                      | 2                                                      | 0.5                                                    | 2.046 V                                                 | 2 V        |

| 100                      | 2.5                                    | 4                                                      | 1                                                      | 0.25                                                   | 1.023 V                                                 | 1 V        |

| 101                      | 5.0                                    | 2                                                      | 0.5                                                    | 0.125                                                  | 0.5115 V                                                | 0.5 V      |

| 110                      | 10.0                                   | 1                                                      | 0.25                                                   | 0.0625                                                 | 0.25575 V                                               | 0.25 V     |

| 111                      | 20.0                                   | 0.5                                                    | 0.125                                                  | 0.03125                                                | 0.127875 V                                              | 0.125 V    |

#### Notes:

- 1. LSB voltage equivalences assume VAREF = 2.56 V.

- 2. Full Scale voltage for n-bit mode: ((2^n) 1) x (LSB for a n-bit Conversion)

- 3. These are the only valid ranges for the Temperature Monitor Block Prescaler.

Table 2-58 details the settings available to control the MUX within each of the AV, AC, and AT circuits. This MUX determines whether the signal routed to the ADC is the direct analog input, prescaled signal, or output of either the Current Monitor Block or the Temperature Monitor Block.

Table 2-58 • Analog Multiplexer Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[4] | Control Lines Bx[3] | ADC Connected To                      |

|---------------------|---------------------|---------------------------------------|

| 0                   | 0                   | Prescaler                             |

| 0                   | 1                   | Direct input                          |

| 1                   | 0                   | Current amplifier temperature monitor |

| 1                   | 1                   | Not valid                             |

Table 2-59 details the settings available to control the Direct Analog Input switch for the AV, AC, and AT pins.

Table 2-59 • Direct Analog Input Switch Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[5] | Direct Input Switch |

|---------------------|---------------------|

| 0                   | Off                 |

| 1                   | On                  |

Table 2-60 details the settings available to control the polarity of the signals coming to the AV, AC, and AT pins. Note that the only valid setting for the AT pin is logic 0 to support positive voltages.

Table 2-60 • Voltage Polarity Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)\*

| Control Lines Bx[6] | Input Signal Polarity |

|---------------------|-----------------------|

| 0                   | Positive              |

| 1                   | Negative              |

Note: \*The B3[6] signal for the AT pad should be kept at logic 0 to accept only positive voltages.

# **5 V Output Tolerance**

Fusion I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, Fusion I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceed the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level '1' and level '0' will be recognized correctly by 5 V TTL receivers.

# Simultaneously Switching Outputs and PCB Layout

- Simultaneously switching outputs (SSOs) can produce signal integrity problems on adjacent signals that are not part of the SSO bus. Both inductive and capacitive coupling parasitics of bond wires inside packages and of traces on PCBs will transfer noise from SSO busses onto signals adjacent to those busses. Additionally, SSOs can produce ground bounce noise and VCCI dip noise. These two noise types are caused by rapidly changing currents through GND and VCCI package pin inductances during switching activities:

- Ground bounce noise voltage = L(GND) \* di/dt

- VCCI dip noise voltage = L(VCCI) \* di/dt

Any group of four or more input pins switching on the same clock edge is considered an SSO bus. The shielding should be done both on the board and inside the package unless otherwise described.

In-package shielding can be achieved in several ways; the required shielding will vary depending on whether pins next to SSO bus are LVTTL/LVCMOS inputs, LVTTL/LVCMOS outputs, or GTL/SSTL/HSTL/LVDS/LVPECL inputs and outputs. Board traces in the vicinity of the SSO bus have to be adequately shielded from mutual coupling and inductive noise that can be generated by the SSO bus. Also, noise generated by the SSO bus needs to be reduced inside the package.

PCBs perform an important function in feeding stable supply voltages to the IC and, at the same time, maintaining signal integrity between devices.

Key issues that need to considered are as follows:

- Power and ground plane design and decoupling network design

- · Transmission line reflections and terminations

# Summary of I/O Timing Characteristics – Default I/O Software Settings

Table 2-90 • Summary of AC Measuring Points

Applicable to All I/O Bank Types

| Standard                   | Input Reference Voltage (VREF_TYP) | Board Termination Voltage (VTT_REF) | Measuring Trip Point<br>(Vtrip)         |

|----------------------------|------------------------------------|-------------------------------------|-----------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | _                                  | _                                   | 1.4 V                                   |

| 2.5 V LVCMOS               | -                                  | -                                   | 1.2 V                                   |

| 1.8 V LVCMOS               | -                                  | -                                   | 0.90 V                                  |

| 1.5 V LVCMOS               | -                                  | -                                   | 0.75 V                                  |

| 3.3 V PCI                  | -                                  | -                                   | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)) |

| 3.3 V PCI-X                | -                                  | -                                   | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)  |

| 3.3 V GTL                  | 0.8 V                              | 1.2 V                               | VREF                                    |

| 2.5 V GTL                  | 0.8 V                              | 1.2 V                               | VREF                                    |

| 3.3 V GTL+                 | 1.0 V                              | 1.5 V                               | VREF                                    |

| 2.5 V GTL+                 | 1.0 V                              | 1.5 V                               | VREF                                    |

| HSTL (I)                   | 0.75 V                             | 0.75 V                              | VREF                                    |

| HSTL (II)                  | 0.75 V                             | 0.75 V                              | VREF                                    |

| SSTL2 (I)                  | 1.25 V                             | 1.25 V                              | VREF                                    |

| SSTL2 (II)                 | 1.25 V                             | 1.25 V                              | VREF                                    |

| SSTL3 (I)                  | 1.5 V                              | 1.485 V                             | VREF                                    |

| SSTL3 (II)                 | 1.5 V                              | 1.485 V                             | VREF                                    |

| LVDS                       | -                                  | -                                   | Cross point                             |

| LVPECL                     | -                                  | -                                   | Cross point                             |

Table 2-91 • I/O AC Parameter Definitions

| Parameter         | Definition                                                                  |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer with Schmitt trigger disabled    |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>PYS</sub>  | Pad to Data delay through the Input Buffer with Schmitt trigger enabled     |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

#### Table 2-132 • 1.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 12.33           | 0.04             | 1.42            | 0.43              | 11.79           | 12.33           | 2.45            | 2.32            | ns    |

|                   | -1             | 0.56              | 10.49           | 0.04             | 1.21            | 0.36              | 10.03           | 10.49           | 2.08            | 1.98            | ns    |

|                   | -2             | 0.49              | 9.21            | 0.03             | 1.06            | 0.32              | 8.81            | 9.21            | 1.83            | 1.73            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-133 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.65            | 0.04             | 1.42            | 0.43              | 6.31            | 7.65            | 2.45            | 2.45            | ns    |

|                   | <b>–</b> 1     | 0.56              | 6.50            | 0.04             | 1.21            | 0.36              | 5.37            | 6.50            | 2.08            | 2.08            | ns    |

|                   | -2             | 0.49              | 5.71            | 0.03             | 1.06            | 0.32              | 4.71            | 5.71            | 1.83            | 1.83            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

# I/O Register Specifications

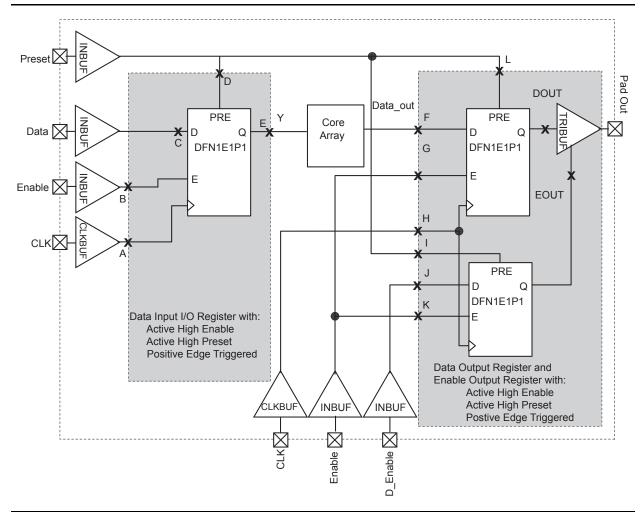

# Fully Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

Figure 2-137 • Timing Model of Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

#### IEEE 1532 Characteristics

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/Os" section on page 2-132 for more details.

## **Timing Characteristics**

Table 2-186 • JTAG 1532

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | -2    | <b>–</b> 1 | Std.  | Units |

|----------------------|-----------------------------|-------|------------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 0.50  | 0.57       | 0.67  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 1.00  | 1.13       | 1.33  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 0.50  | 0.57       | 0.67  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 1.00  | 1.13       | 1.33  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 6.00  | 6.80       | 8.00  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 20.00 | 22.67      | 26.67 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 25.00 | 22.00      | 19.00 | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.00  | 0.00       | 0.00  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.20  | 0.23       | 0.27  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | TBD        | TBD   | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-231 Revision 6

Table 3-3 • Input Resistance of Analog Pads

| Pads   | Pad Configuration                  | Prescaler Range  | Input Resistance to Ground |

|--------|------------------------------------|------------------|----------------------------|

| AV, AC | Analog Input (direct input to ADC) | -                | 2 kΩ (typical)             |

|        |                                    | -                | > 10 MΩ                    |

|        | Analog Input (positive prescaler)  | +16 V to +2 V    | 1 MΩ (typical)             |

|        |                                    | +1 V to +0.125 V | > 10 MΩ                    |

|        | Analog Input (negative prescaler)  | –16 V to –2 V    | 1 MΩ (typical)             |

|        |                                    | –1 V to –0.125 V | > 10 MΩ                    |

|        | Digital input                      | +16 V to +2 V    | 1 MΩ (typical)             |

|        | Current monitor                    | +16 V to +2 V    | 1 MΩ (typical)             |

|        |                                    | −16 V to −2 V    | 1 MΩ (typical)             |

| AT     | Analog Input (direct input to ADC) | -                | 1 MΩ (typical)             |

|        | Analog Input (positive prescaler)  | +16 V, +4 V      | 1 MΩ (typical)             |

|        | Digital input                      | +16 V, +4 V      | 1 MΩ (typical)             |

|        | Temperature monitor                | +16 V, +4 V      | > 10 MΩ                    |

Table 3-4 • Overshoot and Undershoot Limits <sup>1</sup>

| VCCI          | Average VCCI–GND Overshoot or Undershoot<br>Duration as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                              | 1.4 V                                         |

|               | 5%                                                                                               | 1.49 V                                        |

| 3.0 V         | 10%                                                                                              | 1.1 V                                         |

|               | 5%                                                                                               | 1.19 V                                        |

| 3.3 V         | 10%                                                                                              | 0.79 V                                        |

|               | 5%                                                                                               | 0.88 V                                        |

| 3.6 V         | 10%                                                                                              | 0.45 V                                        |

|               | 5%                                                                                               | 0.54 V                                        |

#### Notes:

- 1. Based on reliability requirements at a junction temperature of 85°C.

- 2. The duration is allowed at one cycle out of six clock cycle. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

|            |                 | FG256           |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| E13        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| E14        | GCC2/IO33NDB1V0 | IO42NDB1V0      | IO32NDB2V0      | IO46NDB2V0       |

| E15        | GCB2/IO33PDB1V0 | GBC2/IO42PDB1V0 | GBC2/IO32PDB2V0 | GBC2/IO46PDB2V0  |

| E16        | GND             | GND             | GND             | GND              |

| F1         | NC              | NC              | IO79NDB4V0      | IO111NDB4V0      |

| F2         | NC              | NC              | IO79PDB4V0      | IO111PDB4V0      |

| F3         | GFB1/IO48PPB3V0 | IO72NDB3V0      | IO76NDB4V0      | IO112NDB4V0      |

| F4         | GFC0/IO49NDB3V0 | IO72PDB3V0      | IO76PDB4V0      | IO112PDB4V0      |

| F5         | NC              | NC              | IO82PSB4V0      | IO120PSB4V0      |

| F6         | GFC1/IO49PDB3V0 | GAC2/IO74PPB3V0 | GAC2/IO83PPB4V0 | GAC2/IO123PPB4V0 |

| F7         | NC              | IO09RSB0V0      | IO04PPB0V0      | IO05PPB0V1       |

| F8         | NC              | IO19RSB0V0      | IO08NDB0V1      | IO11NDB0V1       |

| F9         | NC              | NC              | IO20PDB1V0      | IO27PDB1V1       |

| F10        | NC              | IO29RSB0V0      | IO23NDB1V1      | IO37NDB1V2       |

| F11        | NC              | IO43NDB1V0      | IO36NDB2V0      | IO50NDB2V0       |

| F12        | NC              | IO43PDB1V0      | IO36PDB2V0      | IO50PDB2V0       |

| F13        | NC              | IO44NDB1V0      | IO39NDB2V0      | IO59NDB2V0       |

| F14        | NC              | GCA2/IO44PDB1V0 | GCA2/IO39PDB2V0 | GCA2/IO59PDB2V0  |

| F15        | GCC1/IO34PDB1V0 | GCB2/IO45PDB1V0 | GCB2/IO40PDB2V0 | GCB2/IO60PDB2V0  |

| F16        | GCC0/IO34NDB1V0 | IO45NDB1V0      | IO40NDB2V0      | IO60NDB2V0       |

| G1         | GEC0/IO46NPB3V0 | IO70NPB3V0      | IO74NPB4V0      | IO109NPB4V0      |

| G2         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| G3         | GEC1/IO46PPB3V0 | GFB2/IO70PPB3V0 | GFB2/IO74PPB4V0 | GFB2/IO109PPB4V0 |

| G4         | GFA1/IO47PDB3V0 | GFA2/IO71PDB3V0 | GFA2/IO75PDB4V0 | GFA2/IO110PDB4V0 |

| G5         | GND             | GND             | GND             | GND              |

| G6         | GFA0/IO47NDB3V0 | IO71NDB3V0      | IO75NDB4V0      | IO110NDB4V0      |

| G7         | GND             | GND             | GND             | GND              |

| G8         | VCC             | VCC             | VCC             | VCC              |

| G9         | GND             | GND             | GND             | GND              |

| G10        | VCC             | VCC             | VCC             | VCC              |

| G11        | GDA1/IO37NDB1V0 | GCC0/IO47NDB1V0 | GCC0/IO43NDB2V0 | GCC0/IO62NDB2V0  |

| G12        | GND             | GND             | GND             | GND              |

| G13        | IO37PDB1V0      | GCC1/IO47PDB1V0 | GCC1/IO43PDB2V0 | GCC1/IO62PDB2V0  |

| G14        | GCB0/IO35NPB1V0 | IO46NPB1V0      | IO41NPB2V0      | IO61NPB2V0       |

| G15        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| G16        | GCB1/IO35PPB1V0 | GCC2/IO46PPB1V0 | GCC2/IO41PPB2V0 | GCC2/IO61PPB2V0  |

| H1         | GEB1/IO45PDB3V0 | GFC2/IO69PDB3V0 | GFC2/IO73PDB4V0 | GFC2/IO108PDB4V0 |

| H2         | GEB0/IO45NDB3V0 | IO69NDB3V0      | IO73NDB4V0      | IO108NDB4V0      |

Fusion Family of Mixed Signal FPGAs

|               | FG484           |                  |  |  |

|---------------|-----------------|------------------|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |

| P21           | IO51PDB2V0      | IO73PDB2V0       |  |  |

| P22           | IO49NDB2V0      | IO71NDB2V0       |  |  |

| R1            | IO69PDB4V0      | IO102PDB4V0      |  |  |

| R2            | IO69NDB4V0      | IO102NDB4V0      |  |  |

| R3            | VCCIB4          | VCCIB4           |  |  |

| R4            | IO64PDB4V0      | IO91PDB4V0       |  |  |

| R5            | IO64NDB4V0      | IO91NDB4V0       |  |  |

| R6            | NC              | IO92PDB4V0       |  |  |

| R7            | GND             | GND              |  |  |

| R8            | GND             | GND              |  |  |

| R9            | VCC33A          | VCC33A           |  |  |

| R10           | GNDA            | GNDA             |  |  |

| R11           | VCC33A          | VCC33A           |  |  |

| R12           | GNDA            | GNDA             |  |  |

| R13           | VCC33A          | VCC33A           |  |  |

| R14           | GNDA            | GNDA             |  |  |

| R15           | VCC             | VCC              |  |  |

| R16           | GND             | GND              |  |  |

| R17           | NC              | IO74NDB2V0       |  |  |

| R18           | GDA0/IO54NDB2V0 | GDA0/IO81NDB2V0  |  |  |

| R19           | GDB0/IO53NDB2V0 | GDB0/IO80NDB2V0  |  |  |

| R20           | VCCIB2          | VCCIB2           |  |  |

| R21           | IO50NDB2V0      | IO75NDB2V0       |  |  |

| R22           | IO50PDB2V0      | IO75PDB2V0       |  |  |

| T1            | NC              | IO100PPB4V0      |  |  |

| T2            | GND             | GND              |  |  |

| Т3            | IO66PDB4V0      | IO95PDB4V0       |  |  |

| T4            | IO66NDB4V0      | IO95NDB4V0       |  |  |

| T5            | VCCIB4          | VCCIB4           |  |  |

| T6            | NC              | IO92NDB4V0       |  |  |

| T7            | GNDNVM          | GNDNVM           |  |  |

| T8            | GNDA            | GNDA             |  |  |

| Т9            | NC              | NC               |  |  |

| T10           | AV4             | AV4              |  |  |

| T11           | NC              | NC               |  |  |

| FG484         |                 |                  |  |

|---------------|-----------------|------------------|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |

| T12           | AV5             | AV5              |  |

| T13           | AC5             | AC5              |  |

| T14           | NC              | NC               |  |

| T15           | GNDA            | GNDA             |  |

| T16           | NC              | IO77PPB2V0       |  |

| T17           | NC              | IO74PDB2V0       |  |

| T18           | VCCIB2          | VCCIB2           |  |

| T19           | IO55NDB2V0      | IO82NDB2V0       |  |

| T20           | GDA2/IO55PDB2V0 | GDA2/IO82PDB2V0  |  |

| T21           | GND             | GND              |  |

| T22           | GDC1/IO52PDB2V0 | GDC1/IO79PDB2V0  |  |

| U1            | IO67PDB4V0      | IO98PDB4V0       |  |

| U2            | IO67NDB4V0      | IO98NDB4V0       |  |

| U3            | GEC1/IO63PDB4V0 | GEC1/IO90PDB4V0  |  |

| U4            | GEC0/IO63NDB4V0 | GEC0/IO90NDB4V0  |  |

| U5            | GND             | GND              |  |

| U6            | VCCNVM          | VCCNVM           |  |

| U7            | VCCIB4          | VCCIB4           |  |

| U8            | VCC15A          | VCC15A           |  |

| U9            | GNDA            | GNDA             |  |

| U10           | AC4             | AC4              |  |

| U11           | VCC33A          | VCC33A           |  |

| U12           | GNDA            | GNDA             |  |

| U13           | AG5             | AG5              |  |

| U14           | GNDA            | GNDA             |  |

| U15           | PUB             | PUB              |  |

| U16           | VCCIB2          | VCCIB2           |  |

| U17           | TDI             | TDI              |  |

| U18           | GND             | GND              |  |

| U19           | IO57NDB2V0      | IO84NDB2V0       |  |

| U20           | GDC2/IO57PDB2V0 | GDC2/IO84PDB2V0  |  |

| U21           | NC              | IO77NPB2V0       |  |

| U22           | GDC0/IO52NDB2V0 | GDC0/IO79NDB2V0  |  |

| V1            | GEB1/IO62PDB4V0 | GEB1/IO89PDB4V0  |  |

| V2            | GEB0/IO62NDB4V0 | GEB0/IO89NDB4V0  |  |

| FG484         |                 |                  |  |

|---------------|-----------------|------------------|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |

| V3            | VCCIB4          | VCCIB4           |  |

| V4            | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  |  |

| V5            | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  |  |

| V6            | GND             | GND              |  |

| V7            | VCC33PMP        | VCC33PMP         |  |

| V8            | NC              | NC               |  |

| V9            | VCC33A          | VCC33A           |  |

| V10           | AG4             | AG4              |  |

| V11           | AT4             | AT4              |  |

| V12           | ATRTN2          | ATRTN2           |  |

| V13           | AT5             | AT5              |  |

| V14           | VCC33A          | VCC33A           |  |

| V15           | NC              | NC               |  |

| V16           | VCC33A          | VCC33A           |  |

| V17           | GND             | GND              |  |

| V18           | TMS             | TMS              |  |

| V19           | VJTAG           | VJTAG            |  |

| V20           | VCCIB2          | VCCIB2           |  |

| V21           | TRST            | TRST             |  |

| V22           | TDO             | TDO              |  |

| W1            | NC              | IO93PDB4V0       |  |

| W2            | GND             | GND              |  |

| W3            | NC              | IO93NDB4V0       |  |

| W4            | GEB2/IO59PDB4V0 | GEB2/IO86PDB4V0  |  |

| W5            | IO59NDB4V0      | IO86NDB4V0       |  |

| W6            | AV0             | AV0              |  |

| W7            | GNDA            | GNDA             |  |

| W8            | AV1             | AV1              |  |

| W9            | AV2             | AV2              |  |

| W10           | GNDA            | GNDA             |  |

| W11           | AV3             | AV3              |  |

| W12           | AV6             | AV6              |  |

| W13           | GNDA            | GNDA             |  |

| W14           | AV7             | AV7              |  |

| W15           | AV8             | AV8              |  |

| FG484         |                 |                  |  |

|---------------|-----------------|------------------|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |

| W16           | GNDA            | GNDA             |  |

| W17           | AV9             | AV9              |  |

| W18           | VCCIB2          | VCCIB2           |  |

| W19           | NC              | IO68PPB2V0       |  |

| W20           | TCK             | TCK              |  |

| W21           | GND             | GND              |  |

| W22           | NC              | IO76PPB2V0       |  |

| Y1            | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |  |

| Y2            | IO60NDB4V0      | IO87NDB4V0       |  |

| Y3            | GEA2/IO58PDB4V0 | GEA2/IO85PDB4V0  |  |

| Y4            | IO58NDB4V0      | IO85NDB4V0       |  |

| Y5            | NCAP            | NCAP             |  |

| Y6            | AC0             | AC0              |  |

| Y7            | VCC33A          | VCC33A           |  |

| Y8            | AC1             | AC1              |  |

| Y9            | AC2             | AC2              |  |

| Y10           | VCC33A          | VCC33A           |  |

| Y11           | AC3             | AC3              |  |

| Y12           | AC6             | AC6              |  |

| Y13           | VCC33A          | VCC33A           |  |

| Y14           | AC7             | AC7              |  |

| Y15           | AC8             | AC8              |  |

| Y16           | VCC33A          | VCC33A           |  |

| Y17           | AC9             | AC9              |  |

| Y18           | ADCGNDREF       | ADCGNDREF        |  |

| Y19           | PTBASE          | PTBASE           |  |

| Y20           | GNDNVM          | GNDNVM           |  |

| Y21           | VCCNVM          | VCCNVM           |  |

| Y22           | VPUMP           | VPUMP            |  |

4-26 Revision 6

## Fusion Family of Mixed Signal FPGAs

| Revision                 | Changes                                                                                                                                                                                  | Page  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance v0.6 (continued) | The "Analog-to-Digital Converter Block" section was updated with the following statement:  "All results are MSB justified in the ADC."                                                   | 2-99  |

|                          | The information about the ADCSTART signal was updated in the "ADC Description" section.                                                                                                  | 2-102 |

|                          | Table 2-46 · Analog Channel Specifications was updated.                                                                                                                                  | 2-118 |

|                          | Table 2-47 · ADC Characteristics in Direct Input Mode was updated.                                                                                                                       | 2-121 |

|                          | Table 2-51 • ACM Address Decode Table for Analog Quad was updated.                                                                                                                       | 2-127 |

|                          | In Table 2-53 • Analog Quad ACM Byte Assignment, the Function and Default Setting for Bit 6 in Byte 3 was updated.                                                                       | 2-130 |

|                          | The "Introduction" section was updated to include information about digital inputs, outputs, and bibufs.                                                                                 | 2-133 |

|                          | In Table 2-69 • Fusion Pro I/O Features, the programmable delay descriptions were updated for the following features:  Single-ended receiver                                             | 2-137 |

|                          | Voltage-referenced differential receiver                                                                                                                                                 |       |

|                          | LVDS/LVPECL differential receiver features                                                                                                                                               |       |

|                          | The "User I/O Naming Convention" section was updated to include "V" and "z" descriptions                                                                                                 | 2-159 |

|                          | The "VCC33PMP Analog Power Supply (3.3 V)" section was updated to include information about avoiding high current draw.                                                                  | 2-224 |

|                          | The "VCCNVM Flash Memory Block Power Supply (1.5 V)" section was updated to include information about avoiding high current draw.                                                        | 2-224 |

|                          | The "VMVx I/O Supply Voltage (quiet)" section was updated to include this statement: VMV and VCCI must be connected to the same power supply and $V_{CCI}$ pins within a given I/O bank. | 2-185 |

|                          | The "PUB Push Button" section was updated to include information about leaving the pin floating if it is not used.                                                                       | 2-228 |

|                          | The "PTBASE Pass Transistor Base" section was updated to include information about leaving the pin floating if it is not used.                                                           | 2-228 |

|                          | The "PTEM Pass Transistor Emitter" section was updated to include information about leaving the pin floating if it is not used.                                                          | 2-228 |

|                          | The heading was incorrect in the "208-Pin PQFP" table. It should be AFS250 and not AFS090.                                                                                               | 3-8   |