E·XFI

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | -                                                            |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | 27648                                                        |

| Number of I/O                  | 75                                                           |

| Number of Gates                | 90000                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 256-LBGA                                                     |

| Supplier Device Package        | 256-FPBGA (17x17)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs090-2fg256 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Clock Conditioning Circuits

In Fusion devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations.

The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides.

Each CCC can implement up to three independent global buffers (with or without programmable delay), or a PLL function (programmable frequency division/multiplication, phase shift, and delays) with up to three global outputs. Unused global outputs of a PLL can be used to implement independent global buffers, up to a maximum of three global outputs for a given CCC.

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, and CLKC-GLC) of a given CCC.

A PLL macro uses the CLKA CCC input to drive its reference clock. It uses the GLA and, optionally, the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global output cannot be reused if the YB (or YC) output is used (Figure 2-19). Refer to the "PLL Macro" section on page 2-27 for more information.

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- · 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

- The FPGA core

The CCC block is fully configurable, either via flash configuration bits set in the programming bitstream or through an asynchronous interface. This asynchronous interface is dynamically accessible from inside the Fusion device to permit changes of parameters (such as divide ratios) during device operation. To increase the versatility and flexibility of the clock conditioning system, the CCC configuration is determined either by the user during the design process, with configuration data being stored in flash memory as part of the device programming procedure, or by writing data into a dedicated shift register during normal device operation. This latter mode allows the user to dynamically reconfigure the CCC without the need for core programming. The shift register is accessed through a simple serial interface. Refer to the "UJTAG Applications in Microsemi's Low-Power Flash Devices" chapter of the *Fusion FPGA Fabric User Guide* and the "CCC and PLL Characteristics" section on page 2-28 for more information.

Device Architecture

# PLL Macro

The PLL functionality of the clock conditioning block is supported by the PLL macro. Note that the PLL macro reference clock uses the CLKA input of the CCC block, which is only accessible from the global A[2:0] package pins. Refer to Figure 2-22 on page 2-25 for more information.

The PLL macro provides five derived clocks (three independent) from a single reference clock. The PLL feedback loop can be driven either internally or externally. The PLL macro also provides power-down input and lock output signals. During power-up, POWERDOWN should be asserted Low until VCC is up. See Figure 2-19 on page 2-23 for more information.

Inputs:

- · CLKA: selected clock input

- POWERDOWN (active low): disables PLLs. The default state is power-down on (active low).

Outputs:

- LOCK (active high): indicates that PLL output has locked on the input reference signal

- GLA, GLB, GLC: outputs to respective global networks

- YB, YC: allows output from the CCC to be routed back to the FPGA core

As previously described, the PLL allows up to five flexible and independently configurable clock outputs. Figure 2-23 on page 2-26 illustrates the various clock output options and delay elements.

As illustrated, the PLL supports three distinct output frequencies from a given input clock. Two of these (GLB and GLC) can be routed to the B and C global networks, respectively, and/or routed to the device core (YB and YC).

There are five delay elements to support phase control on all five outputs (GLA, GLB, GLC, YB, and YC).

There is also a delay element in the feedback loop that can be used to advance the clock relative to the reference clock.

The PLL macro reference clock can be driven by an INBUF macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

The PLL macro reference clock can be driven directly from the FPGA core.

The PLL macro reference clock can also be driven from an I/O routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate it from the hardwired I/O connection described earlier.

The visual PLL configuration in SmartGen, available with the Libero SoC and Designer tools, will derive the necessary internal divider ratios based on the input frequency and desired output frequencies selected by the user. SmartGen allows the user to select the various delays and phase shift values necessary to adjust the phases between the reference clock (CLKA) and the derived clocks (GLA, GLB, GLC, YB, and YC). SmartGen also allows the user to select where the input clock is coming from. SmartGen automatically instantiates the special macro, PLLINT, when needed.

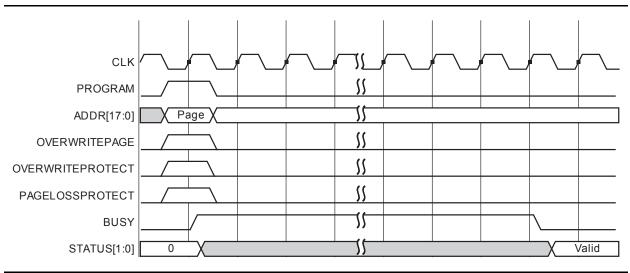

# **Program Operation**

A Program operation is initiated by asserting the PROGRAM signal on the interface. Program operations save the contents of the Page Buffer to the FB Array. Due to the technologies inherent in the FB, the total programming (including erase) time per page of the eNVM is 6.8 ms. While the FB is writing the data to the array, the BUSY signal will be asserted.

During a Program operation, the sector and page addresses on ADDR are compared with the stored address for the page (and sector) in the Page Buffer. If there is a mismatch between the two addresses, the Program operation will be aborted and an error will be reported on the STATUS output.

It is possible to write the Page Buffer to a different page in memory. When asserting the PROGRAM pin, if OVERWRITEPAGE is asserted as well, the FB will write the contents of the Page Buffer to the sector and page designated on the ADDR inputs if the destination page is not Overwrite Protected.

A Program operation can be utilized to either modify the contents of the page in the flash memory block or change the protections for the page. Setting the OVERWRITEPROTECT bit on the interface while asserting the PROGRAM pin will put the page addressed into Overwrite Protect Mode. Overwrite Protect Mode safeguards a page from being inadvertently overwritten during subsequent Program or Erase operations.

Program operations that result in a STATUS value of '01' do not modify the addressed page. For all other values of STATUS, the addressed page is modified. Program errors include the following:

- 1. Attempting to program a page that is Overwrite Protected (STATUS = '01')

- 2. Attempting to program a page that is not in the Page Buffer when the Page Buffer has entered Page Loss Protection Mode (STATUS = '01')

- Attempting to perform a program with OVERWRITEPAGE set when the page addressed has been Overwrite Protected (STATUS = '01')

- 4. The Write Count of the page programmed exceeding the Write Threshold defined in the part specification (STATUS = '11')

- 5. The ECC Logic determining that there is an uncorrectable error within the programmed page (STATUS = '10')

- 6. Attempting to program a page that is **not** in the Page Buffer when OVERWRITEPAGE is not set and the page in the Page Buffer is modified (STATUS = '01')

- 7. Attempting to program the page in the Page Buffer when the Page Buffer is **not** modified

The waveform for a Program operation is shown in Figure 2-36.

## Figure 2-36 • FB Program Waveform

Note: OVERWRITEPAGE is only sampled when the PROGRAM or ERASEPAGE pins are asserted. OVERWRITEPAGE is ignored in all other operations.

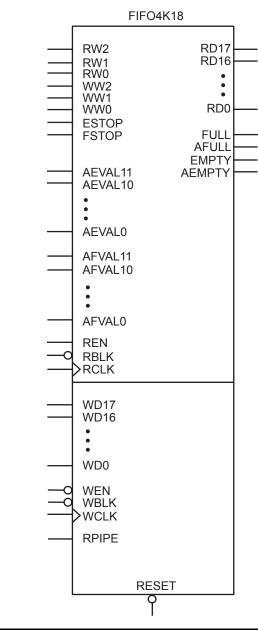

# Modes of Operation

There are two read modes and one write mode:

- Read Nonpipelined (synchronous—1 clock edge): In the standard read mode, new data is driven

onto the RD bus in the same clock cycle following RA and REN valid. The read address is

registered on the read port clock active edge, and data appears at RD after the RAM access time.

Setting PIPE to OFF enables this mode.

- Read Pipelined (synchronous—2 clock edges): The pipelined mode incurs an additional clock delay from the address to the data but enables operation at a much higher frequency. The read address is registered on the read port active clock edge, and the read data is registered and appears at RD after the second read clock edge. Setting PIPE to ON enables this mode.

- Write (synchronous—1 clock edge): On the write clock active edge, the write data is written into the SRAM at the write address when WEN is High. The setup times of the write address, write enables, and write data are minimal with respect to the write clock. Write and read transfers are described with timing requirements in the "SRAM Characteristics" section on page 2-63 and the "FIFO Characteristics" section on page 2-72.

#### **RAM Initialization**

Each SRAM block can be individually initialized on power-up by means of the JTAG port using the UJTAG mechanism (refer to the "JTAG IEEE 1532" section on page 2-229 and the *Fusion SRAM/FIFO Blocks* application note). The shift register for a target block can be selected and loaded with the proper bit configuration to enable serial loading. The 4,608 bits of data can be loaded in a single operation.

# FIFO4K18 Description

Figure 2-56 • FIFO4KX18

| Signal Name     | Number<br>of Bits | Direction | Function                                                  | Location of<br>Details |

|-----------------|-------------------|-----------|-----------------------------------------------------------|------------------------|

| AG6             | 1                 | Output    |                                                           | Analog Quad            |

| AT6             | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN67      | 1                 | Input     | Temperature monitor return shared by Analog Quads 6 and 7 | Analog Quad            |

| AV7             | 1                 | Input     | Analog Quad 7                                             | Analog Quad            |

| AC7             | 1                 | Input     |                                                           | Analog Quad            |

| AG7             | 1                 | Output    |                                                           | Analog Quad            |

| AT7             | 1                 | Input     |                                                           | Analog Quad            |

| AV8             | 1                 | Input     | Analog Quad 8                                             | Analog Quad            |

| AC8             | 1                 | Input     |                                                           | Analog Quad            |

| AG8             | 1                 | Output    |                                                           | Analog Quad            |

| AT8             | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN89      | 1                 | Input     | Temperature monitor return shared by Analog Quads 8 and 9 | Analog Quad            |

| AV9             | 1                 | Input     | Analog Quad 9                                             | Analog Quad            |

| AC9             | 1                 | Input     |                                                           | Analog Quad            |

| AG9             | 1                 | Output    |                                                           | Analog Quad            |

| AT9             | 1                 | Input     |                                                           | Analog Quad            |

| RTCMATCH        | 1                 | Output    | МАТСН                                                     | RTC                    |

| RTCPSMMATCH     | 1                 | Output    | MATCH connected to VRPSM                                  | RTC                    |

| RTCXTLMODE[1:0] | 2                 | Output    | Drives XTLOSC RTCMODE[1:0] pins                           | RTC                    |

| RTCXTLSEL       | 1                 | Output    | Drives XTLOSC MODESEL pin                                 | RTC                    |

| RTCCLK          | 1                 | Input     | RTC clock input                                           | RTC                    |

### Table 2-36 • Analog Block Pin Description (continued)

# **Analog Quad**

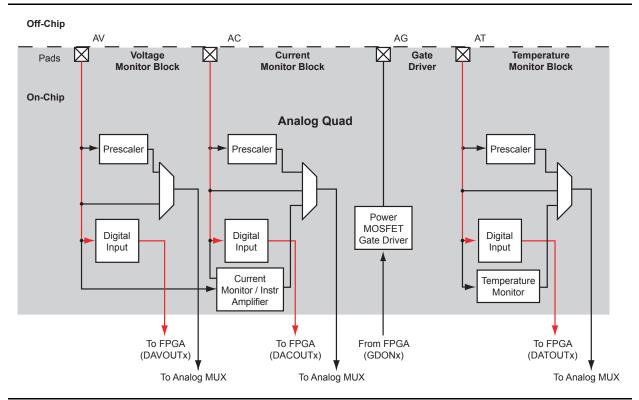

With the Fusion family, Microsemi introduces the Analog Quad, shown in Figure 2-65 on page 2-81, as the basic analog I/O structure. The Analog Quad is a four-channel system used to precondition a set of analog signals before sending it to the ADC for conversion into a digital signal. To maximize the usefulness of the Analog Quad, the analog input signals can also be configured as LVTTL digital input signals. The Analog Quad is divided into four sections.

The first section is called the Voltage Monitor Block, and its input pin is named AV. It contains a twochannel analog multiplexer that allows an incoming analog signal to be routed directly to the ADC or allows the signal to be routed to a prescaler circuit before being sent to the ADC. The prescaler can be configured to accept analog signals between -12 V and 0 or between 0 and +12 V. The prescaler circuit scales the voltage applied to the ADC input pad such that it is compatible with the ADC input voltage range. The AV pin can also be used as a digital input pin.

The second section of the Analog Quad is called the Current Monitor Block. Its input pin is named AC. The Current Monitor Block contains all the same functions as the Voltage Monitor Block with one addition, which is a current monitoring function. A small external current sensing resistor (typically less than 1  $\Omega$ ) is connected between the AV and AC pins and is in series with a power source. The Current Monitor Block contains a current monitor circuit that converts the current through the external resistor to a voltage that can then be read using the ADC.

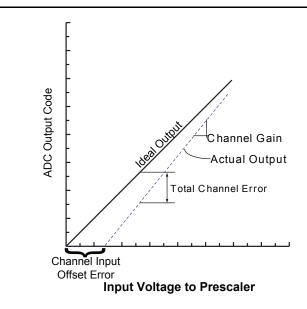

#### Channel Input Offset Error

Channel Offset error is measured as the input voltage that causes the transition from zero to a count of one. An Ideal Prescaler will have offset equal to  $\frac{1}{2}$  of LSB voltage. Offset error is a positive or negative when the first transition point is higher or lower than ideal. Offset error is expressed in LSB or input voltage.

#### **Total Channel Error**

Total Channel Error is defined as the total error measured compared to the ideal value. Total Channel Error is the sum of gain error and offset error combined. Figure 2-68 shows how Total Channel Error is measured.

Total Channel Error is defined as the difference between the actual ADC output and ideal ADC output. In the example shown in Figure 2-68, the Total Channel Error would be a negative number.

Figure 2-68 • Total Channel Error Example

# **Direct Digital Input**

The AV, AC, and AT pads can also be configured as high-voltage digital inputs (Figure 2-69). As these pads are 12 V–tolerant, the digital input can also be up to 12 V. However, the frequency at which these pads can operate is limited to 10 MHz.

To enable one of these analog input pads to operate as a digital input, its corresponding Digital Input Enable (DENAxy) pin on the Analog Block must be pulled High, where x is either V, C, or T (for AV, AC, or AT pads, respectively) and y is in the range 0 to 9, corresponding to the appropriate Analog Quad.

When the pad is configured as a digital input, the signal will come out of the Analog Block macro on the appropriate DAxOUTy pin, where x represents the pad type (V for AV pad, C for AC pad, or T for AT pad) and y represents the appropriate Analog Quad number. Example: If the AT pad in Analog Quad 5 is configured as a digital input, it will come out on the DATOUT5 pin of the Analog Block macro.

Figure 2-69 • Analog Quad Direct Digital Input Configuration

Device Architecture

#### Table 2-49 • Analog Channel Specifications (continued)

#### Commercial Temperature Range Conditions, $T_J = 85^{\circ}C$ (unless noted otherwise), Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter           | Description              | Condition                                                            | Min. | Тур.       | Max. | Units |

|---------------------|--------------------------|----------------------------------------------------------------------|------|------------|------|-------|

| Digital Input u     | using Analog Pads AV, AC | and AT                                                               |      | I          |      | 1     |

| VIND <sup>2,3</sup> | Input Voltage            | Refer to Table 3-2 on page 3-3                                       |      |            |      |       |

| VHYSDIN             | Hysteresis               |                                                                      |      | 0.3        |      | V     |

| VIHDIN              | Input High               |                                                                      |      | 1.2        |      | V     |

| VILDIN              | Input Low                |                                                                      |      | 0.9        |      | V     |

| VMPWDIN             | Minimum Pulse With       |                                                                      | 50   |            |      | ns    |

| F <sub>DIN</sub>    | Maximum Frequency        |                                                                      |      |            | 10   | MHz   |

| ISTBDIN             | Input Leakage Current    |                                                                      |      | 2          |      | μA    |

| IDYNDIN             | Dynamic Current          |                                                                      |      | 20         |      | μA    |

| t <sub>INDIN</sub>  | Input Delay              |                                                                      |      | 10         |      | ns    |

| Gate Driver O       | utput Using Analog Pad A | G                                                                    |      | <b>I I</b> |      |       |

| VG                  | Voltage Range            | Refer to Table 3-2 on page 3-3                                       |      |            |      |       |

| IG                  | Output Current Drive     | High Current Mode <sup>6</sup> at 1.0 V                              |      |            | ±20  | mA    |

|                     |                          | Low Current Mode: ±1 µA                                              | 0.8  | 1.0        | 1.3  | μA    |

|                     |                          | Low Current Mode: ±3 µA                                              | 2.0  | 2.7        | 3.3  | μA    |

|                     |                          | Low Current Mode: ± 10 µA                                            | 7.4  | 9.0        | 11.5 | μA    |

|                     |                          | Low Current Mode: ± 30 µA                                            | 21.0 | 27.0       | 32.0 | μA    |

| IOFFG               | Maximum Off Current      |                                                                      |      |            | 100  | nA    |

| F <sub>G</sub>      | Maximum switching rate   | High Current Mode <sup>6</sup> at 1.0 V, 1 k $\Omega$ resistive load |      | 1.3        |      | MHz   |

|                     |                          | Low Current Mode:<br>±1 μA, 3 MΩ resistive load                      |      | 3          |      | KHz   |

|                     |                          | Low Current Mode:<br>±3 μA, 1 MΩ resistive load                      |      | 7          |      | KHz   |

|                     |                          | Low Current Mode: $\pm 10 \ \mu$ A, 300 k $\Omega$ resistive load    |      | 25         |      | KHz   |

|                     |                          | Low Current Mode: $\pm 30 \ \mu$ A, 105 k $\Omega$ resistive load    |      | 78         |      | KHz   |

Notes:

1. VRSM is the maximum voltage drop across the current sense resistor.

2. Analog inputs used as digital inputs can tolerate the same voltage limits as the corresponding analog pad. There is no reliability concern on digital inputs as long as VIND does not exceed these limits.

3. VIND is limited to VCC33A + 0.2 to allow reaching 10 MHz input frequency.

4. An averaging of 1,024 samples (LPF setting in Analog System Builder) is required and the maximum capacitance allowed across the AT pins is 500 pF.

- 5. The temperature offset is a fixed positive value.

- 6. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

- 7. When using SmartGen Analog System Builder, CalibIP is required to obtain specified offset. For further details on CalibIP, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

## Table 2-68 • I/O Bank Support by Device

| I/O Bank     | AFS090 | AFS250 | AFS600 | AFS1500 |

|--------------|--------|--------|--------|---------|

| Standard I/O | Ν      | Ν      | -      | -       |

| Advanced I/O | E, W   | E, W   | E, W   | E, W    |

| Pro I/O      | -      | -      | Ν      | N       |

| Analog Quad  | S      | S      | S      | S       |

*Note: E* = *East side of the device*

W = West side of the device

*N* = *North* side of the device

S = South side of the device

# Table 2-69 • Fusion VCCI Voltages and Compatible Standards

| VCCI (typical) | Compatible Standards                                                                              |

|----------------|---------------------------------------------------------------------------------------------------|

| 3.3 V          | LVTTL/LVCMOS 3.3, PCI 3.3, SSTL3 (Class I and II),* GTL+ 3.3, GTL 3.3,* LVPECL                    |

| 2.5 V          | LVCMOS 2.5, LVCMOS 2.5/5.0, SSTL2 (Class I and II),* GTL+ 2.5,* GTL 2.5,* LVDS, BLVDS, M-<br>LVDS |

| 1.8 V          | LVCMOS 1.8                                                                                        |

| 1.5 V          | LVCMOS 1.5, HSTL (Class I),* HSTL (Class II)*                                                     |

*Note:* \*I/O standard supported by Pro I/O banks.

## Table 2-70 • Fusion VREF Voltages and Compatible Standards\*

| VREF (typical) | Compatible Standards            |

|----------------|---------------------------------|

| 1.5 V          | SSTL3 (Class I and II)          |

| 1.25 V         | SSTL2 (Class I and II)          |

| 1.0 V          | GTL+ 2.5, GTL+ 3.3              |

| 0.8 V          | GTL 2.5, GTL 3.3                |

| 0.75 V         | HSTL (Class I), HSTL (Class II) |

*Note:* \*I/O standards supported by Pro I/O banks.

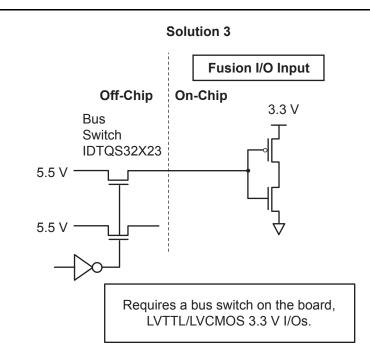

# Solution 3

The board-level design must ensure that the reflected waveform at the pad does not exceed limits provided in Table 3-4 on page 3-4. This is a long-term reliability requirement.

This scheme will also work for a 3.3 V PCI/PCIX configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the bus switch, as shown in Figure 2-105. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

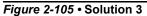

# Solution 4

Figure 2-106 • Solution 4

# Table 2-93 • Summary of I/O Timing Characteristics – Software Default SettingsCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V,Worst-Case VCCI = I/O Standard DependentApplicable to Advanced I/Os

|                              |                     |           |                      |                         |        | r    |      |      | 1     |      |      |      |      | r    |      |       |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|------|------|------|-------|------|------|------|------|------|------|-------|

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t роит | top  | toin | tev  | teour | tzı  | tzH  | tız  | ZHţ  | tzLS | tzHS | Units |

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 12 mA               | High      | 35 pF                | -                       | 0.49   | 2.64 | 0.03 | 0.90 | 0.32  | 2.69 | 2.11 | 2.40 | 2.68 | 4.36 | 3.78 | ns    |

| 2.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | _                       | 0.49   | 2.66 | 0.03 | 0.98 | 0.32  | 2.71 | 2.56 | 2.47 | 2.57 | 4.38 | 4.23 | ns    |

| 1.8 V LVCMOS                 | 12 mA               | High      | 35 pF                | -                       | 0.49   | 2.64 | 0.03 | 0.91 | 0.32  | 2.69 | 2.27 | 2.76 | 3.05 | 4.36 | 3.94 | ns    |

| 1.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | -                       | 0.49   | 3.05 | 0.03 | 1.07 | 0.32  | 3.10 | 2.67 | 2.95 | 3.14 | 4.77 | 4.34 | ns    |

| 3.3 V PCI                    | Per PCI<br>spec     | High      | 10 pF                | 25 <sup>2</sup>         | 0.49   | 2.00 | 0.03 | 0.65 | 0.32  | 2.04 | 1.46 | 2.40 | 2.68 | 3.71 | 3.13 | ns    |

| 3.3 V PCI-X                  | Per PCI-X<br>spec   | High      | 10 pF                | 25 <sup>2</sup>         | 0.49   | 2.00 | 0.03 | 0.62 | 0.32  | 2.04 | 1.46 | 2.40 | 2.68 | 3.71 | 3.13 | ns    |

| LVDS                         | 24 mA               | High      | -                    | -                       | 0.49   | 1.37 | 0.03 | 1.20 | N/A   | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | ns    |

| LVPECL                       | 24 mA               | High      | -                    | -                       | 0.49   | 1.34 | 0.03 | 1.05 | N/A   | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | ns    |

Notes:

1. For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

2. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-123 on page 2-197 for connectivity. This resistor is not required during normal operation.

# Table 2-94 • Summary of I/O Timing Characteristics – Software Default SettingsCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V,Worst-Case VCCI = I/O Standard DependentApplicable to Standard I/Os

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t pour | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>Þ</sub> v | teour | tzı  | tzH  | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|-----------------|------------------|------------------|-------|------|------|-----------------|-----------------|-------|

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 8 mA                | High      | 35 pF                | -                       | 0.49   | 3.29            | 0.03             | 0.75             | 0.32  | 3.36 | 2.80 | 1.79            | 2.01            | ns    |

| 2.5 V LVCMOS                 | 8 mA                | High      | 35pF                 | -                       | 0.49   | 3.56            | 0.03             | 0.96             | 0.32  | 3.40 | 3.56 | 1.78            | 1.91            | ns    |

| 1.8 V LVCMOS                 | 4 mA                | High      | 35pF                 | -                       | 0.49   | 4.74            | 0.03             | 0.90             | 0.32  | 4.02 | 4.74 | 1.80            | 1.85            | ns    |

| 1.5 V LVCMOS                 | 2 mA                | High      | 35pF                 |                         | 0.49   | 5.71            | 0.03             | 1.06             | 0.32  | 4.71 | 5.71 | 1.83            | 1.83            | ns    |

Note: For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

Device Architecture

# Table 2-96 • I/O Output Buffer Maximum Resistances <sup>1</sup> (continued)

| Standard                         | Drive Strength | R <sub>PULL-DOWN</sub><br>(ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|----------------------------------|----------------|-----------------------------------------------|---------------------------------------------|

| Applicable to Standard I/O Banks |                |                                               |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA           | 100                                           | 300                                         |

|                                  | 4 mA           | 100                                           | 300                                         |

|                                  | 6 mA           | 50                                            | 150                                         |

|                                  | 8 mA           | 50                                            | 150                                         |

| 2.5 V LVCMOS                     | 2 mA           | 100                                           | 200                                         |

|                                  | 4 mA           | 100                                           | 200                                         |

|                                  | 6 mA           | 50                                            | 100                                         |

|                                  | 8 mA           | 50                                            | 100                                         |

| 1.8 V LVCMOS                     | 2 mA           | 200                                           | 225                                         |

|                                  | 4 mA           | 100                                           | 112                                         |

| 1.5 V LVCMOS                     | 2 mA           | 200                                           | 224                                         |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

2. R<sub>(PULL-DOWN-MAX)</sub> = VOLspec / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

#### Table 2-97 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|       | R <sub>(WEAK F</sub><br>(oh | PULL-UP)<br>ms) | R <sub>(WEAK PULL-DOWN)</sub> 2<br>(ohms) |       |  |

|-------|-----------------------------|-----------------|-------------------------------------------|-------|--|

| VCCI  | Min.                        | Max.            | Min.                                      | Max.  |  |

| 3.3 V | 10 k                        | 45 k            | 10 k                                      | 45 k  |  |

| 2.5 V | 11 k                        | 55 k            | 12 k                                      | 74 k  |  |

| 1.8 V | 18 k                        | 70 k            | 17 k                                      | 110 k |  |

| 1.5 V | 19 k                        | 90 k            | 19 k                                      | 140 k |  |

Notes:

R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>WEAK PULL-UP-MIN</sub>

R<sub>(WEAK PULL-DOWN-MAX)</sub> = VOLspec / I<sub>WEAK PULL-DOWN-MIN</sub>

Device Architecture

# 2.5 V LVCMOS

Low-Voltage CMOS for 2.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 2.5 V applications.

| 2.5 V<br>LVCMOS   | v          | IL        | v         | ІН        | VOL       | VОН       | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|------------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V  | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| Applicable to     | Pro I/O Ba | inks      |           | •         | •         |           |     |    |                         | •                       |                  |                  |

| 4 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10               | 10               |

| 8 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10               | 10               |

| 12 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 12  | 12 | 74                      | 65                      | 10               | 10               |

| 16 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 16  | 16 | 87                      | 83                      | 10               | 10               |

| 24 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 24  | 24 | 124                     | 169                     | 10               | 10               |

| Applicable to     | Advanced   | I/O Bank  | s         | •         | •         |           |     |    |                         | •                       |                  |                  |

| 2 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 2   | 2  | 18                      | 16                      | 10               | 10               |

| 4 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10               | 10               |

| 6 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 6   | 6  | 37                      | 32                      | 10               | 10               |

| 8 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10               | 10               |

| 12 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 12  | 12 | 74                      | 65                      | 10               | 10               |

| 16 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 16  | 16 | 87                      | 83                      | 10               | 10               |

| 24 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 24  | 24 | 124                     | 169                     | 10               | 10               |

| Applicable to     | Standard   | I/O Banks |           |           |           |           |     |    |                         |                         |                  |                  |

| 2 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 2   | 2  | 18                      | 16                      | 10               | 10               |

| 4 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10               | 10               |

| 6 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 6   | 6  | 37                      | 32                      | 10               | 10               |

| 8 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10               | 10               |

## Table 2-110 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

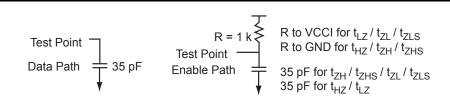

## Figure 2-120 • AC Loading

Table 2-111 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 2.5            | 1.2                  | _               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

# Table 2-122 • 1.8 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade  | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.            | 0.66              | 15.53           | 0.04             | 1.31            | 0.43              | 14.11           | 15.53           | 2.78            | 1.60            | 16.35            | 17.77            | ns    |

|                   | -1              | 0.56              | 13.21           | 0.04             | 1.11            | 0.36              | 12.01           | 13.21           | 2.36            | 1.36            | 13.91            | 15.11            | ns    |

|                   | -2 <sup>2</sup> | 0.49              | 11.60           | 0.03             | 0.98            | 0.32              | 10.54           | 11.60           | 2.07            | 1.19            | 12.21            | 13.27            | ns    |

| 4 mA              | Std.            | 0.66              | 10.48           | 0.04             | 1.31            | 0.43              | 10.41           | 10.48           | 3.23            | 2.73            | 12.65            | 12.71            | ns    |

|                   | -1              | 0.56              | 8.91            | 0.04             | 1.11            | 0.36              | 8.86            | 8.91            | 2.75            | 2.33            | 10.76            | 10.81            | ns    |

|                   | -2              | 0.49              | 7.82            | 0.03             | 0.98            | 0.32              | 7.77            | 7.82            | 2.41            | 2.04            | 9.44             | 9.49             | ns    |

| 8 mA              | Std.            | 0.66              | 8.05            | 0.04             | 1.31            | 0.43              | 8.20            | 7.84            | 3.54            | 3.27            | 10.43            | 10.08            | ns    |

|                   | -1              | 0.56              | 6.85            | 0.04             | 1.11            | 0.36              | 6.97            | 6.67            | 3.01            | 2.78            | 8.88             | 8.57             | ns    |

|                   | -2              | 0.49              | 6.01            | 0.03             | 0.98            | 0.32              | 6.12            | 5.86            | 2.64            | 2.44            | 7.79             | 7.53             | ns    |

| 12 mA             | Std.            | 0.66              | 7.50            | 0.04             | 1.31            | 0.43              | 7.64            | 7.30            | 3.61            | 3.41            | 9.88             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.38            | 0.04             | 1.11            | 0.36              | 6.50            | 6.21            | 3.07            | 2.90            | 8.40             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.60            | 0.03             | 0.98            | 0.32              | 5.71            | 5.45            | 2.69            | 2.55            | 7.38             | 7.12             | ns    |

| 16 mA             | Std.            | 0.66              | 7.29            | 0.04             | 1.31            | 0.43              | 7.23            | 7.29            | 3.71            | 3.95            | 9.47             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.20            | 0.04             | 1.11            | 0.36              | 6.15            | 6.20            | 3.15            | 3.36            | 8.06             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.45            | 0.03             | 0.98            | 0.32              | 5.40            | 5.45            | 2.77            | 2.95            | 7.07             | 7.12             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Timing Characteristics

#### Table 2-136 • 3.3 V PCI/PCI-X

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Pro I/Os

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.81            | 0.04             | 1.05            | 1.67             | 0.43              | 2.86            | 2.00            | 3.28            | 3.61            | 5.09             | 4.23             | ns    |

| -1             | 0.56              | 2.39            | 0.04             | 0.89            | 1.42             | 0.36              | 2.43            | 1.70            | 2.79            | 3.07            | 4.33             | 3.60             | ns    |

| -2             | 0.49              | 2.09            | 0.03             | 0.78            | 1.25             | 0.32              | 2.13            | 1.49            | 2.45            | 2.70            | 3.80             | 3.16             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Table 2-137 • 3.3 V PCI/PCI-X

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Advanced I/Os

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.68            | 0.04             | 0.86            | 0.43             | 2.73              | 1.95            | 3.21            | 3.58            | 4.97            | 4.19             | 0.66             | ns    |

| -1             | 0.56              | 2.28            | 0.04             | 0.73            | 0.36             | 2.32              | 1.66            | 2.73            | 3.05            | 4.22            | 3.56             | 0.56             | ns    |

| -2             | 0.49              | 2.00            | 0.03             | 0.65            | 0.32             | 2.04              | 1.46            | 2.40            | 2.68            | 3.71            | 3.13             | 0.49             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

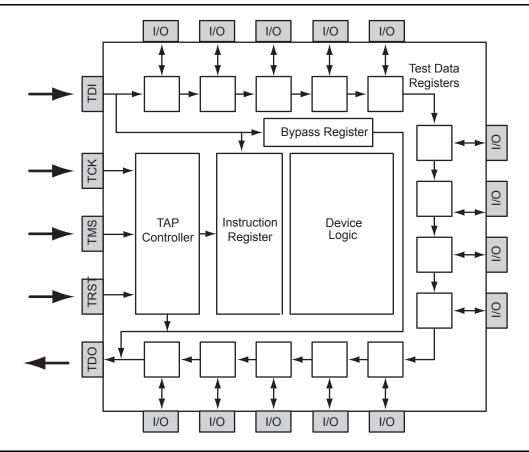

connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Figure 2-146 • Boundary Scan Chain in Fusion

Table 2-185 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

| Symbol                        | Parameter                                          | Commercial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Industrial    | Units |

|-------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|

| AV, AC                        | Unpowered, ADC reset asserted or unconfigured      | -11.0 to 12.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -11.0 to 12.0 | V     |

|                               | Analog input (+16 V to +2 V prescaler range)       | -0.4 to 12.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.4 to 12.0  | V     |

|                               | Analog input (+1 V to +0.125 V prescaler range)    | -0.4 to 3.75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.4 to 3.75  | V     |

|                               | Analog input (–16 V to –2 V prescaler range)       | resetassertedor $-11.0$ to 12.6 $-11.0$ to 12.0 $a + 2$ V prescaler range) $-0.4$ to 12.6 $-0.4$ to 12.0to $+0.125$ V prescaler $-0.4$ to 3.75 $-0.4$ to 3.75 $a - 2$ V prescaler range) $-11.0$ to 0.4 $-11.0$ to 0.4to $-0.125$ V prescaler $-3.75$ to 0.4 $-3.75$ to 0.4to $-0.125$ V prescaler $-0.4$ to 3.75 $-0.4$ to 3.75pout to ADC) $-0.4$ to 3.75 $-0.4$ to 3.75 $-0.4$ to 12.6 $-0.4$ to 12.0resetassertedor $-11.0$ to 12.6 $-11.0$ to 12.0 $\mu A, 3$ $\mu A, 10$ $\mu A, 30$ $\mu A$ ) $-0.4$ to 12.6 $-0.4$ to 12.0 $-11.0$ to 12.0 $\mu A, -3$ $\mu A, -10$ $\mu A, -30$ $-11.0$ to 12.6 $-11.0$ to 12.6 $-11.0$ to 12.0resetassertedor $-0.4$ to 16.0 $-0.4$ to 15.0V prescaler range) $-0.4$ to 16.0 $-0.4$ to 15.0 | V             |       |

|                               | Analog input (–1 V to –0.125 V prescaler range)    | -3.75 to 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -3.75 to 0.4  | V     |

|                               | Analog input (direct input to ADC)                 | -0.4 to 3.75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.4 to 3.75  | V     |

|                               | Digital input                                      | -0.4 to 12.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.4 to 12.0  | V     |

| AG                            | Unpowered, ADC reset asserted or<br>unconfigured   | -11.0 to 12.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -11.0 to 12.0 | V     |

|                               | Low Current Mode (1 µA, 3 µA, 10 µA, 30 µA)        | -0.4 to 12.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.4 to 12.0  | V     |

|                               | Low Current Mode (–1 μΑ, –3 μΑ, –10 μΑ, –30<br>μΑ) | -11.0 to 0.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -11.0 to 0.4  | V     |

|                               | High Current Mode <sup>3</sup>                     | -11.0 to 12.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -11.0 to 12.0 | V     |

| AT                            | Unpowered, ADC reset asserted or unconfigured      | -0.4 to 16.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | –0.4 to 15.0  | V     |

|                               | Analog input (+16 V, 4 V prescaler range)          | -0.4 to 16.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.4 to 15.0  | V     |

|                               | Analog input (direct input to ADC)                 | -0.4 to 3.75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.4 to 3.75  | V     |

|                               | Digital input                                      | -0.4 to 16.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.4 to 15.0  | V     |

| T <sub>STG</sub> <sup>4</sup> | Storage temperature                                | -65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | to +150       | °C    |

| Tj <sup>4</sup>               | Junction temperature                               | +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -125          | °C    |

| Table 3-1 • | Absolute | Maximum | Ratings | (continued) |

|-------------|----------|---------|---------|-------------|

|-------------|----------|---------|---------|-------------|

Notes:

1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-4.

2. Analog data not valid beyond 3.65 V.

3. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

4. For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.

| Symbol              | Parameter <sup>2</sup>              |                               | Commercial     | Industrial     | Units |

|---------------------|-------------------------------------|-------------------------------|----------------|----------------|-------|

| TJ                  | Junction temperature                |                               | 0 to +85       | -40 to +100    | °C    |

| VCC                 | 1.5 V DC core supply voltage        |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VJTAG               | JTAG DC voltage                     |                               | 1.4 to 3.6     | 1.4 to 3.6     | V     |

| VPUMP               | Programming voltage                 | Programming mode <sup>3</sup> | 3.15 to 3.45   | 3.15 to 3.45   | V     |

|                     |                                     | Operation <sup>4</sup>        | 0 to 3.6       | 0 to 3.6       | V     |

| VCCPLL              | Analog power supply (PLL)           |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCI                | 1.5 V DC supply voltage             |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

|                     | 1.8 V DC supply voltage             |                               | 1.7 to 1.9     | 1.7 to 1.9     | V     |

|                     | 2.5 V DC supply voltage             | 2.3 to 2.7                    | 2.3 to 2.7     | V              |       |

|                     | 3.3 V DC supply voltage             | 3.0 to 3.6                    | 3.0 to 3.6     | V              |       |

|                     | LVDS differential I/O               | 2.375 to 2.625                | 2.375 to 2.625 | V              |       |

|                     | LVPECL differential I/O             | 3.0 to 3.6                    | 3.0 to 3.6     | V              |       |

| VCC33A              | +3.3 V power supply                 |                               | 2.97 to 3.63   | 2.97 to 3.63   | V     |

| VCC33PMP            | +3.3 V power supply                 | 2.97 to 3.63                  | 2.97 to 3.63   | V              |       |

| VAREF               | Voltage reference for ADC           | 2.527 to 2.593                | 2.527 to 2.593 | V              |       |

| VCC15A <sup>5</sup> | Digital power supply for the analog | 1.425 to 1.575                | 1.425 to 1.575 | V              |       |

| VCCNVM              | Embedded flash power supply         |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCOSC              | Oscillator power supply             |                               | 2.97 to 3.63   | 2.97 to 3.63   | V     |

| AV, AC <sup>6</sup> | Unpowered, ADC reset asserted o     | r unconfigured                | -10.5 to 12.0  | -10.5 to 11.6  | V     |

|                     | Analog input (+16 V to +2 V presca  | –0.3 to 12.0                  | –0.3 to 11.6   | V              |       |

|                     | Analog input (+1 V to + 0.125 V pre | escaler range)                | -0.3 to 3.6    | -0.3 to 3.6    | V     |

|                     | Analog input (-16 V to -2 V presca  | aler range)                   | -10.5 to 0.3   | -10.5 to 0.3   | V     |

|                     | Analog input (-1 V to -0.125 V pre  | scaler range)                 | -3.6 to 0.3    | -3.6 to 0.3    | V     |

|                     | Analog input (direct input to ADC)  | -0.3 to 3.6                   | -0.3 to 3.6    | V              |       |

|                     | Digital input                       | –0.3 to 12.0                  | –0.3 to 11.6   | V              |       |

| AG <sup>6</sup>     | Unpowered, ADC reset asserted o     | r unconfigured                | -10.5 to 12.0  | -10.5 to 11.6  | V     |

|                     | Low Current Mode (1 µA, 3 µA, 10    | μΑ, 30 μΑ)                    | –0.3 to 12.0   | –0.3 to 11.6   | V     |

|                     | Low Current Mode (-1 µA, -3 µA,     | -10.5 to 0.3                  | -10.5 to 0.3   | V              |       |

|                     | High Current Mode <sup>7</sup>      | -10.5 to 12.0                 | -10.5 to 11.6  | V              |       |

| AT <sup>6</sup>     | Unpowered, ADC reset asserted o     | r unconfigured                | –0.3 to 15.5   | –0.3 to 14.5   | V     |

|                     | Analog input (+16 V, +4 V prescale  | er range)                     | –0.3 to 15.5   | –0.3 to 14.5   | V     |

|                     | Analog input (direct input to ADC)  |                               | -0.3 to 3.6    | -0.3 to 3.6    | V     |

|                     | Digital input                       |                               | -0.3 to 15.5   | -0.3 to 14.5   | V     |

## Table 3-2 • Recommended Operating Conditions<sup>1</sup>

Notes:

1. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-85 on page 2-157.

- 2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 3. The programming temperature range supported is  $T_{ambient} = 0^{\circ}C$  to 85°C.

- 4. VPUMP can be left floating during normal operation (not programming mode).

- 5. Violating the V<sub>CC15A</sub> recommended voltage supply during an embedded flash program cycle can corrupt the page being programmed.

- 6. The input voltage may overshoot by up to 500 mV above the Recommended Maximum (150 mV in Direct mode), provided the duration of the overshoot is less than 50% of the operating lifetime of the device.

- 7. The AG pad should also conform to the limits as specified in Table 2-48 on page 2-114.

$P_{S-CELL}$  =  $N_{S-CELL}$  \* (PAC5 + ( $\alpha_1$  / 2) \* PAC6) \*  $F_{CLK}$

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 3-16 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Sleep Mode

$P_{S-CELL} = 0 W$

# Combinatorial Cells Dynamic Contribution—P<sub>C-CELL</sub>

#### **Operating Mode**

$P_{C-CELL} = N_{C-CELL} * (\alpha_1 / 2) * PAC7 * F_{CLK}$

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 3-16 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Sleep Mode

$P_{C-CELL} = 0 W$

Routing Net Dynamic Contribution—PNET

#### **Operating Mode**

$P_{NET} = (N_{S-CELL} + N_{C-CELL}) * (\alpha_1 / 2) * PAC8 * F_{CLK}$

N<sub>S-CELL</sub> is the number VersaTiles used as sequential modules in the design.

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 3-16 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Sleep Mode

$P_{NET} = 0 W$

## I/O Input Buffer Dynamic Contribution—PINPUTS

#### **Operating Mode**

$P_{INPUTS} = N_{INPUTS} * (\alpha_2 / 2) * PAC9 * F_{CLK}$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 3-16 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Sleep Mode

P<sub>INPUTS</sub> = 0 W

## I/O Output Buffer Dynamic Contribution—POUTPUTS

#### **Operating Mode**

$\mathsf{P}_{\mathsf{OUTPUTS}} = \mathsf{N}_{\mathsf{OUTPUTS}} * (\alpha_2 / 2) * \beta_1 * \mathsf{PAC10} * \mathsf{F}_{\mathsf{CLK}}$

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 3-16 on page 3-27.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 3-17 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

#### Standby Mode and Sleep Mode

P<sub>OUTPUTS</sub> = 0 W