Welcome to <u>E-XFL.COM</u>

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | - ·                                                          |

| Number of Logic Elements/Cells |                                                              |

| Total RAM Bits                 | 27648                                                        |

| Number of I/O                  | 75                                                           |

| Number of Gates                | 90000                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 256-LBGA                                                     |

| Supplier Device Package        | 256-FPBGA (17x17)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs090-fgg256 |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Fusion Device Family Overview

# Instant On

Flash-based Fusion devices are Level 0 Instant On. Instant On Fusion devices greatly simplify total system design and reduce total system cost by eliminating the need for CPLDs. The Fusion Instant On clocking (PLLs) replaces off-chip clocking resources. The Fusion mix of Instant On clocking and analog resources makes these devices an excellent choice for both system supervisor and system management functions. Instant On from a single 3.3 V source enables Fusion devices to initiate, control, and monitor multiple voltage supplies while also providing system clocks. In addition, glitches and brownouts in system power will not corrupt the Fusion device flash configuration. Unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables reduction or complete removal of expensive voltage monitor and brownout detection devices from the PCB design.

Flash-based Fusion devices simplify total system design and reduce cost and design risk, while increasing system reliability.

## Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. Another source of radiation-induced firm errors is alpha particles. For an alpha to cause a soft or firm error, its source must be in very close proximity to the affected circuit. The alpha source must be in the package molding compound or in the die itself. While low-alpha molding compounds are being used increasingly, this helps reduce but does not entirely eliminate alpha-induced firm errors.

Firm errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not occur in Fusion flash-based FPGAs. Once it is programmed, the flash cell configuration element of Fusion FPGAs cannot be altered by high-energy neutrons and is therefore immune to errors from them.

Recoverable (or soft) errors occur in the user data SRAMs of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

# Low Power

Flash-based Fusion devices exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. With Fusion devices, there is no power-on current surge and no high current transition, both of which occur on many FPGAs.

Fusion devices also have low dynamic power consumption and support both low power standby mode and very low power sleep mode, offering further power savings.

# Advanced Flash Technology

The Fusion family offers many benefits, including nonvolatility and reprogrammability through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows very high logic utilization (much higher than competing SRAM technologies) without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

# Advanced Architecture

The proprietary Fusion architecture provides granularity comparable to standard-cell ASICs. The Fusion device consists of several distinct and programmable architectural features, including the following (Figure 1-1 on page 1-5):

- Embedded memories

- Flash memory blocks

- FlashROM

- SRAM and FIFO

- Clocking resources

- PLL and CCC

- RC oscillator

- Crystal oscillator

- No-Glitch MUX (NGMUX)

- Digital I/Os with advanced I/O standards

- FPGA VersaTiles

- Analog components

- ADC

- Analog I/Os supporting voltage, current, and temperature monitoring

- 1.5 V on-board voltage regulator

- Real-time counter

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic lookup table (LUT) equivalent or a D-flip-flop or latch (with or without enable) by programming the appropriate flash switch interconnections. This versatility allows efficient use of the FPGA fabric. The VersaTile capability is unique to the Microsemi families of flash-based FPGAs. VersaTiles and larger functions are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

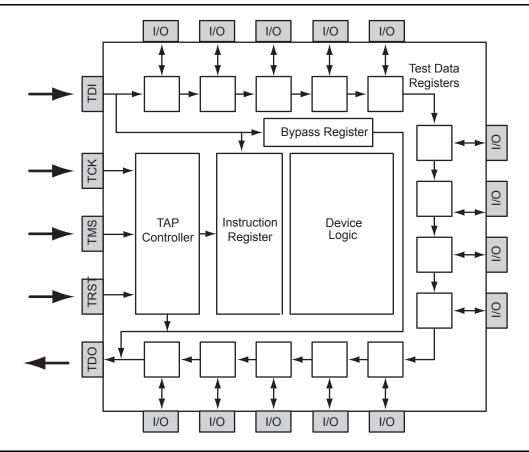

In addition, extensive on-chip programming circuitry allows for rapid (3.3 V) single-voltage programming of Fusion devices via an IEEE 1532 JTAG interface.

# **Unprecedented Integration**

# Integrated Analog Blocks and Analog I/Os

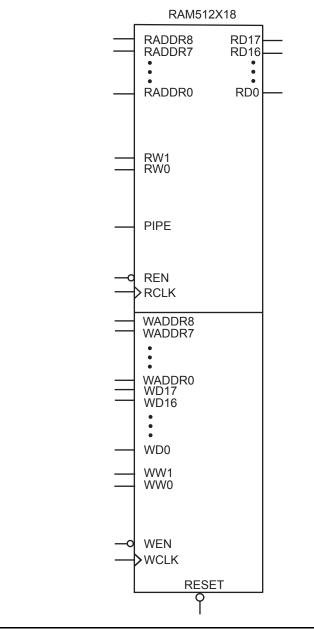

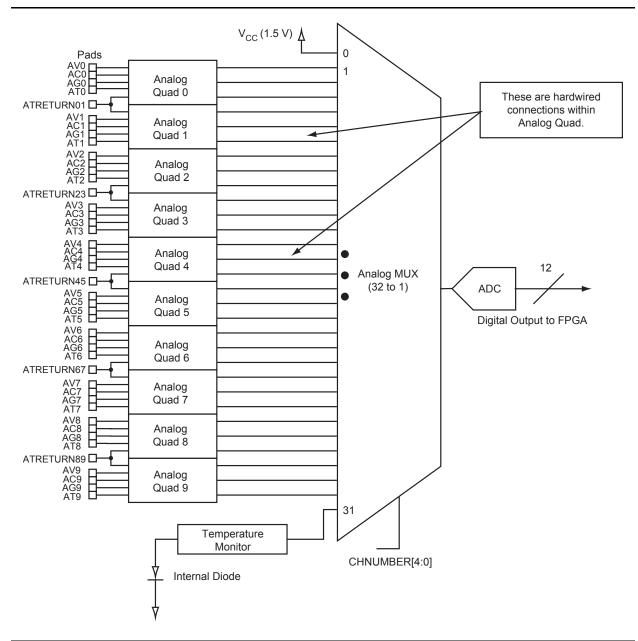

Fusion devices offer robust and flexible analog mixed signal capability in addition to the highperformance flash FPGA fabric and flash memory block. The many built-in analog peripherals include a configurable 32:1 input analog MUX, up to 10 independent MOSFET gate driver outputs, and a configurable ADC. The ADC supports 8-, 10-, and 12-bit modes of operation with a cumulative sample rate up to 600 k samples per second (Ksps), differential nonlinearity (DNL) < 1.0 LSB, and Total Unadjusted Error (TUE) of 0.72 LSB in 10-bit mode. The TUE is used for characterization of the conversion error and includes errors from all sources, such as offset and linearity. Internal bandgap circuitry offers 1% voltage reference accuracy with the flexibility of utilizing an external reference voltage. The ADC channel sampling sequence and sampling rate are programmable and implemented in the FPGA logic using Designer and Libero SoC software tool support.

Two channels of the 32-channel ADCMUX are dedicated. Channel 0 is connected internally to VCC and can be used to monitor core power supply. Channel 31 is connected to an internal temperature diode which can be used to monitor device temperature. The 30 remaining channels can be connected to external analog signals. The exact number of I/Os available for external connection signals is device-dependent (refer to the "Fusion Family" table on page I for details).

# 2 – Device Architecture

# **Fusion Stack Architecture**

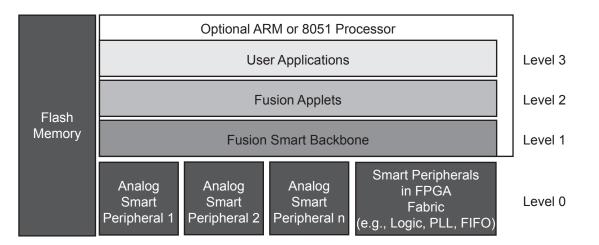

To manage the unprecedented level of integration in Fusion devices, Microsemi developed the Fusion technology stack (Figure 2-1). This layered model offers a flexible design environment, enabling design at very high and very low levels of abstraction. Fusion peripherals include hard analog IP and hard and soft digital IP. Peripherals communicate across the FPGA fabric via a layer of soft gates—the Fusion backbone. Much more than a common bus interface, this Fusion backbone integrates a micro-sequencer within the FPGA fabric and configures the individual peripherals and supports low-level processing of peripheral data. Fusion applets are application building blocks that can control and respond to peripherals and other system signals. Applets can be rapidly combined to create large applications. The technology is scalable across devices, families, design types, and user expertise, and supports a well-defined interface for external IP and tool integration.

At the lowest level, Level 0, are Fusion peripherals. These are configurable functional blocks that can be hardwired structures such as a PLL or analog input channel, or soft (FPGA gate) blocks such as a UART or two-wire serial interface. The Fusion peripherals are configurable and support a standard interface to facilitate communication and implementation.

Connecting and controlling access to the peripherals is the Fusion backbone, Level 1. The backbone is a soft-gate structure, scalable to any number of peripherals. The backbone is a bus and much more; it manages peripheral configuration to ensure proper operation. Leveraging the common peripheral interface and a low-level state machine, the backbone efficiently offloads peripheral management from the system design. The backbone can set and clear flags based upon peripheral behavior and can define performance criteria. The flexibility of the stack enables a designer to configure the silicon, directly bypassing the backbone if that level of control is desired.

One step up from the backbone is the Fusion applet, Level 2. The applet is an application building block that implements a specific function in FPGA gates. It can react to stimuli and board-level events coming through the backbone or from other sources, and responds to these stimuli by accessing and manipulating peripherals via the backbone or initiating some other action. An applet controls or responds to the peripheral(s). Applets can be easily imported or exported from the design environment. The applet structure is open and well-defined, enabling users to import applets from Microsemi, system developers, third parties, and user groups.

Note: Levels 1, 2, and 3 are implemented in FPGA logic gates.

Figure 2-1 • Fusion Architecture Stack

# **Clock Aggregation**

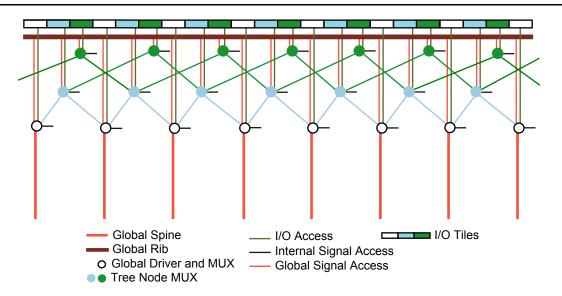

Clock aggregation allows for multi-spine clock domains. A MUX tree provides the necessary flexibility to allow long lines or I/Os to access domains of one, two, or four global spines. Signal access to the clock aggregation system is achieved through long-line resources in the central rib, and also through local resources in the north and south ribs, allowing I/Os to feed directly into the clock system. As Figure 2-14 indicates, this access system is contiguous.

There is no break in the middle of the chip for north and south I/O VersaNet access. This is different from the quadrant clocks, located in these ribs, which only reach the middle of the rib. Refer to the *Using Global Resources in Actel Fusion Devices* application note.

Figure 2-14 • Clock Aggregation Tree Architecture

# Flash Memory Block Diagram

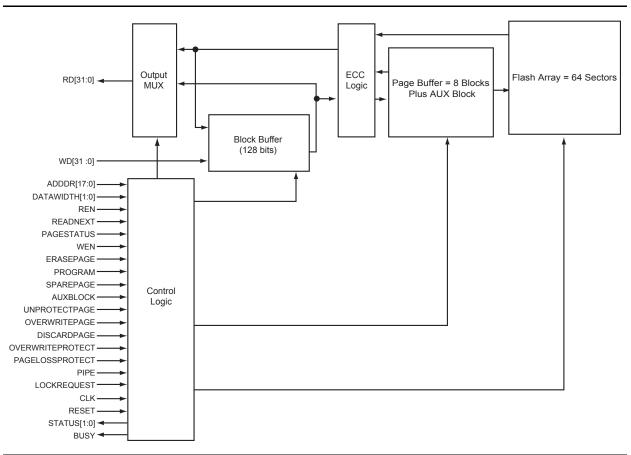

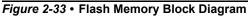

A simplified diagram of the flash memory block is shown in Figure 2-33.

The logic consists of the following sub-blocks:

Flash Array

Contains all stored data. The flash array contains 64 sectors, and each sector contains 33 pages of data.

Page Buffer

A page-wide volatile register. A page contains 8 blocks of data and an AUX block.

- Block Buffer

- Contains the contents of the last block accessed. A block contains 128 data bits.

- ECC Logic

The FB stores error correction information with each block to perform single-bit error correction and double-bit error detection on all data blocks.

# RAM512X18 Description

Figure 2-49 • RAM512X18

Device Architecture

#### *Table 2-32* • RAM512X18

## Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                        | -2   | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                 | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                  | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                | 0.09 | 0.10 | 0.12 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                 | 0.06 | 0.07 | 0.08 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained)                                                               | 2.16 | 2.46 | 2.89 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                     | 0.90 | 1.02 | 1.20 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge | 0.50 | 0.43 | 0.38 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—Applicable to Opening Edge | 0.59 | 0.50 | 0.44 | ns    |

| + 1                   | RESET Low to data out Low on RD (flow-through)                                                                     | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>RSTBQ</sub> 1  | RESET Low to data out Low on RD (pipelined)                                                                        | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                      | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                     | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                          | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                   | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                  | 310  | 272  | 231  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

2. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Device Architecture

The AEMPTY flag is asserted when the difference between the write address and the read address is less than a predefined value. In the example above, a value of 200 for AEVAL means that the AEMPTY flag will be asserted when a read causes the difference between the write address and the read address to drop to 200. It will stay asserted until that difference rises above 200. Note that the FIFO can be configured with different read and write widths; in this case, the AFVAL setting is based on the number of write data entries and the AEVAL setting is based on the number of software and 256×18, only 4,096 bits can be addressed by the 12 bits of AFVAL and AEVAL. The number of words must be multiplied by 8 and 16, instead of 9 and 18. The SmartGen tool automatically uses the proper values. To avoid halfwords being written or read, which could happen if different read and write aspect ratios are specified, the FIFO will assert FULL or EMPTY as soon as at least a minimum of one word cannot be written or read. For example, if a two-bit word is written and a four-bit word is being read, the FIFO will remain in the empty state when the first word is written. This occurs even if the FIFO is not completely empty, because in this case, a complete word cannot be read. The same is applicable in the full state. If a four-bit word is written and a two-bit word is read, the FIFO is full and one word is read. The FULL flag will remain asserted because a complete word cannot be written at this point.

The diode's voltage is measured at each current level and the temperature is calculated based on EQ 7.

$$V_{\text{TMSLO}} - V_{\text{TMSHI}} = n \frac{kT}{q} \left( \ln \frac{I_{\text{TMSLO}}}{I_{\text{TMSHI}}} \right)$$

EQ 7

where

$\textit{I}_{\textit{TMSLO}}$  is the current when the Temperature Strobe is Low, typically 100  $\mu A$

$I_{TMSHI}$  is the current when the Temperature Strobe is High, typically 10  $\mu A$

*V<sub>TMSLO</sub>* is diode voltage while Temperature Strobe is Low

$V_{TMSHI}$  is diode voltage while Temperature Strobe is High

n is the non-ideality factor of the diode-connected transistor. It is typically 1.004 for the Microsemirecommended transistor type 2N3904.

- $K = 1.3806 \text{ x } 10^{-23} \text{ J/K}$  is the Boltzman constant

- $Q = 1.602 \times 10^{-19} C$  is the charge of a proton

When  $I_{TMSLO} / I_{TMSHI} = 10$ , the equation can be simplified as shown in EQ 8.

$$\Delta V = V_{\text{TMSLO}} - V_{\text{TMSHI}} = 1.986 \times 10^{-4} nT$$

EQ 8

In the Fusion TMB, the ideality factor *n* for 2N3904 is 1.004 and  $\Delta V$  is amplified 12.5 times by an internal amplifier; hence the voltage before entering the ADC is as given in EQ 9.

$$V_{ADC} = \Delta V \times 12.5 = 2.5 \text{ mV}/(K \times T)$$

EQ 9

This means the temperature to voltage relationship is 2.5 mV per degree Kelvin. The unique design of Fusion has made the Temperature Monitor System simple for the user. When the 10-bit mode ADC is used, each LSB represents 1 degree Kelvin, as shown in EQ 10. That is, e. 25°C is equal to 293°K and is represented by decimal 293 counts from the ADC.

$$1K = 2.5 \text{ mV} \times \frac{2^{10}}{2.56 \text{ V}} = 1 \text{ LSB}$$

EQ 10

If 8-bit mode is used for the ADC resolution, each LSB represents 4 degrees Kelvin; however, the resolution remains as 1 degree Kelvin per LSB, even for 12-bit mode, due to the Temperature Monitor design. An example of the temperature data format for 10-bit mode is shown in Table 2-38.

| Temperature | Temperature (K) | Digital Output (ADC 10-bit mode) |

|-------------|-----------------|----------------------------------|

| –40°C       | 233             | 00 1110 1001                     |

| –20°C       | 253             | 00 1111 1101                     |

| 0°C         | 273             | 01 0001 0001                     |

| 1°C         | 274             | 01 0001 0010                     |

| 10 °C       | 283             | 01 0001 1011                     |

| 25°C        | 298             | 01 0010 1010                     |

| 50 °C       | 323             | 01 0100 0011                     |

| 85 °C       | 358             | 01 0110 0110                     |

Table 2-38 • Temperature Data Format

# Analog-to-Digital Converter Block

At the heart of the Fusion analog system is a programmable Successive Approximation Register (SAR) ADC. The ADC can support 8-, 10-, or 12-bit modes of operation. In 12-bit mode, the ADC can resolve 500 ksps. All results are MSB-justified in the ADC. The input to the ADC is a large 32:1 analog input multiplexer. A simplified block diagram of the Analog Quads, analog input multiplexer, and ADC is shown in Figure 2-79. The ADC offers multiple self-calibrating modes to ensure consistent high performance both at power-up and during runtime.

Figure 2-79 • ADC Block Diagram

## TUE – Total Unadjusted Error

TUE is a comprehensive specification that includes linearity errors, gain error, and offset error. It is the worst-case deviation from the ideal device performance. TUE is a static specification (Figure 2-87).

Figure 2-87 • Total Unadjusted Error (TUE)

# ADC Operation

Once the ADC has powered up and been released from reset, ADCRESET, the ADC will initiate a calibration routine designed to provide optimal ADC performance. The Fusion ADC offers a robust calibration scheme to reduce integrated offset and linearity errors. The offset and linearity errors of the main capacitor array are compensated for with an 8-bit calibration capacitor array. The offset/linearity error calibration is carried out in two ways. First, a power-up calibration is carried out when the ADC comes out of reset. This is initiated by the CALIBRATE output of the Analog Block macro and is a fixed number of ADC\_CLK cycles (3,840 cycles), as shown in Figure 2-89 on page 2-111. In this mode, the linearity and offset errors of the capacitors are calibrated.

To further compensate for drift and temperature-dependent effects, every conversion is followed by postcalibration of either the offset or a bit of the main capacitor array. The post-calibration ensures that, over time and with temperature, the ADC remains consistent.

After both calibration and the setting of the appropriate configurations, as explained above, the ADC is ready for operation. Setting the ADCSTART signal high for one clock period will initiate the sample and conversion of the analog signal on the channel as configured by CHNUMBER[4:0]. The status signals SAMPLE and BUSY will show when the ADC is sampling and converting (Figure 2-91 on page 2-112). Both SAMPLE and BUSY will initially go high. After the ADC has sampled and held the analog signal, SAMPLE will go low. After the entire operation has completed and the analog signal is converted, BUSY will go low and DATAVALID will go high. This indicates that the digital result is available on the RESULT[11:0] pins.

DATAVALID will remain high until a subsequent ADCSTART is issued. The DATAVALID goes low on the rising edge of SYSCLK as shown in Figure 2-90 on page 2-112. The RESULT signals will be kept constant until the ADC finishes the subsequent sample. The next sampled RESULT will be available when DATAVALID goes high again. It is ideal to read the RESULT when DATAVALID is '1'. The RESULT is latched and remains unchanged until the next DATAVLAID rising edge.

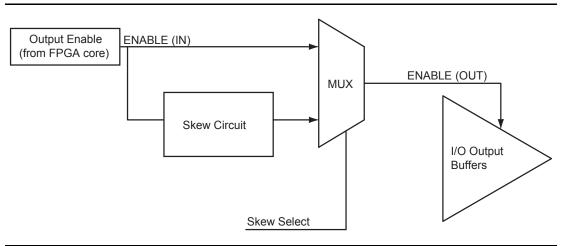

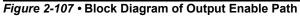

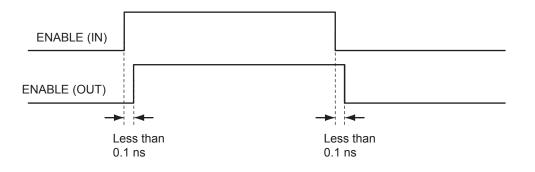

# Selectable Skew between Output Buffer Enable/Disable Time

The configurable skew block is used to delay the output buffer assertion (enable) without affecting deassertion (disable) time.

Figure 2-108 • Timing Diagram (option1: bypasses skew circuit)

Figure 2-109 • Timing Diagram (option 2: enables skew circuit)

Device Architecture

# Table 2-88 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions

|                               |                   |              | VIL VIH   |             | VOL         | VOH       | IOL         | IOH         |    |    |

|-------------------------------|-------------------|--------------|-----------|-------------|-------------|-----------|-------------|-------------|----|----|

| I/O Standard                  | Drive<br>Strength | Slew<br>Rate | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA | mA |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA              | High         | -0.3      | 0.8         | 2           | 3.6       | 0.4         | 2.4         | 8  | 8  |

| 2.5 V LVCMOS                  | 8 mA              | High         | -0.3      | 0.7         | 1.7         | 3.6       | 0.7         | 1.7         | 8  | 8  |

| 1.8 V LVCMOS                  | 4 mA              | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45        | VCCI-0.45   | 4  | 4  |

| 1.5 V LVCMOS                  | 2 mA              | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2  | 2  |

Applicable to Standard I/Os

*Note:* Currents are measured at 85°C junction temperature.

#### Table 2-89 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions

Applicable to All I/O Bank Types

|                            | Comr             | nercial <sup>1</sup> | Indu             | ustrial <sup>2</sup> |

|----------------------------|------------------|----------------------|------------------|----------------------|

|                            | IIL <sup>3</sup> | IIH <sup>4</sup>     | IIL <sup>3</sup> | IIH <sup>4</sup>     |

| DC I/O Standards           | μA               | μΑ                   | μΑ               | μΑ                   |

| 3.3 V LVTTL / 3.3 V LVCMOS | 10               | 10                   | 15               | 15                   |

| 2.5 V LVCMOS               | 10               | 10                   | 15               | 15                   |

| 1.8 V LVCMOS               | 10               | 10                   | 15               | 15                   |

| 1.5 V LVCMOS               | 10               | 10                   | 15               | 15                   |

| 3.3 V PCI                  | 10               | 10                   | 15               | 15                   |

| 3.3 V PCI-X                | 10               | 10                   | 15               | 15                   |

| 3.3 V GTL                  | 10               | 10                   | 15               | 15                   |

| 2.5 V GTL                  | 10               | 10                   | 15               | 15                   |

| 3.3 V GTL+                 | 10               | 10                   | 15               | 15                   |

| 2.5 V GTL+                 | 10               | 10                   | 15               | 15                   |

| HSTL (I)                   | 10               | 10                   | 15               | 15                   |

| HSTL (II)                  | 10               | 10                   | 15               | 15                   |

| SSTL2 (I)                  | 10               | 10                   | 15               | 15                   |

| SSTL2 (II)                 | 10               | 10                   | 15               | 15                   |

| SSTL3 (I)                  | 10               | 10                   | 15               | 15                   |

| SSTL3 (II)                 | 10               | 10                   | 15               | 15                   |

Notes:

1. Commercial range ( $0^{\circ}C < T_J < 85^{\circ}C$ )

2. Industrial range  $(-40^{\circ}C < T_{J} < 100^{\circ}C)$

3. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

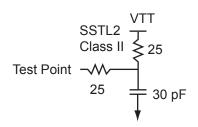

#### SSTL2 Class II

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). Fusion devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

| SSTL2 Class II |           | VIL        | VIH        |           | VOL       | VOH         | IOL | IOH | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|----------------|-----------|------------|------------|-----------|-----------|-------------|-----|-----|-------------------------|-------------------------|-----------------|------------------|

| Drive Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 18 mA          | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.35      | VCCI – 0.43 | 18  | 18  | 124                     | 169                     | 10              | 10               |

Table 2-159 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

#### Figure 2-131 • AC Loading

#### Table 2-160 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                 | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

#### Table 2-161 • SSTL 2 Class II Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.25 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.17            | 0.04             | 1.33            | 0.43              | 2.21            | 1.77            |                 |                 | 4.44             | 4.01             | ns    |

| -1             | 0.56              | 1.84            | 0.04             | 1.14            | 0.36              | 1.88            | 1.51            |                 |                 | 3.78             | 3.41             | ns    |

| -2             | 0.49              | 1.62            | 0.03             | 1.00            | 0.32              | 1.65            | 1.32            |                 |                 | 3.32             | 2.99             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Figure 2-146 • Boundary Scan Chain in Fusion

Table 2-185 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

| Product<br>Grade | Storage<br>Temperature      | Element        | Grade Programming<br>Cycles | Retention |

|------------------|-----------------------------|----------------|-----------------------------|-----------|

| Commercial       | Min. T <sub>J</sub> = 0°C   | FPGA/FlashROM  | 500                         | 20 years  |

|                  | Max. T <sub>J</sub> = 85°C  | Embedded Flash | < 1,000                     | 20 years  |

|                  |                             |                | < 10,000                    | 10 years  |

|                  |                             |                | < 15,000                    | 5 years   |

| Industrial       | Min. T <sub>J</sub> = –40°C | FPGA/FlashROM  | 500                         | 20 years  |

|                  | Max. T <sub>J</sub> = 100°C | Embedded Flash | < 1,000                     | 20 years  |

|                  |                             |                | < 10,000                    | 10 years  |

|                  |                             |                | < 15,000                    | 5 years   |

#### Table 3-5 • FPGA Programming, Storage, and Operating Limits

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every Fusion device. These circuits ensure easy transition from the powered off state to the powered up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 3-1 on page 3-6.

There are five regions to consider during power-up.

Fusion I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 3-1).

- 2. VCCI > VCC 0.75 V (typical).

- 3. Chip is in the operating mode.

#### V<sub>CCI</sub> Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.2 V

Ramping down: 0.5 V < trip\_point\_down < 1.1 V

#### V<sub>CC</sub> Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.1 V

Ramping down: 0.5 V < trip\_point\_down < 1 V

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

# Internal Power-Up Activation Sequence

- 1. Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

## PLL Behavior at Brownout Condition

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper powerup behavior. Power ramp-up should be monotonic at least until VCC and VCCPLX exceed brownout activation levels. The  $V_{CC}$  activation level is specified as 1.1 V worst-case (see Figure 3-1 on page 3-6 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels (0.75 V  $\pm$  0.25 V), the PLL output lock signal goes low and/or the output clock is lost.

# Theta-JA

Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is determined under standard conditions specified by JEDEC (JESD-51), but it has little relevance in actual performance of the product. It should be used with caution but is useful for comparing the thermal performance of one package to another.

A sample calculation showing the maximum power dissipation allowed for the AFS600-FG484 package under forced convection of 1.0 m/s and 75°C ambient temperature is as follows:

Maximum Power Allowed =

$$\frac{T_{J(MAX)} - T_{A(MAX)}}{\theta_{JA}}$$

EQ 4

where

$\theta_{JA}$  = 19.00°C/W (taken from Table 3-6 on page 3-7).

$T_A = 75.00^{\circ}C$

Maximum Power Allowed =

$$\frac{100.00^{\circ}C - 75.00^{\circ}C}{19.00^{\circ}C/W} = 1.3 W$$

EQ 5

The power consumption of a device can be calculated using the Microsemi power calculator. The device's power consumption must be lower than the calculated maximum power dissipation by the package. If the power consumption is higher than the device's maximum allowable power dissipation, a heat sink can be attached on top of the case, or the airflow inside the system must be increased.

## Theta-JB

Junction-to-board thermal resistance ( $\theta_{JB}$ ) measures the ability of the package to dissipate heat from the surface of the chip to the PCB. As defined by the JEDEC (JESD-51) standard, the thermal resistance from junction to board uses an isothermal ring cold plate zone concept. The ring cold plate is simply a means to generate an isothermal boundary condition at the perimeter. The cold plate is mounted on a JEDEC standard board with a minimum distance of 5.0 mm away from the package edge.

# Theta-JC

Junction-to-case thermal resistance ( $\theta_{JC}$ ) measures the ability of a device to dissipate heat from the surface of the chip to the top or bottom surface of the package. It is applicable for packages used with external heat sinks. Constant temperature is applied to the surface in consideration and acts as a boundary condition. This only applies to situations where all or nearly all of the heat is dissipated through the surface in consideration.

# Calculation for Heat Sink

For example, in a design implemented in an AFS600-FG484 package with 2.5 m/s airflow, the power consumption value using the power calculator is 3.00 W. The user-dependent  $T_a$  and  $T_j$  are given as follows:

$T_{J} = 100.00^{\circ}C$

$T_A = 70.00^{\circ}C$

From the datasheet:

$\theta_{JA} = 17.00^{\circ}C/W$  $\theta_{JC} = 8.28^{\circ}C/W$

$$P = \frac{T_J - T_A}{\theta_{JA}} = \frac{100^{\circ}C - 70^{\circ}C}{17.00 \text{ W}} = 1.76 \text{ W}$$

EQ 6

| Parameter          | Description                | Conditions                                                            | Temp.                  | Min | Тур  | Мах | Unit |

|--------------------|----------------------------|-----------------------------------------------------------------------|------------------------|-----|------|-----|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current    | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 4.8  | 10  | mA   |

|                    |                            | VCC = 1.575 V                                                         | T <sub>J</sub> = 85°C  |     | 8.2  | 30  | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 15   | 50  | mA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VCC = 0 V   |                        |     | 0    | 0   | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies      | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 9.8  | 13  | mA   |

|                    | current                    | VCC33 = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 9.8  | 14  | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 10.8 | 15  | mA   |

|                    |                            | Operational standby, only                                             | T <sub>J</sub> = 25°C  |     | 0.29 | 2   | mA   |

|                    |                            | Analog Quad and –3.3 V<br>output ON, VCC33 = 3.63 V                   | T <sub>J</sub> = 85°C  |     | 0.31 | 2   | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 0.45 | 2   | mA   |

|                    |                            | Standby mode <sup>5</sup> , VCC33 = 3.63V                             | T <sub>J</sub> = 25°C  |     | 2.9  | 3.0 | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 85°C  |     | 2.9  | 3.1 | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 3.5  | 6   | mA   |

|                    |                            | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                              | T <sub>J</sub> = 25°C  |     | 19   | 18  | μA   |

|                    |                            |                                                                       | T <sub>J</sub> = 85°C  |     | 19   | 20  | μΑ   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 24   | 25  | μA   |

| ICCI <sup>3</sup>  | I/O quiescent current      | Operational standby <sup>6</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 266  | 437 | μΑ   |

|                    |                            | VCClx = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 266  | 437 | μΑ   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 266  | 437 | μA   |

| IJTAG              | JTAG I/O quiescent current | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 80   | 100 | μA   |

|                    |                            | VJTAG = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 80   | 100 | μA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 80   | 100 | μA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VJTAG = 0 V |                        |     | 0    | 0   | μA   |

Notes:

1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, and ICCI2.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTA G = VPUMP = 0 V.

Datasheet Information

| Revision                           | Changes                                                                                                                                                                                                                                       | Page            |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| v2.0, Revision 1<br>(continued)    | Table 3-6 • Package Thermal Resistance was updated to include new data.                                                                                                                                                                       | 3-7             |

|                                    | In EQ 4 to EQ 6, the junction temperature was changed from 110°C to 100°C.                                                                                                                                                                    | 3-8 to 3-8      |

|                                    | Table 3-8 • AFS1500 Quiescent Supply Current Characteristics through Table 3-11 • AFS090 Quiescent Supply Current Characteristics are new and have replaced the Quiescent Supply Current Characteristics (IDDQ) table.                        | 3-10 to<br>3-16 |

|                                    | In Table 3-14 • Different Components Contributing to the Dynamic Power Consumption in Fusion Devices, the power supply for PAC9 and PAC10 were changed from VMV/VCC to VCCI.                                                                  | 3-22            |

|                                    | In Table 3-15 • Different Components Contributing to the Static Power Consumption in Fusion Devices, the power supply for PDC7 and PDC8 were changed from VMV/VCC to VCCI. PDC1 was updated from TBD to 18.                                   | 3-23            |

|                                    | The "QN108" table was updated to remove the duplicates of pins B12 and B34.                                                                                                                                                                   | 4-2             |

| Preliminary v1.7<br>(October 2008) | The version number category was changed from Advance to Preliminary, which means the datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible. |                 |

|                                    | For the VIL and VIH parameters, 0.30 * VCCI was changed to 0.35 * VCCI and 0.70 * VCCI was changed to 0.65 * VCCI in Table 2-126 • Minimum and Maximum DC Input and Output Levels.                                                            | 2-193           |

|                                    | The version number category was changed from Advance to Preliminary, which means the datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible. | N/A             |

|                                    | The following updates were made to Table 2-141 • Minimum and Maximum DC Input and Output Levels:                                                                                                                                              | 2-200           |

|                                    | Temperature Digital Output                                                                                                                                                                                                                    |                 |

|                                    | 213 00 1111 1101                                                                                                                                                                                                                              |                 |

|                                    | 283 01 0001 1011                                                                                                                                                                                                                              |                 |

|                                    | 3580101100110– only the digital output was updated.Temperature 358 remains in the temperature column.                                                                                                                                         |                 |

|                                    | In Advance v1.2, the "VAREF Analog Reference Voltage" pin description was significantly updated but the change was not noted in the change table.                                                                                             | 2-225           |

| Advance v1.6<br>(August 2008)      | The title of the datasheet changed from Actel Programmable System Chips to Actel Fusion Mixed Signal FPGAs. In addition, all instances of programmable system chip were changed to mixed signal FPGA.                                         | N/A             |

|                                    | The references to the <i>Peripherals User's Guide</i> in the "No-Glitch MUX (NGMUX)" section and "Voltage Regulator Power Supply Monitor (VRPSM)" section were changed to <i>Fusion Handbook</i> .                                            | 2-32, 2-42      |

| Advance v1.5<br>(July 2008)        | The following bullet was updated from High-Voltage Input Tolerance: ±12 V to High-Voltage Input Tolerance: 10.5 V to 12 V.                                                                                                                    | I               |

|                                    | The following bullet was updated from Programmable 1, 3, 10, 30 $\mu A$ and 25 mA Drive Strengths to Programmable 1, 3, 10, 30 $\mu A$ and 20 mA Drive Strengths.                                                                             | I               |

# **Datasheet Categories**

## Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "Fusion Device Status" table, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

# **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

## Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

## Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

## Production

This version contains information that is considered to be final.

# **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.