Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | -                                                            |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | 27648                                                        |

| Number of I/O                  | 37                                                           |

| Number of Gates                | 90000                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 108-WFQFN                                                    |

| Supplier Device Package        | 108-QFN (8x8)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs090-qng108 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| Fusion Device Family Overview                                           |       |

|-------------------------------------------------------------------------|-------|

| Introduction                                                            |       |

| General Description                                                     |       |

| Unprecedented Integration                                               |       |

| Related Documents                                                       | 1-10  |

| Device Architecture                                                     |       |

| Fusion Stack Architecture                                               |       |

| Core Architecture                                                       |       |

| Clocking Resources                                                      |       |

| Real-Time Counter System                                                | 2-3   |

| Embedded Memories                                                       |       |

| Analog Block                                                            |       |

| Analog Configuration MUX                                                | 2-126 |

| User I/Os                                                               | 2-132 |

| Pin Descriptions                                                        | 2-223 |

| Security                                                                | 2-228 |

| DC and Power Characteristics                                            |       |

| General Specifications                                                  |       |

| Calculating Power Dissipation                                           |       |

| Power Consumption                                                       | 3-32  |

| Package Pin Assignments                                                 |       |

| QN108                                                                   | 4     |

| QN180                                                                   |       |

| PQ208                                                                   |       |

| FG256                                                                   |       |

| FG484                                                                   |       |

| FG676                                                                   |       |

| Datasheet Information                                                   |       |

| List of Changes                                                         | 5     |

| Datasheet Categories                                                    |       |

| Safety Critical. Life Support, and High-Reliability Applications Policy |       |

#### Instant On

Flash-based Fusion devices are Level 0 Instant On. Instant On Fusion devices greatly simplify total system design and reduce total system cost by eliminating the need for CPLDs. The Fusion Instant On clocking (PLLs) replaces off-chip clocking resources. The Fusion mix of Instant On clocking and analog resources makes these devices an excellent choice for both system supervisor and system management functions. Instant On from a single 3.3 V source enables Fusion devices to initiate, control, and monitor multiple voltage supplies while also providing system clocks. In addition, glitches and brownouts in system power will not corrupt the Fusion device flash configuration. Unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables reduction or complete removal of expensive voltage monitor and brownout detection devices from the PCB design.

Flash-based Fusion devices simplify total system design and reduce cost and design risk, while increasing system reliability.

#### Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. Another source of radiation-induced firm errors is alpha particles. For an alpha to cause a soft or firm error, its source must be in very close proximity to the affected circuit. The alpha source must be in the package molding compound or in the die itself. While low-alpha molding compounds are being used increasingly, this helps reduce but does not entirely eliminate alpha-induced firm errors.

Firm errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not occur in Fusion flash-based FPGAs. Once it is programmed, the flash cell configuration element of Fusion FPGAs cannot be altered by high-energy neutrons and is therefore immune to errors from them.

Recoverable (or soft) errors occur in the user data SRAMs of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

#### Low Power

Flash-based Fusion devices exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. With Fusion devices, there is no power-on current surge and no high current transition, both of which occur on many FPGAs.

Fusion devices also have low dynamic power consumption and support both low power standby mode and very low power sleep mode, offering further power savings.

## **Advanced Flash Technology**

The Fusion family offers many benefits, including nonvolatility and reprogrammability through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows very high logic utilization (much higher than competing SRAM technologies) without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

1-3 Revision 6

#### **No-Glitch MUX (NGMUX)**

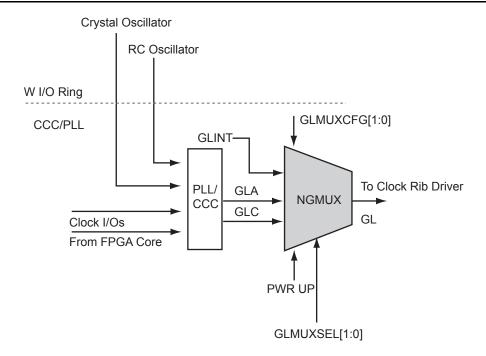

Positioned downstream from the PLL/CCC blocks, the NGMUX provides a special switching sequence between two asynchronous clock domains that prevents generating any unwanted narrow clock pulses. The NGMUX is used to switch the source of a global between three different clock sources. Allowable inputs are either two PLL/CCC outputs or a PLL/CCC output and a regular net, as shown in Figure 2-24. The GLMUXCFG[1:0] configuration bits determine the source of the CLK inputs (i.e., internal signal or GLC). These are set by SmartGen during design but can also be changed by dynamically reconfiguring the PLL. The GLMUXSEL[1:0] bits control which clock source is passed through the NGMUX to the global network (GL). See Table 2-13.

Figure 2-24 • NGMUX

Table 2-13 • NGMUX Configuration and Selection Table

| GLMUXCFG[1:0] | GLMUXSEL[1:0] |   | Selected Input Signal | MUX Type       |

|---------------|---------------|---|-----------------------|----------------|

| 00            | Х             | 0 | GLA                   | 2-to-1 GLMUX   |

| 00            | Х             | 1 | GLC                   | 2-to-1 GLIVIOX |

| 01            | Х             | 0 | GLA                   | 2-to-1 GLMUX   |

| 01            | Х             | 1 | GLINT                 | 2-10-1 GLIVIOX |

2-29 Revision 6

#### **SRAM and FIFO**

All Fusion devices have SRAM blocks along the north side of the device. Additionally, AFS600 and AFS1500 devices have an SRAM block on the south side of the device. To meet the needs of high-performance designs, the memory blocks operate strictly in synchronous mode for both read and write operations. The read and write clocks are completely independent, and each may operate at any desired frequency less than or equal to 350 MHz. The following configurations are available:

- 4k×1, 2k×2, 1k×4, 512×9 (dual-port RAM—two read, two write or one read, one write)

- 512×9, 256×18 (two-port RAM—one read and one write)

- Sync write, sync pipelined/nonpipelined read

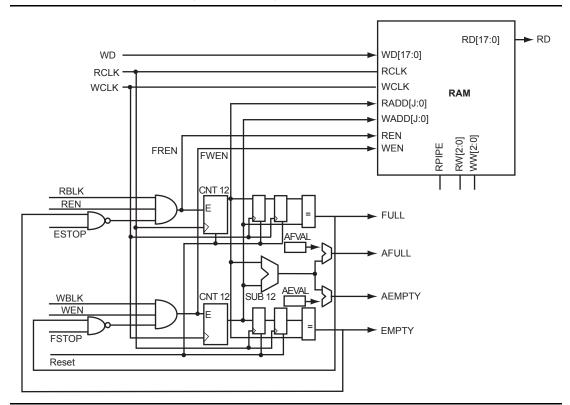

The Fusion SRAM memory block includes dedicated FIFO control logic to generate internal addresses and external flag logic (FULL, EMPTY, AFULL, AEMPTY).

During RAM operation, addresses are sourced by the user logic, and the FIFO controller is ignored. In FIFO mode, the internal addresses are generated by the FIFO controller and routed to the RAM array by internal MUXes. Refer to Figure 2-47 for more information about the implementation of the embedded FIFO controller.

The Fusion architecture enables the read and write sizes of RAMs to be organized independently, allowing for bus conversion. This is done with the WW (write width) and RW (read width) pins. The different D×W configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1. For example, the write size can be set to 256×18 and the read size to 512×9.

Both the write and read widths for the RAM blocks can be specified independently with the WW (write width) and RW (read width) pins. The different D×W configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1.

Refer to the allowable RW and WW values supported for each of the RAM macro types in Table 2-27 on page 2-58.

When a width of one, two, or four is selected, the ninth bit is unused. For example, when writing 9-bit values and reading 4-bit values, only the first four bits and the second four bits of each 9-bit value are addressable for read operations. The ninth bit is not accessible.

2-55 Revision 6

Conversely, when writing 4-bit values and reading 9-bit values, the ninth bit of a read operation will be undefined. The RAM blocks employ little-endian byte order for read and write operations.

Figure 2-47 • Fusion RAM Block with Embedded FIFO Controller

The following signals are used to configure the RAM4K9 memory element.

#### WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 2-27).

Table 2-27 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA1, WIDTHA0                          | WIDTHB1, WIDTHB0                      | D×W   |

|-------------------------------------------|---------------------------------------|-------|

| 00                                        | 00                                    | 4k×1  |

| 01                                        | 01                                    | 2k×2  |

| 10                                        | 10                                    | 1k×4  |

| 11                                        | 11                                    | 512×9 |

| Note: The aspect ratio settings are const | ant and cannot be changed on the fly. | •     |

#### **BLKA and BLKB**

These signals are active low and will enable the respective ports when asserted. When a BLKx signal is deasserted, the corresponding port's outputs hold the previous value.

#### WENA and WENB

These signals switch the RAM between read and write mode for the respective ports. A Low on these signals indicates a write operation, and a High indicates a read.

#### CLKA and CLKB

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A Low on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A High indicates a pipelined, read and data appears on the corresponding output in the next clock cycle.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A Low on these signals makes the output retain data from the previous read. A High indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

#### RESET

This active low signal resets the output to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory.

#### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 2-28).

Table 2-28 • Address Pins Unused/Used for Various Supported Bus Widths

| D×W   | ADDRx   |        |  |  |  |  |

|-------|---------|--------|--|--|--|--|

|       | Unused  | Used   |  |  |  |  |

| 4k×1  | None    | [11:0] |  |  |  |  |

| 2k×2  | [11]    | [10:0] |  |  |  |  |

| 1k×4  | [11:10] | [9:0]  |  |  |  |  |

| 512×9 | [11:9]  | [8:0]  |  |  |  |  |

Note: The "x" in ADDRx implies A or B.

#### **Modes of Operation**

There are two read modes and one write mode:

- Read Nonpipelined (synchronous—1 clock edge): In the standard read mode, new data is driven

onto the RD bus in the same clock cycle following RA and REN valid. The read address is

registered on the read port clock active edge, and data appears at RD after the RAM access time.

Setting PIPE to OFF enables this mode.

- Read Pipelined (synchronous—2 clock edges): The pipelined mode incurs an additional clock delay from the address to the data but enables operation at a much higher frequency. The read address is registered on the read port active clock edge, and the read data is registered and appears at RD after the second read clock edge. Setting PIPE to ON enables this mode.

- Write (synchronous—1 clock edge): On the write clock active edge, the write data is written into

the SRAM at the write address when WEN is High. The setup times of the write address, write

enables, and write data are minimal with respect to the write clock. Write and read transfers are

described with timing requirements in the "SRAM Characteristics" section on page 2-63 and the

"FIFO Characteristics" section on page 2-72.

#### RAM Initialization

Each SRAM block can be individually initialized on power-up by means of the JTAG port using the UJTAG mechanism (refer to the "JTAG IEEE 1532" section on page 2-229 and the *Fusion SRAM/FIFO Blocks* application note). The shift register for a target block can be selected and loaded with the proper bit configuration to enable serial loading. The 4,608 bits of data can be loaded in a single operation.

Table 2-32 • RAM512X18

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                        | -2   | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                 | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                  | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                | 0.09 | 0.10 | 0.12 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                 | 0.06 | 0.07 | 0.08 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained)                                                               | 2.16 | 2.46 | 2.89 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                     | 0.90 | 1.02 | 1.20 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge | 0.50 | 0.43 | 0.38 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—Applicable to Opening Edge | 0.59 | 0.50 | 0.44 | ns    |

| <b>,</b> 1            | RESET Low to data out Low on RD (flow-through)                                                                     | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>RSTBQ</sub> 1  | RESET Low to data out Low on RD (pipelined)                                                                        | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                      | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                     | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                          | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                   | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                  | 310  | 272  | 231  | MHz   |

#### Notes:

2-67 Revision 6

<sup>1.</sup> For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

<sup>2.</sup> For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

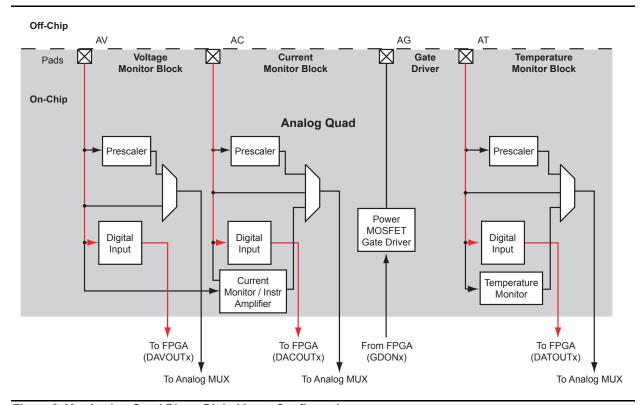

### **Direct Digital Input**

The AV, AC, and AT pads can also be configured as high-voltage digital inputs (Figure 2-69). As these pads are 12 V-tolerant, the digital input can also be up to 12 V. However, the frequency at which these pads can operate is limited to 10 MHz.

To enable one of these analog input pads to operate as a digital input, its corresponding Digital Input Enable (DENAxy) pin on the Analog Block must be pulled High, where x is either V, C, or T (for AV, AC, or AT pads, respectively) and y is in the range 0 to 9, corresponding to the appropriate Analog Quad.

When the pad is configured as a digital input, the signal will come out of the Analog Block macro on the appropriate DAxOUTy pin, where x represents the pad type (V for AV pad, C for AC pad, or T for AT pad) and y represents the appropriate Analog Quad number. Example: If the AT pad in Analog Quad 5 is configured as a digital input, it will come out on the DATOUT5 pin of the Analog Block macro.

Figure 2-69 • Analog Quad Direct Digital Input Configuration

2-85 Revision 6

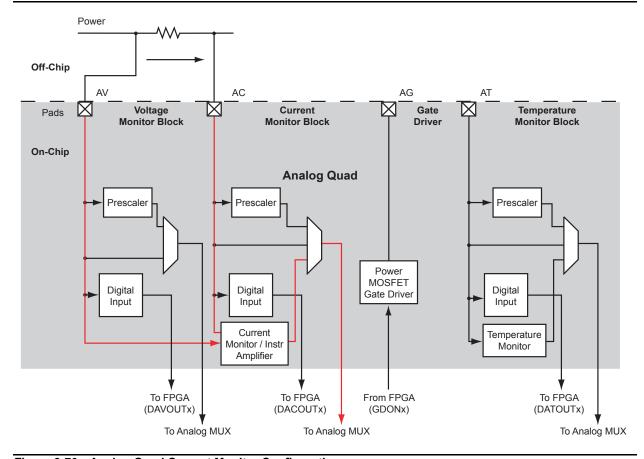

#### **Current Monitor**

The Fusion Analog Quad is an excellent element for voltage- and current-monitoring applications. In addition to supporting the same functionality offered by the AV pad, the AC pad can be configured to monitor current across an external sense resistor (Figure 2-70). To support this current monitor function, a differential amplifier with 10x gain passes the amplified voltage drop between the AV and AC pads to the ADC. The amplifier enables the user to use very small resistor values, thereby limiting any impact on the circuit. This function of the AC pad does not limit AV pad operation. The AV pad can still be configured for use as a direct voltage input or scaled through the AV prescaler independently of it's use as an input to the AC pad's differential amplifier.

Figure 2-70 • Analog Quad Current Monitor Configuration

Refer to Table 2-46 on page 2-109 and the "Acquisition Time or Sample Time Control" section on page 2-107

$$t_{\text{sample}} = (2 + STC) \times t_{\text{ADCCLK}}$$

EQ 20

STC: Sample Time Control value (0-255)

t<sub>SAMPLE</sub> is the sample time

#### Table 2-46 • STC Bits Function

| Name | Bits  | Function            |

|------|-------|---------------------|

| STC  | [7:0] | Sample time control |

Sample time is computed based on the period of ADCCLK.

#### **Distribution Phase**

The second phase is called the distribution phase. During distribution phase, the ADC computes the equivalent digital value from the value stored in the input capacitor. In this phase, the output signal SAMPLE goes back to '0', indicating the sample is completed; but the BUSY signal remains '1', indicating the ADC is still busy for distribution. The distribution time depends strictly on the number of bits. If the ADC is configured as a 10-bit ADC, then 10 ADCCLK cycles are needed. EQ 8 describes the distribution time.

$$t_{distrib} = N \times t_{ADCCLK}$$

EQ 21

N: Number of bits

#### Post-Calibration Phase

The last phase is the post-calibration phase. This is an optional phase. The post-calibration phase takes two ADCCLK cycles. The output BUSY signal will remain '1' until the post-calibration phase is completed. If the post-calibration phase is skipped, then the BUSY signal goes to '0' after distribution phase. As soon as BUSY signal goes to '0', the DATAVALID signal goes to '1', indicating the digital result is available on the RESULT output signals. DATAVAILD will remain '1' until the next ADCSTART is asserted. Microsemi recommends enabling post-calibration to compensate for drift and temperature-dependent effects. This ensures that the ADC remains consistent over time and with temperature. The post-calibration phase is enabled by bit 3 of the Mode register. EQ 9 describes the post-calibration time.

$$t_{post-cal} = MODE[3] \times (2 \times t_{ADCCLK})$$

EQ 22

MODE[3]: Bit 3 of the Mode register, described in Table 2-41 on page 2-106.

The calculation for the conversion time for the ADC is summarized in EQ 23.

EQ 23

t<sub>conv</sub>: conversion time

$t_{sync\_read}$ : maximum time for a signal to synchronize with SYSCLK. For calculation purposes, the worst case is a period of SYSCLK,  $t_{SYSCLK}$ .

t<sub>sample</sub>: Sample time t<sub>distrib</sub>: Distribution time

t<sub>post-cal</sub>: Post-calibration time

$t_{\text{sync\_write}}$ : Maximum time for a signal to synchronize with SYSCLK. For calculation purposes, the worst case is a period of SYSCLK,  $t_{\text{SYSCLK}}$ .

2-109 Revision 6

The optimal setting for the system running at 66 MHz with an ADC for 10-bit mode chosen is shown in Table 2-47:

Table 2-47 • Optimal Setting at 66 MHz in 10-Bit Mode

| TVC[7:0]  | = 1      | = 0x01 |

|-----------|----------|--------|

| STC[7:0]  | = 3      | = 0x03 |

| MODE[3:0] | = b'0100 | = 0x4* |

*Note:* No power-down after every conversion is chosen in this case; however, if the application is power-sensitive, the MODE[2] can be set to '0', as described above, and it will not affect any performance.

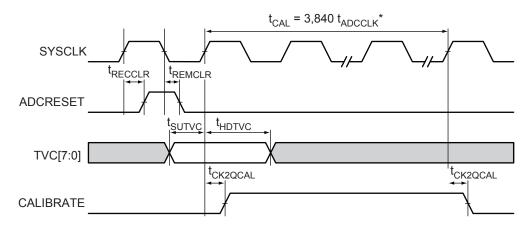

#### **Timing Diagrams**

Note: \*Refer to EQ 15 on page 2-107 for the calculation on the period of ADCCLK, t<sub>ADCCLK</sub>.

Figure 2-89 • Power-Up Calibration Status Signal Timing Diagram

2-111 Revision 6

#### 2.5 V LVCMOS

Low-Voltage CMOS for 2.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 2.5 V applications.

Table 2-110 • Minimum and Maximum DC Input and Output Levels

| 2.5 V<br>LVCMOS   | v          | IL        | v         | TH .      | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|------------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V  | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| Applicable to     | Pro I/O Ba | nks       | •         | •         | •         | •         |     |    |                         | •                       |                         |                         |

| 4 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10                      | 10                      |

| 8 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10                      | 10                      |

| 12 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 12  | 12 | 74                      | 65                      | 10                      | 10                      |

| 16 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 16  | 16 | 87                      | 83                      | 10                      | 10                      |

| 24 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 24  | 24 | 124                     | 169                     | 10                      | 10                      |

| Applicable to     | Advanced   | I/O Bank  | s         | •         | •         | •         |     |    |                         | •                       |                         |                         |

| 2 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 2   | 2  | 18                      | 16                      | 10                      | 10                      |

| 4 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10                      | 10                      |

| 6 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 6   | 6  | 37                      | 32                      | 10                      | 10                      |

| 8 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10                      | 10                      |

| 12 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 12  | 12 | 74                      | 65                      | 10                      | 10                      |

| 16 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 16  | 16 | 87                      | 83                      | 10                      | 10                      |

| 24 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 24  | 24 | 124                     | 169                     | 10                      | 10                      |

| Applicable to     | Standard   | I/O Banks |           | •         | •         | •         | •   |    |                         | •                       | •                       |                         |

| 2 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 2   | 2  | 18                      | 16                      | 10                      | 10                      |

| 4 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10                      | 10                      |

| 6 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 6   | 6  | 37                      | 32                      | 10                      | 10                      |

| 8 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

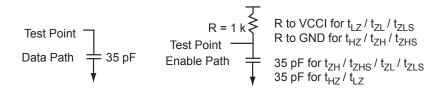

Figure 2-120 • AC Loading

Table 2-111 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 2.5            | 1.2                  | _               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

2-181 Revision 6

#### Input Register

Figure 2-139 • Input Register Timing Diagram

**Timing Characteristics**

Table 2-176 • Input Data Register Propagation Delays

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.24 | 0.27 | 0.32 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.26 | 0.30 | 0.35 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.37 | 0.42 | 0.50 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.32 | 0.37 | 0.43 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### VCC Core Supply Voltage

Supply voltage to the FPGA core, nominally 1.5 V. VCC is also required for powering the JTAG state machine, in addition to VJTAG. Even when a Fusion device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the Fusion device.

#### VCCIBx I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are either four (AFS090 and AFS250) or five (AFS600 and AFS1500) I/O banks on the Fusion devices plus a dedicated VJTAG bank.

Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCI pins tied to GND.

#### VCCPLA/B PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V, where A and B refer to the PLL. AFS090 and AFS250 each have a single PLL. The AFS600 and AFS1500 devices each have two PLLs. Microsemi recommends tying VCCPLX to VCC and using proper filtering circuits to decouple VCC noise from PLL. If unused, VCCPLA/B should be tied to GND.

#### VCOMPLA/B Ground for West and East PLL

VCOMPLA is the ground of the west PLL (CCC location F) and VCOMPLB is the ground of the east PLL (CCC location C).

#### VJTAG JTAG Supply Voltage

Fusion devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a Fusion device is in a JTAG chain of interconnected boards and it is desired to power down the board containing the Fusion device, this may be done provided both VJTAG and VCC to the Fusion part remain powered; otherwise, JTAG signals will not be able to transition the Fusion device, even in bypass mode.

#### VPUMP Programming Supply Voltage

Fusion devices support single-voltage ISP programming of the configuration flash and FlashROM. For programming, VPUMP should be in the 3.3 V +/-5% range. During normal device operation, VPUMP can be left floating or can be tied to any voltage between 0 V and 3.6 V.

When the VPUMP pin is tied to ground, it shuts off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

Table 3-1 • Absolute Maximum Ratings (continued)

| Symbol                        | Parameter                                       | Commercial    | Industrial    | Units |

|-------------------------------|-------------------------------------------------|---------------|---------------|-------|

| AV, AC                        | Unpowered, ADC reset asserted or unconfigured   | -11.0 to 12.6 | -11.0 to 12.0 | V     |

|                               | Analog input (+16 V to +2 V prescaler range)    | -0.4 to 12.6  | -0.4 to 12.0  | V     |

|                               | Analog input (+1 V to +0.125 V prescaler range) | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Analog input (–16 V to –2 V prescaler range)    | -11.0 to 0.4  | -11.0 to 0.4  | V     |

|                               | Analog input (-1 V to -0.125 V prescaler range) | -3.75 to 0.4  | -3.75 to 0.4  | V     |

|                               | Analog input (direct input to ADC)              | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Digital input                                   | –0.4 to 12.6  | -0.4 to 12.0  | V     |

| AG                            | Unpowered, ADC reset asserted or unconfigured   | -11.0 to 12.6 | -11.0 to 12.0 | V     |

|                               | Low Current Mode (1 μA, 3 μA, 10 μA, 30 μA)     | –0.4 to 12.6  | -0.4 to 12.0  | V     |

|                               | Low Current Mode (–1 μA, –3 μA, –10 μA, –30 μA) | -11.0 to 0.4  | -11.0 to 0.4  | V     |

|                               | High Current Mode <sup>3</sup>                  | -11.0 to 12.6 | -11.0 to 12.0 | V     |

| AT                            | Unpowered, ADC reset asserted or unconfigured   | -0.4 to 16.0  | -0.4 to 15.0  | V     |

|                               | Analog input (+16 V, 4 V prescaler range)       | –0.4 to 16.0  | -0.4 to 15.0  | V     |

|                               | Analog input (direct input to ADC)              | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Digital input                                   | -0.4 to 16.0  | -0.4 to 15.0  | V     |

| T <sub>STG</sub> <sup>4</sup> | Storage temperature                             | <b>–</b> 65 t | to +150       | °C    |

| T <sub>J</sub> <sup>4</sup>   | Junction temperature                            | +             | 125           | °C    |

#### Notes:

- 1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-4.

- 2. Analog data not valid beyond 3.65 V.

- 3. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

- 4. For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.

#### Methodology

#### Total Power Consumption—P<sub>TOTAL</sub>

#### Operating Mode, Standby Mode, and Sleep Mode

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—P<sub>STAT</sub>

#### **Operating Mode**

$P_{STAT}$  = PDC1 + ( $N_{NVM-BLOCKS}$  \* PDC4) + PDC5+ ( $N_{QUADS}$  \* PDC6) + ( $N_{INPUTS}$  \* PDC7) + ( $N_{OUTPUTS}$  \* PDC8) + ( $N_{PLLS}$  \* PDC9)

$\ensuremath{N_{\text{NVM-BLOCKS}}}$  is the number of NVM blocks available in the device.

N<sub>QUADS</sub> is the number of Analog Quads used in the design.

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$N_{\mbox{\scriptsize OUTPUTS}}$  is the number of I/O output buffers used in the design.

N<sub>PLLS</sub> is the number of PLLs available in the device.

#### Standby Mode

$P_{STAT} = PDC2$

#### Sleep Mode

$P_{STAT} = PDC3$

#### Total Dynamic Power Consumption—PDYN

#### **Operating Mode**

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub> + P<sub>NVM</sub>+ P<sub>XTL-OSC</sub> + P<sub>RC-OSC</sub> + P<sub>AB</sub>

#### Standby Mode

$P_{DYN} = P_{XTL-OSC}$

#### Sleep Mode

$P_{DYN} = 0 W$

#### Global Clock Dynamic Contribution—P<sub>CLOCK</sub>

#### **Operating Mode**

P<sub>CLOCK</sub> = (PAC1 + N<sub>SPINE</sub> \* PAC2 + N<sub>ROW</sub> \* PAC3 + N<sub>S-CELL</sub> \* PAC4) \* F<sub>CLK</sub>

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *Fusion and Extended Temperature Fusion FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *Fusion and Extended Temperature Fusion FPGA Fabric User's Guide*.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CFLL</sub> is the number of VersaTiles used as sequential modules in the design.

#### Standby Mode and Sleep Mode

P<sub>CLOCK</sub> = 0 W

#### Sequential Cells Dynamic Contribution—P<sub>S-CELL</sub>

#### **Operating Mode**

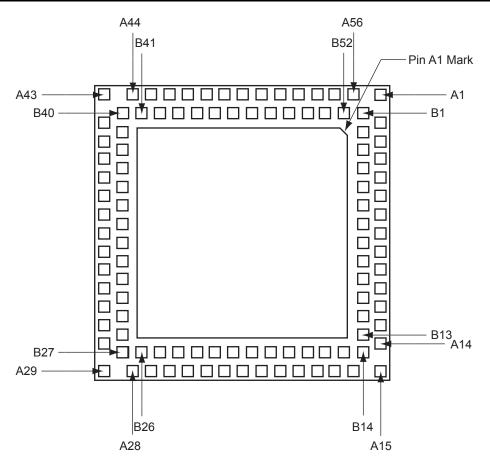

# 4 – Package Pin Assignments

## **QN108**

Note: The die attach paddle center of the package is tied to ground (GND).

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

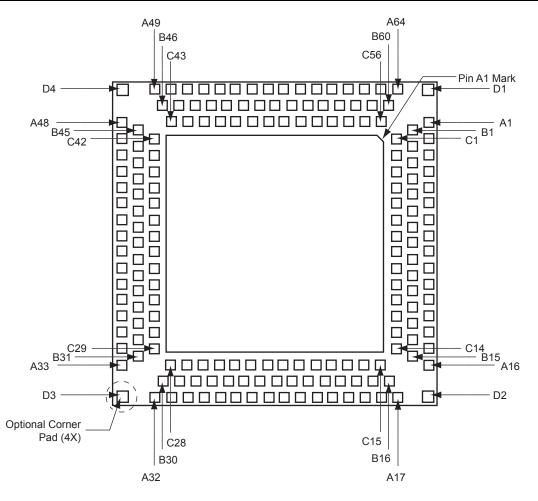

## **QN180**

Note: The die attach paddle center of the package is tied to ground (GND).

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

4-3 Revision 6

| FG484         |                 |                  |

|---------------|-----------------|------------------|

| Pin<br>Number | AFS600 Function | AFS1500 Function |

| V3            | VCCIB4          | VCCIB4           |

| V4            | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  |

| V5            | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  |

| V6            | GND             | GND              |

| V7            | VCC33PMP        | VCC33PMP         |

| V8            | NC              | NC               |

| V9            | VCC33A          | VCC33A           |

| V10           | AG4             | AG4              |

| V11           | AT4             | AT4              |

| V12           | ATRTN2          | ATRTN2           |

| V13           | AT5             | AT5              |

| V14           | VCC33A          | VCC33A           |

| V15           | NC              | NC               |

| V16           | VCC33A          | VCC33A           |

| V17           | GND             | GND              |

| V18           | TMS             | TMS              |

| V19           | VJTAG           | VJTAG            |

| V20           | VCCIB2          | VCCIB2           |

| V21           | TRST            | TRST             |

| V22           | TDO             | TDO              |

| W1            | NC              | IO93PDB4V0       |

| W2            | GND             | GND              |

| W3            | NC              | IO93NDB4V0       |

| W4            | GEB2/IO59PDB4V0 | GEB2/IO86PDB4V0  |

| W5            | IO59NDB4V0      | IO86NDB4V0       |

| W6            | AV0             | AV0              |

| W7            | GNDA            | GNDA             |

| W8            | AV1             | AV1              |

| W9            | AV2             | AV2              |

| W10           | GNDA            | GNDA             |

| W11           | AV3             | AV3              |

| W12           | AV6             | AV6              |

| W13           | GNDA            | GNDA             |

| W14           | AV7             | AV7              |

| W15           | AV8             | AV8              |

| FG484         |                 |                  |

|---------------|-----------------|------------------|

| Pin<br>Number | AFS600 Function | AFS1500 Function |

| W16           | GNDA            | GNDA             |

| W17           | AV9             | AV9              |

| W18           | VCCIB2          | VCCIB2           |

| W19           | NC              | IO68PPB2V0       |

| W20           | TCK             | TCK              |

| W21           | GND             | GND              |

| W22           | NC              | IO76PPB2V0       |

| Y1            | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |

| Y2            | IO60NDB4V0      | IO87NDB4V0       |

| Y3            | GEA2/IO58PDB4V0 | GEA2/IO85PDB4V0  |

| Y4            | IO58NDB4V0      | IO85NDB4V0       |

| Y5            | NCAP            | NCAP             |

| Y6            | AC0             | AC0              |

| Y7            | VCC33A          | VCC33A           |

| Y8            | AC1             | AC1              |

| Y9            | AC2             | AC2              |

| Y10           | VCC33A          | VCC33A           |

| Y11           | AC3             | AC3              |

| Y12           | AC6             | AC6              |

| Y13           | VCC33A          | VCC33A           |

| Y14           | AC7             | AC7              |

| Y15           | AC8             | AC8              |

| Y16           | VCC33A          | VCC33A           |

| Y17           | AC9             | AC9              |

| Y18           | ADCGNDREF       | ADCGNDREF        |

| Y19           | PTBASE          | PTBASE           |

| Y20           | GNDNVM          | GNDNVM           |

| Y21           | VCCNVM          | VCCNVM           |

| Y22           | VPUMP           | VPUMP            |

4-26 Revision 6