Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | 27648                                                         |

| Number of I/O                  | 37                                                            |

| Number of Gates                | 90000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 108-WFQFN                                                     |

| Supplier Device Package        | 108-QFN (8x8)                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs090-qng108i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Clock Conditioning Circuits**

In Fusion devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations.

The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides.

Each CCC can implement up to three independent global buffers (with or without programmable delay), or a PLL function (programmable frequency division/multiplication, phase shift, and delays) with up to three global outputs. Unused global outputs of a PLL can be used to implement independent global buffers, up to a maximum of three global outputs for a given CCC.

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, and CLKC-GLC) of a given CCC.

A PLL macro uses the CLKA CCC input to drive its reference clock. It uses the GLA and, optionally, the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global output cannot be reused if the YB (or YC) output is used (Figure 2-19). Refer to the "PLL Macro" section on page 2-27 for more information.

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

- · The FPGA core

The CCC block is fully configurable, either via flash configuration bits set in the programming bitstream or through an asynchronous interface. This asynchronous interface is dynamically accessible from inside the Fusion device to permit changes of parameters (such as divide ratios) during device operation. To increase the versatility and flexibility of the clock conditioning system, the CCC configuration is determined either by the user during the design process, with configuration data being stored in flash memory as part of the device programming procedure, or by writing data into a dedicated shift register during normal device operation. This latter mode allows the user to dynamically reconfigure the CCC without the need for core programming. The shift register is accessed through a simple serial interface. Refer to the "UJTAG Applications in Microsemi's Low-Power Flash Devices" chapter of the *Fusion FPGA Fabric User Guide* and the "CCC and PLL Characteristics" section on page 2-28 for more information.

Table 2-19 • Flash Memory Block Pin Names (continued)

| Interface Name | Width | Direction | Description                                                                                                                                |

|----------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS[1:0]    | 2     | Out       | Status of the last operation completed:                                                                                                    |

|                |       |           | 00: Successful completion                                                                                                                  |

|                |       |           | 01: Read-/Unprotect-Page: single error detected and corrected                                                                              |

|                |       |           | Write: operation addressed a write-protected page Erase-Page: protection violation Program: Page Buffer is unmodified Protection violation |

|                |       |           | 10: Read-/Unprotect-Page: two or more errors detected                                                                                      |

|                |       |           | 11: Write: attempt to write to another page before programming current page                                                                |

|                |       |           | Erase-Page/Program: page write count has exceeded the 10-year retention threshold                                                          |

| UNPROTECTPAGE  | 1     | In        | When asserted, the page addressed is copied into the Page Buffer and the Page Buffer is made writable.                                     |

| WD[31:0]       | 32    | In        | Write data                                                                                                                                 |

| WEN            | 1     | In        | When asserted, stores WD in the page buffer.                                                                                               |

All flash memory block input signals are active high, except for RESET.

2-41 Revision 6

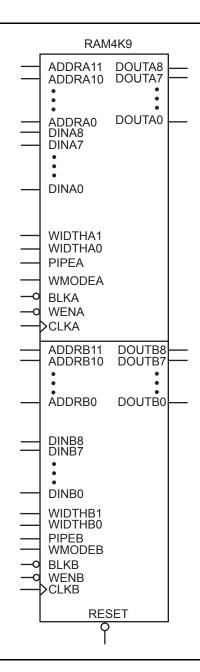

# **RAM4K9 Description**

Figure 2-48 • RAM4K9

2-57 Revision 6

# **Analog Block**

With the Fusion family, Microsemi has introduced the world's first mixed-mode FPGA solution. Supporting a robust analog peripheral mix, Fusion devices will support a wide variety of applications. It is this Analog Block that separates Fusion from all other FPGA solutions on the market today.

By combining both flash and high-speed CMOS processes in a single chip, these devices offer the best of both worlds. The high-performance CMOS is used for building RAM resources. These high-performance structures support device operation up to 350 MHz. Additionally, the advanced Microsemi 0.13 µm flash process incorporates high-voltage transistors and a high-isolation, triple-well process. Both of these are suited for the flash-based programmable logic and nonvolatile memory structures.

High-voltage transistors support the integration of analog technology in several ways. They aid in noise immunity so that the analog portions of the chip can be better isolated from the digital portions, increasing analog accuracy. Because they support high voltages, Microsemi flash FPGAs can be connected directly to high-voltage input signals, eliminating the need for external resistor divider networks, reducing component count, and increasing accuracy. By supporting higher internal voltages, the Microsemi advanced flash process enables high dynamic range on analog circuitry, increasing precision and signal—noise ratio. Microsemi flash FPGAs also drive high-voltage outputs, eliminating the need for external level shifters and drivers.

The unique triple-well process enables the integration of high-performance analog features with increased noise immunity and better isolation. By increasing the efficiency of analog design, the triple-well process also enables a smaller overall design size, reducing die size and cost.

The Analog Block consists of the Analog Quad I/O structure, RTC (for details refer to the "Real-Time Counter System" section on page 2-31), ADC, and ACM. All of these elements are combined in the single Analog Block macro, with which the user implements this functionality (Figure 2-64).

The Analog Block needs to be reset/reinitialized after the core powers up or the device is programmed. An external reset/initialize signal, which can come from the internal voltage regulator when it powers up, must be applied.

Table 2-36 • Analog Block Pin Description (continued)

| Signal Name     | Number of Bits | Direction | Function                                                  | Location of<br>Details |

|-----------------|----------------|-----------|-----------------------------------------------------------|------------------------|

| AG6             | 1              | Output    |                                                           | Analog Quad            |

| AT6             | 1              | Input     |                                                           | Analog Quad            |

| ATRETURN67      | 1              | Input     | Temperature monitor return shared by Analog Quads 6 and 7 | Analog Quad            |

| AV7             | 1              | Input     | Analog Quad 7                                             | Analog Quad            |

| AC7             | 1              | Input     |                                                           | Analog Quad            |

| AG7             | 1              | Output    |                                                           | Analog Quad            |

| AT7             | 1              | Input     |                                                           | Analog Quad            |

| AV8             | 1              | Input     | Analog Quad 8                                             | Analog Quad            |

| AC8             | 1              | Input     |                                                           | Analog Quad            |

| AG8             | 1              | Output    |                                                           | Analog Quad            |

| AT8             | 1              | Input     |                                                           | Analog Quad            |

| ATRETURN89      | 1              | Input     | Temperature monitor return shared by Analog Quads 8 and 9 | Analog Quad            |

| AV9             | 1              | Input     | Analog Quad 9                                             | Analog Quad            |

| AC9             | 1              | Input     |                                                           | Analog Quad            |

| AG9             | 1              | Output    |                                                           | Analog Quad            |

| AT9             | 1              | Input     |                                                           | Analog Quad            |

| RTCMATCH        | 1              | Output    | MATCH                                                     | RTC                    |

| RTCPSMMATCH     | 1              | Output    | MATCH connected to VRPSM                                  | RTC                    |

| RTCXTLMODE[1:0] | 2              | Output    | Drives XTLOSC RTCMODE[1:0] pins                           | RTC                    |

| RTCXTLSEL       | 1              | Output    | Drives XTLOSC MODESEL pin                                 | RTC                    |

| RTCCLK          | 1              | Input     | RTC clock input                                           | RTC                    |

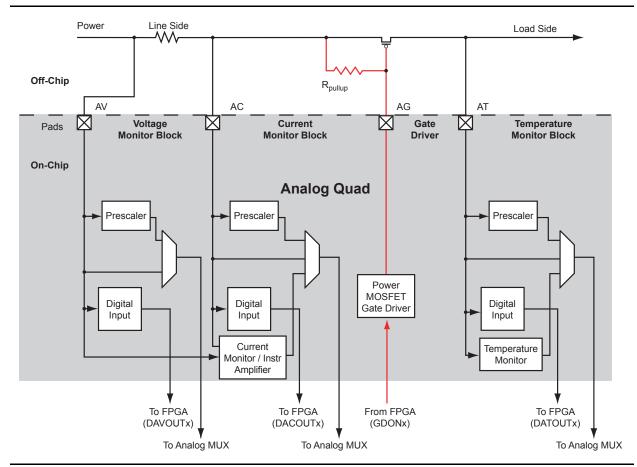

# **Analog Quad**

With the Fusion family, Microsemi introduces the Analog Quad, shown in Figure 2-65 on page 2-81, as the basic analog I/O structure. The Analog Quad is a four-channel system used to precondition a set of analog signals before sending it to the ADC for conversion into a digital signal. To maximize the usefulness of the Analog Quad, the analog input signals can also be configured as LVTTL digital input signals. The Analog Quad is divided into four sections.

The first section is called the Voltage Monitor Block, and its input pin is named AV. It contains a two-channel analog multiplexer that allows an incoming analog signal to be routed directly to the ADC or allows the signal to be routed to a prescaler circuit before being sent to the ADC. The prescaler can be configured to accept analog signals between –12 V and 0 or between 0 and +12 V. The prescaler circuit scales the voltage applied to the ADC input pad such that it is compatible with the ADC input voltage range. The AV pin can also be used as a digital input pin.

The second section of the Analog Quad is called the Current Monitor Block. Its input pin is named AC. The Current Monitor Block contains all the same functions as the Voltage Monitor Block with one addition, which is a current monitoring function. A small external current sensing resistor (typically less than 1  $\Omega$ ) is connected between the AV and AC pins and is in series with a power source. The Current Monitor Block contains a current monitor circuit that converts the current through the external resistor to a voltage that can then be read using the ADC.

### Gate Driver

The Fusion Analog Quad includes a Gate Driver connected to the Quad's AG pin (Figure 2-74). Designed to work with external p- or n-channel MOSFETs, the Gate driver is a configurable current sink or source and requires an external pull-up or pull-down resistor. The AG supports 4 selectable gate drive levels: 1  $\mu$ A, 3  $\mu$ A, 10  $\mu$ A, and 30  $\mu$ A (Figure 2-75 on page 2-91). The AG also supports a High Current Drive mode in which it can sink 20 mA; in this mode the switching rate is approximately 1.3 MHz with 100 ns turn-on time and 600 ns turn-off time. Modeled on an open-drain-style output, it does not output a voltage level without an appropriate pull-up or pull-down resistor. If 1 V is forced on the drain, the current sinking/sourcing will exceed the ability of the transistor, and the device could be damaged.

The AG pad is turned on via the corresponding GDONx pin in the Analog Block macro, where x is the number of the corresponding Analog Quad for the AG pad to be enabled (GDON0 to GDON9).

Figure 2-74 • Gate Driver

The gate-to-source voltage ( $V_{gs}$ ) of the external MOSFET is limited to the programmable drive current times the external pull-up or pull-down resistor value (EQ 5).

$$V_{as} \le I_a \times (R_{pullup} \text{ or } R_{pulldown})$$

EQ 5

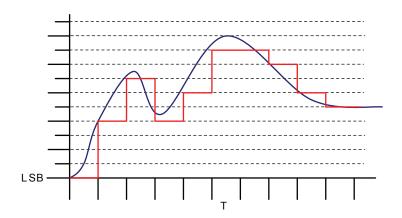

This process results in a binary approximation of VIN. Generally, there is a fixed interval T, the sampling period, between the samples. The inverse of the sampling period is often referred to as the sampling frequency  $f_S = 1 / T$ . The combined effect is illustrated in Figure 2-82.

Figure 2-82 • Conversion Example

Figure 2-82 demonstrates that if the signal changes faster than the sampling rate can accommodate, or if the actual value of VIN falls between counts in the result, this information is lost during the conversion. There are several techniques that can be used to address these issues.

First, the sampling rate must be chosen to provide enough samples to adequately represent the input signal. Based on the Nyquist-Shannon Sampling Theorem, the minimum sampling rate must be at least twice the frequency of the highest frequency component in the target signal (Nyquist Frequency). For example, to recreate the frequency content of an audio signal with up to 22 KHz bandwidth, the user must sample it at a minimum of 44 ksps. However, as shown in Figure 2-82, significant post-processing of the data is required to interpolate the value of the waveform during the time between each sample.

Similarly, to re-create the amplitude variation of a signal, the signal must be sampled with adequate resolution. Continuing with the audio example, the dynamic range of the human ear (the ratio of the amplitude of the threshold of hearing to the threshold of pain) is generally accepted to be 135 dB, and the dynamic range of a typical symphony orchestra performance is around 85 dB. Most commercial recording media provide about 96 dB of dynamic range using 16-bit sample resolution. But 16-bit fidelity does not necessarily mean that you need a 16-bit ADC. As long as the input is sampled at or above the Nyquist Frequency, post-processing techniques can be used to interpolate intermediate values and reconstruct the original input signal to within desired tolerances.

If sophisticated digital signal processing (DSP) capabilities are available, the best results are obtained by implementing a reconstruction filter, which is used to interpolate many intermediate values with higher resolution than the original data. Interpolating many intermediate values increases the effective number of samples, and higher resolution increases the effective number of bits in the sample. In many cases, however, it is not cost-effective or necessary to implement such a sophisticated reconstruction algorithm. For applications that do not require extremely fine reproduction of the input signal, alternative methods can enhance digital sampling results with relatively simple post-processing. The details of such techniques are out of the scope of this chapter; refer to the *Improving ADC Results through Oversampling and Post-Processing of Data* white paper for more information.

2-99 Revision 6

### Intra-Conversion

Performing a conversion during power-up calibration is possible but should be avoided, since the performance is not guaranteed, as shown in Table 2-49 on page 2-117. This is described as intra-conversion. Figure 2-92 on page 2-113 shows intra-conversion, (conversion that starts during power-up calibration).

### Injected Conversion

A conversion can be interrupted by another conversion. Before the current conversion is finished, a second conversion can be started by issuing a pulse on signal ADCSTART. When a second conversion is issued before the current conversion is completed, the current conversion would be dropped and the ADC would start the second conversion on the rising edge of the SYSCLK. This is known as injected conversion. Since the ADC is synchronous, the minimum time to issue a second conversion is two clock cycles of SYSCLK after the previous one. Figure 2-93 on page 2-113 shows injected conversion, (conversion that starts before a previously started conversion is finished). The total time for calibration still remains 3,840 ADCCLK cycles.

# ADC Example

This example shows how to choose the correct settings to achieve the fastest sample time in 10-bit mode for a system that runs at 66 MHz. Assume the acquisition times defined in Table 2-44 on page 2-108 for 10-bit mode, which gives  $0.549 \mu s$  as a minimum hold time.

The period of SYSCLK:  $t_{SYSCLK}$  = 1/66 MHz = 0.015  $\mu s$

Choosing TVC between 1 and 33 will meet the maximum and minimum period for the ADCCLK requirement. A higher TVC leads to a higher ADCCLK period.

The minimum TVC is chosen so that  $t_{distrib}$  and  $t_{post-cal}$  can be run faster. The period of ADCCLK with a TVC of 1 can be computed by EQ 24.

$$t_{ADCCLK} = 4 \times (1 + TVC) \times t_{SYSCLK} = 4 \times (1 + 1) \times 0.015 \ \mu s = 0.12 \ \mu s$$

EQ 24

The STC value can now be computed by using the minimum sample/hold time from Table 2-44 on page 2-108, as shown in EQ 25.

STC =

$$\frac{t_{\text{sample}}}{t_{\Delta DCCLK}} - 2 = \frac{0.549 \,\mu\text{s}}{0.12 \,\mu\text{s}} - 2 = 4.575 - 2 = 2.575$$

EQ 25

You must round up to 3 to accommodate the minimum sample time requirement. The actual sample time,  $t_{\text{sample}}$ , with an STC of 3, is now equal to 0.6  $\mu$ s, as shown in EQ 26

$$t_{\text{sample}} = (2 + \text{STC}) \times t_{\text{ADCCLK}} = (2 + 3) \times t_{\text{ADCCLK}} = 5 \times 0.12 \ \mu \text{s} = 0.6 \ \mu \text{s}$$

EQ 26

Microsemi recommends post-calibration for temperature drift over time, so post-calibration is enabled.

The post-calibration time,  $t_{\text{post-cal}}$ , can be computed by EQ 27. The post-calibration time is 0.24  $\mu s$ .

$$t_{post-cal} = 2 \times t_{ADCCLK} = 0.24 \mu s$$

EQ 27

The distribution time,  $t_{distrib}$ , is equal to 1.2  $\mu$ s and can be computed as shown in EQ 28 (N is number of bits, referring back to EQ 8 on page 2-94).

$$t_{distrib} = N \times t_{ADCCLK} = 10 \times 0.12 = 1.2 \mu s$$

EQ 28

The total conversion time can now be summated, as shown in EQ 29 (referring to EQ 23 on page 2-109).

$$t_{sync}$$

read +  $t_{sample}$  +  $t_{distrib}$  +  $t_{post-cal}$  +  $t_{sync}$  write = (0.015 + 0.60 + 1.2 + 0.24 + 0.015)  $\mu s$  = 2.07  $\mu s$

EQ 29

# Temperature Reading Noise RMS vs. Averaging 12 10 8 6 4 2 10 10 100 1000 10000 Number of Averages

Figure 2-96 • Temperature Reading Noise When Averaging is Used

# **Electrostatic Discharge (ESD) Protection**

Fusion devices are tested per JEDEC Standard JESD22-A114-B.

Fusion devices contain clamp diodes at every I/O, global, and power pad. Clamp diodes protect all device pads against damage from ESD as well as from excessive voltage transients.

Each I/O has two clamp diodes. One diode has its positive (P) side connected to the pad and its negative (N) side connected to VCCI. The second diode has its P side connected to GND and its N side connected to the pad. During operation, these diodes are normally biased in the Off state, except when transient voltage is significantly above VCCI or below GND levels.

By selecting the appropriate I/O configuration, the diode is turned on or off. Refer to Table 2-75 and Table 2-76 on page 2-143 for more information about I/O standards and the clamp diode.

The second diode is always connected to the pad, regardless of the I/O configuration selected.

Table 2-75 • Fusion Standard and Advanced I/O - Hot-Swap and 5 V Input Tolerance Capabilities

|                                                             | Clamp           | Diode        | Hot In          | sertion      | 5 V Input 1      | Folerance <sup>1</sup> | Innut            | Output   |

|-------------------------------------------------------------|-----------------|--------------|-----------------|--------------|------------------|------------------------|------------------|----------|

| I/O Assignment                                              | Standard<br>I/O | Advanced I/O | Standard<br>I/O | Advanced I/O | Standard<br>I/O  | Advanced I/O           | Input<br>Buffer  | Buffer   |

| 3.3 V LVTTL/LVCMOS                                          | No              | Yes          | Yes             | No           | Yes <sup>1</sup> | Yes <sup>1</sup>       | Enabled/Disabled |          |

| 3.3 V PCI, 3.3 V PCI-X                                      | N/A             | Yes          | N/A             | No           | N/A              | Yes <sup>1</sup>       | Enabled/Disabled |          |

| LVCMOS 2.5 V                                                | No              | Yes          | Yes             | No           | No               | No                     | Enabled/Disabled |          |

| LVCMOS 2.5 V / 5.0 V                                        | N/A             | Yes          | N/A             | No           | N/A              | Yes <sup>2</sup>       | Enabled/I        | Disabled |

| LVCMOS 1.8 V                                                | No              | Yes          | Yes             | No           | No               | No                     | Enabled/I        | Disabled |

| LVCMOS 1.5 V                                                | No              | Yes          | Yes             | No           | No               | No                     | Enabled/I        | Disabled |

| Differential,<br>LVDS/BLVDS/M-<br>LVDS/ LVPECL <sup>3</sup> | N/A             | Yes          | N/A             | No           | N/A              | No                     | Enabled/l        | Disabled |

### Notes:

- 1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

- 2. Can be implemented with an external resistor and an internal clamp diode.

- 3. Bidirectional LVPECL buffers are not supported. I/Os can be configured as either input buffers or output buffers.

Table 2-76 • Fusion Pro I/O - Hot-Swap and 5 V Input Tolerance Capabilities

| I/O Assignment                                      | Clamp<br>Diode | Hot<br>Insertion | 5 V Input<br>Tolerance | Input Buffer     | Output Buffer |  |

|-----------------------------------------------------|----------------|------------------|------------------------|------------------|---------------|--|

| 3.3 V LVTTL/LVCMOS                                  | No             | Yes              | Yes <sup>1</sup>       | Enabled/Disabled |               |  |

| 3.3 V PCI, 3.3 V PCI-X                              | Yes            | No               | Yes <sup>1</sup>       | Enabled/Disabled |               |  |

| LVCMOS 2.5 V 3                                      | No             | Yes              | No                     | Enabled/Disabled |               |  |

| LVCMOS 2.5 V / 5.0 V <sup>3</sup>                   | Yes            | No               | Yes <sup>2</sup>       | Enabled          | l/Disabled    |  |

| LVCMOS 1.8 V                                        | No             | Yes              | No                     | Enabled          | l/Disabled    |  |

| LVCMOS 1.5 V                                        | No             | Yes              | No                     | Enabled/Disabled |               |  |

| Voltage-Referenced Input Buffer                     | No             | Yes              | No                     | Enabled          | l/Disabled    |  |

| Differential, LVDS/BLVDS/M-LVDS/LVPECL <sup>4</sup> | No             | Yes              | No                     | Enabled          | l/Disabled    |  |

### Notes:

- 1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

- 2. Can be implemented with an external resistor and an internal clamp diode.

- In the SmartGen, FlashROM, Flash Memory System Builder, and Analog System Builder User Guide, select the LVCMOS5 macro for the LVCMOS 2.5 V / 5.0 V I/O standard or the LVCMOS25 macro for the LVCMOS 2.5 V I/O standard

- 4. Bidirectional LVPECL buffers are not supported. I/Os can be configured as either input buffers or output buffers.

2-143 Revision 6

# **5 V Input Tolerance**

I/Os can support 5 V input tolerance when LVTTL 3.3 V, LVCMOS 3.3 V, LVCMOS 2.5 V / 5 V, and LVCMOS 2.5 V configurations are used (see Table 2-77 on page 2-147 for more details). There are four recommended solutions (see Figure 2-103 to Figure 2-106 on page 2-146 for details of board and macro setups) to achieve 5 V receiver tolerance. All the solutions meet a common requirement of limiting the voltage at the input to 3.6 V or less. In fact, the I/O absolute maximum voltage rating is 3.6 V, and any voltage above 3.6 V may cause long-term gate oxide failures.

### Solution 1

The board-level design needs to ensure that the reflected waveform at the pad does not exceed the limits provided in Table 3-4 on page 3-4. This is a long-term reliability requirement.

This scheme will also work for a 3.3 V PCI / PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the two external resistors, as explained below. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

The following are some examples of possible resistor values (based on a simplified simulation model with no line effects and 10  $\Omega$  transmitter output resistance, where Rtx\_out\_high = (VCCI – VOH) / IOH, Rtx\_out\_low = VOL / IOL).

Example 1 (high speed, high current):

```

Rtx_out_high = Rtx_out_low = 10 \Omega

R1 = 36 \Omega (±5%), P(r1)min = 0.069 \Omega

R2 = 82 \Omega (±5%), P(r2)min = 0.158 \Omega

Imax_tx = 5.5 \text{ V} / (82 * 0.95 + 36 * 0.95 + 10) = 45.04 \text{ mA}

t_{RISE} = t_{FALL} = 0.85 \text{ ns at C_pad_load} = 10 \text{ pF (includes up to 25% safety margin)}

t_{RISE} = t_{FALL} = 4 \text{ ns at C_pad_load} = 50 \text{ pF (includes up to 25% safety margin)}

Example 2 (low-medium speed, medium current):

Rtx_out_high = Rtx_out_low = 10 \Omega

R1 = 220 \Omega (±5%), P(r1)min = 0.018 \Omega

R2 = 390 \Omega (±5%), P(r2)min = 0.032 \Omega

Imax_tx = 5.5 \text{ V} / (220 * 0.95 + 390 * 0.95 + 10) = 9.17 \text{ mA}

t_{RISE} = t_{FALL} = 4 \text{ ns at C_pad_load} = 10 \text{ pF (includes up to 25% safety margin)}

t_{RISE} = t_{FALL} = 20 \text{ ns at C_pad_load} = 50 \text{ pF (includes up to 25% safety margin)}

```

Other values of resistors are also allowed as long as the resistors are sized appropriately to limit the voltage at the receiving end to 2.5 V < Vin(rx) < 3.6 V when the transmitter sends a logic 1. This range of  $\text{Vin\_dc}(rx)$  must be assured for any combination of transmitter supply (5 V  $\pm$  0.5 V), transmitter output resistance, and board resistor tolerances.

Fusion Family of Mixed Signal FPGAs

Table 2-93 • Summary of I/O Timing Characteristics – Software Default Settings Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, **Worst-Case VCCI = I/O Standard Dependent** Applicable to Advanced I/Os

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | tpour | ф    | toin | t <sub>Р</sub> ү | teour | tzL  | tzн  | tız  | t <sub>HZ</sub> | tzıs | t <sub>Z</sub> HS | Units |

|------------------------------|---------------------|-----------|----------------------|-------------------------|-------|------|------|------------------|-------|------|------|------|-----------------|------|-------------------|-------|

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 12 mA               | High      | 35 pF                | -                       | 0.49  | 2.64 | 0.03 | 0.90             | 0.32  | 2.69 | 2.11 | 2.40 | 2.68            | 4.36 | 3.78              | ns    |

| 2.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | _                       | 0.49  | 2.66 | 0.03 | 0.98             | 0.32  | 2.71 | 2.56 | 2.47 | 2.57            | 4.38 | 4.23              | ns    |

| 1.8 V LVCMOS                 | 12 mA               | High      | 35 pF                | _                       | 0.49  | 2.64 | 0.03 | 0.91             | 0.32  | 2.69 | 2.27 | 2.76 | 3.05            | 4.36 | 3.94              | ns    |

| 1.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | _                       | 0.49  | 3.05 | 0.03 | 1.07             | 0.32  | 3.10 | 2.67 | 2.95 | 3.14            | 4.77 | 4.34              | ns    |

| 3.3 V PCI                    | Per PCI<br>spec     | High      | 10 pF                | 25 <sup>2</sup>         | 0.49  | 2.00 | 0.03 | 0.65             | 0.32  | 2.04 | 1.46 | 2.40 | 2.68            | 3.71 | 3.13              | ns    |

| 3.3 V PCI-X                  | Per PCI-X<br>spec   | High      | 10 pF                | 25 <sup>2</sup>         | 0.49  | 2.00 | 0.03 | 0.62             | 0.32  | 2.04 | 1.46 | 2.40 | 2.68            | 3.71 | 3.13              | ns    |

| LVDS                         | 24 mA               | High      | _                    | _                       | 0.49  | 1.37 | 0.03 | 1.20             | N/A   | N/A  | N/A  | N/A  | N/A             | N/A  | N/A               | ns    |

| LVPECL                       | 24 mA               | High      | _                    | -                       | 0.49  | 1.34 | 0.03 | 1.05             | N/A   | N/A  | N/A  | N/A  | N/A             | N/A  | N/A               | ns    |

### Notes:

- 1. For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

- 2. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-123 on page 2-197 for connectivity. This resistor is not required during normal operation.

Table 2-94 • Summary of I/O Timing Characteristics – Software Default Settings Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, **Worst-Case VCCI = I/O Standard Dependent** Applicable to Standard I/Os

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t bour | top  | t <sub>DIN</sub> | tpy  | teour | tzt  | нг   | tLZ  | tнz  | Units |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|------|------------------|------|-------|------|------|------|------|-------|

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 8 mA                | High      | 35 pF                | _                       | 0.49   | 3.29 | 0.03             | 0.75 | 0.32  | 3.36 | 2.80 | 1.79 | 2.01 | ns    |

| 2.5 V LVCMOS                 | 8 mA                | High      | 35pF                 | -                       | 0.49   | 3.56 | 0.03             | 0.96 | 0.32  | 3.40 | 3.56 | 1.78 | 1.91 | ns    |

| 1.8 V LVCMOS                 | 4 mA                | High      | 35pF                 | _                       | 0.49   | 4.74 | 0.03             | 0.90 | 0.32  | 4.02 | 4.74 | 1.80 | 1.85 | ns    |

| 1.5 V LVCMOS                 | 2 mA                | High      | 35pF                 | ı                       | 0.49   | 5.71 | 0.03             | 1.06 | 0.32  | 4.71 | 5.71 | 1.83 | 1.83 | ns    |

Note: For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

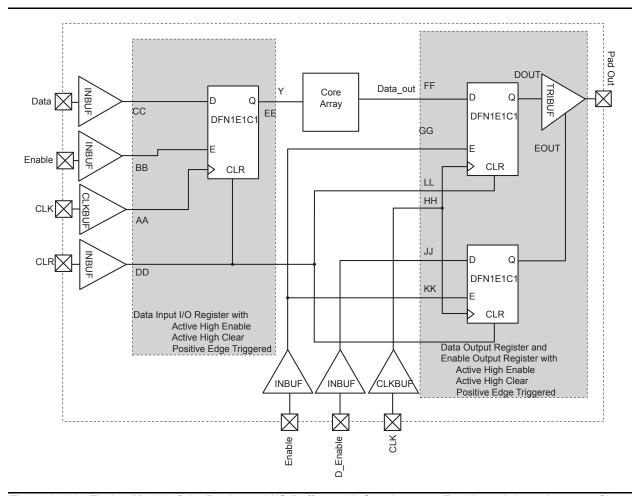

# Fully Registered I/O Buffers with Synchronous Enable and Asynchronous Clear

Figure 2-138 • Timing Model of the Registered I/O Buffers with Synchronous Enable and Asynchronous Clear

# **Pin Descriptions**

# **Supply Pins**

GND Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

GNDQ Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ needs to always be connected on the board to GND. Note: In FG256, FG484, and FG676 packages, GNDQ and GND pins are connected within the package and are labeled as GND pins in the respective package pin assignment tables.

ADCGNDREF Analog Reference Ground

Analog ground reference used by the ADC. This pad should be connected to a quiet analog ground.

GNDA Ground (analog)

Quiet ground supply voltage to the Analog Block of Fusion devices. The use of a separate analog ground helps isolate the analog functionality of the Fusion device from any digital switching noise. A 0.2 V maximum differential voltage between GND and GNDA/GNDQ should apply to system implementation.

GNDAQ Ground (analog quiet)

Quiet ground supply voltage to the analog I/O of Fusion devices. The use of a separate analog ground helps isolate the analog functionality of the Fusion device from any digital switching noise. A 0.2 V maximum differential voltage between GND and GNDA/GNDQ should apply to system implementation. Note: In FG256, FG484, and FG676 packages, GNDAQ and GNDA pins are connected within the package and are labeled as GNDA pins in the respective package pin assignment tables.

GNDNVM Flash Memory Ground

Ground supply used by the Fusion device's flash memory block module(s).

GNDOSC Oscillator Ground

Ground supply for both integrated RC oscillator and crystal oscillator circuit.

VCC15A Analog Power Supply (1.5 V)

1.5 V clean analog power supply input for use by the 1.5 V portion of the analog circuitry.

VCC33A Analog Power Supply (3.3 V)

3.3 V clean analog power supply input for use by the 3.3 V portion of the analog circuitry.

VCC33N Negative 3.3 V Output

This is the -3.3 V output from the voltage converter. A 2.2  $\mu$ F capacitor must be connected from this pin to ground.

VCC33PMP Analog Power Supply (3.3 V)

3.3 V clean analog power supply input for use by the analog charge pump. To avoid high current draw, VCC33PMP should be powered up simultaneously with or after VCC33A.

VCCNVM Flash Memory Block Power Supply (1.5 V)

1.5 V power supply input used by the Fusion device's flash memory block module(s). To avoid high current draw, VCC should be powered up before or simultaneously with VCCNVM.

VCCOSC Oscillator Power Supply (3.3 V)

Power supply for both integrated RC oscillator and crystal oscillator circuit. The internal 100 MHz oscillator, powered by the VCCOSC pin, is needed for device programming, operation of the VDDN33 pump, and eNVM operation. VCCOSC is off only when VCCA is off. VCCOSC must be powered whenever the Fusion device needs to function.

2-223 Revision 6

# **Calculating Power Dissipation**

# **Quiescent Supply Current**

Table 3-8 • AFS1500 Quiescent Supply Current Characteristics

| Parameter          | Description             | Conditions                                                          | Temp.                  | Min. | Тур. | Max. | Unit |

|--------------------|-------------------------|---------------------------------------------------------------------|------------------------|------|------|------|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current | Operational standby <sup>4</sup> ,                                  | $T_J = 25^{\circ}C$    |      | 20   | 40   | mA   |

|                    |                         | VCC = 1.575 V                                                       | T <sub>J</sub> = 85°C  |      | 32   | 65   | mA   |

|                    |                         |                                                                     | T <sub>J</sub> = 100°C |      | 59   | 120  | mA   |

|                    |                         | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VCC = 0 V |                        |      | 0    | 0    | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies   | Operational standby <sup>4</sup> ,                                  | $T_J = 25^{\circ}C$    |      | 9.8  | 13   | mA   |

|                    | current                 | VCC33 = 3.63 V                                                      | T <sub>J</sub> = 85°C  |      | 10.7 | 14   | mA   |

|                    |                         |                                                                     | T <sub>J</sub> = 100°C |      | 10.8 | 15   | mA   |

|                    |                         | Operational standby, only Analog                                    | T <sub>J</sub> = 25°C  |      | 0.31 | 2    | mA   |

|                    |                         | Quad and –3.3 V output ON,<br>VCC33 = 3.63 V                        | T <sub>J</sub> = 85°C  |      | 0.35 | 2    | mA   |

|                    |                         |                                                                     | T <sub>J</sub> = 100°C |      | 0.45 | 2    | mA   |

|                    |                         | Standby mode <sup>5</sup> , VCC33 = 3.63 V                          | T <sub>J</sub> = 25°C  |      | 2.9  | 3.6  | mA   |

|                    |                         |                                                                     | T <sub>J</sub> = 85°C  |      | 2.9  | 4    | mA   |

|                    |                         |                                                                     | T <sub>J</sub> = 100°C |      | 3.3  | 6    | mA   |

|                    |                         | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                            | $T_J = 25^{\circ}C$    |      | 17   | 19   | μΑ   |

|                    |                         |                                                                     | T <sub>J</sub> = 85°C  |      | 18   | 20   | μΑ   |

|                    |                         |                                                                     | T <sub>J</sub> = 100°C |      | 24   | 25   | μΑ   |

| ICCI <sup>3</sup>  | I/O quiescent current   | Operational standby <sup>4</sup> ,                                  | T <sub>J</sub> = 25°C  |      | 417  | 649  | μΑ   |

|                    |                         | Standby mode, and Sleep Mode <sup>6</sup> , VCCIx = 3.63 V          | T <sub>J</sub> = 85°C  |      | 417  | 649  | μΑ   |

|                    |                         |                                                                     | T <sub>J</sub> = 100°C |      | 417  | 649  | μΑ   |

### Notes:

- 1. ICC is the 1.5 V power supplies, ICC and ICC15A.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

Table 3-10 • AFS250 Quiescent Supply Current Characteristics

| Parameter          | Description                | Conditions                                                         | Temp.                  | Min | Тур  | Max | Unit |

|--------------------|----------------------------|--------------------------------------------------------------------|------------------------|-----|------|-----|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current    | Operational standby <sup>4</sup> ,                                 | T <sub>J</sub> = 25°C  |     | 4.8  | 10  | mA   |

|                    |                            | VCC = 1.575 V                                                      | T <sub>J</sub> = 85°C  |     | 8.2  | 30  | mA   |

|                    |                            |                                                                    | T <sub>J</sub> = 100°C |     | 15   | 50  | mA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> , VCC = 0 V   |                        |     | 0    | 0   | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies      | Operational standby <sup>4</sup> ,                                 | T <sub>J</sub> = 25°C  |     | 9.8  | 13  | mA   |

|                    | current                    | VCC33 = 3.63 V                                                     | T <sub>J</sub> = 85°C  |     | 9.8  | 14  | mA   |

|                    |                            |                                                                    | T <sub>J</sub> = 100°C |     | 10.8 | 15  | mA   |

|                    |                            | Operational standby, only                                          | $T_J = 25^{\circ}C$    |     | 0.29 | 2   | mA   |

|                    |                            | Analog Quad and –3.3 V<br>output ON, VCC33 = 3.63 V                | $T_J = 85^{\circ}C$    |     | 0.31 | 2   | mA   |

|                    |                            |                                                                    | T <sub>J</sub> = 100°C |     | 0.45 | 2   | mA   |

|                    |                            | Standby mode <sup>5</sup> , VCC33 = 3.63V                          | $T_J = 25^{\circ}C$    |     | 2.9  | 3.0 | mA   |

|                    |                            |                                                                    | T <sub>J</sub> = 85°C  |     | 2.9  | 3.1 | mA   |

|                    |                            |                                                                    | T <sub>J</sub> = 100°C |     | 3.5  | 6   | mA   |

|                    |                            | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                           | $T_J = 25^{\circ}C$    |     | 19   | 18  | μΑ   |

|                    |                            |                                                                    | $T_J = 85^{\circ}C$    |     | 19   | 20  | μΑ   |

|                    |                            |                                                                    | T <sub>J</sub> = 100°C |     | 24   | 25  | μΑ   |

| ICCI <sup>3</sup>  | I/O quiescent current      | Operational standby <sup>6</sup> ,                                 | $T_J = 25^{\circ}C$    |     | 266  | 437 | μΑ   |

|                    |                            | VCCIx = 3.63 V                                                     | T <sub>J</sub> = 85°C  |     | 266  | 437 | μΑ   |

|                    |                            |                                                                    | T <sub>J</sub> = 100°C |     | 266  | 437 | μA   |

| IJTAG              | JTAG I/O quiescent current | Operational standby <sup>4</sup> ,                                 | T <sub>J</sub> = 25°C  |     | 80   | 100 | μA   |

|                    |                            | VJTAG = 3.63 V                                                     | T <sub>J</sub> = 85°C  |     | 80   | 100 | μA   |

|                    |                            |                                                                    | T <sub>J</sub> = 100°C |     | 80   | 100 | μΑ   |

|                    |                            | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> , VJTAG = 0 V |                        |     | 0    | 0   | μA   |

# Notes:

- 1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, and ICCI2.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTA G = VPUMP = 0 V.

Table 3-10 • AFS250 Quiescent Supply Current Characteristics (continued)

| Parameter | Description                 | Conditions                                                            | Temp.                  | Min | Тур | Max | Unit |

|-----------|-----------------------------|-----------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| IPP       | Programming supply          | Non-programming mode,                                                 | T <sub>J</sub> = 25°C  |     | 37  | 80  | μΑ   |

|           | current                     | VPUMP = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 37  | 80  | μΑ   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 80  | 100 | μΑ   |

|           |                             | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VPUMP = 0 V |                        |     | 0   | 0   | μΑ   |

| ICCNVM    | Embedded NVM current        | Reset asserted,                                                       | T <sub>J</sub> = 25°C  |     | 10  | 40  | μΑ   |

|           |                             | VCCNVM = 1.575 V                                                      | T <sub>J</sub> = 85°C  |     | 14  | 40  | μΑ   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 14  | 40  | μΑ   |

| ICCPLL    | 1.5 V PLL quiescent current | Operational standby,                                                  | T <sub>J</sub> = 25°C  |     | 65  | 100 | μΑ   |

|           |                             | VCCPLL = 1.575 V                                                      | T <sub>J</sub> = 85°C  |     | 65  | 100 | μΑ   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 65  | 100 | μΑ   |

### Notes:

- 1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, and ICCI2.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTA G = VPUMP = 0 V.

3-15 Revision 6

# RC Oscillator Dynamic Contribution—P<sub>RC-OSC</sub>

# **Operating Mode**

P<sub>RC-OSC</sub> = PAC19

Standby Mode and Sleep Mode

$P_{RC-OSC} = 0 W$

# Analog System Dynamic Contribution—PAR

### **Operating Mode**

$P_{AB} = PAC20$

Standby Mode and Sleep Mode

$P_{AB} = 0 W$

# Guidelines

### **Toggle Rate Definition**

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that the net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100%, as all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ..

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + ... 0.78125%) / 8.

### **Enable Rate Definition**

Output enable rate is the average percentage of time during which tristate outputs are enabled. When non-tristate output buffers are used, the enable rate should be 100%.

Table 3-16 • Toggle Rate Guidelines Recommended for Power Calculation

| Component  | Definition             | Guideline |

|------------|------------------------|-----------|

| $\alpha_1$ | 10%                    |           |

| $\alpha_2$ | I/O buffer toggle rate | 10%       |

### Table 3-17 • Enable Rate Guidelines Recommended for Power Calculation

| Component | Definition                                   | Guideline |  |  |  |  |

|-----------|----------------------------------------------|-----------|--|--|--|--|

| $\beta_1$ | β <sub>1</sub> I/O output buffer enable rate |           |  |  |  |  |

| $\beta_2$ | 12.5%                                        |           |  |  |  |  |

| $\beta_3$ | RAM enable rate for write operations         | 12.5%     |  |  |  |  |

| $\beta_4$ | NVM enable rate for read operations          | 0%        |  |  |  |  |

3-27 Revision 6

# **PQ208**

# Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

4-7 Revision 6

| FG484         |                 |                  |

|---------------|-----------------|------------------|

| Pin<br>Number | AFS600 Function | AFS1500 Function |

| A1            | GND             | GND              |

| A2            | VCC             | NC               |

| A3            | GAA1/IO01PDB0V0 | GAA1/IO01PDB0V0  |

| A4            | GAB0/IO02NDB0V0 | GAB0/IO02NDB0V0  |

| A5            | GAB1/IO02PDB0V0 | GAB1/IO02PDB0V0  |

| A6            | IO07NDB0V1      | IO07NDB0V1       |

| A7            | IO07PDB0V1      | IO07PDB0V1       |

| A8            | IO10PDB0V1      | IO09PDB0V1       |

| A9            | IO14NDB0V1      | IO13NDB0V2       |

| A10           | IO14PDB0V1      | IO13PDB0V2       |

| A11           | IO17PDB1V0      | IO24PDB1V0       |

| A12           | IO18PDB1V0      | IO26PDB1V0       |

| A13           | IO19NDB1V0      | IO27NDB1V1       |

| A14           | IO19PDB1V0      | IO27PDB1V1       |

| A15           | IO24NDB1V1      | IO35NDB1V2       |

| A16           | IO24PDB1V1      | IO35PDB1V2       |

| A17           | GBC0/IO26NDB1V1 | GBC0/IO40NDB1V2  |

| A18           | GBA0/IO28NDB1V1 | GBA0/IO42NDB1V2  |

| A19           | IO29NDB1V1      | IO43NDB1V2       |

| A20           | IO29PDB1V1      | IO43PDB1V2       |

| A21           | VCC             | NC               |

| A22           | GND             | GND              |

| AA1           | VCC             | NC               |

| AA2           | GND             | GND              |

| AA3           | VCCIB4          | VCCIB4           |

| AA4           | VCCIB4          | VCCIB4           |

| AA5           | PCAP            | PCAP             |

| AA6           | AG0             | AG0              |

| AA7           | GNDA            | GNDA             |

| AA8           | AG1             | AG1              |

| AA9           | AG2             | AG2              |

| AA10          | GNDA            | GNDA             |

| AA11          | AG3             | AG3              |

| AA12          | AG6             | AG6              |

| AA13          | GNDA            | GNDA             |

| FG484         |                 |                  |

|---------------|-----------------|------------------|

| Pin<br>Number | AFS600 Function | AFS1500 Function |

| AA14          | AG7             | AG7              |

| AA15          | AG8             | AG8              |

| AA16          | GNDA            | GNDA             |

| AA17          | AG9             | AG9              |

| AA18          | VAREF           | VAREF            |

| AA19          | VCCIB2          | VCCIB2           |

| AA20          | PTEM            | PTEM             |

| AA21          | GND             | GND              |

| AA22          | VCC             | NC               |

| AB1           | GND             | GND              |

| AB2           | VCC             | NC               |

| AB3           | NC              | IO94NSB4V0       |

| AB4           | GND             | GND              |

| AB5           | VCC33N          | VCC33N           |

| AB6           | AT0             | AT0              |

| AB7           | ATRTN0          | ATRTN0           |

| AB8           | AT1             | AT1              |

| AB9           | AT2             | AT2              |

| AB10          | ATRTN1          | ATRTN1           |

| AB11          | AT3             | AT3              |

| AB12          | AT6             | AT6              |

| AB13          | ATRTN3          | ATRTN3           |

| AB14          | AT7             | AT7              |

| AB15          | AT8             | AT8              |

| AB16          | ATRTN4          | ATRTN4           |

| AB17          | AT9             | AT9              |

| AB18          | VCC33A          | VCC33A           |

| AB19          | GND             | GND              |

| AB20          | NC              | IO76NPB2V0       |

| AB21          | VCC             | NC               |

| AB22          | GND             | GND              |

| B1            | VCC             | NC               |

| B2            | GND             | GND              |

| В3            | GAA0/IO01NDB0V0 | GAA0/IO01NDB0V0  |

| B4            | GND             | GND              |

4-20 Revision 6