Welcome to E-XFL.COM

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | ·                                                             |

| Number of Logic Elements/Cells |                                                               |

| Total RAM Bits                 | 36864                                                         |

| Number of I/O                  | 93                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 208-BFQFP                                                     |

| Supplier Device Package        | 208-PQFP (28x28)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs250-1pqg208 |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Device Architecture

#### Timing Characteristics

Table 2-1 • Combinatorial Cell Propagation DelaysCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                  | Parameter       | -2   | -1   | Std. | Units |

|--------------------|---------------------------|-----------------|------|------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 0.40 | 0.46 | 0.54 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| NAND2              | Y = !(A ⋅ B)              | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 0.74 | 0.84 | 0.99 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 0.70 | 0.79 | 0.93 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 0.87 | 1.00 | 1.17 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 0.51 | 0.58 | 0.68 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 0.56 | 0.64 | 0.75 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

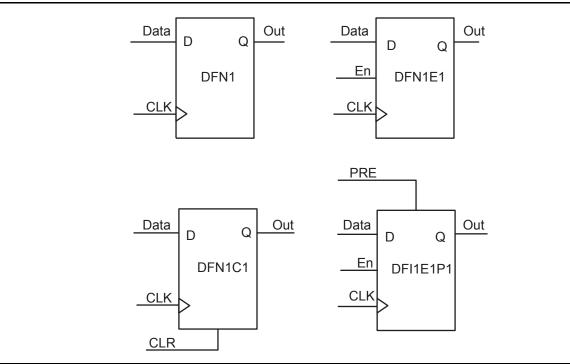

## Sample VersaTile Specifications—Sequential Module

The Fusion library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library (Figure 2-5). For more details, refer to the *IGLOO*, *ProASIC3*, *SmartFusion and Fusion Macro Library Guide*.

Figure 2-5 • Sample of Sequential Cells

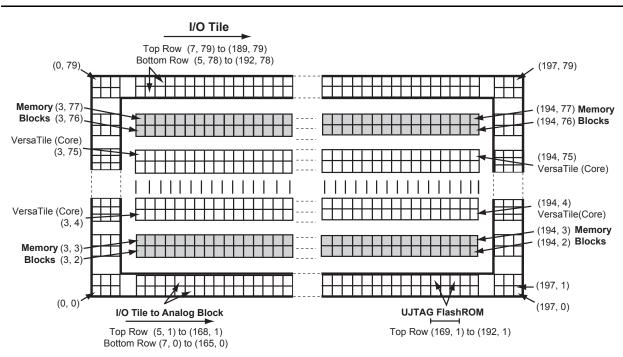

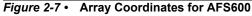

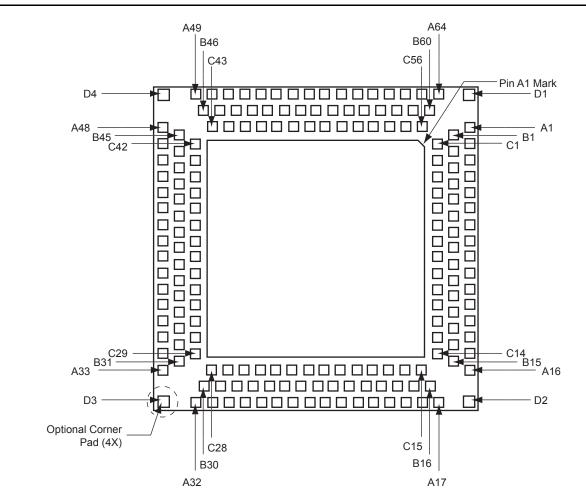

# **Array Coordinates**

During many place-and-route operations in the Microsemi Designer software tool, it is possible to set constraints that require array coordinates. Table 2-3 is provided as a reference. The array coordinates are measured from the lower left (0, 0). They can be used in region constraints for specific logic groups/blocks, designated by a wildcard, and can contain core cells, memories, and I/Os.

Table 2-3 provides array coordinates of core cells and memory blocks.

I/O and cell coordinates are used for placement constraints. Two coordinate systems are needed because there is not a one-to-one correspondence between I/O cells and edge core cells. In addition, the I/O coordinate system changes depending on the die/package combination. It is not listed in Table 2-3. The Designer ChipPlanner tool provides array coordinates of all I/O locations. I/O and cell coordinates are used for placement constraints. However, I/O placement is easier by package pin assignment.

Figure 2-7 illustrates the array coordinates of an AFS600 device. For more information on how to use array coordinates for region/placement constraints, see the *Designer User's Guide* or online help (available in the software) for Fusion software tools.

|         | VersaTiles |     |     |      | Memor  | y Rows   | All    |            |  |

|---------|------------|-----|-----|------|--------|----------|--------|------------|--|

| Device  | М          | in. | М   | Max. |        | Тор      | Min.   | Max.       |  |

|         | x          | У   | x   | У    | (x, y) | (x, y)   | (x, y) | (x, y)     |  |

| AFS090  | 3          | 2   | 98  | 25   | None   | (3, 26)  | (0, 0) | (101, 29)  |  |

| AFS250  | 3          | 2   | 130 | 49   | None   | (3, 50)  | (0, 0) | (133, 53)  |  |

| AFS600  | 3          | 4   | 194 | 75   | (3, 2) | (3, 76)  | (0, 0) | (197, 79)  |  |

| AFS1500 | 3          | 4   | 322 | 123  | (3, 2) | (3, 124) | (0, 0) | (325, 129) |  |

#### Table 2-3 • Array Coordinates

| Figure 2-12 • Global Network Architecture | ; |

|-------------------------------------------|---|

|-------------------------------------------|---|

## Table 2-4 • Globals/Spines/Rows by Device

|                                        | AFS090 | AFS250 | AFS600 | AFS1500 |

|----------------------------------------|--------|--------|--------|---------|

| Global VersaNets (trees)*              | 9      | 9      | 9      | 9       |

| VersaNet Spines/Tree                   | 4      | 8      | 12     | 20      |

| Total Spines                           | 36     | 72     | 108    | 180     |

| VersaTiles in Each Top or Bottom Spine | 384    | 768    | 1,152  | 1,920   |

| Total VersaTiles                       | 2,304  | 6,144  | 13,824 | 38,400  |

Note: \*There are six chip (main) globals and three globals per quadrant.

# Clock Conditioning Circuits

In Fusion devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations.

The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides.

Each CCC can implement up to three independent global buffers (with or without programmable delay), or a PLL function (programmable frequency division/multiplication, phase shift, and delays) with up to three global outputs. Unused global outputs of a PLL can be used to implement independent global buffers, up to a maximum of three global outputs for a given CCC.

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, and CLKC-GLC) of a given CCC.

A PLL macro uses the CLKA CCC input to drive its reference clock. It uses the GLA and, optionally, the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global output cannot be reused if the YB (or YC) output is used (Figure 2-19). Refer to the "PLL Macro" section on page 2-27 for more information.

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- · 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

- The FPGA core

The CCC block is fully configurable, either via flash configuration bits set in the programming bitstream or through an asynchronous interface. This asynchronous interface is dynamically accessible from inside the Fusion device to permit changes of parameters (such as divide ratios) during device operation. To increase the versatility and flexibility of the clock conditioning system, the CCC configuration is determined either by the user during the design process, with configuration data being stored in flash memory as part of the device programming procedure, or by writing data into a dedicated shift register during normal device operation. This latter mode allows the user to dynamically reconfigure the CCC without the need for core programming. The shift register is accessed through a simple serial interface. Refer to the "UJTAG Applications in Microsemi's Low-Power Flash Devices" chapter of the *Fusion FPGA Fabric User Guide* and the "CCC and PLL Characteristics" section on page 2-28 for more information.

There are several popular ADC architectures, each with advantages and limitations.

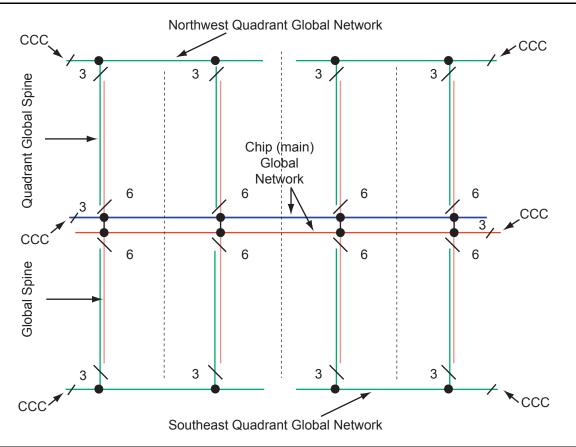

The analog-to-digital converter in Fusion devices is a switched-capacitor Successive Approximation Register (SAR) ADC. It supports 8-, 10-, and 12-bit modes of operation with a cumulative sample rate up to 600 k samples per second (ksps). Built-in bandgap circuitry offers 1% internal voltage reference accuracy or an external reference voltage can be used.

As shown in Figure 2-81, a SAR ADC contains N capacitors with binary-weighted values.

Figure 2-81 • Example SAR ADC Architecture

To begin a conversion, all of the capacitors are quickly discharged. Then VIN is applied to all the capacitors for a period of time (acquisition time) during which the capacitors are charged to a value very close to VIN. Then all of the capacitors are switched to ground, and thus –VIN is applied across the comparator. Now the conversion process begins. First, C is switched to VREF Because of the binary weighting of the capacitors, the voltage at the input of the comparator is then shown by EQ 11.

Voltage at input of comparator = -VIN + VREF / 2

EQ 11

If VIN is greater than VREF / 2, the output of the comparator is 1; otherwise, the comparator output is 0. A register is clocked to retain this value as the MSB of the result. Next, if the MSB is 0, C is switched back to ground; otherwise, it remains connected to VREF, and C / 2 is connected to VREF. The result at the comparator input is now either –VIN + VREF / 4 or –VIN + 3 VREF / 4 (depending on the state of the MSB), and the comparator output now indicates the value of the next most significant bit. This bit is likewise registered, and the process continues for each subsequent bit until a conversion is complete. The conversion process requires some acquisition time plus N + 1 ADC clock cycles to complete.

Device Architecture

## Integrated Voltage Reference

The Fusion device has an integrated on-chip 2.56 V reference voltage for the ADC. The value of this reference voltage was chosen to make the prescaling and postscaling factors for the prescaler blocks change in a binary fashion. However, if desired, an external reference voltage of up to 3.3 V can be connected between the VAREF and ADCGNDREF pins. The VAREFSEL control pin is used to select the reference voltage.

Table 2-42 • VAREF Bit Function

| Name  | Bit | Function                                                           |

|-------|-----|--------------------------------------------------------------------|

| VAREF | 0   | Reference voltage selection                                        |

|       |     | 0 – Internal voltage reference selected. VAREF pin outputs 2.56 V. |

|       |     | 1 – Input external voltage reference from VAREF and ADCGNDREF      |

#### ADC Clock

The speed of the ADC depends on its internal clock, ADCCLK, which is not accessible to users. The ADCCLK is derived from SYSCLK. Input signal TVC[7:0], Time Divider Control, determines the speed of the ADCCLK in relationship to SYSCLK, based on EQ 15.

$$t_{ADCCLK} = 4 \times (1 + TVC) \times t_{SYSCLK}$$

EQ 15

TVC: Time Divider Control (0-255)

$t_{\text{ADCCLK}}$  is the period of ADCCLK, and must be between 0.5 MHz and 10 MHz  $t_{\text{SYSCLK}}$  is the period of SYSCLK

#### Table 2-43 • TVC Bits Function

| Name | Bits  | Function               |

|------|-------|------------------------|

| TVC  | [7:0] | SYSCLK divider control |

The frequency of ADCCLK, f<sub>ADCCLK</sub>, must be within 0.5 Hz to 10 MHz.

The inputs to the ADC are synchronized to SYSCLK. A conversion is initiated by asserting the ADCSTART signal on a rising edge of SYSCLK. Figure 2-90 on page 2-112 and Figure 2-91 on page 2-112 show the timing diagram for the ADC.

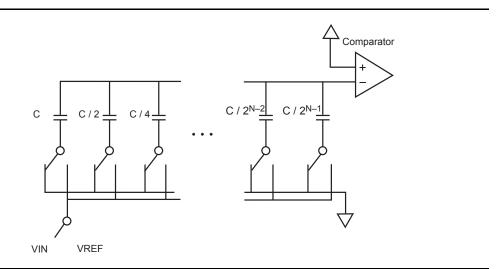

## Acquisition Time or Sample Time Control

Acquisition time (t<sub>SAMPLE</sub>) specifies how long an analog input signal has to charge the internal capacitor array. Figure 2-88 shows a simplified internal input sampling mechanism of a SAR ADC.

## Figure 2-88 • Simplified Sample and Hold Circuitry

The internal impedance ( $Z_{INAD}$ ), external source resistance ( $R_{SOURCE}$ ), and sample capacitor ( $C_{INAD}$ ) form a simple RC network. As a result, the accuracy of the ADC can be affected if the ADC is given insufficient time to charge the capacitor. To resolve this problem, you can either reduce the source resistance or increase the sampling time by changing the acquisition time using the STC signal.

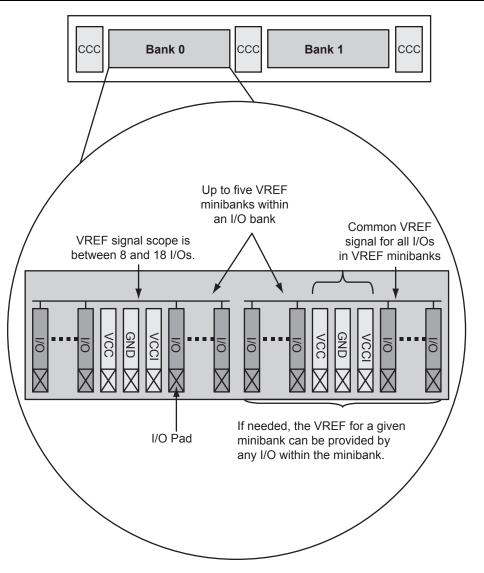

Figure 2-99 • Fusion Pro I/O Bank Detail Showing VREF Minibanks (north side of AFS600 and AFS1500)

| I/O Bank     | Single-Ended I/O Standards                                                                        | Differential I/O<br>Standards | Voltage-Referenced                                                                                          | Hot-<br>Swap |

|--------------|---------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------|--------------|

| Standard I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V                          | _                             | -                                                                                                           | Yes          |

| Advanced I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | -                                                                                                           | -            |

| Pro I/O      | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | GTL+2.5 V / 3.3 V, GTL 2.5 V / 3.3 V,<br>HSTL Class I and II, SSTL2 Class I<br>and II, SSTL3 Class I and II | Yes          |

# **5 V Input Tolerance**

I/Os can support 5 V input tolerance when LVTTL 3.3 V, LVCMOS 3.3 V, LVCMOS 2.5 V / 5 V, and LVCMOS 2.5 V configurations are used (see Table 2-77 on page 2-147 for more details). There are four recommended solutions (see Figure 2-103 to Figure 2-106 on page 2-146 for details of board and macro setups) to achieve 5 V receiver tolerance. All the solutions meet a common requirement of limiting the voltage at the input to 3.6 V or less. In fact, the I/O absolute maximum voltage rating is 3.6 V, and any voltage above 3.6 V may cause long-term gate oxide failures.

# Solution 1

The board-level design needs to ensure that the reflected waveform at the pad does not exceed the limits provided in Table 3-4 on page 3-4. This is a long-term reliability requirement.

This scheme will also work for a 3.3 V PCI / PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the two external resistors, as explained below. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

The following are some examples of possible resistor values (based on a simplified simulation model with no line effects and 10  $\Omega$  transmitter output resistance, where Rtx\_out\_high = (VCCI – VOH) / IOH, Rtx\_out\_low = VOL / IOL).

Example 1 (high speed, high current):

Rtx\_out\_high = Rtx\_out\_low = 10  $\Omega$

R1 = 36  $\Omega$  (±5%), P(r1)min = 0.069  $\Omega$

R2 = 82  $\Omega$  (±5%), P(r2)min = 0.158  $\Omega$

Imax\_tx = 5.5 V / (82 \* 0.95 + 36 \* 0.95 + 10) = 45.04 mA

t<sub>RISE</sub> = t<sub>FALL</sub> = 0.85 ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

t<sub>RISE</sub> = t<sub>FALL</sub> = 4 ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

Example 2 (low-medium speed, medium current):

Rtx\_out\_high = Rtx\_out\_low = 10  $\Omega$

R1 = 220 Ω (±5%), P(r1)min = 0.018 Ω

R2 = 390  $\Omega$  (±5%), P(r2)min = 0.032  $\Omega$

Imax\_tx = 5.5 V / (220 \* 0.95 + 390 \* 0.95 + 10) = 9.17 mA

t<sub>RISE</sub> = t<sub>FALL</sub> = 4 ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

t<sub>RISE</sub> = t<sub>FALL</sub> = 20 ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

Other values of resistors are also allowed as long as the resistors are sized appropriately to limit the voltage at the receiving end to 2.5 V < Vin(rx) < 3.6 V when the transmitter sends a logic 1. This range of Vin\_dc(rx) must be assured for any combination of transmitter supply (5 V ± 0.5 V), transmitter output resistance, and board resistor tolerances.

# Voltage Referenced I/O Characteristics

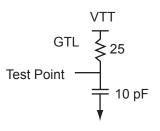

## 3.3 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

| 3.3 V GTL          |           | VIL         | VIF         | 1         | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 20 mA <sup>3</sup> | -0.3      | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | -         | 20  | 20  | 181                     | 268                     | 10               | 10               |

Table 2-138 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

## Figure 2-124 • AC Loading

#### Table 2-139 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                  | 0.8             | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-140 • 3.3 V GTL

```

Commercial Temperature Range Conditions: T_J = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 0.8 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.08            | 0.04             | 2.93            | 0.43              | 2.04            | 2.08            |                 |                 | 4.27             | 4.31             | ns    |

| -1             | 0.56              | 1.77            | 0.04             | 2.50            | 0.36              | 1.73            | 1.77            |                 |                 | 3.63             | 3.67             | ns    |

| -2             | 0.49              | 1.55            | 0.03             | 2.19            | 0.32              | 1.52            | 1.55            |                 |                 | 3.19             | 3.22             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

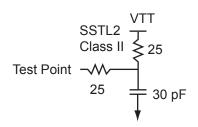

## SSTL2 Class II

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). Fusion devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

| SSTL2 Class II |           | VIL        | VIH        |           | VOL       | VOH         | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|----------------|-----------|------------|------------|-----------|-----------|-------------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 18 mA          | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.35      | VCCI – 0.43 | 18  | 18  | 124                     | 169                     | 10               | 10               |

Table 2-159 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

## Figure 2-131 • AC Loading

#### Table 2-160 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                 | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

#### Table 2-161 • SSTL 2 Class II Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.25 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.17            | 0.04             | 1.33            | 0.43              | 2.21            | 1.77            |                 |                 | 4.44             | 4.01             | ns    |

| -1             | 0.56              | 1.84            | 0.04             | 1.14            | 0.36              | 1.88            | 1.51            |                 |                 | 3.78             | 3.41             | ns    |

| -2             | 0.49              | 1.62            | 0.03             | 1.00            | 0.32              | 1.65            | 1.32            |                 |                 | 3.32             | 2.99             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Table 2-169 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.075         | 1.325          | Cross point          | -               |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

#### Table 2-170 • LVDS

# Commercial Temperature Range Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 2.10            | 0.04             | 1.82            | ns    |

| -1          | 0.56              | 1.79            | 0.04             | 1.55            | ns    |

| -2          | 0.49              | 1.57            | 0.03             | 1.36            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

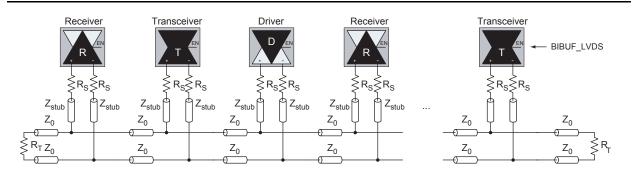

## BLVDS/M-LVDS

Bus LVDS (BLVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations can contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by BLVDS and M-LVDS to accommodate the loading. The driver requires series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus, since the driver can be located anywhere on the bus. These configurations can be implemented using TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-135. The input and output buffer delays are available in the LVDS section in Table 2-171.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case industrial operating conditions at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

Figure 2-135 • BLVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

#### VCC Core Supply Voltage

Supply voltage to the FPGA core, nominally 1.5 V. VCC is also required for powering the JTAG state machine, in addition to VJTAG. Even when a Fusion device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the Fusion device.

#### VCCIBx I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are either four (AFS090 and AFS250) or five (AFS600 and AFS1500) I/O banks on the Fusion devices plus a dedicated VJTAG bank.

Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCI pins tied to GND.

#### VCCPLA/B PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V, where A and B refer to the PLL. AFS090 and AFS250 each have a single PLL. The AFS600 and AFS1500 devices each have two PLLs. Microsemi recommends tying VCCPLX to VCC and using proper filtering circuits to decouple VCC noise from PLL.

If unused, VCCPLA/B should be tied to GND.

#### VCOMPLA/B Ground for West and East PLL

VCOMPLA is the ground of the west PLL (CCC location F) and VCOMPLB is the ground of the east PLL (CCC location C).

#### VJTAG JTAG Supply Voltage

Fusion devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a Fusion device is in a JTAG chain of interconnected boards and it is desired to power down the board containing the Fusion device, this may be done provided both VJTAG and VCC to the Fusion part remain powered; otherwise, JTAG signals will not be able to transition the Fusion device, even in bypass mode.

#### VPUMP Programming Supply Voltage

Fusion devices support single-voltage ISP programming of the configuration flash and FlashROM. For programming, VPUMP should be in the 3.3 V +/-5% range. During normal device operation, VPUMP can be left floating or can be tied to any voltage between 0 V and 3.6 V.

When the VPUMP pin is tied to ground, it shuts off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

The 1.76 W power is less than the required 3.00 W. The design therefore requires a heat sink, or the airflow where the device is mounted should be increased. The design's total junction-to-air thermal resistance requirement can be estimated by EQ 7:

$$\theta_{ja(total)} = \frac{T_J - T_A}{P} = \frac{100^{\circ}C - 70^{\circ}C}{3.00 W} = 10.00^{\circ}C/W$$

Determining the heat sink's thermal performance proceeds as follows:

$$\theta_{\text{JA(TOTAL)}} = \theta_{\text{JC}} + \theta_{\text{CS}} + \theta_{\text{SA}}$$

EQ 8

EQ 7

where

- $\theta_{JA} = 0.37^{\circ}C/W$

- Thermal resistance of the interface material between the case and the heat sink, usually provided by the thermal interface manufacturer

$\theta_{SA}$  = Thermal resistance of the heat sink in °C/W

$$\theta_{SA} = \theta_{JA(TOTAL)} - \theta_{JC} - \theta_{CS}$$

EQ 9

$$\theta_{SA} = 13.33^{\circ}C/W - 8.28^{\circ}C/W - 0.37^{\circ}C/W = 5.01^{\circ}C/W$$

A heat sink with a thermal resistance of 5.01°C/W or better should be used. Thermal resistance of heat sinks is a function of airflow. The heat sink performance can be significantly improved with increased airflow.

Carefully estimating thermal resistance is important in the long-term reliability of an Microsemi FPGA. Design engineers should always correlate the power consumption of the device with the maximum allowable power dissipation of the package selected for that device.

Note: The junction-to-air and junction-to-board thermal resistances are based on JEDEC standard (JESD-51) and assumptions made in building the model. It may not be realized in actual application and therefore should be used with a degree of caution. Junction-to-case thermal resistance assumes that all power is dissipated through the case.

# Temperature and Voltage Derating Factors

Table 3-7 • Temperature and Voltage Derating Factors for Timing Delays<br/>(normalized to  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V)

| Array Voltage |       |      | Junction Ter | nperature (°C) |      |       |  |  |  |  |  |  |  |

|---------------|-------|------|--------------|----------------|------|-------|--|--|--|--|--|--|--|

| VCC (V)       | –40°C | 0°C  | 25°C         | 70°C           | 85°C | 100°C |  |  |  |  |  |  |  |

| 1.425         | 0.88  | 0.93 | 0.95         | 1.00           | 1.02 | 1.05  |  |  |  |  |  |  |  |

| 1.500         | 0.83  | 0.88 | 0.90         | 0.95           | 0.96 | 0.99  |  |  |  |  |  |  |  |

| 1.575         | 0.80  | 0.85 | 0.87         | 0.91           | 0.93 | 0.96  |  |  |  |  |  |  |  |

DC and Power Characteristics

| Table 3-10 • AFS250 Quiescent Supply Current | Characteristics (continued) |

|----------------------------------------------|-----------------------------|

|----------------------------------------------|-----------------------------|

| Parameter | Description                 | Conditions                                                            | Temp.                  | Min | Тур | Мах | Unit |

|-----------|-----------------------------|-----------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| IPP       | Programming supply          | Non-programming mode,                                                 | T <sub>J</sub> = 25°C  |     | 37  | 80  | μA   |

|           | current                     | VPUMP = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 37  | 80  | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 80  | 100 | μA   |

|           |                             | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VPUMP = 0 V |                        |     | 0   | 0   | μA   |

| ICCNVM    | Embedded NVM current        | Reset asserted,                                                       | T <sub>J</sub> = 25°C  |     | 10  | 40  | μA   |

|           |                             | VCCNVM = 1.575 V                                                      | T <sub>J</sub> = 85°C  |     | 14  | 40  | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 14  | 40  | μA   |

| ICCPLL    | 1.5 V PLL quiescent current | Operational standby,                                                  | T <sub>J</sub> = 25°C  |     | 65  | 100 | μA   |

|           |                             | VCCPLL = 1.575 V                                                      | T <sub>J</sub> = 85°C  |     | 65  | 100 | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 65  | 100 | μA   |

Notes:

- 1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, and ICCI2.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTA G = VPUMP = 0 V.

# **Static Power Consumption of Various Internal Resources**

Table 3-15 • Different Components Contributing to the Static Power Consumption in Fusion Devices

| 1         |                                                                     |        |                             |          |            |            |          |       |  |

|-----------|---------------------------------------------------------------------|--------|-----------------------------|----------|------------|------------|----------|-------|--|

|           |                                                                     | Power  |                             | Device-S | pecific St | atic Contr | ibutions |       |  |

| Parameter | Definition                                                          | Supply |                             | AFS1500  | AFS600     | AFS250     | AFS090   | Units |  |

| PDC1      | Core static power contribution in<br>operating mode                 | VCC    | 1.5 V                       | 18       | 7.5        | 4.50       | 3.00     | mW    |  |

| PDC2      | Device static power contribution in<br>standby mode                 | VCC33A | 3.3 V                       |          | 0.0        | 66         |          | mW    |  |

| PDC3      | Device static power contribution in<br>sleep mode                   | VCC33A | 3.3 V                       | V 0.03   |            |            |          | mW    |  |

| PDC4      | NVM static power contribution                                       | VCC    | 1.5 V                       | 1.19     |            |            |          | mW    |  |

| PDC5      | Analog Block static power<br>contribution of ADC                    | VCC33A | 3.3 V                       | 8.25     |            |            |          | mW    |  |

| PDC6      | Analog Block static power<br>contribution per Quad                  | VCC33A | 3.3 V                       | 3.3      |            |            |          | mW    |  |

| PDC7      | Static contribution per input pin – standard dependent contribution | VCCI   | See Table 3-12 on page 3-18 |          |            |            |          |       |  |

| PDC8      | Static contribution per input pin – standard dependent contribution | VCCI   | See Table 3-13 on page 3-20 |          |            |            |          |       |  |

| PDC9      | Static contribution for PLL                                         | VCC    | 1.5 V                       |          | 2.         | 55         |          | mW    |  |

# **Power Calculation Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in the Libero SoC software.

The power calculation methodology described below uses the following variables:

- The number of PLLs as well as the number and the frequency of each output clock generated

- · The number of combinatorial and sequential cells used in the design

- The internal clock frequencies

- · The number and the standard of I/O pins used in the design

- The number of RAM blocks used in the design

- The number of NVM blocks used in the design

- The number of Analog Quads used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 3-16 on page 3-27.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 3-17 on page 3-27.

- Read rate and write rate to the RAM—guidelines are provided for typical applications in Table 3-17 on page 3-27.

- Read rate to the NVM blocks

The calculation should be repeated for each clock domain defined in the design.

# **QN180**

Note: The die attach paddle center of the package is tied to ground (GND).

# Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

Package Pin Assignments

|            | QN180           |                 |  |  |

|------------|-----------------|-----------------|--|--|

| Pin Number | AFS090 Function | AFS250 Function |  |  |

| C21        | AG2             | AG2             |  |  |

| C22        | NC              | NC              |  |  |

| C23        | NC              | NC              |  |  |

| C24        | NC              | NC              |  |  |

| C25        | NC              | AT5             |  |  |

| C26        | GNDAQ           | GNDAQ           |  |  |

| C27        | NC              | NC              |  |  |

| C28        | NC              | NC              |  |  |

| C29        | NC              | NC              |  |  |

| C30        | NC              | NC              |  |  |

| C31        | GND             | GND             |  |  |

| C32        | NC              | NC              |  |  |

| C33        | NC              | NC              |  |  |

| C34        | NC              | NC              |  |  |

| C35        | GND             | GND             |  |  |

| C36        | GDB0/IO39NPB1V0 | GDA0/IO54NPB1V0 |  |  |

| C37        | GDA1/IO37NSB1V0 | GDC0/IO52NSB1V0 |  |  |

| C38        | GCA0/IO36NDB1V0 | GCA0/IO49NDB1V0 |  |  |

| C39        | GCB1/IO35PPB1V0 | GCB1/IO48PPB1V0 |  |  |

| C40        | GND             | GND             |  |  |

| C41        | GCA2/IO32NPB1V0 | IO41NPB1V0      |  |  |

| C42        | GBB2/IO31NDB1V0 | IO40NDB1V0      |  |  |

| C43        | NC              | NC              |  |  |

| C44        | NC              | GBA1/IO39RSB0V0 |  |  |

| C45        | NC              | GBB0/IO36RSB0V0 |  |  |

| C46        | GND             | GND             |  |  |

| C47        | NC              | IO30RSB0V0      |  |  |

| C48        | IO22RSB0V0      | IO27RSB0V0      |  |  |

| C49        | GND             | GND             |  |  |

| C50        | IO13RSB0V0      | IO16RSB0V0      |  |  |

| C51        | IO09RSB0V0      | IO12RSB0V0      |  |  |

| C52        | IO06RSB0V0      | IO09RSB0V0      |  |  |

| C53        | GND             | GND             |  |  |

| C54        | NC              | GAB1/IO03RSB0V0 |  |  |

| C55        | NC              | GAA0/IO00RSB0V0 |  |  |

| C56        | NC              | NC              |  |  |

|            | QN180           |                 |

|------------|-----------------|-----------------|

| Pin Number | AFS090 Function | AFS250 Function |

| D1         | NC              | NC              |

| D2         | NC              | NC              |

| D3         | NC              | NC              |

| D4         | NC              | NC              |

| FG256      |                 |                 |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| K9         | VCC             | VCC             | VCC             | VCC              |

| K10        | GND             | GND             | GND             | GND              |

| K11        | NC              | GDC2/IO57PPB1V0 | GDC2/IO57PPB2V0 | GDC2/IO84PPB2V0  |

| K12        | GND             | GND             | GND             | GND              |

| K13        | NC              | GDA0/IO54NDB1V0 | GDA0/IO54NDB2V0 | GDA0/IO81NDB2V0  |

| K14        | NC              | GDA2/IO55PPB1V0 | GDA2/IO55PPB2V0 | GDA2/IO82PPB2V0  |

| K15        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| K16        | NC              | GDB1/IO53PPB1V0 | GDB1/IO53PPB2V0 | GDB1/IO80PPB2V0  |

| L1         | NC              | GEC1/IO63PDB3V0 | GEC1/IO63PDB4V0 | GEC1/IO90PDB4V0  |

| L2         | NC              | GEC0/IO63NDB3V0 | GEC0/IO63NDB4V0 | GEC0/IO90NDB4V0  |

| L3         | NC              | GEB1/IO62PDB3V0 | GEB1/IO62PDB4V0 | GEB1/IO89PDB4V0  |

| L4         | NC              | GEB0/IO62NDB3V0 | GEB0/IO62NDB4V0 | GEB0/IO89NDB4V0  |

| L5         | NC              | IO60NDB3V0      | IO60NDB4V0      | IO87NDB4V0       |

| L6         | NC              | GEC2/IO60PDB3V0 | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |

| L7         | GNDA            | GNDA            | GNDA            | GNDA             |

| L8         | AC0             | AC0             | AC2             | AC2              |

| L9         | AV2             | AV2             | AV4             | AV4              |

| L10        | AC3             | AC3             | AC5             | AC5              |

| L11        | PTEM            | PTEM            | PTEM            | PTEM             |

| L12        | TDO             | TDO             | TDO             | TDO              |

| L13        | VJTAG           | VJTAG           | VJTAG           | VJTAG            |

| L14        | NC              | IO57NPB1V0      | IO57NPB2V0      | IO84NPB2V0       |

| L15        | GDB2/IO41PPB1V0 | GDB2/IO56PPB1V0 | GDB2/IO56PPB2V0 | GDB2/IO83PPB2V0  |

| L16        | NC              | IO55NPB1V0      | IO55NPB2V0      | IO82NPB2V0       |

| M1         | GND             | GND             | GND             | GND              |

| M2         | NC              | GEA1/IO61PDB3V0 | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  |

| M3         | NC              | GEA0/IO61NDB3V0 | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  |

| M4         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| M5         | NC              | IO58NPB3V0      | IO58NPB4V0      | IO85NPB4V0       |

| M6         | NC              | NC              | AV0             | AV0              |

| M7         | NC              | NC              | AC1             | AC1              |

| M8         | AG1             | AG1             | AG3             | AG3              |

| M9         | AC2             | AC2             | AC4             | AC4              |

| M10        | AC4             | AC4             | AC6             | AC6              |

| M11        | NC              | AG5             | AG7             | AG7              |

| M12        | VPUMP           | VPUMP           | VPUMP           | VPUMP            |

| M13        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| M14        | TMS             | TMS             | TMS             | TMS              |

# **Datasheet Categories**

# Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "Fusion Device Status" table, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

# **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

## Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

# Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

# Production

This version contains information that is considered to be final.

# **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.