Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | 36864                                                          |

| Number of I/O                  | 65                                                             |

| Number of Gates                | 250000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                                |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                             |

| Package / Case                 | 180-WFQFN Dual Rows, Exposed Pad                               |

| Supplier Device Package        | 180-QFN (10x10)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs250-1qng180i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

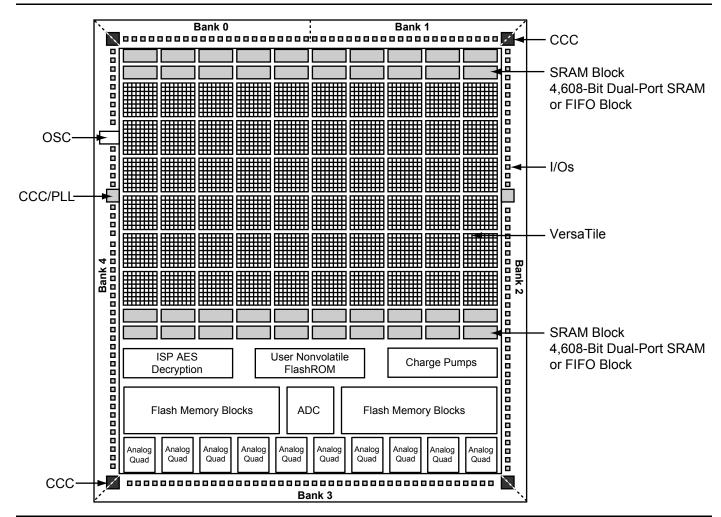

# **Fusion Device Architecture Overview**

Figure 1 • Fusion Device Architecture Overview (AFS600)

# Package I/Os: Single-/Double-Ended (Analog)

| Fusion Devices        | AFS090     | AFS250                | AFS600                | AFS1500                |

|-----------------------|------------|-----------------------|-----------------------|------------------------|

| ARM Cortex-M1 Devices |            | M1AFS250              | M1AFS600              | M1AFS1500              |

| Pigeon Point Devices  |            |                       | P1AFS600 <sup>1</sup> | P1AFS1500 <sup>1</sup> |

| MicroBlade Devices    |            | U1AFS250 <sup>2</sup> | U1AFS600 <sup>2</sup> | U1AFS1500 <sup>2</sup> |

| QN108 <sup>3</sup>    | 37/9 (16)  |                       |                       |                        |

| QN180 <sup>3</sup>    | 60/16 (20) | 65/15 (24)            |                       |                        |

| PQ208 <sup>4</sup>    |            | 93/26 (24)            | 95/46 (40)            |                        |

| FG256                 | 75/22 (20) | 114/37 (24)           | 119/58 (40)           | 119/58 (40)            |

| FG484                 |            |                       | 172/86 (40)           | 223/109 (40)           |

| FG676                 |            |                       |                       | 252/126 (40)           |

#### Notes:

- 1. Pigeon Point devices are only offered in FG484 and FG256.

- 2. MicroBlade devices are only offered in FG256.

- 3. Package not available.

- 4. Fusion devices in the same package are pin compatible with the exception of the PQ208 package (AFS250 and AFS600).

II Revision 6

# **Routing Architecture**

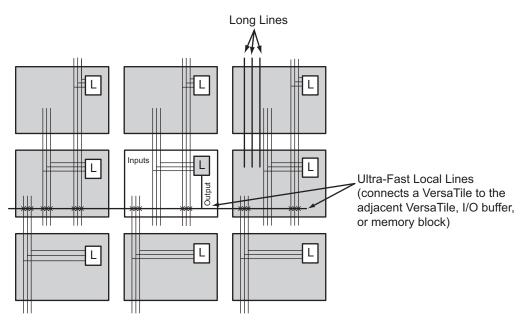

The routing structure of Fusion devices is designed to provide high performance through a flexible four-level hierarchy of routing resources: ultra-fast local resources; efficient long-line resources; high-speed very-long-line resources; and the high-performance VersaNet networks.

The ultra-fast local resources are dedicated lines that allow the output of each VersaTile to connect directly to every input of the eight surrounding VersaTiles (Figure 2-8). The exception to this is that the SET/CLR input of a VersaTile configured as a D-flip-flop is driven only by the VersaNet global network.

The efficient long-line resources provide routing for longer distances and higher-fanout connections. These resources vary in length (spanning one, two, or four VersaTiles), run both vertically and horizontally, and cover the entire Fusion device (Figure 2-9 on page 2-9). Each VersaTile can drive signals onto the efficient long-line resources, which can access every input of every VersaTile. Active buffers are inserted automatically by routing software to limit loading effects.

The high-speed very-long-line resources, which span the entire device with minimal delay, are used to route very long or high-fanout nets: length ±12 VersaTiles in the vertical direction and length ±16 in the horizontal direction from a given core VersaTile (Figure 2-10 on page 2-10). Very long lines in Fusion devices, like those in ProASIC3 devices, have been enhanced. This provides a significant performance boost for long-reach signals.

The high-performance VersaNet global networks are low-skew, high-fanout nets that are accessible from external pins or from internal logic (Figure 2-11 on page 2-11). These nets are typically used to distribute clocks, reset signals, and other high-fanout nets requiring minimum skew. The VersaNet networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically, with signals accessing every input on all VersaTiles.

Note: Input to the core cell for the D-flip-flop set and reset is only available via the VersaNet global network connection.

Figure 2-8 • Ultra-Fast Local Lines Connected to the Eight Nearest Neighbors

Table 2-7 • AFS250 Global Resource Timing

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                               | _                 | -2 -1             |                   | Si                | Units             |                   |        |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------|

| raraineter           | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Office |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.89              | 1.12              | 1.02              | 1.27              | 1.20              | 1.50              | ns     |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.88              | 1.14              | 1.00              | 1.30              | 1.17              | 1.53              | ns     |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |                   |                   |                   |                   |                   |                   | ns     |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |                   |                   |                   |                   |                   |                   | ns     |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.30              |                   | 0.35              | ns     |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-8 • AFS090 Global Resource Timing

Commercial Temperature Range Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V

| Davameter            | December                                  |                   | -2                |                   | -1                |                   | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.84              | 1.07              | 0.96              | 1.21              | 1.13              | 1.43              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.83              | 1.10              | 0.95              | 1.25              | 1.12              | 1.47              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |                   |                   |                   |                   |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |                   |                   |                   |                   |                   |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.27              |                   | 0.30              |                   | 0.36              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-17 Revision 6

# Table 2-16 • RTC Control/Status Register

| Bit | Name         | Description                                                                                                                                                                                                                                                          | Default<br>Value |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 7   | rtc_rst      | RTC Reset                                                                                                                                                                                                                                                            |                  |

|     |              | 1 – Resets the RTC                                                                                                                                                                                                                                                   |                  |

|     |              | 0 – Deassert reset on after two ACM_CLK cycle.                                                                                                                                                                                                                       |                  |

| 6   | cntr_en      | Counter Enable                                                                                                                                                                                                                                                       | 0                |

|     |              | 1 – Enables the counter; rtc_rst must be deasserted as well. First counter increments after 64 RTCCLK positive edges.                                                                                                                                                |                  |

|     |              | 0 – Disables the crystal prescaler but does not reset the counter value. Counter value can only be updated when the counter is disabled.                                                                                                                             |                  |

| 5   | vr_en_mat    | Voltage Regulator Enable on Match                                                                                                                                                                                                                                    | 0                |

|     |              | 1 – Enables RTCMATCH and RTCPSMMATCH to output 1 when the counter value equals the Match Register value. This enables the 1.5 V voltage regulator when RTCPSMMATCH connects to the RTCPSMMATCH signal in VRPSM.  0 – RTCMATCH and RTCPSMMATCH output 0 at all times. |                  |

| 4:3 | xt mode[1:0] | Crystal Mode                                                                                                                                                                                                                                                         | 00               |

| 1.0 | AL_mode[n.o] | Controls RTCXTLMODE[1:0]. Connects to RTC_MODE signal in XTLOSC. XTL_MODE uses this value when xtal_en is 1. See the "Crystal Oscillator" section on page 2-20 for mode configuration.                                                                               |                  |

| 2   | rst_cnt_omat | Reset Counter on Match                                                                                                                                                                                                                                               | 0                |

|     |              | 1 – Enables the sync clear of the counter when the counter value equals the Match Register value. The counter clears on the rising edge of the clock. If all the Match Registers are set to 0, the clear is disabled.  0 – Counter increments indefinitely           |                  |

| 1   | rstb cnt     | Counter Reset, active Low                                                                                                                                                                                                                                            | 0                |

|     | _            | 0 - Resets the 40-bit counter value                                                                                                                                                                                                                                  |                  |

| 0   | xtal_en      | Crystal Enable                                                                                                                                                                                                                                                       | 0                |

|     |              | Controls RTCXTLSEL. Connects to SELMODE signal in XTLOSC.                                                                                                                                                                                                            |                  |

|     |              | 0 – XTLOSC enables control by FPGA_EN; xt_mode is not used. Sleep mode requires this bit to equal 0.                                                                                                                                                                 |                  |

|     |              | 1 – Enables XTLOSC, XTL_MODE control by xt_mode                                                                                                                                                                                                                      |                  |

|     |              | Standby mode requires this bit to be set to 1.                                                                                                                                                                                                                       |                  |

|     |              | See the "Crystal Oscillator" section on page 2-20 for further details on SELMODE configuration.                                                                                                                                                                      |                  |

2-35 Revision 6

# Flash Memory Block Pin Names

Table 2-19 • Flash Memory Block Pin Names

| Interface Name   | Width | Direction | Description                                                                                                                              |

|------------------|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR[17:0]       | 18    | In        | Byte offset into the FB. Byte-based address.                                                                                             |

| AUXBLOCK         | 1     | In        | When asserted, the page addressed is used to access the auxiliary block within that page.                                                |

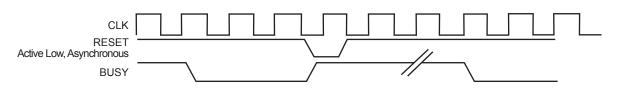

| BUSY             | 1     | Out       | When asserted, indicates that the FB is performing an operation.                                                                         |

| CLK              | 1     | ln        | User interface clock. All operations and status are synchronous to the rising edge of this clock.                                        |

| DATAWIDTH[1:0]   | 2     | In        | Data width  00 = 1 byte in RD/WD[7:0]  01 = 2 bytes in RD/WD[15:0]  1x = 4 bytes in RD/WD[31:0]                                          |

| DISCARDPAGE      | 1     | In        | When asserted, the contents of the Page Buffer are discarded so that a new page write can be started.                                    |

| ERASEPAGE        | 1     | In        | When asserted, the address page is to be programmed with all zeros. ERASEPAGE must transition synchronously with the rising edge of CLK. |

| LOCKREQUEST      | 1     | ln        | When asserted, indicates to the JTAG controller that the FPGA interface is accessing the FB.                                             |

| OVERWRITEPAGE    | 1     | ln        | When asserted, the page addressed is overwritten with the contents of the Page Buffer if the page is writable.                           |

| OVERWRITEPROTECT | 1     | ln        | When asserted, all program operations will set the overwrite protect bit of the page being programmed.                                   |

| PAGESTATUS       | 1     | In        | When asserted with REN, initiates a read page status operation.                                                                          |

| PAGELOSSPROTECT  | 1     | ln        | When asserted, a modified Page Buffer must be programmed or discarded before accessing a new page.                                       |

| PIPE             | 1     | In        | Adds a pipeline stage to the output for operation above 50 MHz.                                                                          |

| PROGRAM          | 1     | ln        | When asserted, writes the contents of the Page Buffer into the FB page addressed.                                                        |

| RD[31:0]         | 32    | Out       | Read data; data will be valid from the first non-busy cycle (BUSY = 0) after REN has been asserted.                                      |

| READNEXT         | 1     | In        | When asserted with REN, initiates a read-next operation.                                                                                 |

| REN              | 1     | In        | When asserted, initiates a read operation.                                                                                               |

| RESET            | 1     | In        | When asserted, resets the state of the FB (active low).                                                                                  |

| SPAREPAGE        | 1     | ln        | When asserted, the sector addressed is used to access the spare page within that sector.                                                 |

# Flash Memory Block Characteristics

Figure 2-44 • Reset Timing Diagram

Table 2-25 • Flash Memory Block Timing Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V

| Parameter                  | Description                                        | -2    | -1    | Std.  | Units |

|----------------------------|----------------------------------------------------|-------|-------|-------|-------|

| + .                        | Clock-to-Q in 5-cycle read mode of the Read Data   | 7.99  | 9.10  | 10.70 | ns    |

| t <sub>CLK2RD</sub>        | Clock-to-Q in 6-cycle read mode of the Read Data   | 5.03  | 5.73  | 6.74  | ns    |

| +                          | Clock-to-Q in 5-cycle read mode of BUSY            | 4.95  | 5.63  | 6.62  | ns    |

| t <sub>CLK2BUSY</sub>      | Clock-to-Q in 6-cycle read mode of BUSY            | 4.45  | 5.07  | 5.96  | ns    |

| +                          | Clock-to-Status in 5-cycle read mode               | 11.24 | 12.81 | 15.06 | ns    |

| <sup>T</sup> CLK2STATUS    | Clock-to-Status in 6-cycle read mode               | 4.48  | 5.10  | 6.00  | ns    |

| t <sub>DSUNVM</sub>        | Data Input Setup time for the Control Logic        | 1.92  | 2.19  | 2.57  | ns    |

| t <sub>DHNVM</sub>         | Data Input Hold time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>ASUNVM</sub>        | Address Input Setup time for the Control Logic     | 2.76  | 3.14  | 3.69  | ns    |

| t <sub>AHNVM</sub>         | Address Input Hold time for the Control Logic      | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUDWNVM</sub>       | Data Width Setup time for the Control Logic        | 1.85  | 2.11  | 2.48  | ns    |

| t <sub>HDDWNVM</sub>       | Data Width Hold time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SURENNVM</sub>      | Read Enable Setup time for the Control Logic       | 3.85  | 4.39  | 5.16  | ns    |

| t <sub>HDRENNVM</sub>      | Read Enable Hold Time for the Control Logic        | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUWENNVM</sub>      | Write Enable Setup time for the Control Logic      | 2.37  | 2.69  | 3.17  | ns    |

| t <sub>HDWENNVM</sub>      | Write Enable Hold Time for the Control Logic       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUPROGNVM</sub>     | Program Setup time for the Control Logic           | 2.16  | 2.46  | 2.89  | ns    |

| t <sub>HDPROGNVM</sub>     | Program Hold time for the Control Logic            | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUSPAREPAGE</sub>   | SparePage Setup time for the Control Logic         | 3.74  | 4.26  | 5.01  | ns    |

| t <sub>HDSPAREPAGE</sub>   | SparePage Hold time for the Control Logic          | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUAUXBLK</sub>      | Auxiliary Block Setup Time for the Control Logic   | 3.74  | 4.26  | 5.00  | ns    |

| t <sub>HDAUXBLK</sub>      | Auxiliary Block Hold Time for the Control Logic    | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SURDNEXT</sub>      | ReadNext Setup Time for the Control Logic          | 2.17  | 2.47  | 2.90  | ns    |

| t <sub>HDRDNEXT</sub>      | ReadNext Hold Time for the Control Logic           | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUERASEPG</sub>     | Erase Page Setup Time for the Control Logic        | 3.76  | 4.28  | 5.03  | ns    |

| t <sub>HDERASEPG</sub>     | Erase Page Hold Time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUUNPROTECTPG</sub> | Unprotect Page Setup Time for the Control Logic    | 2.01  | 2.29  | 2.69  | ns    |

| thdunprotecteg             | Unprotect Page Hold Time for the Control Logic     | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUDISCARDPG</sub>   | Discard Page Setup Time for the Control Logic      | 1.88  | 2.14  | 2.52  | ns    |

| t <sub>HDDISCARDPG</sub>   | Discard Page Hold Time for the Control Logic       | 0.00  | 0.00  | 0.00  | ns    |

| tsuoverwrpro               | Overwrite Protect Setup Time for the Control Logic | 1.64  | 1.86  | 2.19  | ns    |

| t <sub>HDOVERWRPRO</sub>   | Overwrite Protect Hold Time for the Control Logic  | 0.00  | 0.00  | 0.00  | ns    |

Table 2-25 • Flash Memory Block Timing (continued)

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                  | Description                                                            | -2     | -1    | Std.  | Units |

|----------------------------|------------------------------------------------------------------------|--------|-------|-------|-------|

| tsupglosspro               | Page Loss Protect Setup Time for the Control Logic                     | 1.69   | 1.93  | 2.27  | ns    |

| t <sub>HDPGLOSSPRO</sub>   | Page Loss Protect Hold Time for the Control Logic                      | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SUPGSTAT</sub>      | Page Status Setup Time for the Control Logic                           | 2.49   | 2.83  | 3.33  | ns    |

| t <sub>HDPGSTAT</sub>      | Page Status Hold Time for the Control Logic                            | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SUOVERWRPG</sub>    | Over Write Page Setup Time for the Control Logic                       | 1.88   | 2.14  | 2.52  | ns    |

| t <sub>HDOVERWRPG</sub>    | Over Write Page Hold Time for the Control Logic                        | 0.00   | 0.00  | 0.00  | ns    |

| tsulockrequest             | Lock Request Setup Time for the Control Logic                          |        | 0.99  | 1.16  | ns    |

| t <sub>HDLOCKREQUEST</sub> | Lock Request Hold Time for the Control Logic                           | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>RECARNVM</sub>      | Reset Recovery Time                                                    | 0.94   | 1.07  | 1.25  | ns    |

| t <sub>REMARNVM</sub>      | Reset Removal Time                                                     | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>MPWARNVM</sub>      | Asynchronous Reset Minimum Pulse Width for the Control Logic           | 10.00  | 12.50 | 12.50 | ns    |

| t <sub>MPWCLKNVM</sub>     | Clock Minimum Pulse Width for the Control Logic                        | 4.00   | 5.00  | 5.00  | ns    |

| +                          | Maximum Frequency for Clock for the Control Logic – for AFS1500/AFS600 | 80.00  | 80.00 | 80.00 | MHz   |

| <sup>T</sup> FMAXCLKNVM    | Maximum Frequency for Clock for the Control Logic – for AFS250/AFS090  | 100.00 | 80.00 | 80.00 | MHz   |

## **FlashROM**

Fusion devices have 1 kbit of on-chip nonvolatile flash memory that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core (Figure 2-45).

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports a synchronous read and can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank that is being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

The maximum FlashROM access clock is given in Table 2-26 on page 2-54. Figure 2-46 shows the timing behavior of the FlashROM access cycle—the address has to be set up on the rising edge of the clock for DOUT to be valid on the next falling edge of the clock.

If the address is unchanged for two cycles:

- D0 becomes invalid t<sub>CK2Q</sub> ns after the second rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the second falling edge.

If the address unchanged for three cycles:

- D0 becomes invalid t<sub>CK2O</sub> ns after the second rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the second falling edge.

- D0 becomes invalid t<sub>CK2Q</sub> ns after the third rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the third falling edge.

2-53 Revision 6

# FIFO Characteristics

# **Timing Waveforms**

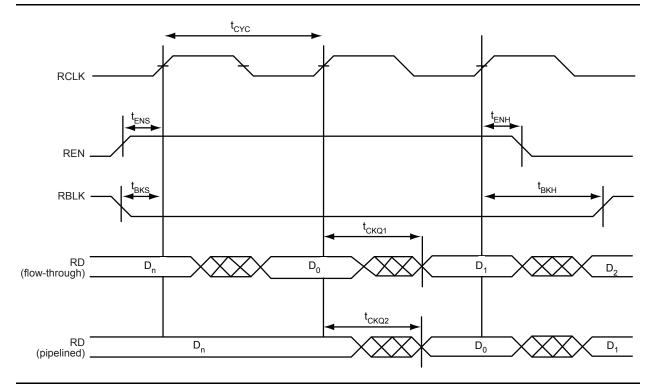

Figure 2-57 • FIFO Read

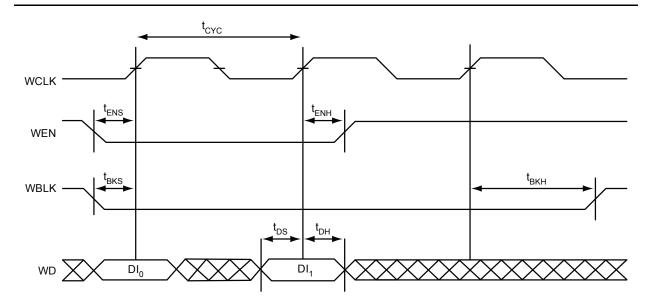

Figure 2-58 • FIFO Write

Table 2-36 • Analog Block Pin Description (continued)

| Signal Name     | Number of Bits | Direction | Function                                                  | Location of<br>Details |

|-----------------|----------------|-----------|-----------------------------------------------------------|------------------------|

| AG6             | 1              | Output    |                                                           | Analog Quad            |

| AT6             | 1              | Input     |                                                           | Analog Quad            |

| ATRETURN67      | 1              | Input     | Temperature monitor return shared by Analog Quads 6 and 7 | Analog Quad            |

| AV7             | 1              | Input     | Analog Quad 7                                             | Analog Quad            |

| AC7             | 1              | Input     |                                                           | Analog Quad            |

| AG7             | 1              | Output    |                                                           | Analog Quad            |

| AT7             | 1              | Input     |                                                           | Analog Quad            |

| AV8             | 1              | Input     | Analog Quad 8                                             | Analog Quad            |

| AC8             | 1              | Input     |                                                           | Analog Quad            |

| AG8             | 1              | Output    |                                                           | Analog Quad            |

| AT8             | 1              | Input     |                                                           | Analog Quad            |

| ATRETURN89      | 1              | Input     | Temperature monitor return shared by Analog Quads 8 and 9 | Analog Quad            |

| AV9             | 1              | Input     | Analog Quad 9                                             | Analog Quad            |

| AC9             | 1              | Input     |                                                           | Analog Quad            |

| AG9             | 1              | Output    |                                                           | Analog Quad            |

| AT9             | 1              | Input     |                                                           | Analog Quad            |

| RTCMATCH        | 1              | Output    | MATCH                                                     | RTC                    |

| RTCPSMMATCH     | 1              | Output    | MATCH connected to VRPSM                                  | RTC                    |

| RTCXTLMODE[1:0] | 2              | Output    | Drives XTLOSC RTCMODE[1:0] pins                           | RTC                    |

| RTCXTLSEL       | 1              | Output    | Drives XTLOSC MODESEL pin                                 | RTC                    |

| RTCCLK          | 1              | Input     | RTC clock input                                           | RTC                    |

# **Analog Quad**

With the Fusion family, Microsemi introduces the Analog Quad, shown in Figure 2-65 on page 2-81, as the basic analog I/O structure. The Analog Quad is a four-channel system used to precondition a set of analog signals before sending it to the ADC for conversion into a digital signal. To maximize the usefulness of the Analog Quad, the analog input signals can also be configured as LVTTL digital input signals. The Analog Quad is divided into four sections.

The first section is called the Voltage Monitor Block, and its input pin is named AV. It contains a two-channel analog multiplexer that allows an incoming analog signal to be routed directly to the ADC or allows the signal to be routed to a prescaler circuit before being sent to the ADC. The prescaler can be configured to accept analog signals between –12 V and 0 or between 0 and +12 V. The prescaler circuit scales the voltage applied to the ADC input pad such that it is compatible with the ADC input voltage range. The AV pin can also be used as a digital input pin.

The second section of the Analog Quad is called the Current Monitor Block. Its input pin is named AC. The Current Monitor Block contains all the same functions as the Voltage Monitor Block with one addition, which is a current monitoring function. A small external current sensing resistor (typically less than 1  $\Omega$ ) is connected between the AV and AC pins and is in series with a power source. The Current Monitor Block contains a current monitor circuit that converts the current through the external resistor to a voltage that can then be read using the ADC.

# **5 V Output Tolerance**

Fusion I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, Fusion I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceed the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level '1' and level '0' will be recognized correctly by 5 V TTL receivers.

# Simultaneously Switching Outputs and PCB Layout

- Simultaneously switching outputs (SSOs) can produce signal integrity problems on adjacent signals that are not part of the SSO bus. Both inductive and capacitive coupling parasitics of bond wires inside packages and of traces on PCBs will transfer noise from SSO busses onto signals adjacent to those busses. Additionally, SSOs can produce ground bounce noise and VCCI dip noise. These two noise types are caused by rapidly changing currents through GND and VCCI package pin inductances during switching activities:

- Ground bounce noise voltage = L(GND) \* di/dt

- VCCI dip noise voltage = L(VCCI) \* di/dt

Any group of four or more input pins switching on the same clock edge is considered an SSO bus. The shielding should be done both on the board and inside the package unless otherwise described.

In-package shielding can be achieved in several ways; the required shielding will vary depending on whether pins next to SSO bus are LVTTL/LVCMOS inputs, LVTTL/LVCMOS outputs, or GTL/SSTL/HSTL/LVDS/LVPECL inputs and outputs. Board traces in the vicinity of the SSO bus have to be adequately shielded from mutual coupling and inductive noise that can be generated by the SSO bus. Also, noise generated by the SSO bus needs to be reduced inside the package.

PCBs perform an important function in feeding stable supply voltages to the IC and, at the same time, maintaining signal integrity between devices.

Key issues that need to considered are as follows:

- Power and ground plane design and decoupling network design

- · Transmission line reflections and terminations

Figure 2-112 • Timing Diagram (with skew circuit selected)

# Weak Pull-Up and Weak Pull-Down Resistors

Fusion devices support optional weak pull-up and pull-down resistors for each I/O pin. When the I/O is pulled up, it is connected to the VCCI of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to Table 2-97 on page 2-171 for more information.

# **Slew Rate Control and Drive Strength**

Fusion devices support output slew rate control: high and low. The high slew rate option is recommended to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected. Drive strength should also be selected according to the design requirements and noise immunity of the system.

The output slew rate and multiple drive strength controls are available in LVTTL/LVCMOS  $3.3\,V$ , LVCMOS  $2.5\,V$ , LVCMOS  $2.5\,V$ , LVCMOS  $2.5\,V$ ,  $2.5\,V$ , and LVCMOS  $2.5\,V$ , and LVCMOS  $2.5\,V$ . All other I/O standards have a high output slew rate by default.

For Fusion slew rate and drive strength specifications, refer to the appropriate I/O bank table:

- Fusion Standard I/O (Table 2-78 on page 2-152)

- Fusion Advanced I/O (Table 2-79 on page 2-152)

- Fusion Pro I/O (Table 2-80 on page 2-152)

Table 2-83 on page 2-155 lists the default values for the above selectable I/O attributes as well as those that are preset for each I/O standard.

Refer to Table 2-78, Table 2-79, and Table 2-80 on page 2-152 for SLEW and OUT\_DRIVE settings. Table 2-81 on page 2-153 and Table 2-82 on page 2-154 list the I/O default attributes. Table 2-83 on page 2-155 lists the voltages for the supported I/O standards.

2-151 Revision 6

Table 2-83 • Fusion Pro I/O Supported Standards and Corresponding VREF and VTT Voltages

| I/O Standard               | Input/Output Supply<br>Voltage (VCCI_TYP) | Input Reference Voltage<br>(VREF_TYP) | Board Termination Voltage (VTT_TYP) |

|----------------------------|-------------------------------------------|---------------------------------------|-------------------------------------|

| LVTTL/LVCMOS 3.3 V         | 3.30 V                                    | -                                     | -                                   |

| LVCMOS 2.5 V               | 2.50 V                                    | -                                     | -                                   |

| LVCMOS 2.5 V / 5.0 V Input | 2.50 V                                    | -                                     | -                                   |

| LVCMOS 1.8 V               | 1.80 V                                    | -                                     | -                                   |

| LVCMOS 1.5 V               | 1.50 V                                    | -                                     | _                                   |

| PCI 3.3 V                  | 3.30 V                                    | -                                     | -                                   |

| PCI-X 3.3 V                | 3.30 V                                    | -                                     | -                                   |

| GTL+ 3.3 V                 | 3.30 V                                    | 1.00 V                                | 1.50 V                              |

| GTL+ 2.5 V                 | 2.50 V                                    | 1.00 V                                | 1.50 V                              |

| GTL 3.3 V                  | 3.30 V                                    | 0.80 V                                | 1.20 V                              |

| GTL 2.5 V                  | 2.50 V                                    | 0.80 V                                | 1.20 V                              |

| HSTL Class I               | 1.50 V                                    | 0.75 V                                | 0.75 V                              |

| HSTL Class II              | 1.50 V                                    | 0.75 V                                | 0.75 V                              |

| SSTL3 Class I              | 3.30 V                                    | 1.50 V                                | 1.50 V                              |

| SSTL3 Class II             | 3.30 V                                    | 1.50 V                                | 1.50 V                              |

| SSTL2 Class I              | 2.50 V                                    | 1.25 V                                | 1.25 V                              |

| SSTL2 Class II             | 2.50 V                                    | 1.25 V                                | 1.25 V                              |

| LVDS, BLVDS, M-LVDS        | 2.50 V                                    | -                                     | _                                   |

| LVPECL                     | 3.30 V                                    | -                                     | _                                   |

2-155 Revision 6

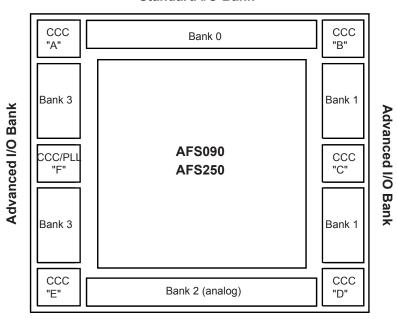

# **User I/O Naming Convention**

Due to the comprehensive and flexible nature of Fusion device user I/Os, a naming scheme is used to show the details of the I/O (Figure 2-113 on page 2-158 and Figure 2-114 on page 2-159). The name identifies to which I/O bank it belongs, as well as the pairing and pin polarity for differential I/Os.

I/O Nomenclature = Gmn/IOuxwByVz

Gmn is only used for I/Os that also have CCC access—i.e., global pins.

- G = Global

- m = Global pin location associated with each CCC on the device: A (northwest corner), B (northeast corner), C (east middle), D (southeast corner), E (southwest corner), and F (west middle).

- n = Global input MUX and pin number of the associated Global location m, either A0, A1, A2, B0, B1, B2, C0, C1, or C2. Figure 2-22 on page 2-25 shows the three input pins per clock source MUX at CCC location m.

- u = I/O pair number in the bank, starting at 00 from the northwest I/O bank and proceeding in a clockwise direction.

- x = P (Positive) or N (Negative) for differential pairs, or R (Regular single-ended) for the I/Os that support single-ended and voltage-referenced I/O standards only. U (Positive-LVDS only) or V (Negative-LVDS only) restrict the I/O differential pair from being selected as an LVPECL pair.

- w = D (Differential Pair), P (Pair), or S (Single-Ended). D (Differential Pair) if both members of the pair are bonded out to adjacent pins or are separated only by one GND or NC pin; P (Pair) if both members of the pair are bonded out but do not meet the adjacency requirement; or S (Single-Ended) if the I/O pair is not bonded out. For Differential (D) pairs, adjacency for ball grid packages means only vertical or horizontal. Diagonal adjacency does not meet the requirements for a true differential pair.

- B = Bank

- y = Bank number (0-3). The Bank number starts at 0 from the northwest I/O bank and proceeds in a clockwise direction.

- V = Reference voltage

- z = Minibank number

#### Standard I/O Bank

**Analog Quads**

Figure 2-113 • Naming Conventions of Fusion Devices with Three Digital I/O Banks

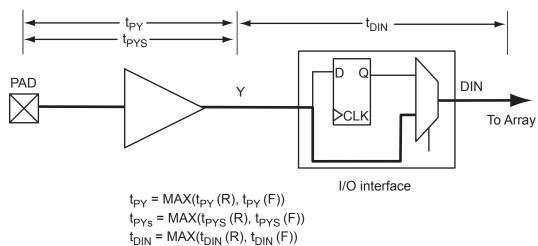

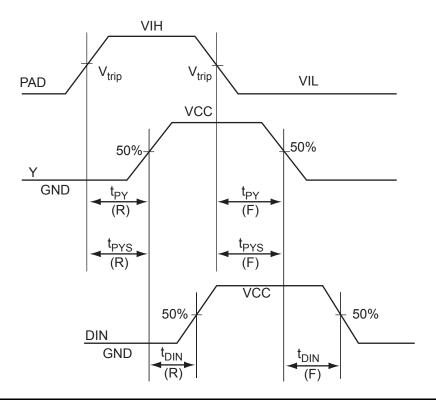

Figure 2-116 • Input Buffer Timing Model and Delays (example)

2-161 Revision 6

# Detailed I/O DC Characteristics

Table 2-95 • Input Capacitance

| Symbol             | Definition                         | Conditions           | Min. | Max. | Units |

|--------------------|------------------------------------|----------------------|------|------|-------|

| C <sub>IN</sub>    | Input capacitance                  | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

| C <sub>INCLK</sub> | Input capacitance on the clock pin | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

# Table 2-96 • I/O Output Buffer Maximum Resistances 1

| Standard                    | Drive Strength              | R <sub>PULL-DOWN</sub><br>(ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|-----------------------------|-----------------------------|-----------------------------------------------|---------------------------------------------|

| Applicable to Pro I/O Banks | 1                           |                                               |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS  | 4 mA                        | 100                                           | 300                                         |

|                             | 8 mA                        | 50                                            | 150                                         |

|                             | 12 mA                       | 25                                            | 75                                          |

|                             | 16 mA                       | 17                                            | 50                                          |

|                             | 24 mA                       | 11                                            | 33                                          |

| 2.5 V LVCMOS                | 4 mA                        | 100                                           | 200                                         |

|                             | 8 mA                        | 50                                            | 100                                         |

|                             | 12 mA                       | 25                                            | 50                                          |

|                             | 16 mA                       | 20                                            | 40                                          |

|                             | 24 mA                       | 11                                            | 22                                          |

| 1.8 V LVCMOS                | 2 mA                        | 200                                           | 225                                         |

|                             | 4 mA                        | 100                                           | 112                                         |

|                             | 6 mA                        | 50                                            | 56                                          |

|                             | 8 mA                        | 50                                            | 56                                          |

|                             | 12 mA                       | 20                                            | 22                                          |

|                             | 16 mA                       | 20                                            | 22                                          |

| 1.5 V LVCMOS                | 2 mA                        | 200                                           | 224                                         |

|                             | 4 mA                        | 100                                           | 112                                         |

|                             | 6 mA                        | 67                                            | 75                                          |

|                             | 8 mA                        | 33                                            | 37                                          |

|                             | 12 mA                       | 33                                            | 37                                          |

| 3.3 V PCI/PCI-X             | Per PCI/PCI-X specification | 25                                            | 75                                          |

| 3.3 V GTL                   | 20 mA                       | 11                                            | -                                           |

| 2.5 V GTL                   | 20 mA                       | 14                                            | -                                           |

| 3.3 V GTL+                  | 35 mA                       | 12                                            | -                                           |

| 2.5 V GTL+                  | 33 mA                       | 15                                            | _                                           |

#### Notes:

2-169 Revision 6

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

<sup>2.</sup>  $R_{(PULL-DOWN-MAX)} = VOLspec / I_{OLspec}$

<sup>3.</sup> R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

## **Timing Characteristics**

Table 2-128 • 1.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 14.11           | 0.04             | 1.70            | 2.14             | 0.43              | 14.37           | 13.14           | 3.40            | 2.68            | 16.61            | 15.37            | ns    |

|                   | -1             | 0.56              | 12.00           | 0.04             | 1.44            | 1.82             | 0.36              | 12.22           | 11.17           | 2.90            | 2.28            | 14.13            | 13.08            | ns    |

|                   | -2             | 0.49              | 10.54           | 0.03             | 1.27            | 1.60             | 0.32              | 10.73           | 9.81            | 2.54            | 2.00            | 12.40            | 11.48            | ns    |

| 4 mA              | Std.           | 0.66              | 11.23           | 0.04             | 1.70            | 2.14             | 0.43              | 11.44           | 9.87            | 3.77            | 3.36            | 13.68            | 12.10            | ns    |

|                   | -1             | 0.56              | 9.55            | 0.04             | 1.44            | 1.82             | 0.36              | 9.73            | 8.39            | 3.21            | 2.86            | 11.63            | 10.29            | ns    |

|                   | -2             | 0.49              | 8.39            | 0.03             | 1.27            | 1.60             | 0.32              | 8.54            | 7.37            | 2.81            | 2.51            | 10.21            | 9.04             | ns    |

| 8 mA              | Std.           | 0.66              | 10.45           | 0.04             | 1.70            | 2.14             | 0.43              | 10.65           | 9.24            | 3.84            | 3.55            | 12.88            | 11.48            | ns    |

|                   | -1             | 0.56              | 8.89            | 0.04             | 1.44            | 1.82             | 0.36              | 9.06            | 7.86            | 3.27            | 3.02            | 10.96            | 9.76             | ns    |

|                   | -2             | 0.49              | 7.81            | 0.03             | 1.27            | 1.60             | 0.32              | 7.95            | 6.90            | 2.87            | 2.65            | 9.62             | 8.57             | ns    |

| 12 mA             | Std.           | 0.66              | 10.02           | 0.04             | 1.70            | 2.14             | 0.43              | 10.20           | 9.23            | 3.97            | 4.22            | 12.44            | 11.47            | ns    |

|                   | -1             | 0.56              | 8.52            | 0.04             | 1.44            | 1.82             | 0.36              | 8.68            | 7.85            | 3.38            | 3.59            | 10.58            | 9.75             | ns    |

|                   | -2             | 0.49              | 7.48            | 0.03             | 1.27            | 1.60             | 0.32              | 7.62            | 6.89            | 2.97            | 3.15            | 9.29             | 8.56             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-129 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOU</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 8.53            | 0.04             | 1.70            | 2.14             | 0.43             | 7.26            | 8.53            | 3.39            | 2.79            | 9.50             | 10.77            | ns    |

|                   | <b>–</b> 1     | 0.56              | 7.26            | 0.04             | 1.44            | 1.82             | 0.36             | 6.18            | 7.26            | 2.89            | 2.37            | 8.08             | 9.16             | ns    |

|                   | -2             | 0.49              | 6.37            | 0.03             | 1.27            | 1.60             | 0.32             | 5.42            | 6.37            | 2.53            | 2.08            | 7.09             | 8.04             | ns    |

| 4 mA              | Std.           | 0.66              | 5.41            | 0.04             | 1.70            | 2.14             | 0.43             | 5.22            | 5.41            | 3.75            | 3.48            | 7.45             | 7.65             | ns    |

|                   | <b>–</b> 1     | 0.56              | 4.60            | 0.04             | 1.44            | 1.82             | 0.36             | 4.44            | 4.60            | 3.19            | 2.96            | 6.34             | 6.50             | ns    |

|                   | -2             | 0.49              | 4.04            | 0.03             | 1.27            | 1.60             | 0.32             | 3.89            | 4.04            | 2.80            | 2.60            | 5.56             | 5.71             | ns    |

| 8 mA              | Std.           | 0.66              | 4.80            | 0.04             | 1.70            | 2.14             | 0.43             | 4.89            | 4.75            | 3.83            | 3.67            | 7.13             | 6.98             | ns    |

|                   | <b>–</b> 1     | 0.56              | 4.09            | 0.04             | 1.44            | 1.82             | 0.36             | 4.16            | 4.04            | 3.26            | 3.12            | 6.06             | 5.94             | ns    |

|                   | -2             | 0.49              | 3.59            | 0.03             | 1.27            | 1.60             | 0.32             | 3.65            | 3.54            | 2.86            | 2.74            | 5.32             | 5.21             | ns    |

| 12 mA             | Std.           | 0.66              | 4.42            | 0.04             | 1.70            | 2.14             | 0.43             | 4.50            | 3.62            | 3.96            | 4.37            | 6.74             | 5.86             | ns    |

|                   | <b>–</b> 1     | 0.56              | 3.76            | 0.04             | 1.44            | 1.82             | 0.36             | 3.83            | 3.08            | 3.37            | 3.72            | 5.73             | 4.98             | ns    |

|                   | -2             | 0.49              | 3.30            | 0.03             | 1.27            | 1.60             | 0.32             | 3.36            | 2.70            | 2.96            | 3.27            | 5.03             | 4.37             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-130 • 1.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 1.4 V

Applicable to Advanced I/Os

| Daire             | 0              |                   |                 |                  |                 |                   |                 |                 |          |                 |                  |                  |       |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|----------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | $t_{LZ}$ | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

| 2 mA              | Std.           | 0.66              | 12.78           | 0.04             | 1.31            | 0.43              | 12.81           | 12.78           | 3.40     | 2.64            | 15.05            | 15.02            | ns    |

|                   | <b>–</b> 1     | 0.56              | 10.87           | 0.04             | 1.11            | 0.36              | 10.90           | 10.87           | 2.89     | 2.25            | 12.80            | 12.78            | ns    |

|                   | -2             | 0.49              | 9.55            | 0.03             | 0.98            | 0.32              | 9.57            | 9.55            | 2.54     | 1.97            | 11.24            | 11.22            | ns    |

| 4 mA              | Std.           | 0.66              | 10.01           | 0.04             | 1.31            | 0.43              | 10.19           | 9.55            | 3.75     | 3.27            | 12.43            | 11.78            | ns    |

|                   | <b>–</b> 1     | 0.56              | 8.51            | 0.04             | 1.11            | 0.36              | 8.67            | 8.12            | 3.19     | 2.78            | 10.57            | 10.02            | ns    |

|                   | -2             | 0.49              | 7.47            | 0.03             | 0.98            | 0.32              | 7.61            | 7.13            | 2.80     | 2.44            | 9.28             | 8.80             | ns    |

| 8 mA              | Std.           | 0.66              | 9.33            | 0.04             | 1.31            | 0.43              | 9.51            | 8.89            | 3.83     | 3.43            | 11.74            | 11.13            | ns    |

|                   | <b>–</b> 1     | 0.56              | 7.94            | 0.04             | 1.11            | 0.36              | 8.09            | 7.56            | 3.26     | 2.92            | 9.99             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.97            | 0.03             | 0.98            | 0.32              | 7.10            | 6.64            | 2.86     | 2.56            | 8.77             | 8.31             | ns    |

| 12 mA             | Std.           | 0.66              | 8.91            | 0.04             | 1.31            | 0.43              | 9.07            | 8.89            | 3.95     | 4.05            | 11.31            | 11.13            | ns    |

|                   | <b>–</b> 1     | 0.56              | 7.58            | 0.04             | 1.11            | 0.36              | 7.72            | 7.57            | 3.36     | 3.44            | 9.62             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.65            | 0.03             | 0.98            | 0.32              | 6.78            | 6.64            | 2.95     | 3.02            | 8.45             | 8.31             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-131 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 8.36            | 0.04             | 1.44            | 0.43              | 6.82            | 8.36            | 3.39            | 2.77            | 9.06             | 10.60            | ns    |

|                   | -1             | 0.56              | 7.11            | 0.04             | 1.22            | 0.36              | 5.80            | 7.11            | 2.88            | 2.35            | 7.71             | 9.02             | ns    |

|                   | -2             | 0.49              | 6.24            | 0.03             | 1.07            | 0.32              | 5.10            | 6.24            | 2.53            | 2.06            | 6.76             | 7.91             | ns    |

| 4 mA              | Std.           | 0.66              | 5.31            | 0.04             | 1.44            | 0.43              | 4.85            | 5.31            | 3.74            | 3.40            | 7.09             | 7.55             | ns    |

|                   | -1             | 0.56              | 4.52            | 0.04             | 1.22            | 0.36              | 4.13            | 4.52            | 3.18            | 2.89            | 6.03             | 6.42             | ns    |

|                   | -2             | 0.49              | 3.97            | 0.03             | 1.07            | 0.32              | 3.62            | 3.97            | 2.79            | 2.54            | 5.29             | 5.64             | ns    |

| 8 mA              | Std.           | 0.66              | 4.67            | 0.04             | 1.44            | 0.43              | 4.55            | 4.67            | 3.82            | 3.56            | 6.78             | 6.90             | ns    |

|                   | -1             | 0.56              | 3.97            | 0.04             | 1.22            | 0.36              | 3.87            | 3.97            | 3.25            | 3.03            | 5.77             | 5.87             | ns    |

|                   | -2             | 0.49              | 3.49            | 0.03             | 1.07            | 0.32              | 3.40            | 3.49            | 2.85            | 2.66            | 5.07             | 5.16             | ns    |

| 12 mA             | Std.           | 0.66              | 4.08            | 0.04             | 1.44            | 0.43              | 4.15            | 3.58            | 3.94            | 4.20            | 6.39             | 5.81             | ns    |

|                   | -1             | 0.56              | 3.47            | 0.04             | 1.22            | 0.36              | 3.53            | 3.04            | 3.36            | 3.58            | 5.44             | 4.95             | ns    |

|                   | -2             | 0.49              | 3.05            | 0.03             | 1.07            | 0.32              | 3.10            | 2.67            | 2.95            | 3.14            | 4.77             | 4.34             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-195 Revision 6

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

#### TRST Boundary Scan Reset Pin

The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the TAP is held in reset mode. The resistor values must be chosen from Table 2-183 and must satisfy the parallel resistance value requirement. The values in Table 2-183 correspond to the resistor recommended when a single device is used and to the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entering an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

# **Special Function Pins**

#### NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC Don't Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

#### NCAP Negative Capacitor

Negative Capacitor is where the negative terminal of the charge pump capacitor is connected. A capacitor, with a  $2.2 \, \mu F$  recommended value, is required to connect between PCAP and NCAP.

#### PCAP Positive Capacitor

Positive Capacitor is where the positive terminal of the charge pump capacitor is connected. A capacitor, with a 2.2 µF recommended value, is required to connect between PCAP and NCAP.

#### PUB Push Button

*Push button* is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.

#### PTBASE Pass Transistor Base

Pass Transistor Base is the control signal of the voltage regulator. This pin should be connected to the base of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

#### PTEM Pass Transistor Emitter

Pass Transistor Emitter is the feedback input of the voltage regulator.

This pin should be connected to the emitter of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

# XTAL1 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

2-227 Revision 6

Table 3-5 • FPGA Programming, Storage, and Operating Limits

| Product<br>Grade | Storage<br>Temperature      | Element        | Grade Programming Cycles | Retention |

|------------------|-----------------------------|----------------|--------------------------|-----------|

| Commercial       | Min. T <sub>J</sub> = 0°C   | FPGA/FlashROM  | 500                      | 20 years  |

|                  | Max. T <sub>J</sub> = 85°C  | Embedded Flash | < 1,000                  | 20 years  |

|                  |                             |                | < 10,000                 | 10 years  |

|                  |                             |                | < 15,000                 | 5 years   |

| Industrial       | Min. $T_J = -40$ °C         | FPGA/FlashROM  | 500                      | 20 years  |

|                  | Max. T <sub>J</sub> = 100°C | Embedded Flash | < 1,000                  | 20 years  |

|                  |                             |                | < 10,000                 | 10 years  |

|                  |                             |                | < 15,000                 | 5 years   |

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every Fusion device. These circuits ensure easy transition from the powered off state to the powered up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 3-1 on page 3-6.

There are five regions to consider during power-up.

Fusion I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 3-1).

- 2. VCCI > VCC 0.75 V (typical).

- 3. Chip is in the operating mode.

#### **V<sub>CCI</sub>** Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.2 V Ramping down: 0.5 V < trip\_point\_down < 1.1 V

**V<sub>CC</sub>** Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.1 V Ramping down: 0.5 V < trip\_point\_down < 1 V

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

## Internal Power-Up Activation Sequence

- 1. Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

#### PLL Behavior at Brownout Condition

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper power-up behavior. Power ramp-up should be monotonic at least until VCC and VCCPLX exceed brownout activation levels. The  $V_{CC}$  activation level is specified as 1.1 V worst-case (see Figure 3-1 on page 3-6 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels  $(0.75~V\pm0.25~V)$ , the PLL output lock signal goes low and/or the output clock is lost.

3-5 Revision 6

Table 3-13 • Summary of I/O Output Buffer Power (per pin)—Default I/O Software Settings<sup>1</sup>

|                                | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power PDC8 (mW) <sup>2</sup> | Dynamic Power PAC10 (µW/MHz) <sup>3</sup> |

|--------------------------------|------------------------|----------|-------------------------------------|-------------------------------------------|

| Applicable to Pro I/O Banks    |                        |          | · ·                                 | l                                         |

| Single-Ended                   |                        |          |                                     |                                           |

| 3.3 V LVTTL/LVCMOS             | 35                     | 3.3      | _                                   | 474.70                                    |

| 2.5 V LVCMOS                   | 35                     | 2.5      | -                                   | 270.73                                    |

| 1.8 V LVCMOS                   | 35                     | 1.8      | -                                   | 151.78                                    |

| 1.5 V LVCMOS (JESD8-11)        | 35                     | 1.5      | -                                   | 104.55                                    |

| 3.3 V PCI                      | 10                     | 3.3      | -                                   | 204.61                                    |

| 3.3 V PCI-X                    | 10                     | 3.3      | -                                   | 204.61                                    |

| Voltage-Referenced             |                        |          | •                                   | •                                         |

| 3.3 V GTL                      | 10                     | 3.3      | -                                   | 24.08                                     |

| 2.5 V GTL                      | 10                     | 2.5      | -                                   | 13.52                                     |

| 3.3 V GTL+                     | 10                     | 3.3      | -                                   | 24.10                                     |

| 2.5 V GTL+                     | 10                     | 2.5      | -                                   | 13.54                                     |

| HSTL (I)                       | 20                     | 1.5      | 7.08                                | 26.22                                     |

| HSTL (II)                      | 20                     | 1.5      | 13.88                               | 27.22                                     |

| SSTL2 (I)                      | 30                     | 2.5      | 16.69                               | 105.56                                    |

| SSTL2 (II)                     | 30                     | 2.5      | 25.91                               | 116.60                                    |

| SSTL3 (I)                      | 30                     | 3.3      | 26.02                               | 114.87                                    |

| SSTL3 (II)                     | 30                     | 3.3      | 42.21                               | 131.76                                    |

| Differential                   |                        |          | •                                   | •                                         |

| LVDS                           | -                      | 2.5      | 7.70                                | 89.62                                     |

| LVPECL                         | -                      | 3.3      | 19.42                               | 168.02                                    |

| Applicable to Advanced I/O Bar | nks                    |          |                                     |                                           |

| Single-Ended                   |                        |          |                                     |                                           |

| 3.3 V LVTTL / 3.3 V LVCMOS     | 35                     | 3.3      | -                                   | 468.67                                    |

| 2.5 V LVCMOS                   | 35                     | 2.5      | -                                   | 267.48                                    |

| 1.8 V LVCMOS                   | 35                     | 1.8      | -                                   | 149.46                                    |

| 1.5 V LVCMOS (JESD8-11)        | 35                     | 1.5      | -                                   | 103.12                                    |

| 3.3 V PCI                      | 10                     | 3.3      | -                                   | 201.02                                    |

| 3.3 V PCI-X                    | 10                     | 3.3      | -                                   | 201.02                                    |

## Notes: