Welcome to <u>E-XFL.COM</u>

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details |

|---------|

|---------|

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | 36864                                                         |

| Number of I/O                  | 93                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 208-BFQFP                                                     |

| Supplier Device Package        | 208-PQFP (28x28)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs250-2pq208i |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.5 V Voltage Regulator

The 1.5 V voltage regulator uses an external pass transistor to generate 1.5 V from a 3.3 V supply. The base of the pass transistor is tied to PTBASE, the collector is tied to 3.3 V, and an emitter is tied to PTBASE and the 1.5 V supplies of the Fusion device. Figure 2-27 on page 2-31 shows the hook-up of the 1.5 V voltage regulator to an external pass transistor.

Microsemi recommends using a PN2222A or 2N2222A transistor. The gain of such a transistor is approximately 25, with a maximum base current of 20 mA. The maximum current that can be supported is 0.5 A. Transistors with different gain can also be used for different current requirements.

# Table 2-18 • Electrical Characteristics

| Symbol  | Parameter         | Condition |                           | Min   | Typical | Max   | Units |

|---------|-------------------|-----------|---------------------------|-------|---------|-------|-------|

| VOUT    | Output Voltage    | Tj = 25°C |                           | 1.425 | 1.5     | 1.575 | V     |

| ICC33A  | Operation Current | Tj = 25⁰C | ILOAD = 1 mA              |       | 11      |       | mA    |

|         |                   |           | ILOAD = 100 mA            |       | 11      |       | mA    |

|         |                   |           | ILOAD = 0.5 A             |       | 30      |       | mA    |

| ∆VOUT   | Load Regulation   | Tj = 25°C | ILOAD = 1 mA to 0.5 A     |       | 90      |       | mV    |

|         | Line Regulation   | Tj = 25°C | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 1 mA              |       | 10.6    |       | mV/V  |

|         |                   |           | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 100 mA            |       | 12.1    |       | mV/V  |

| ∆VOUT   |                   |           | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 500 mA            |       | 10.6    |       | mV/V  |

|         | Dropout Voltage*  | Tj = 25⁰C | ILOAD = 1 mA              |       | 0.63    |       | V     |

|         |                   |           | ILOAD = 100 mA            |       | 0.84    |       | V     |

|         |                   |           | ILOAD = 0.5 A             |       | 1.35    |       | V     |

| IPTBASE | PTBase Current    | Tj = 25°C | ILOAD = 1 mA              |       | 48      |       | μA    |

|         |                   |           | ILOAD = 100 mA            |       | 736     |       | μA    |

|         |                   |           | ILOAD = 0.5 A             |       | 12      | 20    | mA    |

# VCC33A = 3.3 V

Note: \*Data collected with 2N2222A.

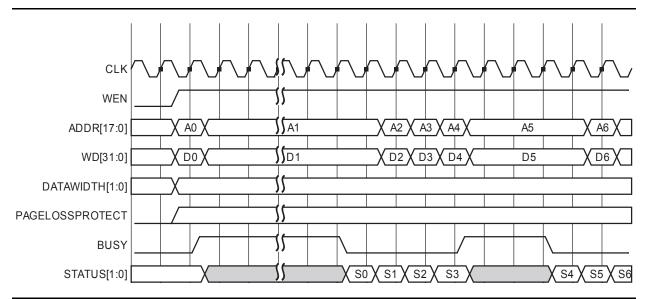

Access to the FB is controlled by the BUSY signal. The BUSY output is synchronous to the CLK signal. FB operations are only accepted in cycles where BUSY is logic 0.

### Write Operation

Write operations are initiated with the assertion of the WEN signal. Figure 2-35 on page 2-45 illustrates the multiple Write operations.

Figure 2-35 • FB Write Waveform

When a Write operation is initiated to a page that is currently not in the Page Buffer, the FB control logic will issue a BUSY signal to the user interface while the page is loaded from the FB Array into the Page Buffer. A Copy Page operation takes no less than 55 cycles and could take more if a Write or Unprotect Page operation is started while the NVM is busy pre-fetching a block. The basic operation is to read a block from the array into the block register (5 cycles) and then write the block register to the page buffer (1 cycle) and if necessary, when the copy is complete, reading the block being written from the page buffer into the block buffer (1 cycle). A page contains 9 blocks, so 9 blocks multiplied by 6 cycles to read/write each block, plus 1 is 55 cycles total. Subsequent writes to the same block of the page will incur no busy cycles. A write to another block in the page will assert BUSY for four cycles (five cycles when PIPE is asserted), to allow the data to be written to the Page Buffer and have the current block loaded into the Block Buffer.

Write operations are considered successful as long as the STATUS output is '00'. A non-zero STATUS indicates that an error was detected during the operation and the write was not performed. Note that the STATUS output is "sticky"; it is unchanged until another operation is started.

Only one word can be written at a time. Write word width is controlled by the DATAWIDTH bus. Users are responsible for keeping track of the contents of the Page Buffer and when to program it to the array. Just like a regular RAM, writing to random addresses is possible. Users can write into the Page Buffer in any order but will incur additional BUSY cycles. It is not necessary to modify the entire Page Buffer before saving it to nonvolatile memory.

Write errors include the following:

- 1. Attempting to write a page that is Overwrite Protected (STATUS = '01'). The write is not performed.

- 2. Attempting to write to a page that is not in the Page Buffer when Page Loss Protection is enabled (STATUS = '11'). The write is not performed.

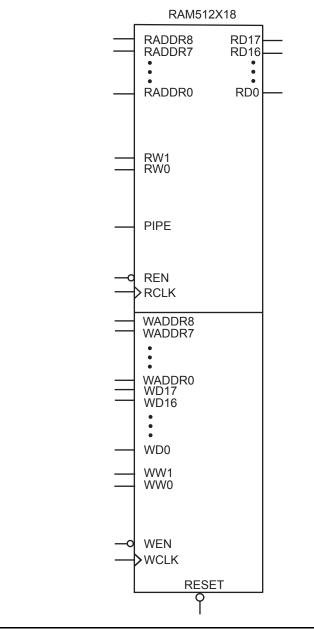

The following signals are used to configure the RAM4K9 memory element.

# WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 2-27).

| WIDTHA1, WIDTHA0                                                               | WIDTHB1, WIDTHB0 | D×W   |  |  |  |  |  |

|--------------------------------------------------------------------------------|------------------|-------|--|--|--|--|--|

| 00                                                                             | 00               | 4k×1  |  |  |  |  |  |

| 01                                                                             | 01               | 2k×2  |  |  |  |  |  |

| 10                                                                             | 10               | 1k×4  |  |  |  |  |  |

| 11                                                                             | 11               | 512×9 |  |  |  |  |  |

| Note: The aspect ratio settings are constant and cannot be changed on the fly. |                  |       |  |  |  |  |  |

# BLKA and BLKB

These signals are active low and will enable the respective ports when asserted. When a BLKx signal is deasserted, the corresponding port's outputs hold the previous value.

### WENA and WENB

These signals switch the RAM between read and write mode for the respective ports. A Low on these signals indicates a write operation, and a High indicates a read.

### CLKA and CLKB

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

# PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A Low on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A High indicates a pipelined, read and data appears on the corresponding output in the next clock cycle.

### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A Low on these signals makes the output retain data from the previous read. A High indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

#### RESET

This active low signal resets the output to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory.

### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 2-28).

#### Table 2-28 • Address Pins Unused/Used for Various Supported Bus Widths

| D×W   | ADDRx   |        |  |  |  |

|-------|---------|--------|--|--|--|

|       | Unused  | Used   |  |  |  |

| 4k×1  | None    | [11:0] |  |  |  |

| 2k×2  | [11]    | [10:0] |  |  |  |

| 1k×4  | [11:10] | [9:0]  |  |  |  |

| 512×9 | [11:9]  | [8:0]  |  |  |  |

Note: The "x" in ADDRx implies A or B.

# RAM512X18 Description

Figure 2-49 • RAM512X18

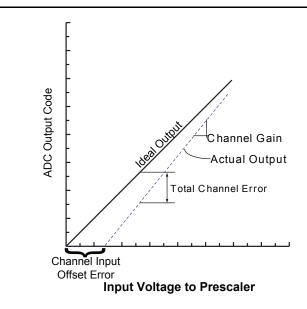

### Channel Input Offset Error

Channel Offset error is measured as the input voltage that causes the transition from zero to a count of one. An Ideal Prescaler will have offset equal to  $\frac{1}{2}$  of LSB voltage. Offset error is a positive or negative when the first transition point is higher or lower than ideal. Offset error is expressed in LSB or input voltage.

#### **Total Channel Error**

Total Channel Error is defined as the total error measured compared to the ideal value. Total Channel Error is the sum of gain error and offset error combined. Figure 2-68 shows how Total Channel Error is measured.

Total Channel Error is defined as the difference between the actual ADC output and ideal ADC output. In the example shown in Figure 2-68, the Total Channel Error would be a negative number.

Figure 2-68 • Total Channel Error Example

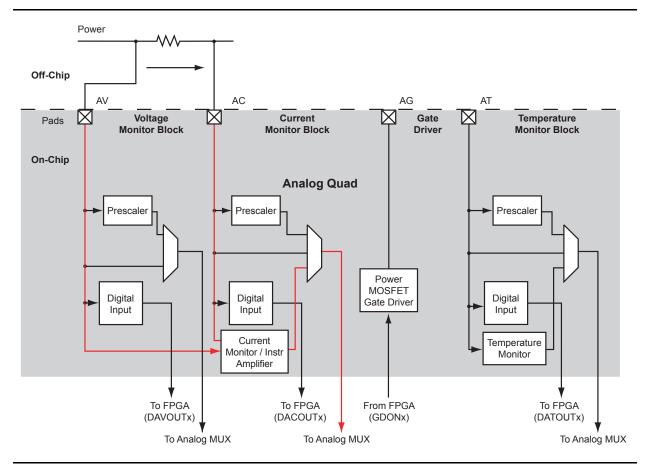

# **Current Monitor**

The Fusion Analog Quad is an excellent element for voltage- and current-monitoring applications. In addition to supporting the same functionality offered by the AV pad, the AC pad can be configured to monitor current across an external sense resistor (Figure 2-70). To support this current monitor function, a differential amplifier with 10x gain passes the amplified voltage drop between the AV and AC pads to the ADC. The amplifier enables the user to use very small resistor values, thereby limiting any impact on the circuit. This function of the AC pad does not limit AV pad operation. The AV pad can still be configured for use as a direct voltage input or scaled through the AV prescaler independently of it's use as an input to the AC pad's differential amplifier.

Figure 2-70 • Analog Quad Current Monitor Configuration

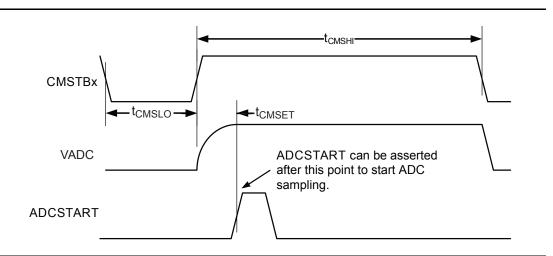

To initiate a current measurement, the appropriate Current Monitor Strobe (CMSTB) signal on the AB macro must be asserted low for at least  $t_{CMSLO}$  in order to discharge the previous measurement. Then CMSTB must be asserted high for at least  $t_{CMSET}$  prior to asserting the ADCSTART signal. The CMSTB must remain high until after the SAMPLE signal is de-asserted by the AB macro. Note that the minimum sample time cannot be less than  $t_{CMSHI}$ . Figure 2-71 shows the timing diagram of CMSTB in relationship with the ADC control signals.

Figure 2-71 • Timing Diagram for Current Monitor Strobe

Figure 2-72 illustrates positive current monitor operation. The differential voltage between AV and AC goes into the 10× amplifier and is then converted by the ADC. For example, a current of 1.5 A is drawn from a 10 V supply and is measured by the voltage drop across a 0.050  $\Omega$  sense resistor, The voltage drop is amplified by ten times by the amplifier and then measured by the ADC. The 1.5 A current creates a differential voltage across the sense resistor of 75 mV. This becomes 750 mV after amplification. Thus, the ADC measures a current of 1.5 A as 750 mV. Using an ADC with 8-bit resolution and VAREF of 2.56 V, the ADC result is decimal 75. EQ 3 shows how to compute the current from the ADC result.

$$||| = (ADC \times V_{AREF}) / (10 \times 2^{N} \times R_{sense})$$

EQ 3

where

I is the current flowing through the sense resistor

ADC is the result from the ADC

VAREF is the Reference voltage

N is the number of bits

Rsense is the resistance of the sense resistor

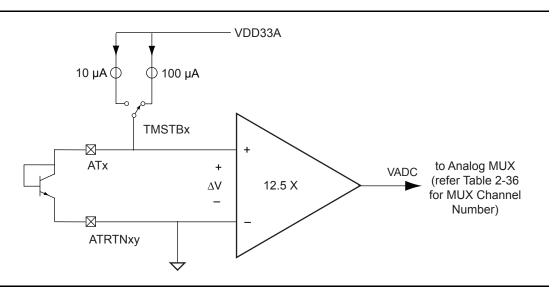

Fusion uses a remote diode as a temperature sensor. The Fusion Temperature Monitor uses a differential input; the AT pin and ATRTN (AT Return) pin are the differential inputs to the Temperature Monitor. There is one Temperature Monitor in each Quad. A simplified block diagram is shown in Figure 2-77.

Figure 2-77 • Block Diagram for Temperature Monitor Circuit

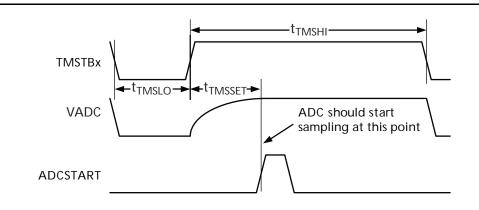

The Fusion approach to measuring temperature is forcing two different currents through the diode with a ratio of 10:1. The switch that controls the different currents is controlled by the Temperature Monitor Strobe signal, TMSTB. Setting TMSTB to '1' will initiate a Temperature reading. The TMSTB should remain '1' until the ADC finishes sampling the voltage from the Temperature Monitor. The minimum sample time for the Temperature Monitor cannot be less than the minimum strobe high time minus the setup time. Figure 2-78 shows the timing diagram.

Note: When the IEEE 1149.1 Boundary Scan EXTEST instruction is executed, the AG pad drive strength ceases and becomes a 1 µA sink into the Fusion device.

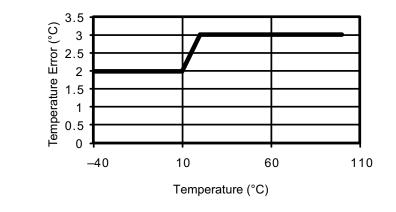

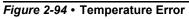

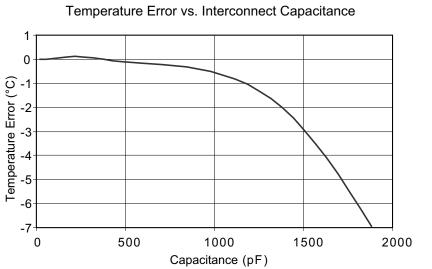

# **Typical Performance Characteristics**

Temperature Errror vs. Die Temperature

Figure 2-95 • Effect of External Sensor Capacitance

Figure 2-96 • Temperature Reading Noise When Averaging is Used

**Analog System Characteristics**

## Table 2-49 • Analog Channel Specifications

## Commercial Temperature Range Conditions, T<sub>J</sub> = 85°C (unless noted otherwise), Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter          | Description                            | Condition                                  | Min.                 | Тур. | Max.                                          | Units |

|--------------------|----------------------------------------|--------------------------------------------|----------------------|------|-----------------------------------------------|-------|

| Voltage Monit      | tor Using Analog Pads AV,              | AC and AT (using prescaler)                |                      |      | 1                                             |       |

|                    | Input Voltage<br>(Prescaler)           | Refer to Table 3-2 on page 3-3             |                      |      |                                               |       |

| VINAP              | Uncalibrated Gain and<br>Offset Errors | Refer to Table 2-51 on page 2-122          |                      |      |                                               |       |

|                    | Calibrated Gain and<br>Offset Errors   | Refer to Table 2-52 on page 2-123          |                      |      |                                               |       |

|                    | Bandwidth1                             |                                            |                      |      | 100                                           | KHz   |

|                    | Input Resistance                       | Refer to Table 3-3 on page 3-4             |                      |      |                                               |       |

|                    | Scaling Factor                         | Prescaler modes (Table 2-57 on page 2-130) |                      |      |                                               |       |

|                    | Sample Time                            |                                            | 10                   |      |                                               | μs    |

| Current Moni       | tor Using Analog Pads AV               | and AC                                     |                      |      |                                               |       |

| VRSM <sup>1</sup>  | Maximum Differential<br>Input Voltage  |                                            |                      |      | VAREF / 10                                    | mV    |

|                    | Resolution                             | Refer to "Current Monitor" section         |                      |      |                                               |       |

|                    | Common Mode Range                      |                                            |                      |      | - 10.5 to +12                                 | V     |

| CMRR               | Common Mode<br>Rejection Ratio         | DC – 1 KHz                                 |                      | 60   |                                               | dB    |

|                    |                                        | 1 KHz - 10 KHz                             |                      | 50   |                                               | dB    |

|                    |                                        | > 10 KHz                                   |                      | 30   |                                               | dB    |

| t <sub>CMSHI</sub> | Strobe High time                       |                                            | ADC<br>conv.<br>time |      | 200                                           | μs    |

| t <sub>CMSHI</sub> | Strobe Low time                        |                                            | 5                    |      |                                               | μs    |

| t <sub>CMSHI</sub> | Settling time                          |                                            | 0.02                 |      |                                               | μs    |

|                    | Accuracy                               | Input differential voltage > 50 mV         |                      |      | -2 -(0.05 x<br>VRSM) to +2 +<br>(0.05 x VRSM) | mV    |

Notes:

1. VRSM is the maximum voltage drop across the current sense resistor.

2. Analog inputs used as digital inputs can tolerate the same voltage limits as the corresponding analog pad. There is no reliability concern on digital inputs as long as VIND does not exceed these limits.

- 3. VIND is limited to VCC33A + 0.2 to allow reaching 10 MHz input frequency.

- 4. An averaging of 1,024 samples (LPF setting in Analog System Builder) is required and the maximum capacitance allowed across the AT pins is 500 pF.

- 5. The temperature offset is a fixed positive value.

- 6. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

- 7. When using SmartGen Analog System Builder, CalibIP is required to obtain specified offset. For further details on CalibIP, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

Fusion Family of Mixed Signal FPGAs

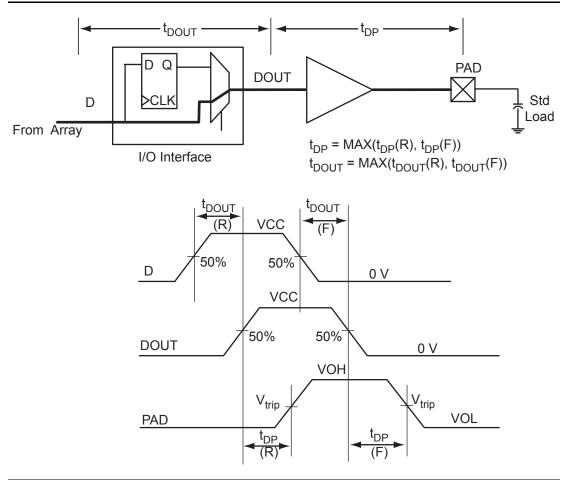

Figure 2-117 • Output Buffer Model and Delays (example)

Device Architecture

# Table 2-96 • I/O Output Buffer Maximum Resistances <sup>1</sup> (continued)

| Standard                         | Drive Strength | R <sub>PULL-DOWN</sub><br>(ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|----------------------------------|----------------|-----------------------------------------------|---------------------------------------------|

| Applicable to Standard I/O Banks |                |                                               |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA           | 100                                           | 300                                         |

|                                  | 4 mA           | 100                                           | 300                                         |

|                                  | 6 mA           | 50                                            | 150                                         |

|                                  | 8 mA           | 50                                            | 150                                         |

| 2.5 V LVCMOS                     | 2 mA           | 100                                           | 200                                         |

|                                  | 4 mA           | 100                                           | 200                                         |

|                                  | 6 mA           | 50                                            | 100                                         |

|                                  | 8 mA           | 50                                            | 100                                         |

| 1.8 V LVCMOS                     | 2 mA           | 200                                           | 225                                         |

|                                  | 4 mA           | 100                                           | 112                                         |

| 1.5 V LVCMOS                     | 2 mA           | 200                                           | 224                                         |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

2. R<sub>(PULL-DOWN-MAX)</sub> = VOLspec / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

#### Table 2-97 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

| vcci  | R <sub>(WEAK F</sub><br>(oh | PULL-UP)<br>ms) | R <sub>(WEAK PULL-DOWN)</sub> <sup>2</sup><br>(ohms) |       |  |

|-------|-----------------------------|-----------------|------------------------------------------------------|-------|--|

|       | Min.                        | Max.            | Min.                                                 | Max.  |  |

| 3.3 V | 10 k                        | 45 k            | 10 k                                                 | 45 k  |  |

| 2.5 V | 11 k                        | 55 k            | 12 k                                                 | 74 k  |  |

| 1.8 V | 18 k                        | 70 k            | 17 k                                                 | 110 k |  |

| 1.5 V | 19 k                        | 90 k            | 19 k                                                 | 140 k |  |

Notes:

R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>WEAK PULL-UP-MIN</sub>

R<sub>(WEAK PULL-DOWN-MAX)</sub> = VOLspec / I<sub>WEAK PULL-DOWN-MIN</sub>

Device Architecture

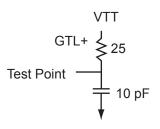

# 3.3 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-144 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL+        |           | VIL        | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 35 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | -         | 35  | 35 | 181                     | 268                     | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

### Figure 2-126 • AC Loading

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                  | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-146 • 3.3 V GTL+

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.06            | 0.04             | 1.59            | 0.43              | 2.09            | 2.06            |                 |                 | 4.33             | 4.29             | ns    |

| -1             | 0.56              | 1.75            | 0.04             | 1.35            | 0.36              | 1.78            | 1.75            |                 |                 | 3.68             | 3.65             | ns    |

| -2             | 0.49              | 1.53            | 0.03             | 1.19            | 0.32              | 1.56            | 1.53            |                 |                 | 3.23             | 3.20             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

# *Table 3-13* • Summary of I/O Output Buffer Power (per pin)—Default I/O Software Settings<sup>1</sup> (continued)

|                                | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC8 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup> |

|--------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Differential                   |                        |          | •                                      | •                                            |

| LVDS                           | -                      | 2.5      | 7.74                                   | 88.92                                        |

| LVPECL                         | -                      | 3.3      | 19.54                                  | 166.52                                       |

| Applicable to Standard I/O Ban | s                      |          |                                        |                                              |

| Single-Ended                   |                        |          |                                        |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS     | 35                     | 3.3      | -                                      | 431.08                                       |

| 2.5 V LVCMOS                   | 35                     | 2.5      | -                                      | 247.36                                       |

| 1.8 V LVCMOS                   | 35                     | 1.8      | _                                      | 128.46                                       |

| 1.5 V LVCMOS (JESD8-11)        | 35                     | 1.5      | -                                      | 89.46                                        |

Notes:

1. Dynamic power consumption is given for standard load and software-default drive strength and output slew.

2. PDC8 is the static power (where applicable) measured on VCCI.

3. PAC10 is the total dynamic power measured on VCC and VCCI.

# Example of Power Calculation

This example considers a shift register with 5,000 storage tiles, including a counter and memory that stores analog information. The shift register is clocked at 50 MHz and stores and reads information from a RAM.

The device used is a commercial AFS600 device operating in typical conditions.

The calculation below uses the power calculation methodology previously presented and shows how to determine the dynamic and static power consumption of resources used in the application.

Also included in the example is the calculation of power consumption in operating, standby, and sleep modes to illustrate the benefit of power-saving modes.

# Global Clock Contribution—P<sub>CLOCK</sub>

$F_{CLK}$  = 50 MHz Number of sequential VersaTiles: N<sub>S-CELL</sub> = 5,000 Estimated number of Spines: N<sub>SPINES</sub> = 5 Estimated number of Rows: N<sub>ROW</sub> = 313

# **Operating Mode**

$$\begin{split} & \mathsf{P}_{\mathsf{CLOCK}} = (\mathsf{PAC1} + \mathsf{N}_{\mathsf{SPINE}} * \mathsf{PAC2} + \mathsf{N}_{\mathsf{ROW}} * \mathsf{PAC3} + \mathsf{N}_{\mathsf{S}\text{-}\mathsf{CELL}} * \mathsf{PAC4}) * \mathsf{F}_{\mathsf{CLK}} \\ & \mathsf{P}_{\mathsf{CLOCK}} = (0.0128 + 5 * 0.0019 + 313 * 0.00081 + 5,000 * 0.00011) * 50 \\ & \mathsf{P}_{\mathsf{CLOCK}} = 41.28 \ \mathsf{mW} \end{split}$$

# Standby Mode and Sleep Mode

$P_{CLOCK} = 0 W$

Logic—Sequential Cells, Combinational Cells, and Routing Net Contributions— $P_{S-CELL}$ ,  $P_{C-CELL}$ , and  $P_{NET}$

$\label{eq:F_CLK} \ensuremath{\mathsf{F_{CLK}}}\xspace = 50 \ensuremath{\,\mathsf{MHz}}\xspace \\ \ensuremath{\mathsf{Number}}\xspace of sequential VersaTiles: \ensuremath{\mathsf{N}_{S-CELL}}\xspace = 5,000 \\ \ensuremath{\mathsf{Number}}\xspace of versaTiles: \ensuremath{\mathsf{N}_{C-CELL}}\xspace = 6,000 \\ \ensuremath{\mathsf{Estimated}}\xspace toggle rate of VersaTile outputs: \ensuremath{\alpha_1}\xspace = 0.1 \ensuremath{\,(10\%)}\xspace \ensuremath{}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{}\xspace \ensuremath{}\xspace \ensuremath{\mathsf{R}}\xspace \ensuremath{}\xspace \ensuremath{$

# **Operating Mode**

$$\begin{split} \mathsf{P}_{S\text{-}CELL} &= \mathsf{N}_{S\text{-}CELL} * (\mathsf{P}_{\mathsf{AC5}}\text{+} (\alpha_1 \, / \, 2) * \mathsf{PAC6}) * \mathsf{F}_{\mathsf{CLK}} \\ \mathsf{P}_{S\text{-}CELL} &= 5,000 * (0.00007 + (0.1 \, / \, 2) * 0.00029) * 50 \\ \mathsf{P}_{S\text{-}CELL} &= 21.13 \text{ mW} \end{split}$$

$P_{C-CELL} = N_{C-CELL}^* (\alpha_1 / 2) * PAC7 * F_{CLK}$  $P_{C-CELL} = 6,000 * (0.1 / 2) * 0.00029 * 50$  $P_{C-CELL} = 4.35 \text{ mW}$

$$\begin{split} \mathsf{P}_{\mathsf{NET}} &= (\mathsf{N}_{\mathsf{S}\text{-}\mathsf{CELL}} + \mathsf{N}_{\mathsf{C}\text{-}\mathsf{CELL}}) * (\alpha_1 \,/\, 2) * \mathsf{PAC8} * \mathsf{F}_{\mathsf{CLK}} \\ \mathsf{P}_{\mathsf{NET}} &= (5,000 + 6,000) * (0.1 \,/\, 2) * 0.0007 * 50 \\ \mathsf{P}_{\mathsf{NET}} &= 19.25 \text{ mW} \end{split}$$

$P_{LOGIC} = P_{S-CELL} + P_{C-CELL} + P_{NET}$  $P_{LOGIC} = 21.13 \text{ mW} + 4.35 \text{ mW} + 19.25 \text{ mW}$  $P_{LOGIC} = 44.73 \text{ mW}$

Standby Mode and Sleep Mode

# PLL/CCC Contribution—P<sub>PLL</sub>

PLL is not used in this application.

$P_{PLL} = 0 W$

# Nonvolatile Memory—P<sub>NVM</sub>

Nonvolatile memory is not used in this application.

$P_{NVM} = 0 W$

# Crystal Oscillator—P<sub>XTL-OSC</sub>

The application utilizes standby mode. The crystal oscillator is assumed to be active.

### **Operating Mode**

P<sub>XTL-OSC</sub> = PAC18

$P_{XTL-OSC} = 0.63 \text{ mW}$

### Standby Mode

P<sub>XTL-OSC</sub> = PAC18

P<sub>XTL-OSC</sub> = 0.63 mW

#### Sleep Mode

$P_{XTL-OSC} = 0 W$

# RC Oscillator—P<sub>RC-OSC</sub>

# **Operating Mode**

P<sub>RC-OSC</sub> = PAC19

$P_{RC-OSC} = 3.30 \text{ mW}$

#### Standby Mode and Sleep Mode

$P_{RC-OSC} = 0 W$

## Analog System—P<sub>AB</sub>

Number of Quads used: N<sub>QUADS</sub> = 4

#### **Operating Mode**

P<sub>AB</sub> = PAC20

$P_{AB}$  = 3.00 mW

#### Standby Mode and Sleep Mode

$P_{AB} = 0 W$

# Total Dynamic Power Consumption—P<sub>DYN</sub>

#### **Operating Mode**

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub> + P<sub>NVM</sub>+ P<sub>XTL-OSC</sub> + P<sub>RC-OSC</sub> + P<sub>AB</sub> P<sub>DYN</sub> = 41.28 mW + 21.1 mW + 4.35 mW + 19.25 mW + 1.30 mW + 47.47 mW + 1.38 mW + 0 + 0 + 0 + 0.63 mW + 3.30 mW + 3.00 mW

P<sub>DYN</sub> = 143.06 mW

### Standby Mode

$P_{DYN} = P_{XTL-OSC}$  $P_{DYN} = 0.63 \text{ mW}$

#### Sleep Mode

$P_{DYN} = 0 W$

|            | QN180           |                 | QN180      |                 |                 |  |

|------------|-----------------|-----------------|------------|-----------------|-----------------|--|

| Pin Number | AFS090 Function | AFS250 Function | Pin Number | AFS090 Function | AFS250 Function |  |

| B9         | XTAL2           | XTAL2           | B45        | GBA2/IO31PDB1V0 | GBA2/IO40PDB1V0 |  |

| B10        | GEA0/IO44NDB3V0 | GFA0/IO66NDB3V0 | B46        | GNDQ            | GNDQ            |  |

| B11        | GEB2/IO42PDB3V0 | IO60NDB3V0      | B47        | GBA1/IO30RSB0V0 | GBA0/IO38RSB0V0 |  |

| B12        | VCC             | VCC             | B48        | GBB1/IO28RSB0V0 | GBC1/IO35RSB0V0 |  |

| B13        | VCCNVM          | VCCNVM          | B49        | VCC             | VCC             |  |

| B14        | VCC15A          | VCC15A          | B50        | GBC0/IO25RSB0V0 | IO31RSB0V0      |  |

| B15        | NCAP            | NCAP            | B51        | IO23RSB0V0      | IO28RSB0V0      |  |

| B16        | VCC33N          | VCC33N          | B52        | IO20RSB0V0      | IO25RSB0V0      |  |

| B17        | GNDAQ           | GNDAQ           | B53        | VCC             | VCC             |  |

| B18        | AC0             | AC0             | B54        | IO11RSB0V0      | IO14RSB0V0      |  |

| B19        | AT0             | AT0             | B55        | IO08RSB0V0      | IO11RSB0V0      |  |

| B20        | AT1             | AT1             | B56        | GAC1/IO05RSB0V0 | IO08RSB0V0      |  |

| B21        | AV1             | AV1             | B57        | VCCIB0          | VCCIB0          |  |

| B22        | AC2             | AC2             | B58        | GAB0/IO02RSB0V0 | GAC0/IO04RSB0V0 |  |

| B23        | ATRTN1          | ATRTN1          | B59        | GAA0/IO00RSB0V0 | GAA1/IO01RSB0V0 |  |

| B24        | AG3             | AG3             | B60        | VCCPLA          | VCCPLA          |  |

| B25        | AV3             | AV3             | C1         | NC              | NC              |  |

| B26        | AG4             | AG4             | C2         | NC              | VCCIB3          |  |

| B27        | ATRTN2          | ATRTN2          | C3         | GND             | GND             |  |

| B28        | NC              | AC5             | C4         | NC              | GFC2/IO69PPB3V0 |  |

| B29        | VCC33A          | VCC33A          | C5         | GFC1/IO49PDB3V0 | GFC1/IO68PDB3V0 |  |

| B30        | VAREF           | VAREF           | C6         | GFA0/IO47NPB3V0 | GFB0/IO67NPB3V0 |  |

| B31        | PUB             | PUB             | C7         | VCCIB3          | NC              |  |

| B32        | PTEM            | PTEM            | C8         | GND             | GND             |  |

| B33        | GNDNVM          | GNDNVM          | C9         | GEA1/IO44PDB3V0 | GFA1/IO66PDB3V0 |  |

| B34        | VCC             | VCC             | C10        | GEA2/IO42NDB3V0 | GEC2/IO60PDB3V0 |  |

| B35        | ТСК             | ТСК             | C11        | NC              | GEA2/IO58PSB3V0 |  |

| B36        | TMS             | TMS             | C12        | NC              | NC              |  |

| B37        | TRST            | TRST            | C13        | GND             | GND             |  |

| B38        | GDB2/IO41PSB1V0 | GDA2/IO55PSB1V0 | C14        | NC              | NC              |  |

| B39        | GDC0/IO38NDB1V0 | GDB0/IO53NDB1V0 | C15        | NC              | NC              |  |

| B40        | VCCIB1          | VCCIB1          | C16        | GNDA            | GNDA            |  |

| B41        | GCA1/IO36PDB1V0 | GCA1/IO49PDB1V0 | C17        | NC              | NC              |  |

| B42        | GCC0/IO34NDB1V0 | GCC0/IO47NDB1V0 | C18        | NC              | NC              |  |

| B43        | GCB2/IO33PSB1V0 | GBC2/IO42PSB1V0 | C19        | NC              | NC              |  |

| B44        | VCC             | VCC             | C20        | NC              | NC              |  |

Package Pin Assignments

|               | FG484           |                  | FG484         |                 |                  |  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |  |

| L17           | VCCIB2          | VCCIB2           | N8            | GND             | GND              |  |

| L18           | IO46PDB2V0      | IO69PDB2V0       | N9            | GND             | GND              |  |

| L19           | GCA1/IO45PDB2V0 | GCA1/IO64PDB2V0  | N10           | VCC             | VCC              |  |

| L20           | VCCIB2          | VCCIB2           | N11           | GND             | GND              |  |

| L21           | GCC0/IO43NDB2V0 | GCC0/IO62NDB2V0  | N12           | VCC             | VCC              |  |

| L22           | GCC1/IO43PDB2V0 | GCC1/IO62PDB2V0  | N13           | GND             | GND              |  |

| M1            | NC              | IO103PDB4V0      | N14           | VCC             | VCC              |  |

| M2            | XTAL1           | XTAL1            | N15           | GND             | GND              |  |

| M3            | VCCIB4          | VCCIB4           | N16           | GDB2/IO56PDB2V0 | GDB2/IO83PDB2V0  |  |

| M4            | GNDOSC          | GNDOSC           | N17           | NC              | IO78PDB2V0       |  |

| M5            | GFC0/IO72NDB4V0 | GFC0/IO107NDB4V0 | N18           | GND             | GND              |  |

| M6            | VCCIB4          | VCCIB4           | N19           | IO47NDB2V0      | IO72NDB2V0       |  |

| M7            | GFB0/IO71NDB4V0 | GFB0/IO106NDB4V0 | N20           | IO47PDB2V0      | IO72PDB2V0       |  |

| M8            | VCCIB4          | VCCIB4           | N21           | GND             | GND              |  |

| M9            | VCC             | VCC              | N22           | IO49PDB2V0      | IO71PDB2V0       |  |

| M10           | GND             | GND              | P1            | GFA1/IO70PDB4V0 | GFA1/IO105PDB4V0 |  |

| M11           | VCC             | VCC              | P2            | GFA0/IO70NDB4V0 | GFA0/IO105NDB4V0 |  |

| M12           | GND             | GND              | P3            | IO68NDB4V0      | IO101NDB4V0      |  |

| M13           | VCC             | VCC              | P4            | IO65PDB4V0      | IO96PDB4V0       |  |

| M14           | GND             | GND              | P5            | IO65NDB4V0      | IO96NDB4V0       |  |

| M15           | VCCIB2          | VCCIB2           | P6            | NC              | IO99NDB4V0       |  |

| M16           | IO48NDB2V0      | IO70NDB2V0       | P7            | NC              | IO97NDB4V0       |  |

| M17           | VCCIB2          | VCCIB2           | P8            | VCCIB4          | VCCIB4           |  |

| M18           | IO46NDB2V0      | IO69NDB2V0       | P9            | VCC             | VCC              |  |

| M19           | GCA0/IO45NDB2V0 | GCA0/IO64NDB2V0  | P10           | GND             | GND              |  |

| M20           | VCCIB2          | VCCIB2           | P11           | VCC             | VCC              |  |

| M21           | GCB0/IO44NDB2V0 | GCB0/IO63NDB2V0  | P12           | GND             | GND              |  |

| M22           | GCB1/IO44PDB2V0 | GCB1/IO63PDB2V0  | P13           | VCC             | VCC              |  |

| N1            | NC              | IO103NDB4V0      | P14           | GND             | GND              |  |

| N2            | GND             | GND              | P15           | VCCIB2          | VCCIB2           |  |

| N3            | IO68PDB4V0      | IO101PDB4V0      | P16           | IO56NDB2V0      | IO83NDB2V0       |  |

| N4            | NC              | IO100NPB4V0      | P17           | NC              | IO78NDB2V0       |  |

| N5            | GND             | GND              | P18           | GDA1/IO54PDB2V0 | GDA1/IO81PDB2V0  |  |

| N6            | NC              | IO99PDB4V0       | P19           | GDB1/IO53PDB2V0 | GDB1/IO80PDB2V0  |  |

| N7            | NC              | IO97PDB4V0       | P20           | IO51NDB2V0      | IO73NDB2V0       |  |

|               | FG484           |                  | FG484         |                 |                  |  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |  |

| P21           | IO51PDB2V0      | IO73PDB2V0       | T12           | AV5             | AV5              |  |

| P22           | IO49NDB2V0      | IO71NDB2V0       | T13           | AC5             | AC5              |  |

| R1            | IO69PDB4V0      | IO102PDB4V0      | T14           | NC              | NC               |  |

| R2            | IO69NDB4V0      | IO102NDB4V0      | T15           | GNDA            | GNDA             |  |

| R3            | VCCIB4          | VCCIB4           | T16           | NC              | IO77PPB2V0       |  |

| R4            | IO64PDB4V0      | IO91PDB4V0       | T17           | NC              | IO74PDB2V0       |  |

| R5            | IO64NDB4V0      | IO91NDB4V0       | T18           | VCCIB2          | VCCIB2           |  |

| R6            | NC              | IO92PDB4V0       | T19           | IO55NDB2V0      | IO82NDB2V0       |  |

| R7            | GND             | GND              | T20           | GDA2/IO55PDB2V0 | GDA2/IO82PDB2V0  |  |

| R8            | GND             | GND              | T21           | GND             | GND              |  |

| R9            | VCC33A          | VCC33A           | T22           | GDC1/IO52PDB2V0 | GDC1/IO79PDB2V0  |  |

| R10           | GNDA            | GNDA             | U1            | IO67PDB4V0      | IO98PDB4V0       |  |

| R11           | VCC33A          | VCC33A           | U2            | IO67NDB4V0      | IO98NDB4V0       |  |

| R12           | GNDA            | GNDA             | U3            | GEC1/IO63PDB4V0 | GEC1/IO90PDB4V0  |  |

| R13           | VCC33A          | VCC33A           | U4            | GEC0/IO63NDB4V0 | GEC0/IO90NDB4V0  |  |

| R14           | GNDA            | GNDA             | U5            | GND             | GND              |  |

| R15           | VCC             | VCC              | U6            | VCCNVM          | VCCNVM           |  |

| R16           | GND             | GND              | U7            | VCCIB4          | VCCIB4           |  |

| R17           | NC              | IO74NDB2V0       | U8            | VCC15A          | VCC15A           |  |

| R18           | GDA0/IO54NDB2V0 | GDA0/IO81NDB2V0  | U9            | GNDA            | GNDA             |  |

| R19           | GDB0/IO53NDB2V0 | GDB0/IO80NDB2V0  | U10           | AC4             | AC4              |  |

| R20           | VCCIB2          | VCCIB2           | U11           | VCC33A          | VCC33A           |  |

| R21           | IO50NDB2V0      | IO75NDB2V0       | U12           | GNDA            | GNDA             |  |

| R22           | IO50PDB2V0      | IO75PDB2V0       | U13           | AG5             | AG5              |  |

| T1            | NC              | IO100PPB4V0      | U14           | GNDA            | GNDA             |  |

| T2            | GND             | GND              | U15           | PUB             | PUB              |  |

| Т3            | IO66PDB4V0      | IO95PDB4V0       | U16           | VCCIB2          | VCCIB2           |  |

| T4            | IO66NDB4V0      | IO95NDB4V0       | U17           | TDI             | TDI              |  |

| Т5            | VCCIB4          | VCCIB4           | U18           | GND             | GND              |  |

| Т6            | NC              | IO92NDB4V0       | U19           | IO57NDB2V0      | IO84NDB2V0       |  |

| Τ7            | GNDNVM          | GNDNVM           | U20           | GDC2/IO57PDB2V0 | GDC2/IO84PDB2V0  |  |

| Т8            | GNDA            | GNDA             | U21           | NC              | IO77NPB2V0       |  |

| Т9            | NC              | NC               | U22           | GDC0/IO52NDB2V0 | GDC0/IO79NDB2V0  |  |

| T10           | AV4             | AV4              | V1            | GEB1/IO62PDB4V0 | GEB1/IO89PDB4V0  |  |

| T11           | NC              | NC               | V2            | GEB0/IO62NDB4V0 | GEB0/IO89NDB4V0  |  |