Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | 36864                                                         |

| Number of I/O                  | 65                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 180-WFQFN Dual Rows, Exposed Pad                              |

| Supplier Device Package        | 180-QFN (10x10)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs250-2qng180 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 – Device Architecture

# **Fusion Stack Architecture**

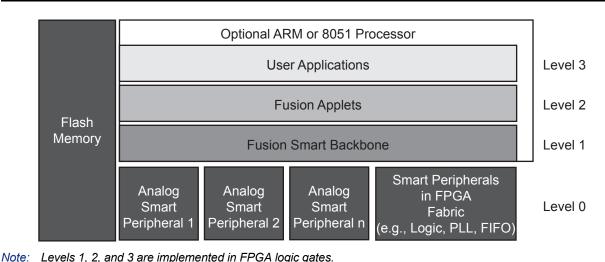

To manage the unprecedented level of integration in Fusion devices, Microsemi developed the Fusion technology stack (Figure 2-1). This layered model offers a flexible design environment, enabling design at very high and very low levels of abstraction. Fusion peripherals include hard analog IP and hard and soft digital IP. Peripherals communicate across the FPGA fabric via a layer of soft gates—the Fusion backbone. Much more than a common bus interface, this Fusion backbone integrates a micro-sequencer within the FPGA fabric and configures the individual peripherals and supports low-level processing of peripheral data. Fusion applets are application building blocks that can control and respond to peripherals and other system signals. Applets can be rapidly combined to create large applications. The technology is scalable across devices, families, design types, and user expertise, and supports a well-defined interface for external IP and tool integration.

At the lowest level, Level 0, are Fusion peripherals. These are configurable functional blocks that can be hardwired structures such as a PLL or analog input channel, or soft (FPGA gate) blocks such as a UART or two-wire serial interface. The Fusion peripherals are configurable and support a standard interface to facilitate communication and implementation.

Connecting and controlling access to the peripherals is the Fusion backbone, Level 1. The backbone is a soft-gate structure, scalable to any number of peripherals. The backbone is a bus and much more; it manages peripheral configuration to ensure proper operation. Leveraging the common peripheral interface and a low-level state machine, the backbone efficiently offloads peripheral management from the system design. The backbone can set and clear flags based upon peripheral behavior and can define performance criteria. The flexibility of the stack enables a designer to configure the silicon, directly bypassing the backbone if that level of control is desired.

One step up from the backbone is the Fusion applet, Level 2. The applet is an application building block that implements a specific function in FPGA gates. It can react to stimuli and board-level events coming through the backbone or from other sources, and responds to these stimuli by accessing and manipulating peripherals via the backbone or initiating some other action. An applet controls or responds to the peripheral(s). Applets can be easily imported or exported from the design environment. The applet structure is open and well-defined, enabling users to import applets from Microsemi, system developers, third parties, and user groups.

Figure 2-1 • Fusion Architecture Stack

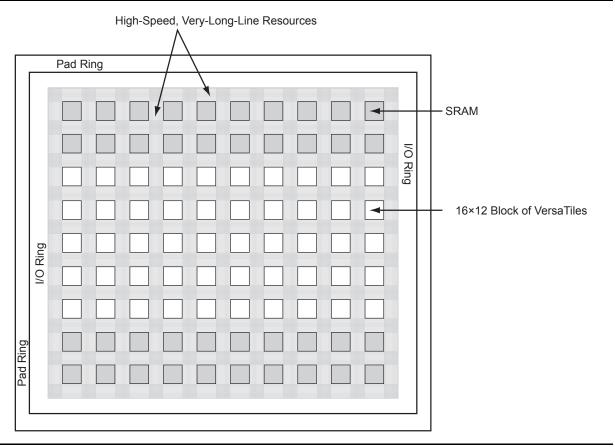

Figure 2-10 • Very-Long-Line Resources

### **CCC Physical Implementation**

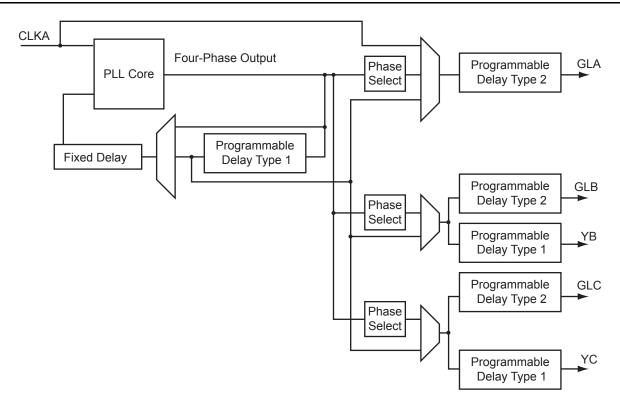

The CCC circuit is composed of the following (Figure 2-23):

- PLL core

- · 3 phase selectors

- · 6 programmable delays and 1 fixed delay

- 5 programmable frequency dividers that provide frequency multiplication/division (not shown in Figure 2-23 because they are automatically configured based on the user's required frequencies)

- 1 dynamic shift register that provides CCC dynamic reconfiguration capability (not shown)

### **CCC Programming**

The CCC block is fully configurable. It is configured via static flash configuration bits in the array, set by the user in the programming bitstream, or configured through an asynchronous dedicated shift register, dynamically accessible from inside the Fusion device. The dedicated shift register permits changes of parameters such as PLL divide ratios and delays during device operation. This latter mode allows the user to dynamically reconfigure the PLL without the need for core programming. The register file is accessed through a simple serial interface.

Note: Clock divider and multiplier blocks are not shown in this figure or in SmartGen. They are automatically configured based on the user's required frequencies.

Figure 2-23 • PLL Block

# Flash Memory Block Diagram

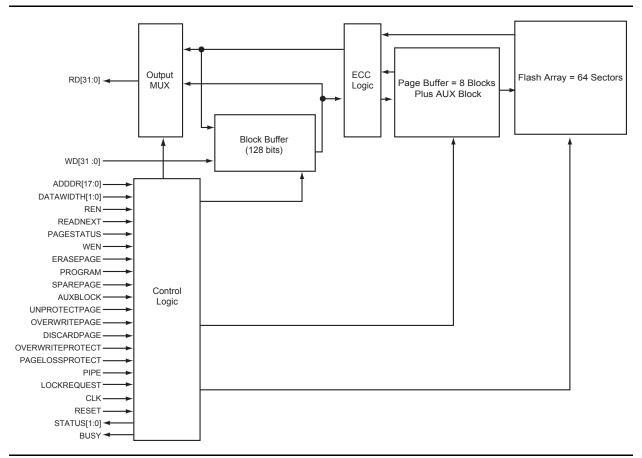

A simplified diagram of the flash memory block is shown in Figure 2-33.

Figure 2-33 • Flash Memory Block Diagram

The logic consists of the following sub-blocks:

- · Flash Array

- Contains all stored data. The flash array contains 64 sectors, and each sector contains 33 pages of data.

- Page Buffer

- A page-wide volatile register. A page contains 8 blocks of data and an AUX block.

- Block Buffer

- Contains the contents of the last block accessed. A block contains 128 data bits.

- · ECC Logic

The FB stores error correction information with each block to perform single-bit error correction and double-bit error detection on all data blocks.

Table 2-32 • RAM512X18

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                        | Description                                                                                                        | -2   | -1   | Std. | Units |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>                  | Address setup time                                                                                                 | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>                  | Address hold time                                                                                                  | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>                 | REN, WEN setup time                                                                                                | 0.09 | 0.10 | 0.12 | ns    |

| t <sub>ENH</sub>                 | REN, WEN hold time                                                                                                 | 0.06 | 0.07 | 0.08 | ns    |

| t <sub>DS</sub>                  | Input data (WD) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>                  | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>                | Clock High to new data valid on RD (output retained)                                                               | 2.16 | 2.46 | 2.89 | ns    |

| t <sub>CKQ2</sub>                | Clock High to new data valid on RD (pipelined)                                                                     | 0.90 | 1.02 | 1.20 | ns    |

| t <sub>C2CRWH</sub> <sup>1</sup> | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge | 0.50 | 0.43 | 0.38 | ns    |

| t <sub>C2CWRH</sub> 1            | Address collision clk-to-clk delay for reliable write access after read on same address—Applicable to Opening Edge | 0.59 | 0.50 | 0.44 | ns    |

| +1                               | RESET Low to data out Low on RD (flow-through)                                                                     | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>RSTBQ</sub> 1             | RESET Low to data out Low on RD (pipelined)                                                                        | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>             | RESET removal                                                                                                      | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>             | RESET recovery                                                                                                     | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>             | RESET minimum pulse width                                                                                          | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>                 | Clock cycle time                                                                                                   | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>                 | Maximum frequency                                                                                                  | 310  | 272  | 231  | MHz   |

### Notes:

2-67 Revision 6

For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

<sup>2.</sup> For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

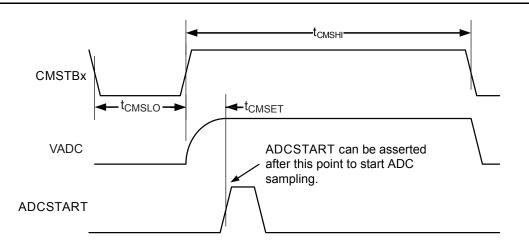

To initiate a current measurement, the appropriate Current Monitor Strobe (CMSTB) signal on the AB macro must be asserted low for at least  $t_{CMSLO}$  in order to discharge the previous measurement. Then CMSTB must be asserted high for at least  $t_{CMSET}$  prior to asserting the ADCSTART signal. The CMSTB must remain high until after the SAMPLE signal is de-asserted by the AB macro. Note that the minimum sample time cannot be less than  $t_{CMSHI}$ . Figure 2-71 shows the timing diagram of CMSTB in relationship with the ADC control signals.

Figure 2-71 • Timing Diagram for Current Monitor Strobe

Figure 2-72 illustrates positive current monitor operation. The differential voltage between AV and AC goes into the 10× amplifier and is then converted by the ADC. For example, a current of 1.5 A is drawn from a 10 V supply and is measured by the voltage drop across a 0.050  $\Omega$  sense resistor, The voltage drop is amplified by ten times by the amplifier and then measured by the ADC. The 1.5 A current creates a differential voltage across the sense resistor of 75 mV. This becomes 750 mV after amplification. Thus, the ADC measures a current of 1.5 A as 750 mV. Using an ADC with 8-bit resolution and VAREF of 2.56 V, the ADC result is decimal 75. EQ 3 shows how to compute the current from the ADC result.

$$|I| = (ADC \times V_{AREF})/(10 \times 2^{N} \times R_{sense})$$

EQ3

where

I is the current flowing through the sense resistor

ADC is the result from the ADC

VAREF is the Reference voltage

N is the number of bits

Rsense is the resistance of the sense resistor

2-87 Revision 6

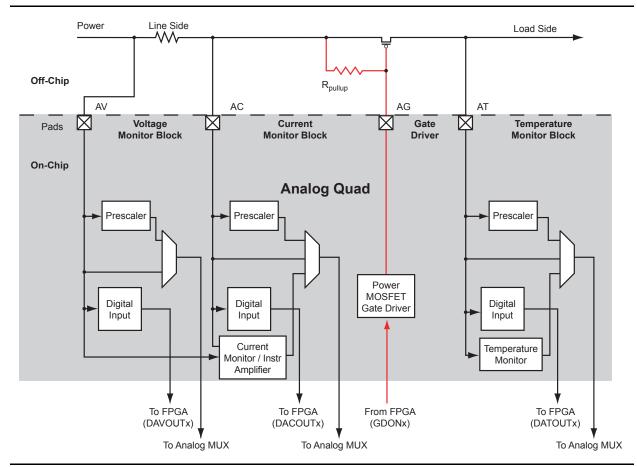

### Gate Driver

The Fusion Analog Quad includes a Gate Driver connected to the Quad's AG pin (Figure 2-74). Designed to work with external p- or n-channel MOSFETs, the Gate driver is a configurable current sink or source and requires an external pull-up or pull-down resistor. The AG supports 4 selectable gate drive levels: 1  $\mu$ A, 3  $\mu$ A, 10  $\mu$ A, and 30  $\mu$ A (Figure 2-75 on page 2-91). The AG also supports a High Current Drive mode in which it can sink 20 mA; in this mode the switching rate is approximately 1.3 MHz with 100 ns turn-on time and 600 ns turn-off time. Modeled on an open-drain-style output, it does not output a voltage level without an appropriate pull-up or pull-down resistor. If 1 V is forced on the drain, the current sinking/sourcing will exceed the ability of the transistor, and the device could be damaged.

The AG pad is turned on via the corresponding GDONx pin in the Analog Block macro, where x is the number of the corresponding Analog Quad for the AG pad to be enabled (GDON0 to GDON9).

Figure 2-74 • Gate Driver

The gate-to-source voltage ( $V_{gs}$ ) of the external MOSFET is limited to the programmable drive current times the external pull-up or pull-down resistor value (EQ 5).

$$V_{as} \le I_a \times (R_{pullup} \text{ or } R_{pulldown})$$

EQ5

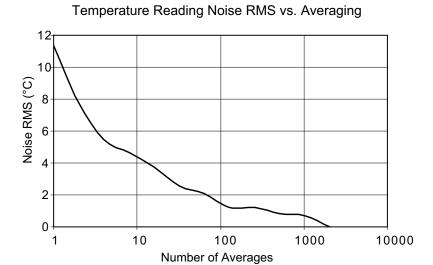

Figure 2-96 • Temperature Reading Noise When Averaging is Used

# **Analog System Characteristics**

Table 2-49 • Analog Channel Specifications

Commercial Temperature Range Conditions,  $T_J$  = 85°C (unless noted otherwise), Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter            | Description                         | Condition                                  | Min.           | Тур. | Max.                                          | Units |

|----------------------|-------------------------------------|--------------------------------------------|----------------|------|-----------------------------------------------|-------|

| Voltage Monit        | or Using Analog Pads AV,            | AC and AT (using prescaler)                | I              |      | 1                                             |       |

|                      | Input Voltage<br>(Prescaler)        | Refer to Table 3-2 on page 3-3             |                |      |                                               |       |

| VINAP                | Uncalibrated Gain and Offset Errors | Refer to Table 2-51 on page 2-122          |                |      |                                               |       |

|                      | Calibrated Gain and Offset Errors   | Refer to Table 2-52 on page 2-123          |                |      |                                               |       |

|                      | Bandwidth1                          |                                            |                |      | 100                                           | KHz   |

|                      | Input Resistance                    | Refer to Table 3-3 on page 3-4             |                |      |                                               |       |

|                      | Scaling Factor                      | Prescaler modes (Table 2-57 on page 2-130) |                |      |                                               |       |

|                      | Sample Time                         |                                            | 10             |      |                                               | μs    |

| <b>Current Monit</b> | tor Using Analog Pads AV            | and AC                                     | II.            | u.   |                                               |       |

| VRSM <sup>1</sup>    | Maximum Differential Input Voltage  |                                            |                |      | VAREF / 10                                    | mV    |

|                      | Resolution                          | Refer to "Current Monitor" section         |                |      |                                               |       |

|                      | Common Mode Range                   |                                            |                |      | - 10.5 to +12                                 | V     |

| CMRR                 | Common Mode<br>Rejection Ratio      | DC – 1 KHz                                 |                | 60   |                                               | dB    |

|                      |                                     | 1 KHz - 10 KHz                             |                | 50   |                                               | dB    |

|                      |                                     | > 10 KHz                                   |                | 30   |                                               | dB    |

| <sup>t</sup> cmshi   | Strobe High time                    |                                            | ADC conv. time |      | 200                                           | μs    |

| t <sub>CMSHI</sub>   | Strobe Low time                     |                                            | 5              |      |                                               | μs    |

| t <sub>CMSHI</sub>   | Settling time                       |                                            | 0.02           |      |                                               | μs    |

|                      | Accuracy                            | Input differential voltage > 50 mV         |                |      | -2 -(0.05 x<br>VRSM) to +2 +<br>(0.05 x VRSM) | mV    |

### Notes:

- 1. VRSM is the maximum voltage drop across the current sense resistor.

- 2. Analog inputs used as digital inputs can tolerate the same voltage limits as the corresponding analog pad. There is no reliability concern on digital inputs as long as VIND does not exceed these limits.

- 3. VIND is limited to VCC33A + 0.2 to allow reaching 10 MHz input frequency.

- 4. An averaging of 1,024 samples (LPF setting in Analog System Builder) is required and the maximum capacitance allowed across the AT pins is 500 pF.

- 5. The temperature offset is a fixed positive value.

- 6. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

- 7. When using SmartGen Analog System Builder, CalibIP is required to obtain specified offset. For further details on CalibIP, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

2-117 Revision 6

# **Analog Quad ACM Description**

Table 2-56 maps out the ACM space associated with configuration of the Analog Quads within the Analog Block. Table 2-56 shows the byte assignment within each quad and the function of each bit within each byte. Subsequent tables will explain each bit setting and how it corresponds to a particular configuration. After 3.3 V and 1.5 V are applied to Fusion, Analog Quad configuration registers are loaded with default settings until the initialization and configuration state machine changes them to user-defined settings.

Table 2-56 • Analog Quad ACM Byte Assignment

| Byte   | Bit | Signal (Bx) | Function                            | Default Setting       |  |  |

|--------|-----|-------------|-------------------------------------|-----------------------|--|--|

| Byte 0 | 0   | B0[0]       | Scaling factor control – prescaler  | Highest voltage range |  |  |

| (AV)   | 1   | B0[1]       |                                     |                       |  |  |

|        | 2   | B0[2]       |                                     |                       |  |  |

|        | 3   | B0[3]       | Analog MUX select                   | Prescaler             |  |  |

|        | 4   | B0[4]       | Current monitor switch              | Off                   |  |  |

|        | 5   | B0[5]       | Direct analog input switch          | Off                   |  |  |

|        | 6   | B0[6]       | Selects V-pad polarity              | Positive              |  |  |

|        | 7   | B0[7]       | Prescaler op amp mode               | Power-down            |  |  |

| Byte 1 | 0   | B1[0]       | Scaling factor control – prescaler  | Highest voltage range |  |  |

| (AC)   | 1   | B1[1]       |                                     |                       |  |  |

|        | 2   | B1[2]       |                                     |                       |  |  |

|        | 3   | B1[3]       | Analog MUX select                   | Prescaler             |  |  |

|        | 4   | B1[4]       |                                     |                       |  |  |

|        | 5   | B1[5]       | Direct analog input switch          | Off                   |  |  |

|        | 6   | B1[6]       | Selects C-pad polarity              | Positive              |  |  |

|        | 7   | B1[7]       | Prescaler op amp mode               | Power-down            |  |  |

| Byte 2 | 0   | B2[0]       | Internal chip temperature monitor * | Off                   |  |  |

| (AG)   | 1   | B2[1]       | Spare                               | -                     |  |  |

|        | 2   | B2[2]       | Current drive control               | Lowest current        |  |  |

|        | 3   | B2[3]       |                                     |                       |  |  |

|        | 4   | B2[4]       | Spare                               | -                     |  |  |

|        | 5   | B2[5]       | Spare                               | _                     |  |  |

|        | 6   | B2[6]       | Selects G-pad polarity              | Positive              |  |  |

|        | 7   | B2[7]       | Selects low/high drive              | Low drive             |  |  |

| Byte 3 | 0   | B3[0]       | Scaling factor control – prescaler  | Highest voltage range |  |  |

| (AT)   | 1   | B3[1]       |                                     |                       |  |  |

|        | 2   | B3[2]       |                                     |                       |  |  |

|        | 3   | B3[3]       | Analog MUX select                   | Prescaler             |  |  |

|        | 4   | B3[4]       |                                     |                       |  |  |

|        | 5   | B3[5]       | Direct analog input switch          | Off                   |  |  |

|        | 6   | B3[6]       | -                                   | -                     |  |  |

|        | 7   | B3[7]       | Prescaler op amp mode               | Power-down            |  |  |

Note: \*For the internal temperature monitor to function, Bit 0 of Byte 2 for all 10 Quads must be set.

2-129 Revision 6

### Fusion Family of Mixed Signal FPGAs

Table 2-68 • I/O Bank Support by Device

| I/O Bank     | AFS090 | AFS250 | AFS600 | AFS1500 |

|--------------|--------|--------|--------|---------|

| Standard I/O | N      | N      | -      | _       |

| Advanced I/O | E, W   | E, W   | E, W   | E, W    |

| Pro I/O      | _      | -      | N      | N       |

| Analog Quad  | S      | S      | S      | S       |

*Note:* E = East side of the device

W = West side of the device N = North side of the device S = South side of the device

Table 2-69 • Fusion VCCI Voltages and Compatible Standards

| VCCI (typical) | Compatible Standards                                                                          |

|----------------|-----------------------------------------------------------------------------------------------|

| 3.3 V          | LVTTL/LVCMOS 3.3, PCI 3.3, SSTL3 (Class I and II),* GTL+ 3.3, GTL 3.3,* LVPECL                |

| 2.5 V          | LVCMOS 2.5, LVCMOS 2.5/5.0, SSTL2 (Class I and II),* GTL+ 2.5,* GTL 2.5,* LVDS, BLVDS, M-LVDS |

| 1.8 V          | LVCMOS 1.8                                                                                    |

| 1.5 V          | LVCMOS 1.5, HSTL (Class I),* HSTL (Class II)*                                                 |

Note: \*I/O standard supported by Pro I/O banks.

Table 2-70 • Fusion VREF Voltages and Compatible Standards\*

| VREF (typical) | Compatible Standards            |

|----------------|---------------------------------|

| 1.5 V          | SSTL3 (Class I and II)          |

| 1.25 V         | SSTL2 (Class I and II)          |

| 1.0 V          | GTL+ 2.5, GTL+ 3.3              |

| 0.8 V          | GTL 2.5, GTL 3.3                |

| 0.75 V         | HSTL (Class I), HSTL (Class II) |

Note: \*I/O standards supported by Pro I/O banks.

### 2.5 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-147 • Minimum and Maximum DC Input and Output Levels

| 2.5 V<br>GTL+     | VIL       |           | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | юзн                     | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-----------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 33 mA             | -0.3      | \'DEE 0.4 | VREF + 0.1 | 3.6       | 0.6       |           | 33  | 33 | 124                     | 169                     | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

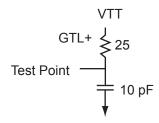

Figure 2-127 • AC Loading

Table 2-148 • AC Waveforms, Measuring Points, and Capacitive Loads

| ı | nput Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---|--------------|----------------|----------------------|-----------------|----------------|------------------------|

| ١ | √REF – 0.1   | VREF + 0.1     | 1.0                  | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-149 • 2.5 V GTL+

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.21            | 0.04             | 1.51            | 0.43              | 2.25            | 2.10            |                 |                 | 4.48             | 4.34             | ns    |

| -1             | 0.56              | 1.88            | 0.04             | 1.29            | 0.36              | 1.91            | 1.79            |                 |                 | 3.81             | 3.69             | ns    |

| -2             | 0.49              | 1.65            | 0.03             | 1.13            | 0.32              | 1.68            | 1.57            |                 |                 | 3.35             | 4.34             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Fusion Family of Mixed Signal FPGAs

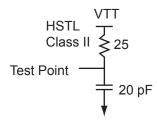

#### **HSTL Class II**

High-Speed Transceiver Logic is a general-purpose high-speed 1.5 V bus standard (EIA/JESD8-6). Fusion devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-153 • Minimum and Maximum DC Input and Output Levels

| HSTL Class II      |           | VIL        | VIH        |           | VOL       | VOH        | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|--------------------|-----------|------------|------------|-----------|-----------|------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive Strength     | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 15 mA <sup>3</sup> | -0.3      | VREF - 0.1 | VREF + 0.1 | 3.6       | 0.4       | VCCI - 0.4 | 15  | 15 | 55                      | 66                      | 10                      | 10                      |

#### Note:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Output drive strength is below JEDEC specification.

Figure 2-129 • AC Loading

Table 2-154 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF - 0.1    | VREF + 0.1     | 0.75                 | 0.75            | 0.75           | 20                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

### **Timing Characteristics**

Table 2-155 • HSTL Class II

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V, VREF = 0.75 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 3.02            | 0.04             | 2.12            | 0.43              | 3.08            | 2.71            |                 |                 | 5.32             | 4.95             | ns    |

| <b>-1</b>      | 0.56              | 2.57            | 0.04             | 1.81            | 0.36              | 2.62            | 2.31            |                 |                 | 4.52             | 4.21             | ns    |

| -2             | 0.49              | 2.26            | 0.03             | 1.59            | 0.32              | 2.30            | 2.03            |                 |                 | 3.97             | 3.70             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

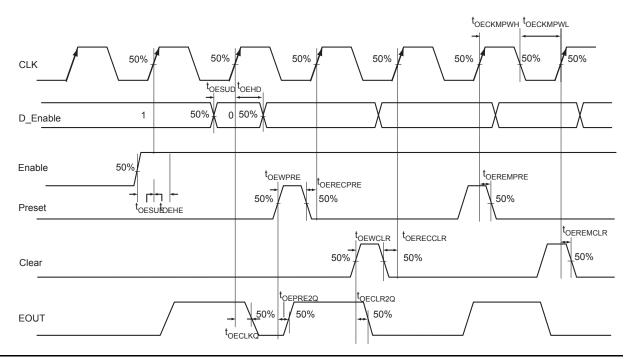

### **Output Enable Register**

Figure 2-141 • Output Enable Register Timing Diagram

### **Timing Characteristics**

Table 2-178 • Output Enable Register Propagation Delays Commercial Temperature Range Conditions: T<sub>1</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -2   | <b>-1</b> | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|-----------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               |      |           | 0.59 | ns    |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                         | 0.31 | 0.36      | 0.42 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.44 | 0.50      | 0.58 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.67 | 0.76      | 0.89 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 |      | 0.76      | 0.89 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         |      | 0.00      | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        |      | 0.25      | 0.30 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        |      | 0.00      | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.36 | 0.41      | 0.48 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           |      |           | 0.43 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

#### TRST Boundary Scan Reset Pin

The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the TAP is held in reset mode. The resistor values must be chosen from Table 2-183 and must satisfy the parallel resistance value requirement. The values in Table 2-183 correspond to the resistor recommended when a single device is used and to the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entering an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

# **Special Function Pins**

#### NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC Don't Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

#### NCAP Negative Capacitor

Negative Capacitor is where the negative terminal of the charge pump capacitor is connected. A capacitor, with a  $2.2 \, \mu F$  recommended value, is required to connect between PCAP and NCAP.

### PCAP Positive Capacitor

Positive Capacitor is where the positive terminal of the charge pump capacitor is connected. A capacitor, with a 2.2 µF recommended value, is required to connect between PCAP and NCAP.

### PUB Push Button

*Push button* is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.

#### PTBASE Pass Transistor Base

Pass Transistor Base is the control signal of the voltage regulator. This pin should be connected to the base of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

### PTEM Pass Transistor Emitter

Pass Transistor Emitter is the feedback input of the voltage regulator.

This pin should be connected to the emitter of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

### XTAL1 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

2-227 Revision 6

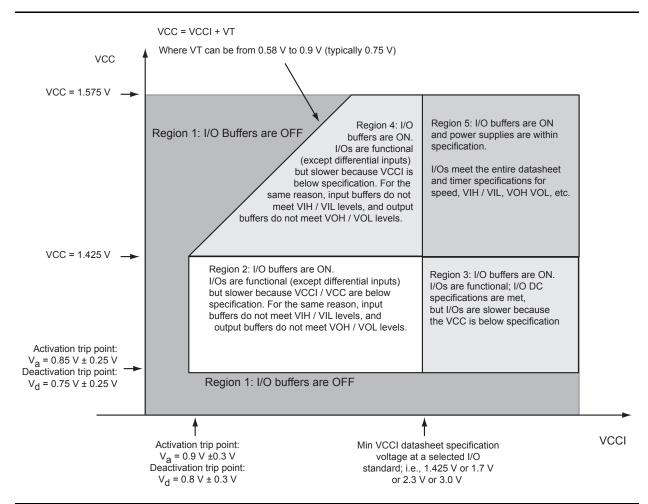

Figure 3-1 • I/O State as a Function of VCCI and VCC Voltage Levels

### **Thermal Characteristics**

### Introduction

The temperature variable in the Microsemi Designer software refers to the junction temperature, not the ambient, case, or board temperatures. This is an important distinction because dynamic and static power consumption will cause the chip's junction temperature to be higher than the ambient, case, or board temperatures. EQ 1 through EQ 3 give the relationship between thermal resistance, temperature gradient, and power.

$$\theta_{JA} = \frac{T_J - \theta_A}{P}$$

EQ 1

$$\theta_{JB} = \frac{T_J - T_B}{P}$$

EQ 2

$$\theta_{JC} = \frac{T_J - T_C}{P}$$

EQ3

where

$\theta_{JA}$  = Junction-to-air thermal resistance

$\theta_{JB}$  = Junction-to-board thermal resistance

$\theta_{JC}$  = Junction-to-case thermal resistance

$T_J$  = Junction temperature

T<sub>A</sub> = Ambient temperature

T<sub>B</sub> = Board temperature (measured 1.0 mm away from the package edge)

T<sub>C</sub> = Case temperature

P = Total power dissipated by the device

Table 3-6 • Package Thermal Resistance

|               |           | $\theta_{JA}$ |         |      |                   |       |

|---------------|-----------|---------------|---------|------|-------------------|-------|

| Product       | Still Air | 1.0 m/s       | 2.5 m/s | θЈС  | $\theta_{\sf JB}$ | Units |

| AFS090-QN108  | 34.5      | 30.0          | 27.7    | 8.1  | 16.7              | °C/W  |

| AFS090-QN180  | 33.3      | 27.6          | 25.7    | 9.2  | 21.2              | °C/W  |

| AFS250-QN180  | 32.2      | 26.5          | 24.7    | 5.7  | 15.0              | °C/W  |

| AFS250-PQ208  | 42.1      | 38.4          | 37      | 20.5 | 36.3              | °C/W  |

| AFS600-PQ208  | 23.9      | 21.3          | 20.48   | 6.1  | 16.5              | °C/W  |

| AFS090-FG256  | 37.7      | 33.9          | 32.2    | 11.5 | 29.7              | °C/W  |

| AFS250-FG256  | 33.7      | 30.0          | 28.3    | 9.3  | 24.8              | °C/W  |

| AFS600-FG256  | 28.9      | 25.2          | 23.5    | 6.8  | 19.9              | °C/W  |

| AFS1500-FG256 | 23.3      | 19.6          | 18.0    | 4.3  | 14.2              | °C/W  |

| AFS600-FG484  | 21.8      | 18.2          | 16.7    | 7.7  | 16.8              | °C/W  |

| AFS1500-FG484 | 21.6      | 16.8          | 15.2    | 5.6  | 14.9              | °C/W  |

| AFS1500-FG676 | TBD       | TBD           | TBD     | TBD  | TBD               | °C/W  |

3-7 Revision 6

Table 3-13 • Summary of I/O Output Buffer Power (per pin)—Default I/O Software Settings<sup>1</sup> (continued)

|                                  | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC8 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup> |  |  |  |

|----------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|--|--|--|

| Differential                     |                        |          |                                        |                                              |  |  |  |

| LVDS                             | _                      | 2.5      | 7.74                                   | 88.92                                        |  |  |  |

| LVPECL                           | _                      | 3.3      | 19.54                                  | 166.52                                       |  |  |  |

| Applicable to Standard I/O Banks |                        |          |                                        |                                              |  |  |  |

| Single-Ended                     |                        |          |                                        |                                              |  |  |  |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 35                     | 3.3      | _                                      | 431.08                                       |  |  |  |

| 2.5 V LVCMOS                     | 35                     | 2.5      | -                                      | 247.36                                       |  |  |  |

| 1.8 V LVCMOS                     | 35                     | 1.8      | _                                      | 128.46                                       |  |  |  |

| 1.5 V LVCMOS (JESD8-11)          | 35                     | 1.5      | _                                      | 89.46                                        |  |  |  |

#### Notes:

- 1. Dynamic power consumption is given for standard load and software-default drive strength and output slew.

- 2. PDC8 is the static power (where applicable) measured on VCCI.

- 3. PAC10 is the total dynamic power measured on VCC and VCCI.

3-21 Revision 6

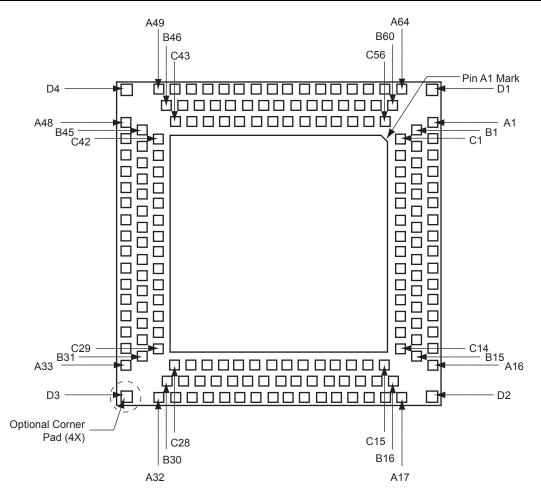

# **QN180**

Note: The die attach paddle center of the package is tied to ground (GND).

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

4-3 Revision 6

| PQ208         |                 |                 |  |  |  |  |  |

|---------------|-----------------|-----------------|--|--|--|--|--|

| Pin<br>Number | AFS250 Function | AFS600 Function |  |  |  |  |  |

| 147           | GCC1/IO47PDB1V0 | IO39NDB2V0      |  |  |  |  |  |

| 148           | IO42NDB1V0      | GCA2/IO39PDB2V0 |  |  |  |  |  |

| 149           | GBC2/IO42PDB1V0 | IO31NDB2V0      |  |  |  |  |  |

| 150           | VCCIB1          | GBB2/IO31PDB2V0 |  |  |  |  |  |

| 151           | GND             | IO30NDB2V0      |  |  |  |  |  |

| 152           | VCC             | GBA2/IO30PDB2V0 |  |  |  |  |  |

| 153           | IO41NDB1V0      | VCCIB2          |  |  |  |  |  |

| 154           | GBB2/IO41PDB1V0 | GNDQ            |  |  |  |  |  |

| 155           | IO40NDB1V0      | VCOMPLB         |  |  |  |  |  |

| 156           | GBA2/IO40PDB1V0 | VCCPLB          |  |  |  |  |  |

| 157           | GBA1/IO39RSB0V0 | VCCIB1          |  |  |  |  |  |

| 158           | GBA0/IO38RSB0V0 | GNDQ            |  |  |  |  |  |

| 159           | GBB1/IO37RSB0V0 | GBB1/IO27PPB1V1 |  |  |  |  |  |

| 160           | GBB0/IO36RSB0V0 | GBA1/IO28PPB1V1 |  |  |  |  |  |

| 161           | GBC1/IO35RSB0V0 | GBB0/IO27NPB1V1 |  |  |  |  |  |

| 162           | VCCIB0          | GBA0/IO28NPB1V1 |  |  |  |  |  |

| 163           | GND             | VCCIB1          |  |  |  |  |  |

| 164           | VCC             | GND             |  |  |  |  |  |

| 165           | GBC0/IO34RSB0V0 | VCC             |  |  |  |  |  |

| 166           | IO33RSB0V0      | GBC1/IO26PDB1V1 |  |  |  |  |  |

| 167           | IO32RSB0V0      | GBC0/IO26NDB1V1 |  |  |  |  |  |

| 168           | IO31RSB0V0      | IO24PPB1V1      |  |  |  |  |  |

| 169           | IO30RSB0V0      | IO23PPB1V1      |  |  |  |  |  |

| 170           | IO29RSB0V0      | IO24NPB1V1      |  |  |  |  |  |

| 171           | IO28RSB0V0      | IO23NPB1V1      |  |  |  |  |  |

| 172           | IO27RSB0V0      | IO22PPB1V0      |  |  |  |  |  |

| 173           | IO26RSB0V0      | IO21PPB1V0      |  |  |  |  |  |

| 174           | IO25RSB0V0      | IO22NPB1V0      |  |  |  |  |  |

| 175           | VCCIB0          | IO21NPB1V0      |  |  |  |  |  |

| 176           | GND             | IO20PSB1V0      |  |  |  |  |  |

| 177           | VCC             | IO19PSB1V0      |  |  |  |  |  |

| 178           | IO24RSB0V0      | IO14NSB0V1      |  |  |  |  |  |

| 179           | IO23RSB0V0      | IO12PDB0V1      |  |  |  |  |  |

| 180           | IO22RSB0V0      | IO12NDB0V1      |  |  |  |  |  |

| 181           | IO21RSB0V0      | VCCIB0          |  |  |  |  |  |

| 182           | IO20RSB0V0      | GND             |  |  |  |  |  |

| 183           | IO19RSB0V0      | VCC             |  |  |  |  |  |

| PQ208         |                 |                 |  |  |  |  |  |

|---------------|-----------------|-----------------|--|--|--|--|--|

| Pin<br>Number | AFS250 Function | AFS600 Function |  |  |  |  |  |

| 184           | IO18RSB0V0      | IO10PPB0V1      |  |  |  |  |  |

| 185           | IO17RSB0V0      | IO09PPB0V1      |  |  |  |  |  |

| 186           | IO16RSB0V0      | IO10NPB0V1      |  |  |  |  |  |

| 187           | IO15RSB0V0      | IO09NPB0V1      |  |  |  |  |  |

| 188           | VCCIB0          | IO08PPB0V1      |  |  |  |  |  |

| 189           | GND             | IO07PPB0V1      |  |  |  |  |  |

| 190           | VCC             | IO08NPB0V1      |  |  |  |  |  |

| 191           | IO14RSB0V0      | IO07NPB0V1      |  |  |  |  |  |

| 192           | IO13RSB0V0      | IO06PPB0V0      |  |  |  |  |  |

| 193           | IO12RSB0V0      | IO05PPB0V0      |  |  |  |  |  |

| 194           | IO11RSB0V0      | IO06NPB0V0      |  |  |  |  |  |

| 195           | IO10RSB0V0      | IO04PPB0V0      |  |  |  |  |  |

| 196           | IO09RSB0V0      | IO05NPB0V0      |  |  |  |  |  |

| 197           | IO08RSB0V0      | IO04NPB0V0      |  |  |  |  |  |

| 198           | IO07RSB0V0      | GAC1/IO03PDB0V0 |  |  |  |  |  |

| 199           | IO06RSB0V0      | GAC0/IO03NDB0V0 |  |  |  |  |  |

| 200           | GAC1/IO05RSB0V0 | VCCIB0          |  |  |  |  |  |

| 201           | VCCIB0          | GND             |  |  |  |  |  |

| 202           | GND             | VCC             |  |  |  |  |  |

| 203           | VCC             | GAB1/IO02PDB0V0 |  |  |  |  |  |

| 204           | GAC0/IO04RSB0V0 | GAB0/IO02NDB0V0 |  |  |  |  |  |

| 205           | GAB1/IO03RSB0V0 | GAA1/IO01PDB0V0 |  |  |  |  |  |

| 206           | GAB0/IO02RSB0V0 | GAA0/IO01NDB0V0 |  |  |  |  |  |

| 207           | GAA1/IO01RSB0V0 | GNDQ            |  |  |  |  |  |

| 208           | GAA0/IO00RSB0V0 | VCCIB0          |  |  |  |  |  |

4-10 Revision 6