Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | 36864                                                          |

| Number of I/O                  | 65                                                             |

| Number of Gates                | 250000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                                |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                             |

| Package / Case                 | 180-WFQFN Dual Rows, Exposed Pad                               |

| Supplier Device Package        | 180-QFN (10x10)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs250-2qng180i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## VersaTile Characteristics

## Sample VersaTile Specifications—Combinatorial Module

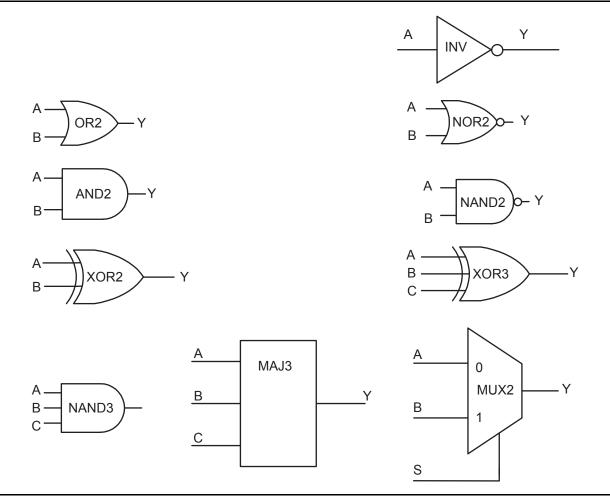

The Fusion library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library (Figure 2-3). For more details, refer to the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide.

Figure 2-3 • Sample of Combinatorial Cells

2-3 Revision 6

## **Program Operation**

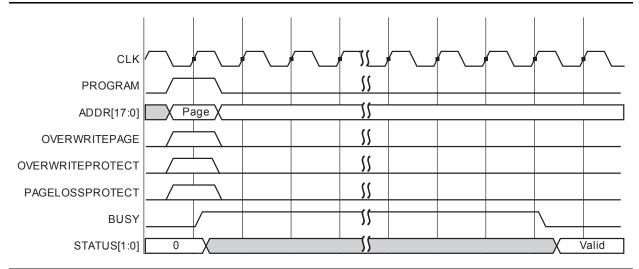

A Program operation is initiated by asserting the PROGRAM signal on the interface. Program operations save the contents of the Page Buffer to the FB Array. Due to the technologies inherent in the FB, the total programming (including erase) time per page of the eNVM is 6.8 ms. While the FB is writing the data to the array, the BUSY signal will be asserted.

During a Program operation, the sector and page addresses on ADDR are compared with the stored address for the page (and sector) in the Page Buffer. If there is a mismatch between the two addresses, the Program operation will be aborted and an error will be reported on the STATUS output.

It is possible to write the Page Buffer to a different page in memory. When asserting the PROGRAM pin, if OVERWRITEPAGE is asserted as well, the FB will write the contents of the Page Buffer to the sector and page designated on the ADDR inputs if the destination page is not Overwrite Protected.

A Program operation can be utilized to either modify the contents of the page in the flash memory block or change the protections for the page. Setting the OVERWRITEPROTECT bit on the interface while asserting the PROGRAM pin will put the page addressed into Overwrite Protect Mode. Overwrite Protect Mode safeguards a page from being inadvertently overwritten during subsequent Program or Erase operations.

Program operations that result in a STATUS value of '01' do not modify the addressed page. For all other values of STATUS, the addressed page is modified. Program errors include the following:

- 1. Attempting to program a page that is Overwrite Protected (STATUS = '01')

- 2. Attempting to program a page that is not in the Page Buffer when the Page Buffer has entered Page Loss Protection Mode (STATUS = '01')

- 3. Attempting to perform a program with OVERWRITEPAGE set when the page addressed has been Overwrite Protected (STATUS = '01')

- 4. The Write Count of the page programmed exceeding the Write Threshold defined in the part specification (STATUS = '11')

- 5. The ECC Logic determining that there is an uncorrectable error within the programmed page (STATUS = '10')

- 6. Attempting to program a page that is **not** in the Page Buffer when OVERWRITEPAGE is not set and the page in the Page Buffer is modified (STATUS = '01')

- 7. Attempting to program the page in the Page Buffer when the Page Buffer is **not** modified

The waveform for a Program operation is shown in Figure 2-36.

Figure 2-36 • FB Program Waveform

Note: OVERWRITEPAGE is only sampled when the PROGRAM or ERASEPAGE pins are asserted. OVERWRITEPAGE is ignored in all other operations.

Refer to Table 2-46 on page 2-109 and the "Acquisition Time or Sample Time Control" section on page 2-107

$$t_{\text{sample}} = (2 + STC) \times t_{\text{ADCCLK}}$$

EQ 20

STC: Sample Time Control value (0-255)

t<sub>SAMPLE</sub> is the sample time

#### Table 2-46 • STC Bits Function

| Name | Bits  | Function            |

|------|-------|---------------------|

| STC  | [7:0] | Sample time control |

Sample time is computed based on the period of ADCCLK.

#### **Distribution Phase**

The second phase is called the distribution phase. During distribution phase, the ADC computes the equivalent digital value from the value stored in the input capacitor. In this phase, the output signal SAMPLE goes back to '0', indicating the sample is completed; but the BUSY signal remains '1', indicating the ADC is still busy for distribution. The distribution time depends strictly on the number of bits. If the ADC is configured as a 10-bit ADC, then 10 ADCCLK cycles are needed. EQ 8 describes the distribution time.

$$t_{distrib} = N \times t_{ADCCLK}$$

EQ 21

N: Number of bits

#### Post-Calibration Phase

The last phase is the post-calibration phase. This is an optional phase. The post-calibration phase takes two ADCCLK cycles. The output BUSY signal will remain '1' until the post-calibration phase is completed. If the post-calibration phase is skipped, then the BUSY signal goes to '0' after distribution phase. As soon as BUSY signal goes to '0', the DATAVALID signal goes to '1', indicating the digital result is available on the RESULT output signals. DATAVAILD will remain '1' until the next ADCSTART is asserted. Microsemi recommends enabling post-calibration to compensate for drift and temperature-dependent effects. This ensures that the ADC remains consistent over time and with temperature. The post-calibration phase is enabled by bit 3 of the Mode register. EQ 9 describes the post-calibration time.

$$t_{post-cal} = MODE[3] \times (2 \times t_{ADCCLK})$$

EQ 22

MODE[3]: Bit 3 of the Mode register, described in Table 2-41 on page 2-106.

The calculation for the conversion time for the ADC is summarized in EQ 23.

EQ 23

t<sub>conv</sub>: conversion time

$t_{sync\_read}$ : maximum time for a signal to synchronize with SYSCLK. For calculation purposes, the worst case is a period of SYSCLK,  $t_{SYSCLK}$ .

t<sub>sample</sub>: Sample time t<sub>distrib</sub>: Distribution time

t<sub>post-cal</sub>: Post-calibration time

$t_{sync\_write}$ : Maximum time for a signal to synchronize with SYSCLK. For calculation purposes, the worst case is a period of SYSCLK,  $t_{SYSCLK}$ .

2-109 Revision 6

# **Typical Performance Characteristics**

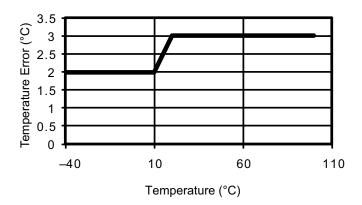

Temperature Errror vs. Die Temperature

Figure 2-94 • Temperature Error

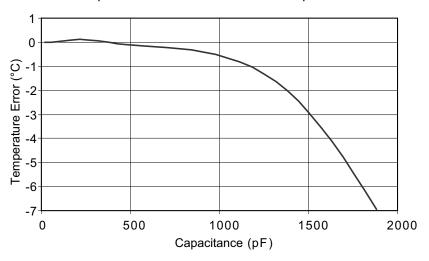

Temperature Error vs. Interconnect Capacitance

Figure 2-95 • Effect of External Sensor Capacitance

2-115 Revision 6

Table 2-50 • ADC Characteristics in Direct Input Mode (continued)

Commercial Temperature Range Conditions, T<sub>J</sub> = 85°C (unless noted otherwise),

Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter  | Description                  | Condition   | Min. | Тур.  | Max.  | Units |

|------------|------------------------------|-------------|------|-------|-------|-------|

| Dynamic Po | erformance                   |             |      |       |       |       |

| SNR        | Signal-to-Noise Ratio        | 8-bit mode  | 48.0 | 49.5  |       | dB    |

|            |                              | 10-bit mode | 58.0 | 60.0  |       | dB    |

|            |                              | 12-bit mode | 62.9 | 64.5  |       | dB    |

| SINAD      | Signal-to-Noise Distortion   | 8-bit mode  | 47.6 | 49.5  |       | dB    |

|            |                              | 10-bit mode | 57.4 | 59.8  |       | dB    |

|            |                              | 12-bit mode | 62.0 | 64.2  |       | dB    |

| THD        | Total Harmonic<br>Distortion | 8-bit mode  |      | -74.4 | -63.0 | dBc   |

|            |                              | 10-bit mode |      | -78.3 | -63.0 | dBc   |

|            |                              | 12-bit mode |      | -77.9 | -64.4 | dBc   |

| ENOB       | Effective Number of Bits     | 8-bit mode  | 7.6  | 7.9   |       | bits  |

|            |                              | 10-bit mode | 9.5  | 9.6   |       | bits  |

|            |                              | 12-bit mode | 10.0 | 10.4  |       | bits  |

| Conversion | Rate                         |             |      |       |       |       |

|            | Conversion Time              | 8-bit mode  | 1.7  |       |       | μs    |

|            |                              | 10-bit mode | 1.8  |       |       | μs    |

|            |                              | 12-bit mode | 2    |       |       | μs    |

|            | Sample Rate                  | 8-bit mode  |      |       | 600   | Ksps  |

|            |                              | 10-bit mode |      |       | 550   | Ksps  |

|            |                              | 12-bit mode |      |       | 500   | Ksps  |

## Notes:

- 1. Accuracy of the external reference is 2.56 V  $\pm$  4.6 mV.

- 2. Data is based on characterization.

- 3. The sample rate is time-shared among active analog inputs.

2-121 Revision 6

For Fusion devices requiring Level 3 and/or Level 4 compliance, the board drivers connected to Fusion I/Os need to have 10 k $\Omega$  (or lower) output drive resistance at hot insertion, and 1 k $\Omega$  (or lower) output drive resistance at hot removal. This is the resistance of the transmitter sending a signal to the Fusion I/O, and no additional resistance is needed on the board. If that cannot be assured, three levels of staging can be used to meet Level 3 and/or Level 4 compliance. Cards with two levels of staging should have the following sequence:

- 1. Grounds

- 2. Powers, I/Os, other pins

## **Cold-Sparing Support**

Cold-sparing means that a subsystem with no power applied (usually a circuit board) is electrically connected to the system that is in operation. This means that all input buffers of the subsystem must present very high input impedance with no power applied so as not to disturb the operating portion of the system.

Pro I/O banks and standard I/O banks fully support cold-sparing.

For Pro I/O banks, standards such as PCI that require I/O clamp diodes, can also achieve cold-sparing compliance, since clamp diodes get disconnected internally when the supplies are at 0 V.

For Advanced I/O banks, since the I/O clamp diode is always active, cold-sparing can be accomplished either by employing a bus switch to isolate the device I/Os from the rest of the system or by driving each advanced I/O pin to 0 V.

If Standard I/O banks are used in applications requiring cold-sparing, a discharge path from the power supply to ground should be provided. This can be done with a discharge resistor or a switched resistor. This is necessary because the standard I/O buffers do not have built-in I/O clamp diodes.

If a resistor is chosen, the resistor value must be calculated based on decoupling capacitance on a given power supply on the board (this decoupling capacitor is in parallel with the resistor). The RC time constant should ensure full discharge of supplies before cold-sparing functionality is required. The resistor is necessary to ensure that the power pins are discharged to ground every time there is an interruption of power to the device.

I/O cold-sparing may add additional current if the pin is configured with either a pull-up or pull down resistor and driven in the opposite direction. A small static current is induced on each IO pin when the pin is driven to a voltage opposite to the weak pull resistor. The current is equal to the voltage drop across the input pin divided by the pull resistor. Please refer to Table 2-95 on page 2-169, Table 2-96 on page 2-169, and Table 2-97 on page 2-171 for the specific pull resistor value for the corresponding I/O standard.

For example, assuming an LVTTL 3.3 V input pin is configured with a weak Pull-up resistor, a current will flow through the pull-up resistor if the input pin is driven low. For an LVTTL 3.3 V, pull-up resistor is ~45 k $\Omega$  and the resulting current is equal to 3.3 V / 45 k $\Omega$  = 73  $\mu$ A for the I/O pin. This is true also when a weak pull-down is chosen and the input pin is driven high. Avoiding this current can be done by driving the input low when a weak pull-down resistor is used, and driving it high when a weak pull-up resistor is used.

In Active and Static modes, this current draw can occur in the following cases:

- · Input buffers with pull-up, driven low

- · Input buffers with pull-down, driven high

- Bidirectional buffers with pull-up, driven low

- · Bidirectional buffers with pull-down, driven high

- Output buffers with pull-up, driven low

- Output buffers with pull-down, driven high

- Tristate buffers with pull-up, driven low

- · Tristate buffers with pull-down, driven high

Temporary overshoots are allowed according to Table 3-4 on page 3-4.

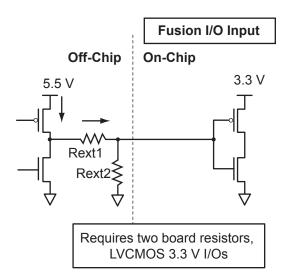

#### Solution 1

Figure 2-103 • Solution 1

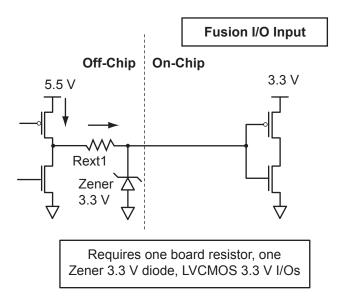

## Solution 2

The board-level design must ensure that the reflected waveform at the pad does not exceed limits provided in Table 3-4 on page 3-4. This is a long-term reliability requirement.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the external resistors and Zener, as shown in Figure 2-104. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

#### Solution 2

Figure 2-104 • Solution 2

2-145 Revision 6

Table 2-77 • Comparison Table for 5 V-Compliant Receiver Scheme

| Scheme | <b>Board Components</b>                                                                                                                                           | Speed                    | Current Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 1    | Two resistors                                                                                                                                                     | Low to high <sup>1</sup> | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2 F    | Resistor and Zener 3.3 V                                                                                                                                          | Medium                   | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3 E    | Bus switch                                                                                                                                                        | High                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| F      | Minimum resistor value <sup>2</sup> R = 47 $\Omega$ at T <sub>J</sub> = 70°C R = 150 $\Omega$ at T <sub>J</sub> = 85°C R = 420 $\Omega$ at T <sub>J</sub> = 100°C | Medium                   | Maximum diode current at 100% duty cycle, signal constantly at '1' $52.7 \text{ mA at T}_J = 70^{\circ}\text{C} / 10\text{-year lifetime}$ $16.5 \text{ mA at T}_J = 85^{\circ}\text{C} / 10\text{-year lifetime}$ $5.9 \text{ mA at T}_J = 100^{\circ}\text{C} / 10\text{-year lifetime}$ For duty cycles other than 100%, the currents can be increased by a factor = 1 / (duty cycle). Example: 20% duty cycle at 70°C Maximum current = $(1/0.2)$ * 52.7 mA = 5 * 52.7 mA = 263.5 mA |

## Notes:

- 1. Speed and current consumption increase as the board resistance values decrease.

- 2. Resistor values ensure I/O diode long-term reliability.

2-147 Revision 6

Fusion Family of Mixed Signal FPGAs

Table 2-109 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 3.0 V

Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade  | t                 | <b>t</b>        | <b>t</b>         | <b>t</b>        | <b>t</b>          | <b>+</b>        | t               | t               | t               | Units  |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|--------|

| Suengui           | Grade           | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Ullita |

| 2 mA              | Std.            | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns     |

|                   | -1              | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns     |

|                   | -2 <sup>2</sup> | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns     |

| 4 mA              | Std.            | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns     |

|                   | -1              | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns     |

|                   | -2              | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns     |

| 6 mA              | Std.            | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns     |

|                   | -1              | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns     |

|                   | -2              | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns     |

| 8 mA              | Std.            | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns     |

|                   | <b>–</b> 1      | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns     |

|                   | -2              | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns     |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-117 • 2.5 V LVCMOS High Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 2.3 V

Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 8.20            | 0.04             | 1.29            | 0.43              | 7.24            | 8.20            | 2.03            | 1.91            | ns    |

|                   | -1             | 0.56              | 6.98            | 0.04             | 1.10            | 0.36              | 6.16            | 6.98            | 1.73            | 1.62            | ns    |

|                   | -2             | 0.49              | 6.13            | 0.03             | 0.96            | 0.32              | 5.41            | 6.13            | 1.52            | 1.43            | ns    |

| 4 mA              | Std.           | 0.66              | 8.20            | 0.04             | 1.29            | 0.43              | 7.24            | 8.20            | 2.03            | 1.91            | ns    |

|                   | -1             | 0.56              | 6.98            | 0.04             | 1.10            | 0.36              | 6.16            | 6.98            | 1.73            | 1.62            | ns    |

|                   | -2             | 0.49              | 6.13            | 0.03             | 0.96            | 0.32              | 5.41            | 6.13            | 1.52            | 1.43            | ns    |

| 6 mA              | Std.           | 0.66              | 4.77            | 0.04             | 1.29            | 0.43              | 4.55            | 4.77            | 2.38            | 2.55            | ns    |

|                   | -1             | 0.56              | 4.05            | 0.04             | 1.10            | 0.36              | 3.87            | 4.05            | 2.03            | 2.17            | ns    |

|                   | -2             | 0.49              | 3.56            | 0.03             | 0.96            | 0.32              | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

| 8 mA              | Std.           | 0.66              | 4.77            | 0.04             | 1.29            | 0.43              | 4.55            | 4.77            | 2.38            | 2.55            | ns    |

|                   | -1             | 0.56              | 4.05            | 0.04             | 1.10            | 0.36              | 3.87            | 4.05            | 2.03            | 2.17            | ns    |

|                   | -2             | 0.49              | 3.56            | 0.03             | 0.96            | 0.32              | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Table 2-132 • 1.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 12.33           | 0.04             | 1.42            | 0.43              | 11.79           | 12.33           | 2.45            | 2.32            | ns    |

|                   | -1             | 0.56              | 10.49           | 0.04             | 1.21            | 0.36              | 10.03           | 10.49           | 2.08            | 1.98            | ns    |

|                   | -2             | 0.49              | 9.21            | 0.03             | 1.06            | 0.32              | 8.81            | 9.21            | 1.83            | 1.73            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-133 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.65            | 0.04             | 1.42            | 0.43              | 6.31            | 7.65            | 2.45            | 2.45            | ns    |

|                   | <b>–</b> 1     | 0.56              | 6.50            | 0.04             | 1.21            | 0.36              | 5.37            | 6.50            | 2.08            | 2.08            | ns    |

|                   | -2             | 0.49              | 5.71            | 0.03             | 1.06            | 0.32              | 4.71            | 5.71            | 1.83            | 1.83            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

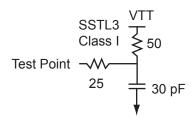

#### SSTL3 Class I

Stub-Speed Terminated Logic for 3.3 V memory bus standard (JESD8-8). Fusion devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-162 • Minimum and Maximum DC Input and Output Levels

| SSTL3 Class I     |           | VIL        | VIH        |           | VOL       | VOH        | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|------------|------------|-----------|-----------|------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 14 mA             | -0.3      | VREF - 0.2 | VREF + 0.2 | 3.6       | 0.7       | VCCI - 1.1 | 14  | 14 | 54                      | 51                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

#### Figure 2-132 • AC Loading

Table 2-163 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF - 0.2    | VREF + 0.2     | 1.5                  | 1.5             | 1.485          | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

## Timing Characteristics

Table 2-164 • SSTL3 Class I

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.5 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.31            | 0.04             | 1.25            | 0.43              | 2.35            | 1.84            |                 |                 | 4.59             | 4.07             | ns    |

| <b>-1</b>      | 0.56              | 1.96            | 0.04             | 1.06            | 0.36              | 2.00            | 1.56            |                 |                 | 3.90             | 3.46             | ns    |

| -2             | 0.49              | 1.72            | 0.03             | 0.93            | 0.32              | 1.75            | 1.37            |                 |                 | 3.42             | 3.04             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-207 Revision 6

#### **ISP**

Fusion devices support IEEE 1532 ISP via JTAG and require a single VPUMP voltage of 3.3 V during programming. In addition, programming via a microcontroller in a target system can be achieved. Refer to the standard or the "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" chapter of the *Fusion FPGA Fabric User's Guide* for more details.

### JTAG IEEE 1532

## **Programming with IEEE 1532**

Fusion devices support the JTAG-based IEEE1532 standard for ISP. As part of this support, when a Fusion device is in an unprogrammed state, all user I/O pins are disabled. This is achieved by keeping the global IO\_EN signal deactivated, which also has the effect of disabling the input buffers. Consequently, the SAMPLE instruction will have no effect while the Fusion device is in this unprogrammed state—different behavior from that of the ProASICPLUS® device family. This is done because SAMPLE is defined in the IEEE1532 specification as a noninvasive instruction. If the input buffers were to be enabled by SAMPLE temporarily turning on the I/Os, then it would not truly be a noninvasive instruction. Refer to the standard or the "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" chapter of the Fusion FPGA Fabric User's Guide for more details.

### **Boundary Scan**

Fusion devices are compatible with IEEE Standard 1149.1, which defines a hardware architecture and the set of mechanisms for boundary scan testing. The basic Fusion boundary scan logic circuit is composed of the test access port (TAP) controller, test data registers, and instruction register (Figure 2-146 on page 2-230). This circuit supports all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) and the optional IDCODE instruction (Table 2-185 on page 2-230).

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI, TDO (test data input and output), TMS (test mode selector), and TRST (test reset input). TMS, TDI, and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary scan test usage. Refer to the "JTAG Pins" section on page 2-226 for pull-up/-down recommendations for TDO and TCK pins. The TAP controller is a 4-bit state machine (16 states) that operates as shown in Figure 2-146 on page 2-230. The 1s and 0s represent the values that must be present on TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the instruction register or the data register is operating in that state.

Table 2-184 • TRST and TCK Pull-Down Recommendations

| VJTAG          | Tie-Off Resistance*          |

|----------------|------------------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ                |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ                |

| VJTAG at 1.8 V | 500 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                |

Note: \*Equivalent parallel resistance if more than one device is on JTAG chain.

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset state. To guarantee a reset of the controller from any of the possible states, TMS must remain High for five TCK cycles. The TRST pin can also be used to asynchronously place the TAP controller in the Test-Logic-Reset state.

Fusion devices support three types of test data registers: bypass, device identification, and boundary scan. The bypass register is selected when no other register needs to be accessed in a device. This speeds up test data transfer to other devices in a test data path. The 32-bit device identification register is a shift register with four fields (LSB, ID number, part number, and version). The boundary scan register observes and controls the state of each I/O pin. Each I/O cell has three boundary scan register cells, each with a serial-in, serial-out, parallel-in, and parallel-out pin.

The serial pins are used to serially connect all the boundary scan register cells in a device into a boundary scan register chain, which starts at the TDI pin and ends at the TDO pin. The parallel ports are

2-229 Revision 6

Table 3-1 • Absolute Maximum Ratings (continued)

| Symbol                        | Parameter                                       | Commercial    | Industrial    | Units |

|-------------------------------|-------------------------------------------------|---------------|---------------|-------|

| AV, AC                        | Unpowered, ADC reset asserted or unconfigured   | -11.0 to 12.6 | -11.0 to 12.0 | V     |

|                               | Analog input (+16 V to +2 V prescaler range)    | -0.4 to 12.6  | -0.4 to 12.0  | V     |

|                               | Analog input (+1 V to +0.125 V prescaler range) | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Analog input (–16 V to –2 V prescaler range)    | -11.0 to 0.4  | -11.0 to 0.4  | V     |

|                               | Analog input (-1 V to -0.125 V prescaler range) | -3.75 to 0.4  | -3.75 to 0.4  | V     |

|                               | Analog input (direct input to ADC)              | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Digital input                                   | -0.4 to 12.6  | -0.4 to 12.0  | V     |

| AG                            | Unpowered, ADC reset asserted or unconfigured   | -11.0 to 12.6 | -11.0 to 12.0 | V     |

|                               | Low Current Mode (1 μA, 3 μA, 10 μA, 30 μA)     | -0.4 to 12.6  | -0.4 to 12.0  | V     |

|                               | Low Current Mode (–1 μA, –3 μA, –10 μA, –30 μA) | -11.0 to 0.4  | -11.0 to 0.4  | V     |

|                               | High Current Mode <sup>3</sup>                  | -11.0 to 12.6 | -11.0 to 12.0 | V     |

| AT                            | Unpowered, ADC reset asserted or unconfigured   | -0.4 to 16.0  | -0.4 to 15.0  | V     |

|                               | Analog input (+16 V, 4 V prescaler range)       | -0.4 to 16.0  | -0.4 to 15.0  | V     |

|                               | Analog input (direct input to ADC)              | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Digital input                                   | -0.4 to 16.0  | -0.4 to 15.0  | V     |

| T <sub>STG</sub> <sup>4</sup> | Storage temperature                             | <b>–</b> 65 t | to +150       | °C    |

| T <sub>J</sub> <sup>4</sup>   | Junction temperature                            | +             | 125           | °C    |

## Notes:

<sup>1.</sup> The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-4.

<sup>2.</sup> Analog data not valid beyond 3.65 V.

<sup>3.</sup> The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

<sup>4.</sup> For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.

# **Calculating Power Dissipation**

## **Quiescent Supply Current**

Table 3-8 • AFS1500 Quiescent Supply Current Characteristics

| Parameter          | Description                              | Conditions                                                                       | Temp.                  | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------------------|----------------------------------------------------------------------------------|------------------------|------|------|------|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current                  | Operational standby <sup>4</sup> ,<br>VCC = 1.575 V                              | $T_J = 25^{\circ}C$    |      | 20   | 40   | mA   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 85°C  |      | 32   | 65   | mA   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 100°C |      | 59   | 120  | mA   |

|                    |                                          | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VCC = 0 V              |                        |      | 0    | 0    | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies                    | Operational standby <sup>4</sup> ,                                               | $T_J = 25^{\circ}C$    |      | 9.8  | 13   | mA   |

|                    | current                                  | VCC33 = 3.63 V                                                                   | T <sub>J</sub> = 85°C  |      | 10.7 | 14   | mA   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 100°C |      | 10.8 | 15   | mA   |

|                    |                                          | Operational standby, only Analog<br>Quad and –3.3 V output ON,<br>VCC33 = 3.63 V | T <sub>J</sub> = 25°C  |      | 0.31 | 2    | mA   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 85°C  |      | 0.35 | 2    | mA   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 100°C |      | 0.45 | 2    | mA   |

|                    |                                          | Standby mode <sup>5</sup> , VCC33 = 3.63 V                                       | T <sub>J</sub> = 25°C  |      | 2.9  | 3.6  | mA   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 85°C  |      | 2.9  | 4    | mA   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 100°C |      | 3.3  | 6    | mA   |

|                    | Sleep mode <sup>6</sup> , VCC33 = 3.63 V | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                                         | T <sub>J</sub> = 25°C  |      | 17   | 19   | μΑ   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 85°C  |      | 18   | 20   | μΑ   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 100°C |      | 24   | 25   | μΑ   |

| ICCI <sup>3</sup>  | I/O quiescent current                    | Operational standby <sup>4</sup> ,                                               | T <sub>J</sub> = 25°C  |      | 417  | 649  | μΑ   |

|                    |                                          | Standby mode, and Sleep Mode <sup>6</sup> , VCCIx = $3.63 \text{ V}$             | T <sub>J</sub> = 85°C  |      | 417  | 649  | μΑ   |

|                    |                                          |                                                                                  | T <sub>J</sub> = 100°C |      | 417  | 649  | μΑ   |

#### Notes:

- 1. ICC is the 1.5 V power supplies, ICC and ICC15A.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

Table 3-12 • Summary of I/O Input Buffer Power (per pin)—Default I/O Software Settings (continued)

|                                  | VCCI (V) | Static Power<br>PDC7 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (μW/MHz) <sup>2</sup> |

|----------------------------------|----------|----------------------------------------|---------------------------------------------|

| Applicable to Advanced I/O Banks | <u>'</u> |                                        |                                             |

| Single-Ended                     |          |                                        |                                             |

| 3.3 V LVTTL/LVCMOS               | 3.3      | _                                      | 16.69                                       |

| 2.5 V LVCMOS                     | 2.5      | _                                      | 5.12                                        |

| 1.8 V LVCMOS                     | 1.8      | _                                      | 2.13                                        |

| 1.5 V LVCMOS (JESD8-11)          | 1.5      | _                                      | 1.45                                        |

| 3.3 V PCI                        | 3.3      | _                                      | 18.11                                       |

| 3.3 V PCI-X                      | 3.3      | _                                      | 18.11                                       |

| Differential                     |          |                                        |                                             |

| LVDS                             | 2.5      | 2.26                                   | 1.20                                        |

| LVPECL                           | 3.3      | 5.72                                   | 1.87                                        |

| Applicable to Standard I/O Banks |          |                                        |                                             |

| 3.3 V LVTTL/LVCMOS               | 3.3      | _                                      | 16.79                                       |

| 2.5 V LVCMOS                     | 2.5      | _                                      | 5.19                                        |

| 1.8 V LVCMOS                     | 1.8      | _                                      | 2.18                                        |

| 1.5 V LVCMOS (JESD8-11)          | 1.5      | _                                      | 1.52                                        |

## Notes:

- 1. PDC7 is the static power (where applicable) measured on VCCI.

- 2. PAC9 is the total dynamic power measured on VCC and VCCI.

3-19 Revision 6

$P_{S-CFII} = 0 W$

$P_{C-CFII} = 0 W$

$P_{NET} = 0 W$

P<sub>LOGIC</sub> = 0 W

## I/O Input and Output Buffer Contribution—P<sub>I/O</sub>

This example uses LVTTL 3.3 V I/O cells. The output buffers are 12 mA-capable, configured with high output slew and driving a 35 pF output load.

$F_{CLK} = 50 \text{ MHz}$

Number of input pins used:  $N_{INPUTS} = 30$ Number of output pins used:  $N_{OUTPUTS} = 40$ Estimated I/O buffer toggle rate:  $\alpha_2 = 0.1$  (10%) Estimated IO buffer enable rate:  $\beta_1 = 1$  (100%)

## **Operating Mode**

$P_{INPUTS}$  =  $N_{INPUTS}$  \*  $(\alpha_2 / 2)$  \* PAC9 \*  $F_{CLK}$

$P_{INPUTS} = 30 * (0.1 / 2) * 0.01739 * 50$

$P_{INPUTS} = 1.30 \text{ mW}$

$P_{OUTPUTS} = N_{OUTPUTS} * (\alpha_2 / 2) * \beta_1 * PAC10 * F_{CLK}$

P<sub>OUTPUTS</sub> = 40 \* (0.1 / 2) \* 1 \* 0.4747 \* 50

$P_{OUTPUTS} = 47.47 \text{ mW}$

$P_{I/O} = P_{INPUTS} + P_{OUTPUTS}$

$P_{I/O} = 1.30 \text{ mW} + 47.47 \text{ mW}$

$P_{I/O} = 48.77 \text{ mW}$

### Standby Mode and Sleep Mode

P<sub>INPUTS</sub> = 0 W

P<sub>OUTPUTS</sub> = 0 W

$P_{I/O} = 0 W$

## RAM Contribution—P<sub>MEMORY</sub>

Frequency of Read Clock:  $F_{READ-CLOCK} = 10 \text{ MHz}$

Frequency of Write Clock: F<sub>WRITE-CLOCK</sub> = 10 MHz

Number of RAM blocks:  $N_{BLOCKS} = 20$

Estimated RAM Read Enable Rate:  $\beta_2$  = 0.125 (12.5%) Estimated RAM Write Enable Rate:  $\beta_3$  = 0.125 (12.5%)

#### **Operating Mode**

$P_{MEMORY} = (N_{BLOCKS} * PAC11 * \beta_2 * F_{READ-CLOCK}) + (N_{BLOCKS} * PAC12 * \beta_3 * F_{WRITE-CLOCK})$

P<sub>MEMORY</sub> = (20 \* 0.025 \* 0.125 \* 10) + (20 \* 0.030 \* 0.125 \* 10)

$P_{MEMORY} = 1.38 \text{ mW}$

## Standby Mode and Sleep Mode

$P_{MEMORY} = 0 W$

3-29 Revision 6

| PQ208         |                 |                 |  |  |  |

|---------------|-----------------|-----------------|--|--|--|

| Pin<br>Number | AFS250 Function | AFS600 Function |  |  |  |

| 1             | VCCPLA          | VCCPLA          |  |  |  |

| 2             | VCOMPLA         | VCOMPLA         |  |  |  |

| 3             | GNDQ            | GAA2/IO85PDB4V0 |  |  |  |

| 4             | VCCIB3          | IO85NDB4V0      |  |  |  |

| 5             | GAA2/IO76PDB3V0 | GAB2/IO84PDB4V0 |  |  |  |

| 6             | IO76NDB3V0      | IO84NDB4V0      |  |  |  |

| 7             | GAB2/IO75PDB3V0 | GAC2/IO83PDB4V0 |  |  |  |

| 8             | IO75NDB3V0      | IO83NDB4V0      |  |  |  |

| 9             | NC              | IO77PDB4V0      |  |  |  |

| 10            | NC              | IO77NDB4V0      |  |  |  |

| 11            | VCC             | IO76PDB4V0      |  |  |  |

| 12            | GND             | IO76NDB4V0      |  |  |  |

| 13            | VCCIB3          | VCC             |  |  |  |

| 14            | IO72PDB3V0      | GND             |  |  |  |

| 15            | IO72NDB3V0      | VCCIB4          |  |  |  |

| 16            | GFA2/IO71PDB3V0 | GFA2/IO75PDB4V0 |  |  |  |

| 17            | IO71NDB3V0      | IO75NDB4V0      |  |  |  |

| 18            | GFB2/IO70PDB3V0 | GFC2/IO73PDB4V0 |  |  |  |

| 19            | IO70NDB3V0      | IO73NDB4V0      |  |  |  |

| 20            | GFC2/IO69PDB3V0 | VCCOSC          |  |  |  |

| 21            | IO69NDB3V0      | XTAL1           |  |  |  |

| 22            | VCC             | XTAL2           |  |  |  |

| 23            | GND             | GNDOSC          |  |  |  |

| 24            | VCCIB3          | GFC1/IO72PDB4V0 |  |  |  |

| 25            | GFC1/IO68PDB3V0 | GFC0/IO72NDB4V0 |  |  |  |

| 26            | GFC0/IO68NDB3V0 | GFB1/IO71PDB4V0 |  |  |  |

| 27            | GFB1/IO67PDB3V0 | GFB0/IO71NDB4V0 |  |  |  |

| 28            | GFB0/IO67NDB3V0 | GFA1/IO70PDB4V0 |  |  |  |

| 29            | VCCOSC          | GFA0/IO70NDB4V0 |  |  |  |

| 30            | XTAL1           | IO69PDB4V0      |  |  |  |

| 31            | XTAL2           | IO69NDB4V0      |  |  |  |

| 32            | GNDOSC          | VCC             |  |  |  |

| 33            | GEB1/IO62PDB3V0 | GND             |  |  |  |

| 34            | GEB0/IO62NDB3V0 | VCCIB4          |  |  |  |

| 35            | GEA1/IO61PDB3V0 | GEC1/IO63PDB4V0 |  |  |  |

| 36            | GEA0/IO61NDB3V0 | GEC0/IO63NDB4V0 |  |  |  |

| 37            | GEC2/IO60PDB3V0 | GEB1/IO62PDB4V0 |  |  |  |

| Pin Number         AFS250 Function         AFS600 Funct           38         IO60NDB3V0         GEB0/IO62NDB | ion  |

|--------------------------------------------------------------------------------------------------------------|------|

|                                                                                                              | ion  |

| 38 IO60NDB3V0 GEB0/IO62NDE                                                                                   |      |

|                                                                                                              | 84V0 |

| 39 GND GEA1/IO61PDE                                                                                          | 84V0 |

| 40 VCCIB3 GEA0/IO61NDE                                                                                       | 84V0 |

| 41 GEB2/IO59PDB3V0 GEC2/IO60PDE                                                                              | 84V0 |

| 42 IO59NDB3V0 IO60NDB4V                                                                                      | 0    |

| 43 GEA2/IO58PDB3V0 VCCIB4                                                                                    |      |

| 44 IO58NDB3V0 GNDQ                                                                                           |      |

| 45 VCC VCC                                                                                                   |      |

| 45 VCC VCC                                                                                                   |      |

| 46 VCCNVM VCCNVM                                                                                             |      |

| 47 GNDNVM GNDNVM                                                                                             |      |

| 48 GND GND                                                                                                   |      |

| 49 VCC15A VCC15A                                                                                             |      |

| 50 PCAP PCAP                                                                                                 |      |

| 51 NCAP NCAP                                                                                                 |      |

| 52 VCC33PMP VCC33PMF                                                                                         | )    |

| 53 VCC33N VCC33N                                                                                             |      |

| 54 GNDA GNDA                                                                                                 |      |

| 55 GNDAQ GNDAQ                                                                                               |      |

| 56 NC AV0                                                                                                    |      |

| 57 NC AC0                                                                                                    |      |

| 58 NC AG0                                                                                                    |      |

| 59 NC AT0                                                                                                    |      |

| 60 NC ATRTNO                                                                                                 |      |

| 61 NC AT1                                                                                                    |      |

| 62 NC AG1                                                                                                    |      |

| 63 NC AC1                                                                                                    |      |

| 64 NC AV1                                                                                                    |      |

| 65 AV0 AV2                                                                                                   |      |

| 66 AC0 AC2                                                                                                   |      |

| 67 AG0 AG2                                                                                                   |      |

| 68 AT0 AT2                                                                                                   |      |

| 69 ATRTN0 ATRTN1                                                                                             |      |

| 70 AT1 AT3                                                                                                   |      |

| 71 AG1 AG3                                                                                                   |      |

| 72 AC1 AC3                                                                                                   |      |

| 73 AV1 AV3                                                                                                   |      |

4-8 Revision 6

|            | FG256           |                 |                 |                  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |

| C7         | IO09RSB0V0      | IO12RSB0V0      | IO06NDB0V0      | IO09NDB0V1       |  |

| C8         | IO14RSB0V0      | IO22RSB0V0      | IO16PDB1V0      | IO23PDB1V0       |  |

| C9         | IO15RSB0V0      | IO23RSB0V0      | IO16NDB1V0      | IO23NDB1V0       |  |

| C10        | IO22RSB0V0      | IO30RSB0V0      | IO25NDB1V1      | IO31NDB1V1       |  |

| C11        | IO20RSB0V0      | IO31RSB0V0      | IO25PDB1V1      | IO31PDB1V1       |  |

| C12        | VCCIB0          | VCCIB0          | VCCIB1          | VCCIB1           |  |

| C13        | GBB1/IO28RSB0V0 | GBC1/IO35RSB0V0 | GBC1/IO26PPB1V1 | GBC1/IO40PPB1V2  |  |

| C14        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |  |

| C15        | GND             | GND             | GND             | GND              |  |

| C16        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |  |

| D1         | GFC2/IO50NPB3V0 | IO75NDB3V0      | IO84NDB4V0      | IO124NDB4V0      |  |

| D2         | GFA2/IO51NDB3V0 | GAB2/IO75PDB3V0 | GAB2/IO84PDB4V0 | GAB2/IO124PDB4V0 |  |

| D3         | GAC2/IO51PDB3V0 | IO76NDB3V0      | IO85NDB4V0      | IO125NDB4V0      |  |

| D4         | GAA2/IO52PDB3V0 | GAA2/IO76PDB3V0 | GAA2/IO85PDB4V0 | GAA2/IO125PDB4V0 |  |

| D5         | GAB2/IO52NDB3V0 | GAB0/IO02RSB0V0 | GAB0/IO02NPB0V0 | GAB0/IO02NPB0V0  |  |

| D6         | GAC0/IO04RSB0V0 | GAC0/IO04RSB0V0 | GAC0/IO03NDB0V0 | GAC0/IO03NDB0V0  |  |

| D7         | IO08RSB0V0      | IO13RSB0V0      | IO06PDB0V0      | IO09PDB0V1       |  |

| D8         | NC              | IO20RSB0V0      | IO14NDB0V1      | IO15NDB0V2       |  |

| D9         | NC              | IO21RSB0V0      | IO14PDB0V1      | IO15PDB0V2       |  |

| D10        | IO21RSB0V0      | IO28RSB0V0      | IO23PDB1V1      | IO37PDB1V2       |  |

| D11        | IO23RSB0V0      | GBB0/IO36RSB0V0 | GBB0/IO27NDB1V1 | GBB0/IO41NDB1V2  |  |

| D12        | NC              | NC              | VCCIB1          | VCCIB1           |  |

| D13        | GBA2/IO31PDB1V0 | GBA2/IO40PDB1V0 | GBA2/IO30PDB2V0 | GBA2/IO44PDB2V0  |  |

| D14        | GBB2/IO31NDB1V0 | IO40NDB1V0      | IO30NDB2V0      | IO44NDB2V0       |  |

| D15        | GBC2/IO32PDB1V0 | GBB2/IO41PDB1V0 | GBB2/IO31PDB2V0 | GBB2/IO45PDB2V0  |  |

| D16        | GCA2/IO32NDB1V0 | IO41NDB1V0      | IO31NDB2V0      | IO45NDB2V0       |  |

| E1         | GND             | GND             | GND             | GND              |  |

| E2         | GFB0/IO48NPB3V0 | IO73NDB3V0      | IO81NDB4V0      | IO118NDB4V0      |  |

| E3         | GFB2/IO50PPB3V0 | IO73PDB3V0      | IO81PDB4V0      | IO118PDB4V0      |  |

| E4         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |  |

| E5         | NC              | IO74NPB3V0      | IO83NPB4V0      | IO123NPB4V0      |  |

| E6         | NC              | IO08RSB0V0      | IO04NPB0V0      | IO05NPB0V1       |  |

| E7         | GND             | GND             | GND             | GND              |  |

| E8         | NC              | IO18RSB0V0      | IO08PDB0V1      | IO11PDB0V1       |  |

| E9         | NC              | NC              | IO20NDB1V0      | IO27NDB1V1       |  |

| E10        | GND             | GND             | GND             | GND              |  |

| E11        | IO24RSB0V0      | GBB1/IO37RSB0V0 | GBB1/IO27PDB1V1 | GBB1/IO41PDB1V2  |  |

| E12        | NC              | IO50PPB1V0      | IO33PSB2V0      | IO48PSB2V0       |  |

|            | 1               | 1               |                 | 1                |  |

4-13 Revision 6

| FG256      |                 |                 |                 |                  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |

| M15        | TRST            | TRST            | TRST            | TRST             |  |

| M16        | GND             | GND             | GND             | GND              |  |

| N1         | GEB2/IO42PDB3V0 | GEB2/IO59PDB3V0 | GEB2/IO59PDB4V0 | GEB2/IO86PDB4V0  |  |

| N2         | GEA2/IO42NDB3V0 | IO59NDB3V0      | IO59NDB4V0      | IO86NDB4V0       |  |

| N3         | NC              | GEA2/IO58PPB3V0 | GEA2/IO58PPB4V0 | GEA2/IO85PPB4V0  |  |

| N4         | VCC33PMP        | VCC33PMP        | VCC33PMP        | VCC33PMP         |  |

| N5         | VCC15A          | VCC15A          | VCC15A          | VCC15A           |  |

| N6         | NC              | NC              | AG0             | AG0              |  |

| N7         | AC1             | AC1             | AC3             | AC3              |  |

| N8         | AG3             | AG3             | AG5             | AG5              |  |

| N9         | AV3             | AV3             | AV5             | AV5              |  |

| N10        | AG4             | AG4             | AG6             | AG6              |  |

| N11        | NC              | NC              | AC8             | AC8              |  |

| N12        | GNDA            | GNDA            | GNDA            | GNDA             |  |

| N13        | VCC33A          | VCC33A          | VCC33A          | VCC33A           |  |

| N14        | VCCNVM          | VCCNVM          | VCCNVM          | VCCNVM           |  |

| N15        | TCK             | TCK             | TCK             | TCK              |  |

| N16        | TDI             | TDI             | TDI             | TDI              |  |

| P1         | VCCNVM          | VCCNVM          | VCCNVM          | VCCNVM           |  |

| P2         | GNDNVM          | GNDNVM          | GNDNVM          | GNDNVM           |  |

| P3         | GNDA            | GNDA            | GNDA            | GNDA             |  |

| P4         | NC              | NC              | AC0             | AC0              |  |

| P5         | NC              | NC              | AG1             | AG1              |  |

| P6         | NC              | NC              | AV1             | AV1              |  |

| P7         | AG0             | AG0             | AG2             | AG2              |  |

| P8         | AG2             | AG2             | AG4             | AG4              |  |

| P9         | GNDA            | GNDA            | GNDA            | GNDA             |  |

| P10        | NC              | AC5             | AC7             | AC7              |  |

| P11        | NC              | NC              | AV8             | AV8              |  |

| P12        | NC              | NC              | AG8             | AG8              |  |

| P13        | NC              | NC              | AV9             | AV9              |  |

| P14        | ADCGNDREF       | ADCGNDREF       | ADCGNDREF       | ADCGNDREF        |  |

| P15        | PTBASE          | PTBASE          | PTBASE          | PTBASE           |  |

| P16        | GNDNVM          | GNDNVM          | GNDNVM          | GNDNVM           |  |

| R1         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |  |

| R2         | PCAP            | PCAP            | PCAP            | PCAP             |  |

| R3         | NC              | NC              | AT1             | AT1              |  |

| R4         | NC              | NC              | AT0             | AT0              |  |

4-17 Revision 6