# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | -                                                            |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | 36864                                                        |

| Number of I/O                  | 93                                                           |

| Number of Gates                | 250000                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                           |

| Package / Case                 | 208-BFQFP                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs250-pq208i |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 – Fusion Device Family Overview

## Introduction

The Fusion mixed signal FPGA satisfies the demand from system architects for a device that simplifies design and unleashes their creativity. As the world's first mixed signal programmable logic family, Fusion integrates mixed signal analog, flash memory, and FPGA fabric in a monolithic device. Fusion devices enable designers to quickly move from concept to completed design and then deliver feature-rich systems to market. This new technology takes advantage of the unique properties of Microsemi flash-based FPGAs, including a high-isolation, triple-well process and the ability to support high-voltage transistors to meet the demanding requirements of mixed signal system design.

Fusion mixed signal FPGAs bring the benefits of programmable logic to many application areas, including power management, smart battery charging, clock generation and management, and motor control. Until now, these applications have only been implemented with costly and space-consuming discrete analog components or mixed signal ASIC solutions. Fusion mixed signal FPGAs present new capabilities for system development by allowing designers to integrate a wide range of functionality into a single device, while at the same time offering the flexibility of upgrades late in the manufacturing process or after the device is in the field. Fusion devices provide an excellent alternative to costly and

time-consuming mixed signal ASIC designs. In addition, when used in conjunction with the ARM Cortex-M1 processor, Fusion technology represents the definitive mixed signal FPGA platform.

Flash-based Fusion devices are Instant On. As soon as system power is applied and within normal operating specifications, Fusion devices are working. Fusion devices have a 128-bit flash-based lock and industry-leading AES decryption, used to secure programmed intellectual property (IP) and configuration data. Fusion devices are the most comprehensive single-chip analog and digital programmable logic solution available today.

To support this new ground-breaking technology, Microsemi has developed a series of major tool innovations to help maximize designer productivity. Implemented as extensions to the popular Microsemi Libero<sup>®</sup> System-on-Chip (SoC) software, these new tools allow designers to easily instantiate and configure peripherals within a design, establish links between peripherals, create or import building blocks or reference designs, and perform hardware verification. This tool suite will also add comprehensive hardware/software debug capability as well as a suite of utilities to simplify development of embedded soft-processor-based solutions.

## **General Description**

The Fusion family, based on the highly successful ProASIC<sup>®</sup>3 and ProASIC3E flash FPGA architecture, has been designed as a high-performance, programmable, mixed signal platform. By combining an advanced flash FPGA core with flash memory blocks and analog peripherals, Fusion devices dramatically simplify system design and, as a result, dramatically reduce overall system cost and board space.

The state-of-the-art flash memory technology offers high-density integrated flash memory blocks, enabling savings in cost, power, and board area relative to external flash solutions, while providing increased flexibility and performance. The flash memory blocks and integrated analog peripherals enable true mixed-mode programmable logic designs. Two examples are using an on-chip soft processor to implement a fully functional flash MCU and using high-speed FPGA logic to offer system and power supervisory capabilities. Instant On, and capable of operating from a single 3.3 V supply, the Fusion family is ideally suited for system management and control applications.

The devices in the Fusion family are categorized by FPGA core density. Each family member contains many peripherals, including flash memory blocks, an analog-to-digital-converter (ADC), high-drive outputs, both RC and crystal oscillators, and a real-time counter (RTC). This provides the user with a high level of flexibility and integration to support a wide variety of mixed signal applications. The flash memory block capacity ranges from 2 Mbits to 8 Mbits. The integrated 12-bit ADC supports up to 30 independently configurable input channels.

## VersaTile Characteristics

## Sample VersaTile Specifications—Combinatorial Module

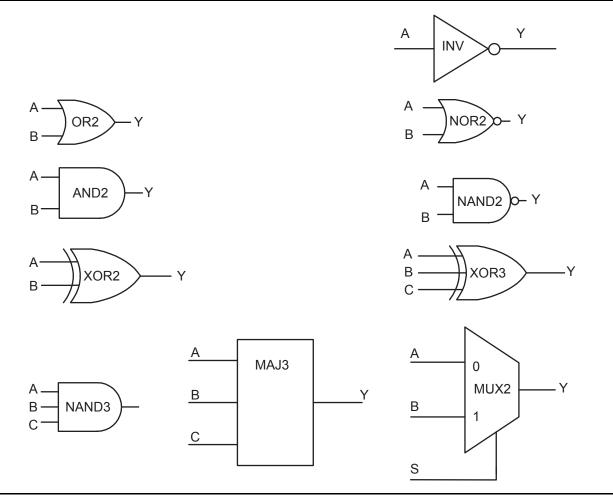

The Fusion library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library (Figure 2-3). For more details, refer to the *IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide*.

Figure 2-3 • Sample of Combinatorial Cells

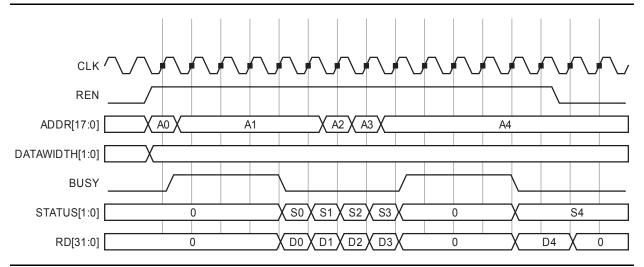

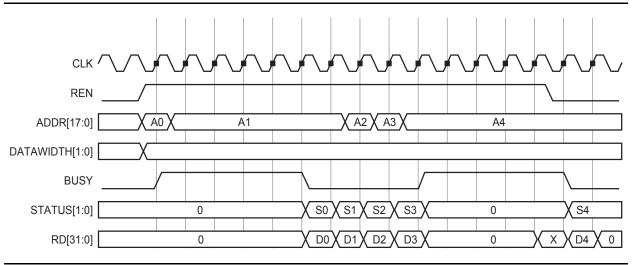

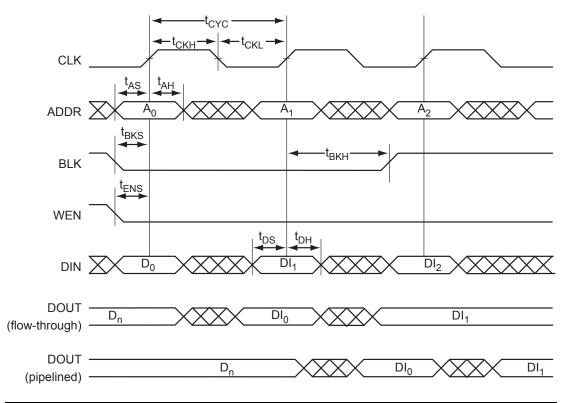

## **Read Operation**

Read operations are designed to read data from the FB Array, Page Buffer, Block Buffer, or status registers. Read operations support a normal read and a read-ahead mode (done by asserting READNEXT). Also, the timing for Read operations is dependent on the setting of PIPE.

The following diagrams illustrate representative timing for Non-Pipe Mode (Figure 2-38) and Pipe Mode (Figure 2-39) reads of the flash memory block interface.

Figure 2-38 • Read Waveform (Non-Pipe Mode, 32-bit access)

Figure 2-39 • Read Waveform (Pipe Mode, 32-bit access)

Device Architecture

## DINA and DINB

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 2-29).

## **DOUTA and DOUTB**

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 2-29). The output data on unused pins is undefined.

Table 2-29 • Unused/Used Input and Output Data Pins for Various Supported Bus Widths

| D×W   | DINx/DOUTx |       |  |  |  |  |

|-------|------------|-------|--|--|--|--|

|       | Unused     | Used  |  |  |  |  |

| 4k×1  | [8:1]      | [0]   |  |  |  |  |

| 2k×2  | [8:2]      | [1:0] |  |  |  |  |

| 1k×4  | [8:4]      | [3:0] |  |  |  |  |

| 512×9 | None       | [8:0] |  |  |  |  |

Note: The "x" in DINx and DOUTx implies A or B.

Figure 2-52 • RAM Write, Output Retained. Applicable to both RAM4K9 and RAM512x18.

Figure 2-53 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 Only.

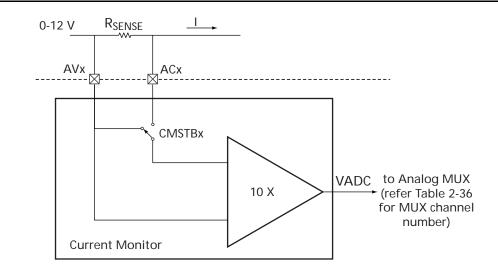

## Figure 2-72 • Positive Current Monitor

Care must be taken when choosing the right resistor for current measurement application. Note that because of the 10× amplification, the maximum measurable difference between the AV and AC pads is  $V_{AREF}$  / 10. A larger AV-to-AC voltage drop will result in ADC saturation; that is, the digital code put out by the ADC will stay fixed at the full scale value. Therefore, the user must select the external sense resistor appropriately. Table 2-38 shows recommended resistor values for different current measurement ranges. When choosing resistor values for a system, there is a trade-off between measurement accuracy and power consumption. Choosing a large resistor will increase the voltage drop and hence increase accuracy of the measurement; however the larger voltage drop dissipates more power (P = I<sup>2</sup> × R).

The Current Monitor is a unipolar system, meaning that the differential voltage swing must be from 0 V to  $V_{AREF}/10$ . Therefore, the Current Monitor only supports differential voltage where  $|V_{AV}-V_{AC}|$  is greater than 0 V. This results in the requirement that the potential of the AV pad must be larger than the potential of the AC pad. This is straightforward for positive voltage systems. For a negative voltage system, it means that the AV pad must be "more negative" than the AC pad. This is shown in Figure 2-73.

In this case, both the AV pad and the AC pad are configured for negative operations and the output of the differential amplifier still falls between 0 V and  $V_{AREF}$  as required.

| Current Range     | Recommended Minimum Resistor Value (Ohms) |

|-------------------|-------------------------------------------|

| > 5 mA – 10 mA    | 10 – 20                                   |

| > 10 mA – 20 mA   | 5 – 10                                    |

| > 20 mA – 50 mA   | 2.5 – 5                                   |

| > 50 mA – 100 mA  | 1 – 2                                     |

| > 100 mA – 200 mA | 0.5 – 1                                   |

| > 200 mA – 500 mA | 0.3 – 0.5                                 |

| > 500 mA – 1 A    | 0.1 – 0.2                                 |

| > 1 A – 2 A       | 0.05 – 0.1                                |

| > 2 A – 4 A       | 0.025 – 0.05                              |

| > 4 A – 8 A       | 0.0125 – 0.025                            |

| > 8 A – 12 A      | 0.00625 – 0.02                            |

Table 2-37 • Recommended Resistor for Different Current Range Measurement

EQ 16 through EQ 18 can be used to calculate the acquisition time required for a given input. The STC signal gives the number of sample periods in ADCCLK for the acquisition time of the desired signal. If the actual acquisition time is higher than the STC value, the settling time error can affect the accuracy of the ADC, because the sampling capacitor is only partially charged within the given sampling cycle. Example acquisition times are given in Table 2-44 and Table 2-45. When controlling the sample time for the ADC along with the use of the active bipolar prescaler, current monitor, or temperature monitor, the minimum sample time(s) for each must be obeyed. EQ 19 can be used to determine the appropriate value of STC.

You can calculate the minimum actual acquisition time by using EQ 16:

EQ 16

EQ 17

For 0.5 LSB gain error, VOUT should be replaced with (VIN –(0.5 × LSB Value)): (VIN – 0.5 × LSB Value) = VIN(1 –  $e^{-t/RC}$ )

$$1 - e^{-e^{-1}}$$

Solving EQ 17:

EQ 18

where  $R = Z_{INAD} + R_{SOURCE}$  and  $C = C_{INAD}$ . Calculate the value of STC by using EQ 19.

t<sub>SAMPLE</sub> = (2 + STC) x (1 / ADCCLK) or t<sub>SAMPLE</sub> = (2 + STC) x (ADC Clock Period)

EQ 19

where ADCCLK = ADC clock frequency in MHz.

where VIN is the ADC reference voltage (VREF)

$t_{SAMPLE}$  = 0.449 µs from bit resolution in Table 2-44.

ADC Clock frequency = 10 MHz or a 100 ns period.

STC = (t<sub>SAMPLE</sub> / (1 / 10 MHz)) - 2 = 4.49 - 2 = 2.49.

You must round up to 3 to accommodate the minimum sample time.

#### Table 2-44 • Acquisition Time Example with VAREF = 2.56 V

| VIN = 2.56V, R = 4K (R <sub>SOURCE</sub> ~ 0), C = 18 pF                         |       |       |  |  |  |  |  |

|----------------------------------------------------------------------------------|-------|-------|--|--|--|--|--|

| Resolution         LSB Value (mV)         Min. Sample/Hold Time for 0.5 LSB (μs) |       |       |  |  |  |  |  |

| 8                                                                                | 10    | 0.449 |  |  |  |  |  |

| 10                                                                               | 2.5   | 0.549 |  |  |  |  |  |

| 12                                                                               | 0.625 | 0.649 |  |  |  |  |  |

| VIN = 3.3V, R = 4K (R <sub>SOURCE</sub> ~ 0), C = 18 pF                          |        |       |  |  |  |  |  |

|----------------------------------------------------------------------------------|--------|-------|--|--|--|--|--|

| Resolution         LSB Value (mV)         Min. Sample/Hold time for 0.5 LSB (µs) |        |       |  |  |  |  |  |

| 8                                                                                | 12.891 | 0.449 |  |  |  |  |  |

| 10                                                                               | 3.223  | 0.549 |  |  |  |  |  |

| 12                                                                               | 0.806  | 0.649 |  |  |  |  |  |

## Sample Phase

A conversion is performed in three phases. In the first phase, the analog input voltage is sampled on the input capacitor. This phase is called sample phase. During the sample phase, the output signals BUSY and SAMPLE change from '0' to '1', indicating the ADC is busy and sampling the analog signal. The sample time can be controlled by input signals STC[7:0]. The sample time can be calculated by EQ 20. When controlling the sample time for the ADC along with the use of Prescaler or Current Monitor or Temperature Monitor, the minimum sample time for each must be obeyed.

**Analog System Characteristics**

### Table 2-49 • Analog Channel Specifications

### Commercial Temperature Range Conditions, T<sub>J</sub> = 85°C (unless noted otherwise), Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter          | Description                            | Condition                                  | Min.                 | Тур. | Max.                                          | Units |

|--------------------|----------------------------------------|--------------------------------------------|----------------------|------|-----------------------------------------------|-------|

| Voltage Monit      | tor Using Analog Pads AV,              | AC and AT (using prescaler)                |                      |      | 1                                             |       |

|                    | Input Voltage<br>(Prescaler)           | Refer to Table 3-2 on page 3-3             |                      |      |                                               |       |

| VINAP              | Uncalibrated Gain and<br>Offset Errors | Refer to Table 2-51 on page 2-122          |                      |      |                                               |       |

|                    | Calibrated Gain and<br>Offset Errors   | Refer to Table 2-52 on page 2-123          |                      |      |                                               |       |

|                    | Bandwidth1                             |                                            |                      |      | 100                                           | KHz   |

|                    | Input Resistance                       | Refer to Table 3-3 on page 3-4             |                      |      |                                               |       |

|                    | Scaling Factor                         | Prescaler modes (Table 2-57 on page 2-130) |                      |      |                                               |       |

|                    | Sample Time                            |                                            | 10                   |      |                                               | μs    |

| Current Moni       | tor Using Analog Pads AV               | and AC                                     |                      |      |                                               |       |

| VRSM <sup>1</sup>  | Maximum Differential<br>Input Voltage  |                                            |                      |      | VAREF / 10                                    | mV    |

|                    | Resolution                             | Refer to "Current Monitor" section         |                      |      |                                               |       |

|                    | Common Mode Range                      |                                            |                      |      | - 10.5 to +12                                 | V     |

| CMRR               | Common Mode<br>Rejection Ratio         | DC – 1 KHz                                 |                      | 60   |                                               | dB    |

|                    |                                        | 1 KHz - 10 KHz                             |                      | 50   |                                               | dB    |

|                    |                                        | > 10 KHz                                   |                      | 30   |                                               | dB    |

| t <sub>CMSHI</sub> | Strobe High time                       |                                            | ADC<br>conv.<br>time |      | 200                                           | μs    |

| t <sub>CMSHI</sub> | Strobe Low time                        |                                            | 5                    |      |                                               | μs    |

| t <sub>CMSHI</sub> | Settling time                          |                                            | 0.02                 |      |                                               | μs    |

|                    | Accuracy                               | Input differential voltage > 50 mV         |                      |      | -2 -(0.05 x<br>VRSM) to +2 +<br>(0.05 x VRSM) | mV    |

Notes:

1. VRSM is the maximum voltage drop across the current sense resistor.

2. Analog inputs used as digital inputs can tolerate the same voltage limits as the corresponding analog pad. There is no reliability concern on digital inputs as long as VIND does not exceed these limits.

- 3. VIND is limited to VCC33A + 0.2 to allow reaching 10 MHz input frequency.

- 4. An averaging of 1,024 samples (LPF setting in Analog System Builder) is required and the maximum capacitance allowed across the AT pins is 500 pF.

- 5. The temperature offset is a fixed positive value.

- 6. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

- 7. When using SmartGen Analog System Builder, CalibIP is required to obtain specified offset. For further details on CalibIP, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

## Table 2-78 • Fusion Standard I/O Standards—OUT\_DRIVE Settings

|                    |   |   | OUT_DR | IVE (mA) |      |      |

|--------------------|---|---|--------|----------|------|------|

| I/O Standards      | 2 | 4 | 6      | 8        | Sle  | ew . |

| LVTTL/LVCMOS 3.3 V | 3 | 3 | 3      | 3        | High | Low  |

| LVCMOS 2.5 V       | 3 | 3 | 3      | 3        | High | Low  |

| LVCMOS 1.8 V       | 3 | 3 | -      | -        | High | Low  |

| LVCMOS 1.5 V       | 3 | - | -      | -        | High | Low  |

## Table 2-79 • Fusion Advanced I/O Standards—SLEW and OUT\_DRIVE Settings

|                    | OUT_DRIVE (mA) |   |   |   |    |    |      |      |

|--------------------|----------------|---|---|---|----|----|------|------|

| I/O Standards      | 2              | 4 | 6 | 8 | 12 | 16 | Sle  | ew 🛛 |

| LVTTL/LVCMOS 3.3 V | 3              | 3 | 3 | 3 | 3  | 3  | High | Low  |

| LVCMOS 2.5 V       | 3              | 3 | 3 | 3 | 3  | -  | High | Low  |

| LVCMOS 1.8 V       | 3              | 3 | 3 | 3 | -  | -  | High | Low  |

| LVCMOS 1.5 V       | 3              | 3 | _ | _ | -  | _  | High | Low  |

|                    | OUT_DRIVE (mA) |   |   |   |    |    |    |      |     |

|--------------------|----------------|---|---|---|----|----|----|------|-----|

| I/O Standards      | 2              | 4 | 6 | 8 | 12 | 16 | 24 | Sle  | w   |

| LVTTL/LVCMOS 3.3 V | 3              | 3 | 3 | 3 | 3  | 3  | 3  | High | Low |

| LVCMOS 2.5 V       | 3              | 3 | 3 | 3 | 3  | 3  | 3  | High | Low |

| LVCMOS 2.5 V/5.0 V | 3              | 3 | 3 | 3 | 3  | 3  | 3  | High | Low |

| LVCMOS 1.8 V       | 3              | 3 | 3 | 3 | 3  | 3  | -  | High | Low |

| LVCMOS 1.5 V       | 3              | 3 | 3 | 3 | 3  | -  | _  | High | Low |

Device Architecture

| I/O Standard                  | Input/Output Supply<br>Voltage (VCCI_TYP) | Input Reference Voltage<br>(VREF_TYP) | Board Termination Voltage<br>(VTT_TYP) |

|-------------------------------|-------------------------------------------|---------------------------------------|----------------------------------------|

| LVTTL/LVCMOS 3.3 V            | 3.30 V                                    | -                                     | -                                      |

| LVCMOS 2.5 V                  | 2.50 V                                    | _                                     | -                                      |

| LVCMOS 2.5 V / 5.0 V<br>Input | 2.50 V                                    | -                                     | -                                      |

| LVCMOS 1.8 V                  | 1.80 V                                    | _                                     | -                                      |

| LVCMOS 1.5 V                  | 1.50 V                                    | _                                     | -                                      |

| PCI 3.3 V                     | 3.30 V                                    | _                                     | _                                      |

| PCI-X 3.3 V                   | 3.30 V                                    | _                                     | _                                      |

| GTL+ 3.3 V                    | 3.30 V                                    | 1.00 V                                | 1.50 V                                 |

| GTL+ 2.5 V                    | 2.50 V                                    | 1.00 V                                | 1.50 V                                 |

| GTL 3.3 V                     | 3.30 V                                    | 0.80 V                                | 1.20 V                                 |

| GTL 2.5 V                     | 2.50 V                                    | 0.80 V                                | 1.20 V                                 |

| HSTL Class I                  | 1.50 V                                    | 0.75 V                                | 0.75 V                                 |

| HSTL Class II                 | 1.50 V                                    | 0.75 V                                | 0.75 V                                 |

| SSTL3 Class I                 | 3.30 V                                    | 1.50 V                                | 1.50 V                                 |

| SSTL3 Class II                | 3.30 V                                    | 1.50 V                                | 1.50 V                                 |

| SSTL2 Class I                 | 2.50 V                                    | 1.25 V                                | 1.25 V                                 |

| SSTL2 Class II                | 2.50 V                                    | 1.25 V                                | 1.25 V                                 |

| LVDS, BLVDS, M-LVDS           | 2.50 V                                    | -                                     | -                                      |

| LVPECL                        | 3.30 V                                    | -                                     | -                                      |

## Table 2-83 • Fusion Pro I/O Supported Standards and Corresponding VREF and VTT Voltages

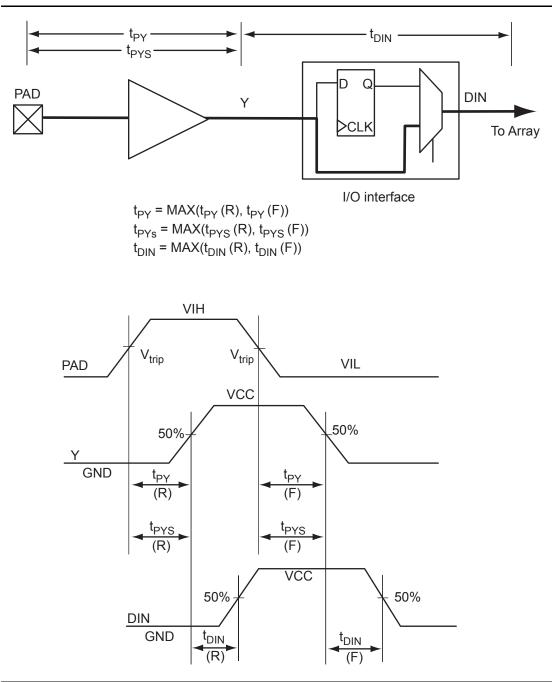

*Figure 2-116* • Input Buffer Timing Model and Delays (example)

Device Architecture

## Table 2-113 • 2.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.60              | 8.82            | 0.04             | 1.51            | 1.66             | 0.43              | 8.13            | 8.82            | 2.72            | 2.29            | 10.37            | 11.05            | ns    |

|                   | -1             | 0.51              | 7.50            | 0.04             | 1.29            | 1.41             | 0.36              | 6.92            | 7.50            | 2.31            | 1.95            | 8.82             | 9.40             | ns    |

|                   | -2             | 0.45              | 6.58            | 0.03             | 1.13            | 1.24             | 0.32              | 6.07            | 6.58            | 2.03            | 1.71            | 7.74             | 8.25             | ns    |

| 8 mA              | Std.           | 0.60              | 5.27            | 0.04             | 1.51            | 1.66             | 0.43              | 5.27            | 5.27            | 3.10            | 3.03            | 7.50             | 7.51             | ns    |

|                   | -1             | 0.51              | 4.48            | 0.04             | 1.29            | 1.41             | 0.36              | 4.48            | 4.48            | 2.64            | 2.58            | 6.38             | 6.38             | ns    |

|                   | -2             | 0.45              | 3.94            | 0.03             | 1.13            | 1.24             | 0.32              | 3.93            | 3.94            | 2.32            | 2.26            | 5.60             | 5.61             | ns    |

| 12 mA             | Std.           | 0.66              | 3.74            | 0.04             | 1.51            | 1.66             | 0.43              | 3.81            | 3.49            | 3.37            | 3.49            | 6.05             | 5.73             | ns    |

|                   | -1             | 0.56              | 3.18            | 0.04             | 1.29            | 1.41             | 0.36              | 3.24            | 2.97            | 2.86            | 2.97            | 5.15             | 4.87             | ns    |

|                   | -2             | 0.49              | 2.80            | 0.03             | 1.13            | 1.24             | 0.32              | 2.85            | 2.61            | 2.51            | 2.61            | 4.52             | 4.28             | ns    |

| 16 mA             | Std.           | 0.66              | 3.53            | 0.04             | 1.51            | 1.66             | 0.43              | 3.59            | 3.12            | 3.42            | 3.62            | 5.83             | 5.35             | ns    |

|                   | -1             | 0.56              | 3.00            | 0.04             | 1.29            | 1.41             | 0.36              | 3.06            | 2.65            | 2.91            | 3.08            | 4.96             | 4.55             | ns    |

|                   | -2             | 0.49              | 2.63            | 0.03             | 1.13            | 1.24             | 0.32              | 2.68            | 2.33            | 2.56            | 2.71            | 4.35             | 4.00             | ns    |

| 24 mA             | Std.           | 0.66              | 3.26            | 0.04             | 1.51            | 1.66             | 0.43              | 3.32            | 2.48            | 3.49            | 4.11            | 5.56             | 4.72             | ns    |

|                   | -1             | 0.56              | 2.77            | 0.04             | 1.29            | 1.41             | 0.36              | 2.83            | 2.11            | 2.97            | 3.49            | 4.73             | 4.01             | ns    |

|                   | -2             | 0.49              | 2.44            | 0.03             | 1.13            | 1.24             | 0.32              | 2.48            | 1.85            | 2.61            | 3.07            | 4.15             | 3.52             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

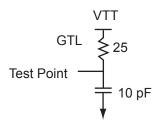

## 2.5 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-141 • Minimum and Maximum DC Input and Output Levels

| 2.5 GTL            |           | VIL         | VIH         |           | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 20 mA <sup>3</sup> | -0.3      | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | -         | 20  | 20  | 124                     | 169                     | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

## Figure 2-125 • AC Loading

#### Table 2-142 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                  | 0.8             | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-143 • 2.5 V GTL

```

Commercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 0.8 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.13            | 0.04             | 2.46            | 0.43              | 2.16            | 2.13            |                 |                 | 4.40             | 4.36             | ns    |

| -1             | 0.56              | 1.81            | 0.04             | 2.09            | 0.36              | 1.84            | 1.81            |                 |                 | 3.74             | 3.71             | ns    |

| -2             | 0.49              | 1.59            | 0.03             | 1.83            | 0.32              | 1.61            | 1.59            |                 |                 | 3.28             | 3.26             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## 3 – DC and Power Characteristics

## **General Specifications**

## **Operating Conditions**

Stresses beyond those listed in Table 3-1 may cause permanent damage to the device.

Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating ranges specified in Table 3-2 on page 3-3.

| Symbol   | Parameter                                  | Commercial                      | Industrial                                                                                  | Units |  |  |

|----------|--------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------|-------|--|--|

| VCC      | DC core supply voltage                     | -0.3 to 1.65                    | -0.3 to 1.65                                                                                | V     |  |  |

| VJTAG    | JTAG DC voltage                            | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

| VPUMP    | Programming voltage                        | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

| VCCPLL   | Analog power supply (PLL)                  | -0.3 to 1.65                    | -0.3 to 1.65                                                                                | V     |  |  |

| VCCI     | DC I/O output buffer supply voltage        | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

| VI       | I/O input voltage <sup>1</sup>             | enabled)<br>–0.3 V to (VCCI + 1 | -0.3 V to (VCCI + 1 V) or 3.6 V, whichever voltage is lower (when I/O hot-insertion mode is |       |  |  |

| VCC33A   | +3.3 V power supply                        | -0.3 to 3.75 <sup>2</sup>       | -0.3 to 3.75 <sup>2</sup>                                                                   | V     |  |  |

| VCC33PMP | +3.3 V power supply                        | -0.3 to 3.75 <sup>2</sup>       | -0.3 to 3.75 <sup>2</sup>                                                                   | V     |  |  |

| VAREF    | Voltage reference for ADC                  | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

| VCC15A   | Digital power supply for the analog system | -0.3 to 1.65                    | -0.3 to 1.65                                                                                | V     |  |  |

| VCCNVM   | Embedded flash power supply                | -0.3 to 1.65                    | -0.3 to 1.65                                                                                | V     |  |  |

| VCCOSC   | Oscillator power supply                    | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

#### Table 3-1 • Absolute Maximum Ratings

Notes:

1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-4.

2. Analog data not valid beyond 3.65 V.

3. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

4. For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.

| Product<br>Grade | Storage<br>Temperature      | Element        | Grade Programming<br>Cycles | Retention |

|------------------|-----------------------------|----------------|-----------------------------|-----------|

| Commercial       | Min. T <sub>J</sub> = 0°C   | FPGA/FlashROM  | 500                         | 20 years  |

|                  | Max. T <sub>J</sub> = 85°C  | Embedded Flash | < 1,000                     | 20 years  |

|                  |                             |                | < 10,000                    | 10 years  |

|                  |                             |                | < 15,000                    | 5 years   |

| Industrial       | Min. T <sub>J</sub> = –40°C | FPGA/FlashROM  | 500                         | 20 years  |

|                  | Max. T <sub>J</sub> = 100°C | Embedded Flash | < 1,000                     | 20 years  |

|                  |                             |                | < 10,000                    | 10 years  |

|                  |                             |                | < 15,000                    | 5 years   |

## Table 3-5 • FPGA Programming, Storage, and Operating Limits

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every Fusion device. These circuits ensure easy transition from the powered off state to the powered up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 3-1 on page 3-6.

There are five regions to consider during power-up.

Fusion I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 3-1).

- 2. VCCI > VCC 0.75 V (typical).

- 3. Chip is in the operating mode.

## V<sub>CCI</sub> Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.2 V

Ramping down: 0.5 V < trip\_point\_down < 1.1 V

## V<sub>CC</sub> Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.1 V

Ramping down: 0.5 V < trip\_point\_down < 1 V

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

## Internal Power-Up Activation Sequence

- 1. Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

## PLL Behavior at Brownout Condition

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper powerup behavior. Power ramp-up should be monotonic at least until VCC and VCCPLX exceed brownout activation levels. The  $V_{CC}$  activation level is specified as 1.1 V worst-case (see Figure 3-1 on page 3-6 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels (0.75 V  $\pm$  0.25 V), the PLL output lock signal goes low and/or the output clock is lost.

DC and Power Characteristics

| Parameter | Description         | Conditions                                                            | Temp.                  | Min. | Тур. | Max. | Unit |

|-----------|---------------------|-----------------------------------------------------------------------|------------------------|------|------|------|------|

| IJTAG     | JTAG I/O quiescent  | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |      | 80   | 100  | μA   |

|           | current             | VJTAG = 3.63 V                                                        | T <sub>J</sub> = 85°C  |      | 80   | 100  | μA   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 80   | 100  | μA   |

|           |                     | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VJTAG = 0 V |                        |      | 0    | 0    | μA   |

| IPP       | Programming supply  | Non-programming mode,                                                 | T <sub>J</sub> = 25°C  |      | 39   | 80   | μA   |

|           | current             | VPUMP = 3.63 V                                                        | T <sub>J</sub> = 85°C  |      | 40   | 80   | μA   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 40   | 80   | μA   |

|           |                     | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VPUMP = 0 V |                        |      | 0    | 0    | μA   |

| ICCNVM    | Embedded NVM        | Reset asserted, V <sub>CCNVM</sub> = 1.575 V                          | T <sub>J</sub> = 25°C  |      | 50   | 150  | μA   |

|           | current             |                                                                       | T <sub>J</sub> =85°C   |      | 50   | 150  | μA   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 50   | 150  | μA   |

| ICCPLL    | 1.5 V PLL quiescent | Operational standby                                                   | T <sub>J</sub> = 25°C  |      | 130  | 200  | μA   |

|           | current             | , VCCPLL = 1.575 V                                                    | T <sub>J</sub> = 85°C  |      | 130  | 200  | μA   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 130  | 200  | μA   |

| Table 3-8 | • AFS1500 Quiescent Supply Current Characteristics (continued) |

|-----------|----------------------------------------------------------------|

|-----------|----------------------------------------------------------------|

Notes:

1. ICC is the 1.5 V power supplies, ICC and ICC15A.

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

|            | FG256           |                 |                 |                  |  |  |  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|--|--|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |  |  |  |

| R5         | AV0             | AV0             | AV2             | AV2              |  |  |  |  |

| R6         | AT0             | AT0             | AT2             | AT2              |  |  |  |  |

| R7         | AV1             | AV1             | AV3             | AV3              |  |  |  |  |

| R8         | AT3             | AT3             | AT5             | AT5              |  |  |  |  |

| R9         | AV4             | AV4             | AV6             | AV6              |  |  |  |  |

| R10        | NC              | AT5             | AT7             | AT7              |  |  |  |  |

| R11        | NC              | AV5             | AV7             | AV7              |  |  |  |  |

| R12        | NC              | NC              | AT9             | AT9              |  |  |  |  |

| R13        | NC              | NC              | AG9             | AG9              |  |  |  |  |

| R14        | NC              | NC              | AC9             | AC9              |  |  |  |  |

| R15        | PUB             | PUB             | PUB             | PUB              |  |  |  |  |

| R16        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |  |  |  |  |

| T1         | GND             | GND             | GND             | GND              |  |  |  |  |

| T2         | NCAP            | NCAP            | NCAP            | NCAP             |  |  |  |  |

| Т3         | VCC33N          | VCC33N          | VCC33N          | VCC33N           |  |  |  |  |

| T4         | NC              | NC              | ATRTN0          | ATRTN0           |  |  |  |  |

| T5         | AT1             | AT1             | AT3             | AT3              |  |  |  |  |

| Т6         | ATRTN0          | ATRTN0          | ATRTN1          | ATRTN1           |  |  |  |  |

| T7         | AT2             | AT2             | AT4             | AT4              |  |  |  |  |

| Т8         | ATRTN1          | ATRTN1          | ATRTN2          | ATRTN2           |  |  |  |  |

| Т9         | AT4             | AT4             | AT6             | AT6              |  |  |  |  |

| T10        | ATRTN2          | ATRTN2          | ATRTN3          | ATRTN3           |  |  |  |  |

| T11        | NC              | NC              | AT8             | AT8              |  |  |  |  |

| T12        | NC              | NC              | ATRTN4          | ATRTN4           |  |  |  |  |

| T13        | GNDA            | GNDA            | GNDA            | GNDA             |  |  |  |  |

| T14        | VCC33A          | VCC33A          | VCC33A          | VCC33A           |  |  |  |  |

| T15        | VAREF           | VAREF           | VAREF           | VAREF            |  |  |  |  |

| T16        | GND             | GND             | GND             | GND              |  |  |  |  |

Package Pin Assignments

|               | FG484           |                  | FG484         |                 |                  |  |  |  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|--|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |  |

| A1            | GND             | GND              | AA14          | AG7             | AG7              |  |  |  |

| A2            | VCC             | NC               | AA15          | AG8             | AG8              |  |  |  |

| A3            | GAA1/IO01PDB0V0 | GAA1/IO01PDB0V0  | AA16          | GNDA            | GNDA             |  |  |  |

| A4            | GAB0/IO02NDB0V0 | GAB0/IO02NDB0V0  | AA17          | AG9             | AG9              |  |  |  |

| A5            | GAB1/IO02PDB0V0 | GAB1/IO02PDB0V0  | AA18          | VAREF           | VAREF            |  |  |  |

| A6            | IO07NDB0V1      | IO07NDB0V1       | AA19          | VCCIB2          | VCCIB2           |  |  |  |

| A7            | IO07PDB0V1      | IO07PDB0V1       | AA20          | PTEM            | PTEM             |  |  |  |

| A8            | IO10PDB0V1      | IO09PDB0V1       | AA21          | GND             | GND              |  |  |  |

| A9            | IO14NDB0V1      | IO13NDB0V2       | AA22          | VCC             | NC               |  |  |  |

| A10           | IO14PDB0V1      | IO13PDB0V2       | AB1           | GND             | GND              |  |  |  |

| A11           | IO17PDB1V0      | IO24PDB1V0       | AB2           | VCC             | NC               |  |  |  |

| A12           | IO18PDB1V0      | IO26PDB1V0       | AB3           | NC              | IO94NSB4V0       |  |  |  |

| A13           | IO19NDB1V0      | IO27NDB1V1       | AB4           | GND             | GND              |  |  |  |

| A14           | IO19PDB1V0      | IO27PDB1V1       | AB5           | VCC33N          | VCC33N           |  |  |  |

| A15           | IO24NDB1V1      | IO35NDB1V2       | AB6           | AT0             | AT0              |  |  |  |

| A16           | IO24PDB1V1      | IO35PDB1V2       | AB7           | ATRTN0          | ATRTN0           |  |  |  |

| A17           | GBC0/IO26NDB1V1 | GBC0/IO40NDB1V2  | AB8           | AT1             | AT1              |  |  |  |

| A18           | GBA0/IO28NDB1V1 | GBA0/IO42NDB1V2  | AB9           | AT2             | AT2              |  |  |  |

| A19           | IO29NDB1V1      | IO43NDB1V2       | AB10          | ATRTN1          | ATRTN1           |  |  |  |

| A20           | IO29PDB1V1      | IO43PDB1V2       | AB11          | AT3             | AT3              |  |  |  |

| A21           | VCC             | NC               | AB12          | AT6             | AT6              |  |  |  |

| A22           | GND             | GND              | AB13          | ATRTN3          | ATRTN3           |  |  |  |

| AA1           | VCC             | NC               | AB14          | AT7             | AT7              |  |  |  |

| AA2           | GND             | GND              | AB15          | AT8             | AT8              |  |  |  |

| AA3           | VCCIB4          | VCCIB4           | AB16          | ATRTN4          | ATRTN4           |  |  |  |

| AA4           | VCCIB4          | VCCIB4           | AB17          | AT9             | AT9              |  |  |  |

| AA5           | PCAP            | PCAP             | AB18          | VCC33A          | VCC33A           |  |  |  |

| AA6           | AG0             | AG0              | AB19          | GND             | GND              |  |  |  |

| AA7           | GNDA            | GNDA             | AB20          | NC              | IO76NPB2V0       |  |  |  |

| AA8           | AG1             | AG1              | AB21          | VCC             | NC               |  |  |  |

| AA9           | AG2             | AG2              | AB22          | GND             | GND              |  |  |  |

| AA10          | GNDA            | GNDA             | B1            | VCC             | NC               |  |  |  |

| AA11          | AG3             | AG3              | B2            | GND             | GND              |  |  |  |

| AA12          | AG6             | AG6              | B3            | GAA0/IO01NDB0V0 | GAA0/IO01NDB0V0  |  |  |  |

| AA13          | GNDA            | GNDA             | B4            | GND             | GND              |  |  |  |

|               | FG484           |                  | FG484         |                 |                  |  |  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |

| P21           | IO51PDB2V0      | IO73PDB2V0       | T12           | AV5             | AV5              |  |  |

| P22           | IO49NDB2V0      | IO71NDB2V0       | T13           | AC5             | AC5              |  |  |

| R1            | IO69PDB4V0      | IO102PDB4V0      | T14           | NC              | NC               |  |  |

| R2            | IO69NDB4V0      | IO102NDB4V0      | T15           | GNDA            | GNDA             |  |  |

| R3            | VCCIB4          | VCCIB4           | T16           | NC              | IO77PPB2V0       |  |  |

| R4            | IO64PDB4V0      | IO91PDB4V0       | T17           | NC              | IO74PDB2V0       |  |  |

| R5            | IO64NDB4V0      | IO91NDB4V0       | T18           | VCCIB2          | VCCIB2           |  |  |

| R6            | NC              | IO92PDB4V0       | T19           | IO55NDB2V0      | IO82NDB2V0       |  |  |

| R7            | GND             | GND              | T20           | GDA2/IO55PDB2V0 | GDA2/IO82PDB2V0  |  |  |

| R8            | GND             | GND              | T21           | GND             | GND              |  |  |

| R9            | VCC33A          | VCC33A           | T22           | GDC1/IO52PDB2V0 | GDC1/IO79PDB2V0  |  |  |

| R10           | GNDA            | GNDA             | U1            | IO67PDB4V0      | IO98PDB4V0       |  |  |

| R11           | VCC33A          | VCC33A           | U2            | IO67NDB4V0      | IO98NDB4V0       |  |  |

| R12           | GNDA            | GNDA             | U3            | GEC1/IO63PDB4V0 | GEC1/IO90PDB4V0  |  |  |

| R13           | VCC33A          | VCC33A           | U4            | GEC0/IO63NDB4V0 | GEC0/IO90NDB4V0  |  |  |

| R14           | GNDA            | GNDA             | U5            | GND             | GND              |  |  |

| R15           | VCC             | VCC              | U6            | VCCNVM          | VCCNVM           |  |  |

| R16           | GND             | GND              | U7            | VCCIB4          | VCCIB4           |  |  |

| R17           | NC              | IO74NDB2V0       | U8            | VCC15A          | VCC15A           |  |  |

| R18           | GDA0/IO54NDB2V0 | GDA0/IO81NDB2V0  | U9            | GNDA            | GNDA             |  |  |

| R19           | GDB0/IO53NDB2V0 | GDB0/IO80NDB2V0  | U10           | AC4             | AC4              |  |  |

| R20           | VCCIB2          | VCCIB2           | U11           | VCC33A          | VCC33A           |  |  |

| R21           | IO50NDB2V0      | IO75NDB2V0       | U12           | GNDA            | GNDA             |  |  |

| R22           | IO50PDB2V0      | IO75PDB2V0       | U13           | AG5             | AG5              |  |  |

| T1            | NC              | IO100PPB4V0      | U14           | GNDA            | GNDA             |  |  |

| T2            | GND             | GND              | U15           | PUB             | PUB              |  |  |

| Т3            | IO66PDB4V0      | IO95PDB4V0       | U16           | VCCIB2          | VCCIB2           |  |  |

| T4            | IO66NDB4V0      | IO95NDB4V0       | U17           | TDI             | TDI              |  |  |

| Т5            | VCCIB4          | VCCIB4           | U18           | GND             | GND              |  |  |

| Т6            | NC              | IO92NDB4V0       | U19           | IO57NDB2V0      | IO84NDB2V0       |  |  |

| Τ7            | GNDNVM          | GNDNVM           | U20           | GDC2/IO57PDB2V0 | GDC2/IO84PDB2V0  |  |  |

| Т8            | GNDA            | GNDA             | U21           | NC              | IO77NPB2V0       |  |  |

| Т9            | NC              | NC               | U22           | GDC0/IO52NDB2V0 | GDC0/IO79NDB2V0  |  |  |

| T10           | AV4             | AV4              | V1            | GEB1/IO62PDB4V0 | GEB1/IO89PDB4V0  |  |  |

| T11           | NC              | NC               | V2            | GEB0/IO62NDB4V0 | GEB0/IO89NDB4V0  |  |  |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.