Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | 36864                                                         |

| Number of I/O                  | 65                                                            |

| Number of Gates                | 250000                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                            |

| Package / Case                 | 180-WFQFN Dual Rows, Exposed Pad                              |

| Supplier Device Package        | 180-QFN (10x10)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs250-qng180i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Global Clocking

Fusion devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there are on-chip oscillators as well as a comprehensive global clock distribution network.

The integrated RC oscillator generates a 100 MHz clock. It is used internally to provide a known clock source to the flash memory read and write control. It can also be used as a source for the PLLs.

The crystal oscillator supports the following operating modes:

- Crystal (32.768 KHz to 20 MHz)

- · Ceramic (500 KHz to 8 MHz)

- RC (32.768 KHz to 4 MHz)

Each VersaTile input and output port has access to nine VersaNets: six main and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via MUXes. The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

## Digital I/Os with Advanced I/O Standards

The Fusion family of FPGAs features a flexible digital I/O structure, supporting a range of voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V). Fusion FPGAs support many different digital I/O standards, both single-ended and differential.

The I/Os are organized into banks, with four or five banks per device. The configuration of these banks determines the I/O standards supported. The banks along the east and west sides of the device support the full range of I/O standards (single-ended and differential). The south bank supports the Analog Quads (analog I/O). In the family's two smaller devices, the north bank supports multiple single-ended digital I/O standards. In the family's larger devices, the north bank is divided into two banks of digital Pro I/Os, supporting a wide variety of single-ended, differential, and voltage-referenced I/O standards.

Each I/O module contains several input, output, and enable registers. These registers allow the implementation of the following applications:

- · Single-Data-Rate (SDR) applications

- Double-Data-Rate (DDR) applications—DDR LVDS I/O for chip-to-chip communications

- Fusion banks support LVPECL, LVDS, BLVDS, and M-LVDS with 20 multi-drop points.

#### **VersaTiles**

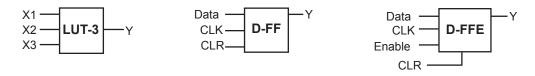

The Fusion core consists of VersaTiles, which are also used in the successful ProASIC3 family. The Fusion VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- · Latch with clear or set

- D-flip-flop with clear or set and optional enable

Refer to Figure 1-2 for the VersaTile configuration arrangement.

# LUT-3 Equivalent D-Flip-Flop with Clear or Set Enable D-Flip-Flop with Clear or Set

Figure 1-2 • VersaTile Configurations

# 2 – Device Architecture

## **Fusion Stack Architecture**

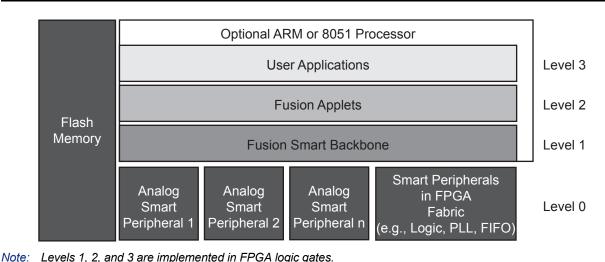

To manage the unprecedented level of integration in Fusion devices, Microsemi developed the Fusion technology stack (Figure 2-1). This layered model offers a flexible design environment, enabling design at very high and very low levels of abstraction. Fusion peripherals include hard analog IP and hard and soft digital IP. Peripherals communicate across the FPGA fabric via a layer of soft gates—the Fusion backbone. Much more than a common bus interface, this Fusion backbone integrates a micro-sequencer within the FPGA fabric and configures the individual peripherals and supports low-level processing of peripheral data. Fusion applets are application building blocks that can control and respond to peripherals and other system signals. Applets can be rapidly combined to create large applications. The technology is scalable across devices, families, design types, and user expertise, and supports a well-defined interface for external IP and tool integration.

At the lowest level, Level 0, are Fusion peripherals. These are configurable functional blocks that can be hardwired structures such as a PLL or analog input channel, or soft (FPGA gate) blocks such as a UART or two-wire serial interface. The Fusion peripherals are configurable and support a standard interface to facilitate communication and implementation.

Connecting and controlling access to the peripherals is the Fusion backbone, Level 1. The backbone is a soft-gate structure, scalable to any number of peripherals. The backbone is a bus and much more; it manages peripheral configuration to ensure proper operation. Leveraging the common peripheral interface and a low-level state machine, the backbone efficiently offloads peripheral management from the system design. The backbone can set and clear flags based upon peripheral behavior and can define performance criteria. The flexibility of the stack enables a designer to configure the silicon, directly bypassing the backbone if that level of control is desired.

One step up from the backbone is the Fusion applet, Level 2. The applet is an application building block that implements a specific function in FPGA gates. It can react to stimuli and board-level events coming through the backbone or from other sources, and responds to these stimuli by accessing and manipulating peripherals via the backbone or initiating some other action. An applet controls or responds to the peripheral(s). Applets can be easily imported or exported from the design environment. The applet structure is open and well-defined, enabling users to import applets from Microsemi, system developers, third parties, and user groups.

Figure 2-1 • Fusion Architecture Stack

### **CCC Physical Implementation**

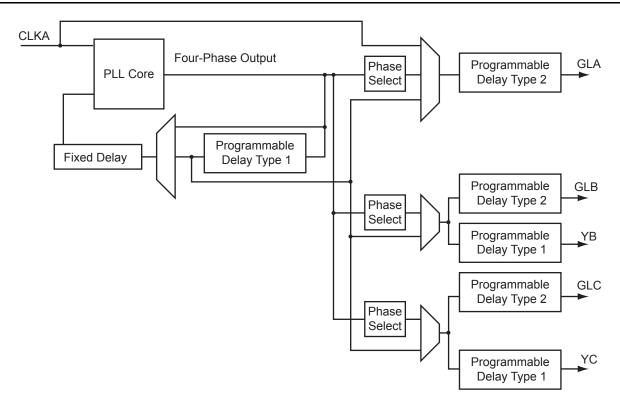

The CCC circuit is composed of the following (Figure 2-23):

- PLL core

- · 3 phase selectors

- · 6 programmable delays and 1 fixed delay

- 5 programmable frequency dividers that provide frequency multiplication/division (not shown in Figure 2-23 because they are automatically configured based on the user's required frequencies)

- 1 dynamic shift register that provides CCC dynamic reconfiguration capability (not shown)

#### **CCC Programming**

The CCC block is fully configurable. It is configured via static flash configuration bits in the array, set by the user in the programming bitstream, or configured through an asynchronous dedicated shift register, dynamically accessible from inside the Fusion device. The dedicated shift register permits changes of parameters such as PLL divide ratios and delays during device operation. This latter mode allows the user to dynamically reconfigure the PLL without the need for core programming. The register file is accessed through a simple serial interface.

Note: Clock divider and multiplier blocks are not shown in this figure or in SmartGen. They are automatically configured based on the user's required frequencies.

Figure 2-23 • PLL Block

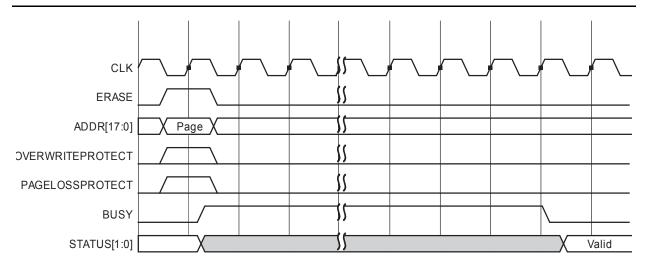

#### **Erase Page Operation**

The Erase Page operation is initiated when the ERASEPAGE pin is asserted. The Erase Page operation allows the user to erase (set user data to zero) any page within the FB.

The use of the OVERWRITEPAGE and PAGELOSSPROTECT pins is the same for erase as for a Program Page operation.

As with the Program Page operation, a STATUS of '01' indicates that the addressed page is not erased. A waveform for an Erase Page operation is shown in Figure 2-37.

Erase errors include the following:

- 1. Attempting to erase a page that is Overwrite Protected (STATUS = '01')

- 2. Attempting to erase a page that is not in the Page Buffer when the Page Buffer has entered Page Loss Protection mode (STATUS = '01')

- 3. The Write Count of the erased page exceeding the Write Threshold defined in the part specification (STATUS = '11')

- 4. The ECC Logic determining that there is an uncorrectable error within the erased page (STATUS = '10')

Figure 2-37 • FB Erase Page Waveform

2-47 Revision 6

The AEMPTY flag is asserted when the difference between the write address and the read address is less than a predefined value. In the example above, a value of 200 for AEVAL means that the AEMPTY flag will be asserted when a read causes the difference between the write address and the read address to drop to 200. It will stay asserted until that difference rises above 200. Note that the FIFO can be configured with different read and write widths; in this case, the AFVAL setting is based on the number of write data entries and the AEVAL setting is based on the number of read data entries. For aspect ratios of 512×9 and 256×18, only 4,096 bits can be addressed by the 12 bits of AFVAL and AEVAL. The number of words must be multiplied by 8 and 16, instead of 9 and 18. The SmartGen tool automatically uses the proper values. To avoid halfwords being written or read, which could happen if different read and write aspect ratios are specified, the FIFO will assert FULL or EMPTY as soon as at least a minimum of one word cannot be written or read. For example, if a two-bit word is written and a four-bit word is being read, the FIFO will remain in the empty state when the first word is written. This occurs even if the FIFO is not completely empty, because in this case, a complete word cannot be read. The same is applicable in the full state. If a four-bit word is written and a two-bit word is read, the FIFO is full and one word is read. The FULL flag will remain asserted because a complete word cannot be written at this point.

2-71 Revision 6

# **Analog Block**

With the Fusion family, Microsemi has introduced the world's first mixed-mode FPGA solution. Supporting a robust analog peripheral mix, Fusion devices will support a wide variety of applications. It is this Analog Block that separates Fusion from all other FPGA solutions on the market today.

By combining both flash and high-speed CMOS processes in a single chip, these devices offer the best of both worlds. The high-performance CMOS is used for building RAM resources. These high-performance structures support device operation up to 350 MHz. Additionally, the advanced Microsemi 0.13 µm flash process incorporates high-voltage transistors and a high-isolation, triple-well process. Both of these are suited for the flash-based programmable logic and nonvolatile memory structures.

High-voltage transistors support the integration of analog technology in several ways. They aid in noise immunity so that the analog portions of the chip can be better isolated from the digital portions, increasing analog accuracy. Because they support high voltages, Microsemi flash FPGAs can be connected directly to high-voltage input signals, eliminating the need for external resistor divider networks, reducing component count, and increasing accuracy. By supporting higher internal voltages, the Microsemi advanced flash process enables high dynamic range on analog circuitry, increasing precision and signal—noise ratio. Microsemi flash FPGAs also drive high-voltage outputs, eliminating the need for external level shifters and drivers.

The unique triple-well process enables the integration of high-performance analog features with increased noise immunity and better isolation. By increasing the efficiency of analog design, the triple-well process also enables a smaller overall design size, reducing die size and cost.

The Analog Block consists of the Analog Quad I/O structure, RTC (for details refer to the "Real-Time Counter System" section on page 2-31), ADC, and ACM. All of these elements are combined in the single Analog Block macro, with which the user implements this functionality (Figure 2-64).

The Analog Block needs to be reset/reinitialized after the core powers up or the device is programmed. An external reset/initialize signal, which can come from the internal voltage regulator when it powers up, must be applied.

Fusion Family of Mixed Signal FPGAs

Table 2-36 describes each pin in the Analog Block. Each function within the Analog Block will be explained in detail in the following sections.

Table 2-36 • Analog Block Pin Description

| Signal Name      | Number of Bits | Direction    | Function                                                                                                                                                                                                                                                                            | Location of<br>Details |

|------------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| VAREF            | 1              | Input/Output | Voltage reference for ADC                                                                                                                                                                                                                                                           | ADC                    |

| ADCGNDREF        | 1              | Input        | External ground reference                                                                                                                                                                                                                                                           | ADC                    |

| MODE[3:0]        | 4              | Input        | ADC operating mode                                                                                                                                                                                                                                                                  | ADC                    |

| SYSCLK           | 1              | Input        | External system clock                                                                                                                                                                                                                                                               |                        |

| TVC[7:0]         | 8              | Input        | Clock divide control                                                                                                                                                                                                                                                                | ADC                    |

| STC[7:0]         | 8              | Input        | Sample time control                                                                                                                                                                                                                                                                 | ADC                    |

| ADCSTART         | 1              | Input        | Start of conversion                                                                                                                                                                                                                                                                 | ADC                    |

| PWRDWN           | 1              | Input        | ADC comparator power-down if 1. When asserted, the ADC will stop functioning, and the digital portion of the analog block will continue operating. This may result in invalid status flags from the analog block. Therefore, Microsemi does not recommend asserting the PWRDWN pin. | ADC                    |

| ADCRESET         | 1              | Input        | ADC resets and disables Analog Quad – active high                                                                                                                                                                                                                                   | ADC                    |

| BUSY             | 1              | Output       | 1 – Running conversion                                                                                                                                                                                                                                                              | ADC                    |

| CALIBRATE        | 1              | Output       | 1 – Power-up calibration                                                                                                                                                                                                                                                            | ADC                    |

| DATAVALID        | 1              | Output       | 1 – Valid conversion result                                                                                                                                                                                                                                                         | ADC                    |

| RESULT[11:0]     | 12             | Output       | Conversion result                                                                                                                                                                                                                                                                   | ADC                    |

| TMSTBINT         | 1              | Input        | Internal temp. monitor strobe                                                                                                                                                                                                                                                       | ADC                    |

| SAMPLE           | 1              | Output       | <ul> <li>1 – An analog signal is actively being sampled (stays high during signal acquisition only)</li> <li>0 – No analog signal is being sampled</li> </ul>                                                                                                                       | ADC                    |

| VAREFSEL         | 1              | Input        | 0 = Output internal voltage reference (2.56 V) to VAREF 1 = Input external voltage reference                                                                                                                                                                                        | ADC                    |

|                  |                |              | from VAREF and ADCGNDREF                                                                                                                                                                                                                                                            |                        |

| CHNUMBER[4:0]    | 5              | Input        | Analog input channel select                                                                                                                                                                                                                                                         | Input<br>multiplexer   |

| ACMCLK           | 1              | Input        | ACM clock                                                                                                                                                                                                                                                                           | ACM                    |

| ACMWEN           | 1              | Input        | ACM write enable – active high                                                                                                                                                                                                                                                      | ACM                    |

| ACMRESET         | 1              | Input        | ACM reset – active low                                                                                                                                                                                                                                                              | ACM                    |

| ACMWDATA[7:0]    | 8              | Input        | ACM write data                                                                                                                                                                                                                                                                      | ACM                    |

| ACMRDATA[7:0]    | 8              | Output       | ACM read data                                                                                                                                                                                                                                                                       | ACM                    |

| ACMADDR[7:0]     | 8              | Input        | ACM address                                                                                                                                                                                                                                                                         | ACM                    |

| CMSTB0 to CMSTB9 | 10             | Input        | Current monitor strobe – 1 per quad, active high                                                                                                                                                                                                                                    | Analog Quad            |

Table 2-36 • Analog Block Pin Description (continued)

| Signal Name     | Number of Bits | Direction | Function                                                  | Location of<br>Details |

|-----------------|----------------|-----------|-----------------------------------------------------------|------------------------|

| AG6             | 1              | Output    |                                                           | Analog Quad            |

| AT6             | 1              | Input     |                                                           | Analog Quad            |

| ATRETURN67      | 1              | Input     | Temperature monitor return shared by Analog Quads 6 and 7 | Analog Quad            |

| AV7             | 1              | Input     | Analog Quad 7                                             | Analog Quad            |

| AC7             | 1              | Input     |                                                           | Analog Quad            |

| AG7             | 1              | Output    |                                                           | Analog Quad            |

| AT7             | 1              | Input     |                                                           | Analog Quad            |

| AV8             | 1              | Input     | Analog Quad 8                                             | Analog Quad            |

| AC8             | 1              | Input     |                                                           | Analog Quad            |

| AG8             | 1              | Output    |                                                           | Analog Quad            |

| AT8             | 1              | Input     |                                                           | Analog Quad            |

| ATRETURN89      | 1              | Input     | Temperature monitor return shared by Analog Quads 8 and 9 | Analog Quad            |

| AV9             | 1              | Input     | Analog Quad 9                                             | Analog Quad            |

| AC9             | 1              | Input     |                                                           | Analog Quad            |

| AG9             | 1              | Output    |                                                           | Analog Quad            |

| AT9             | 1              | Input     |                                                           | Analog Quad            |

| RTCMATCH        | 1              | Output    | MATCH                                                     | RTC                    |

| RTCPSMMATCH     | 1              | Output    | MATCH connected to VRPSM                                  | RTC                    |

| RTCXTLMODE[1:0] | 2              | Output    | Drives XTLOSC RTCMODE[1:0] pins                           | RTC                    |

| RTCXTLSEL       | 1              | Output    | Drives XTLOSC MODESEL pin                                 | RTC                    |

| RTCCLK          | 1              | Input     | RTC clock input                                           | RTC                    |

## **Analog Quad**

With the Fusion family, Microsemi introduces the Analog Quad, shown in Figure 2-65 on page 2-81, as the basic analog I/O structure. The Analog Quad is a four-channel system used to precondition a set of analog signals before sending it to the ADC for conversion into a digital signal. To maximize the usefulness of the Analog Quad, the analog input signals can also be configured as LVTTL digital input signals. The Analog Quad is divided into four sections.

The first section is called the Voltage Monitor Block, and its input pin is named AV. It contains a two-channel analog multiplexer that allows an incoming analog signal to be routed directly to the ADC or allows the signal to be routed to a prescaler circuit before being sent to the ADC. The prescaler can be configured to accept analog signals between –12 V and 0 or between 0 and +12 V. The prescaler circuit scales the voltage applied to the ADC input pad such that it is compatible with the ADC input voltage range. The AV pin can also be used as a digital input pin.

The second section of the Analog Quad is called the Current Monitor Block. Its input pin is named AC. The Current Monitor Block contains all the same functions as the Voltage Monitor Block with one addition, which is a current monitoring function. A small external current sensing resistor (typically less than 1  $\Omega$ ) is connected between the AV and AC pins and is in series with a power source. The Current Monitor Block contains a current monitor circuit that converts the current through the external resistor to a voltage that can then be read using the ADC.

Refer to Table 2-46 on page 2-109 and the "Acquisition Time or Sample Time Control" section on page 2-107

$$t_{\text{sample}} = (2 + STC) \times t_{\text{ADCCLK}}$$

EQ 20

STC: Sample Time Control value (0-255)

t<sub>SAMPLE</sub> is the sample time

#### Table 2-46 • STC Bits Function

| Name | Bits  | Function            |

|------|-------|---------------------|

| STC  | [7:0] | Sample time control |

Sample time is computed based on the period of ADCCLK.

#### **Distribution Phase**

The second phase is called the distribution phase. During distribution phase, the ADC computes the equivalent digital value from the value stored in the input capacitor. In this phase, the output signal SAMPLE goes back to '0', indicating the sample is completed; but the BUSY signal remains '1', indicating the ADC is still busy for distribution. The distribution time depends strictly on the number of bits. If the ADC is configured as a 10-bit ADC, then 10 ADCCLK cycles are needed. EQ 8 describes the distribution time.

$$t_{distrib} = N \times t_{ADCCLK}$$

EQ 21

N: Number of bits

#### Post-Calibration Phase

The last phase is the post-calibration phase. This is an optional phase. The post-calibration phase takes two ADCCLK cycles. The output BUSY signal will remain '1' until the post-calibration phase is completed. If the post-calibration phase is skipped, then the BUSY signal goes to '0' after distribution phase. As soon as BUSY signal goes to '0', the DATAVALID signal goes to '1', indicating the digital result is available on the RESULT output signals. DATAVAILD will remain '1' until the next ADCSTART is asserted. Microsemi recommends enabling post-calibration to compensate for drift and temperature-dependent effects. This ensures that the ADC remains consistent over time and with temperature. The post-calibration phase is enabled by bit 3 of the Mode register. EQ 9 describes the post-calibration time.

$$t_{post-cal} = MODE[3] \times (2 \times t_{ADCCLK})$$

EQ 22

MODE[3]: Bit 3 of the Mode register, described in Table 2-41 on page 2-106.

The calculation for the conversion time for the ADC is summarized in EQ 23.

EQ 23

t<sub>conv</sub>: conversion time

$t_{sync\_read}$ : maximum time for a signal to synchronize with SYSCLK. For calculation purposes, the worst case is a period of SYSCLK,  $t_{SYSCLK}$ .

$t_{\text{sample}}$ : Sample time

t<sub>distrib</sub>: Distribution time

t<sub>post-cal</sub>: Post-calibration time

$t_{sync\_write}$ : Maximum time for a signal to synchronize with SYSCLK. For calculation purposes, the worst case is a period of SYSCLK,  $t_{SYSCLK}$ .

2-109 Revision 6

Table 2-57 details the settings available to control the prescaler values of the AV, AC, and AT pins. Note that the AT pin has a reduced number of available prescaler values.

Table 2-57 • Prescaler Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines<br>Bx[2:0] | Scaling<br>Factor, Pad to<br>ADC Input | LSB for an<br>8-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>10-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>12-Bit<br>Conversion <sup>1</sup><br>(mV) | Full-Scale<br>Voltage in<br>10-Bit<br>Mode <sup>2</sup> | Range Name |

|--------------------------|----------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|------------|

| 000 <sup>3</sup>         | 0.15625                                | 64                                                     | 16                                                     | 4                                                      | 16.368 V                                                | 16 V       |

| 001                      | 0.3125                                 | 32                                                     | 8                                                      | 2                                                      | 8.184 V                                                 | 8 V        |

| 010 <sup>3</sup>         | 0.625                                  | 16                                                     | 4                                                      | 1                                                      | 4.092 V                                                 | 4 V        |

| 011                      | 1.25                                   | 8                                                      | 2                                                      | 0.5                                                    | 2.046 V                                                 | 2 V        |

| 100                      | 2.5                                    | 4                                                      | 1                                                      | 0.25                                                   | 1.023 V                                                 | 1 V        |

| 101                      | 5.0                                    | 2                                                      | 0.5                                                    | 0.125                                                  | 0.5115 V                                                | 0.5 V      |

| 110                      | 10.0                                   | 1                                                      | 0.25                                                   | 0.0625                                                 | 0.25575 V                                               | 0.25 V     |

| 111                      | 20.0                                   | 0.5                                                    | 0.125                                                  | 0.03125                                                | 0.127875 V                                              | 0.125 V    |

#### Notes:

- 1. LSB voltage equivalences assume VAREF = 2.56 V.

- 2. Full Scale voltage for n-bit mode: ((2^n) 1) x (LSB for a n-bit Conversion)

- 3. These are the only valid ranges for the Temperature Monitor Block Prescaler.

Table 2-58 details the settings available to control the MUX within each of the AV, AC, and AT circuits. This MUX determines whether the signal routed to the ADC is the direct analog input, prescaled signal, or output of either the Current Monitor Block or the Temperature Monitor Block.

Table 2-58 • Analog Multiplexer Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[4] | Control Lines Bx[3] | ADC Connected To                      |

|---------------------|---------------------|---------------------------------------|

| 0                   | 0                   | Prescaler                             |

| 0                   | 1                   | Direct input                          |

| 1                   | 0                   | Current amplifier temperature monitor |

| 1                   | 1                   | Not valid                             |

Table 2-59 details the settings available to control the Direct Analog Input switch for the AV, AC, and AT pins.

Table 2-59 • Direct Analog Input Switch Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[5] | Direct Input Switch |

|---------------------|---------------------|

| 0                   | Off                 |

| 1                   | On                  |

Table 2-60 details the settings available to control the polarity of the signals coming to the AV, AC, and AT pins. Note that the only valid setting for the AT pin is logic 0 to support positive voltages.

Table 2-60 • Voltage Polarity Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)\*

| Control Lines Bx[6] | Input Signal Polarity |

|---------------------|-----------------------|

| 0                   | Positive              |

| 1                   | Negative              |

Note: \*The B3[6] signal for the AT pad should be kept at logic 0 to accept only positive voltages.

Table 2-77 • Comparison Table for 5 V-Compliant Receiver Scheme

| Scheme | Board Components                                                                                                                                                  | Speed                    | Current Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Two resistors                                                                                                                                                     | Low to high <sup>1</sup> | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2      | Resistor and Zener 3.3 V                                                                                                                                          | Medium                   | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3      | Bus switch                                                                                                                                                        | High                     | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4      | Minimum resistor value <sup>2</sup> R = 47 $\Omega$ at T <sub>J</sub> = 70°C R = 150 $\Omega$ at T <sub>J</sub> = 85°C R = 420 $\Omega$ at T <sub>J</sub> = 100°C | Medium                   | Maximum diode current at 100% duty cycle, signal constantly at '1' $52.7 \text{ mA at T}_J = 70^{\circ}\text{C} / 10\text{-year lifetime}$ $16.5 \text{ mA at T}_J = 85^{\circ}\text{C} / 10\text{-year lifetime}$ $5.9 \text{ mA at T}_J = 100^{\circ}\text{C} / 10\text{-year lifetime}$ For duty cycles other than 100%, the currents can be increased by a factor = 1 / (duty cycle). Example: 20% duty cycle at 70°C Maximum current = $(1/0.2)$ * 52.7 mA = 5 * 52.7 mA = 263.5 mA |

### Notes:

- 1. Speed and current consumption increase as the board resistance values decrease.

- 2. Resistor values ensure I/O diode long-term reliability.

2-147 Revision 6

Fusion Family of Mixed Signal FPGAs

Table 2-109 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 3.0 V

Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade  | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zh</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.            | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | -1              | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2 <sup>2</sup> | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 4 mA              | Std.            | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | -1              | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2              | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 6 mA              | Std.            | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1              | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

|                   | -2              | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

| 8 mA              | Std.            | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1              | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

|                   | -2              | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

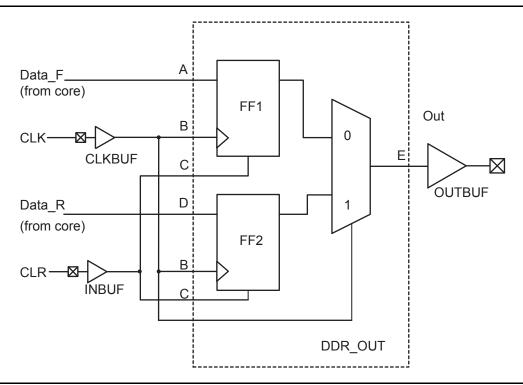

# **Output DDR**

Figure 2-144 • Output DDR Timing Model

Table 2-181 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (From, To) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | C, B                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | C, B                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | A, B                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | A, B                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

2-221 Revision 6

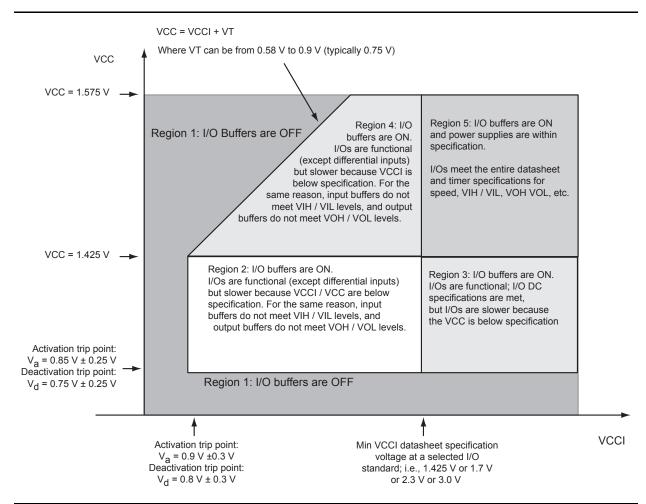

Figure 3-1 • I/O State as a Function of VCCI and VCC Voltage Levels

Table 3-8 • AFS1500 Quiescent Supply Current Characteristics (continued)

| Parameter | Description         | Conditions                                                            | Temp.                  | Min. | Тур. | Max. | Unit |

|-----------|---------------------|-----------------------------------------------------------------------|------------------------|------|------|------|------|

| IJTAG     | JTAG I/O quiescent  | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |      | 80   | 100  | μΑ   |

|           | current             | VJTAG = 3.63 V                                                        | T <sub>J</sub> = 85°C  |      | 80   | 100  | μΑ   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 80   | 100  | μΑ   |

|           |                     | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VJTAG = 0 V |                        |      | 0    | 0    | μA   |

| IPP       | Programming supply  | Non-programming mode,                                                 | T <sub>J</sub> = 25°C  |      | 39   | 80   | μΑ   |

|           | current             | VPUMP = 3.63 V                                                        | T <sub>J</sub> = 85°C  |      | 40   | 80   | μΑ   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 40   | 80   | μΑ   |

|           |                     | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> , VPUMP = 0 V    |                        |      | 0    | 0    | μA   |

| ICCNVM    | Embedded NVM        | Reset asserted, V <sub>CCNVM</sub> = 1.575 V                          | T <sub>J</sub> = 25°C  |      | 50   | 150  | μΑ   |

|           | current             |                                                                       | T <sub>J</sub> =85°C   |      | 50   | 150  | μΑ   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 50   | 150  | μΑ   |

| ICCPLL    | 1.5 V PLL quiescent | Operational standby                                                   | T <sub>J</sub> = 25°C  |      | 130  | 200  | μΑ   |

|           | current             | , VCCPLL = 1.575 V                                                    | T <sub>J</sub> = 85°C  |      | 130  | 200  | μΑ   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 130  | 200  | μΑ   |

#### Notes:

- 1. ICC is the 1.5 V power supplies, ICC and ICC15A.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

3-11 Revision 6

Table 3-11 • AFS090 Quiescent Supply Current Characteristics

| Parameter          | Description                | Conditions                                                                      | Temp.                  | Min | Тур  | Max | Unit |

|--------------------|----------------------------|---------------------------------------------------------------------------------|------------------------|-----|------|-----|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current    | Operational standby <sup>4</sup> ,<br>VCC = 1.575 V                             | T <sub>J</sub> = 25°C  |     | 5    | 7.5 | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 6.5  | 20  | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 14   | 48  | mA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , V <sub>CC</sub> = 0 V |                        |     | 0    | 0   | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies      | Operational standby <sup>4</sup> ,<br>VCC33 = 3.63 V                            | T <sub>J</sub> = 25°C  |     | 9.8  | 12  | mA   |

|                    | current                    |                                                                                 | T <sub>J</sub> = 85°C  |     | 9.8  | 12  | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 10.7 | 15  | mA   |

|                    |                            | Operational standby, only                                                       | T <sub>J</sub> = 25°C  |     | 0.30 | 2   | mA   |

|                    |                            | Analog Quad and –3.3 V output ON, VCC33 = 3.63 V                                | T <sub>J</sub> = 85°C  |     | 0.30 | 2   | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 0.45 | 2   | mA   |

|                    |                            | Standby mode <sup>5</sup> ,<br>VCC33 = 3.63 V                                   | T <sub>J</sub> = 25°C  |     | 2.9  | 2.9 | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 2.9  | 3.0 | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 3.5  | 6   | mA   |

|                    |                            | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                                        | T <sub>J</sub> = 25°C  |     | 17   | 18  | μΑ   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 18   | 20  | μΑ   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 24   | 25  | μΑ   |

| ICCI <sup>3</sup>  | I/O quiescent current      | Operational standby <sup>6</sup> ,<br>VCClx = 3.63 V                            | T <sub>J</sub> = 25°C  |     | 260  | 437 | μΑ   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 260  | 437 | μΑ   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 260  | 437 | μΑ   |

| IJTAG              | JTAG I/O quiescent current | Operational standby <sup>4</sup> ,<br>VJTAG = 3.63 V                            | T <sub>J</sub> = 25°C  |     | 80   | 100 | μΑ   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 80   | 100 | μΑ   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 80   | 100 | μΑ   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VJTAG = 0 V           |                        |     | 0    | 0   | μA   |

| IPP                | Programming supply current | Non-programming mode,<br>VPUMP = 3.63 V                                         | T <sub>J</sub> = 25°C  |     | 37   | 80  | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 37   | 80  | μΑ   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 80   | 100 | μΑ   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VPUMP = 0 V           |                        |     | 0    | 0   | μA   |

#### Notes:

- 1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, and ICCI2.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

### **Example of Power Calculation**

This example considers a shift register with 5,000 storage tiles, including a counter and memory that stores analog information. The shift register is clocked at 50 MHz and stores and reads information from a RAM.

The device used is a commercial AFS600 device operating in typical conditions.

The calculation below uses the power calculation methodology previously presented and shows how to determine the dynamic and static power consumption of resources used in the application.

Also included in the example is the calculation of power consumption in operating, standby, and sleep modes to illustrate the benefit of power-saving modes.

### Global Clock Contribution—P<sub>CLOCK</sub>

$F_{CLK} = 50 \text{ MHz}$

Number of sequential VersaTiles:  $N_{S-CELL} = 5,000$

Estimated number of Spines:  $N_{SPINES} = 5$ Estimated number of Rows:  $N_{ROW} = 313$

#### **Operating Mode**

```

\begin{split} & P_{\text{CLOCK}} = (\text{PAC1} + \text{N}_{\text{SPINE}} * \text{PAC2} + \text{N}_{\text{ROW}} * \text{PAC3} + \text{N}_{\text{S-CELL}} * \text{PAC4}) * F_{\text{CLK}} \\ & P_{\text{CLOCK}} = (0.0128 + 5 * 0.0019 + 313 * 0.00081 + 5,000 * 0.00011) * 50 \\ & P_{\text{CLOCK}} = 41.28 \text{ mW} \end{split}

```

#### Standby Mode and Sleep Mode

P<sub>CLOCK</sub> = 0 W

# $\begin{tabular}{ll} Logic-Sequential Cells, Combinational Cells, and Routing Net Contributions-P_{S-CELL}, \\ P_{C-CELL}, and P_{NET} \end{tabular}$

$F_{CLK} = 50 \text{ MHz}$

Number of sequential VersaTiles: N<sub>S-CELL</sub> = 5,000 Number of combinatorial VersaTiles: N<sub>C-CELL</sub> = 6,000 Estimated toggle rate of VersaTile outputs:  $\alpha_1$  = 0.1 (10%)

#### **Operating Mode**

```

\begin{split} & P_{S\text{-CELL}} = N_{S\text{-CELL}} * (P_{AC5} + (\alpha_1/2) * PAC6) * F_{CLK} \\ & P_{S\text{-CELL}} = 5,000 * (0.00007 + (0.1/2) * 0.00029) * 50 \\ & P_{S\text{-CELL}} = 21.13 \text{ mW} \\ & P_{C\text{-CELL}} = N_{C\text{-CELL}} * (\alpha_1/2) * PAC7 * F_{CLK} \\ & P_{C\text{-CELL}} = 6,000 * (0.1/2) * 0.00029 * 50 \\ & P_{C\text{-CELL}} = 4.35 \text{ mW} \\ & P_{NET} = (N_{S\text{-CELL}} + N_{C\text{-CELL}}) * (\alpha_1/2) * PAC8 * F_{CLK} \\ & P_{NET} = (5,000 + 6,000) * (0.1/2) * 0.0007 * 50 \\ & P_{NET} = 19.25 \text{ mW} \\ & P_{LOGIC} = P_{S\text{-CELL}} + P_{C\text{-CELL}} + P_{NET} \\ & P_{LOGIC} = 21.13 \text{ mW} + 4.35 \text{ mW} + 19.25 \text{ mW} \\ & P_{LOGIC} = 44.73 \text{ mW} \end{split}

```

### Standby Mode and Sleep Mode

Fusion Family of Mixed Signal FPGAs

| FG676                       |                 |  |  |  |

|-----------------------------|-----------------|--|--|--|

| Pin Number AFS1500 Function |                 |  |  |  |

| G13                         | IO22NDB1V0      |  |  |  |

| G14                         | IO22PDB1V0      |  |  |  |

| G15                         | GND             |  |  |  |

| G16                         | IO32PPB1V1      |  |  |  |

| G17                         | IO36NPB1V2      |  |  |  |

| G18                         | VCCIB1          |  |  |  |

| G19                         | GND             |  |  |  |

| G20                         | IO47NPB2V0      |  |  |  |

| G21                         | IO49PDB2V0      |  |  |  |

| G22                         | VCCIB2          |  |  |  |

| G23                         | IO46NDB2V0      |  |  |  |

| G24                         | GBC2/IO46PDB2V0 |  |  |  |

| G25                         | IO48NPB2V0      |  |  |  |

| G26                         | NC              |  |  |  |

| H1                          | GND             |  |  |  |

| H2                          | NC              |  |  |  |

| Н3                          | IO118NDB4V0     |  |  |  |

| H4                          | IO118PDB4V0     |  |  |  |

| H5                          | IO119NPB4V0     |  |  |  |

| H6                          | IO124NDB4V0     |  |  |  |

| H7                          | GND             |  |  |  |

| H8                          | VCOMPLA         |  |  |  |

| H9                          | VCCPLA          |  |  |  |

| H10                         | VCCIB0          |  |  |  |

| H11                         | IO12NDB0V1      |  |  |  |

| H12                         | IO12PDB0V1      |  |  |  |

| H13                         | VCCIB0          |  |  |  |

| H14                         | VCCIB1          |  |  |  |

| H15                         | IO30NDB1V1      |  |  |  |

| H16                         | IO30PDB1V1      |  |  |  |

| H17                         | VCCIB1          |  |  |  |

| H18                         | IO36PPB1V2      |  |  |  |

| H19                         | IO38NPB1V2      |  |  |  |

| H20                         | GND             |  |  |  |

| H21                         | IO49NDB2V0      |  |  |  |

| H22                         | IO50PDB2V0      |  |  |  |

| FG676      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AFS1500 Function |  |  |  |

| H23        | IO50NDB2V0       |  |  |  |

| H24        | IO51PDB2V0       |  |  |  |

| H25        | NC               |  |  |  |

| H26        | GND              |  |  |  |

| J1         | NC               |  |  |  |

| J2         | VCCIB4           |  |  |  |

| J3         | IO115PDB4V0      |  |  |  |

| J4         | GND              |  |  |  |

| J5         | IO116NDB4V0      |  |  |  |

| J6         | IO116PDB4V0      |  |  |  |

| J7         | VCCIB4           |  |  |  |

| J8         | IO117PDB4V0      |  |  |  |

| J9         | VCCIB4           |  |  |  |

| J10        | GND              |  |  |  |

| J11        | IO06NDB0V1       |  |  |  |

| J12        | IO06PDB0V1       |  |  |  |

| J13        | IO16NDB0V2       |  |  |  |

| J14        | IO16PDB0V2       |  |  |  |

| J15        | IO28NDB1V1       |  |  |  |

| J16        | IO28PDB1V1       |  |  |  |

| J17        | GND              |  |  |  |

| J18        | IO38PPB1V2       |  |  |  |

| J19        | IO53PDB2V0       |  |  |  |

| J20        | VCCIB2           |  |  |  |

| J21        | IO52PDB2V0       |  |  |  |

| J22        | IO52NDB2V0       |  |  |  |

| J23        | GND              |  |  |  |

| J24        | IO51NDB2V0       |  |  |  |

| J25        | VCCIB2           |  |  |  |

| J26        | NC               |  |  |  |

| K1         | NC               |  |  |  |

| K2         | NC               |  |  |  |

| K3         | IO115NDB4V0      |  |  |  |

| K4         | IO113PDB4V0      |  |  |  |

| K5         | VCCIB4           |  |  |  |

| K6         | IO114NDB4V0      |  |  |  |

| FG676                       |                  |  |  |  |

|-----------------------------|------------------|--|--|--|

| Pin Number AFS1500 Function |                  |  |  |  |

|                             |                  |  |  |  |

| K7                          | IO114PDB4V0      |  |  |  |

| K8                          | IO117NDB4V0      |  |  |  |

| K9                          | GND              |  |  |  |

| K10                         | VCC              |  |  |  |

| K11                         | VCCIB0           |  |  |  |

| K12                         | GND              |  |  |  |

| K13                         | VCCIB0           |  |  |  |

| K14                         | VCCIB1           |  |  |  |

| K15                         | GND              |  |  |  |

| K16                         | VCCIB1           |  |  |  |

| K17                         | GND              |  |  |  |

| K18                         | GND              |  |  |  |

| K19                         | IO53NDB2V0       |  |  |  |

| K20                         | IO57PDB2V0       |  |  |  |

| K21                         | GCA2/IO59PDB2V0  |  |  |  |

| K22                         | VCCIB2           |  |  |  |

| K23                         | IO54NDB2V0       |  |  |  |

| K24                         | IO54PDB2V0       |  |  |  |

| K25                         | NC               |  |  |  |

| K26                         | NC               |  |  |  |

| L1                          | GND              |  |  |  |

| L2                          | NC               |  |  |  |

| L3                          | IO112PPB4V0      |  |  |  |

| L4                          | IO113NDB4V0      |  |  |  |

| L5                          | GFB2/IO109PDB4V0 |  |  |  |

| L6                          | GFA2/IO110PDB4V0 |  |  |  |

| L7                          | IO112NPB4V0      |  |  |  |

| L8                          | IO104PDB4V0      |  |  |  |

| L9                          | IO111PDB4V0      |  |  |  |

| L10                         | VCCIB4           |  |  |  |

| L11                         | GND              |  |  |  |

| L12                         | VCC              |  |  |  |

| L13                         | GND              |  |  |  |

| L14                         | VCC              |  |  |  |

| L15                         | GND              |  |  |  |

| L16                         | VCC              |  |  |  |

# Package Pin Assignments

| FG676      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | AFS1500 Function |  |  |

| W25        | NC               |  |  |

| W26        | GND              |  |  |

| Y1         | NC               |  |  |

| Y2         | NC               |  |  |

| Y3         | GEB1/IO89PDB4V0  |  |  |

| Y4         | GEB0/IO89NDB4V0  |  |  |

| Y5         | VCCIB4           |  |  |

| Y6         | GEA1/IO88PDB4V0  |  |  |

| Y7         | GEA0/IO88NDB4V0  |  |  |

| Y8         | GND              |  |  |

| Y9         | VCC33PMP         |  |  |

| Y10        | NC               |  |  |

| Y11        | VCC33A           |  |  |

| Y12        | AG4              |  |  |

| Y13        | AT4              |  |  |

| Y14        | ATRTN2           |  |  |

| Y15        | AT5              |  |  |

| Y16        | VCC33A           |  |  |

| Y17        | NC               |  |  |

| Y18        | VCC33A           |  |  |

| Y19        | GND              |  |  |

| Y20        | TMS              |  |  |

| Y21        | VJTAG            |  |  |

| Y22        | VCCIB2           |  |  |

| Y23        | TRST             |  |  |

| Y24        | TDO              |  |  |

| Y25        | NC               |  |  |

| Y26        | NC               |  |  |

4-34 Revision 6

# Fusion Family of Mixed Signal FPGAs

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                                                              | Page             |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Revision 3 (continued)     | The "RC Oscillator" section was revised to correct a sentence that did not differentiate accuracy for commercial and industrial temperature ranges, which is given in Table 2-9 • Electrical Characteristics of RC Oscillator (SAR 33722).                                                                                                                                                           | 2-19             |

|                            | Figure 2-57 • FIFO Read and Figure 2-58 • FIFO Write are new (SAR 34840).                                                                                                                                                                                                                                                                                                                            | 2-72             |

|                            | The first paragraph of the "Offset" section was removed; it was intended to be replaced by the paragraph following it (SAR 22647).                                                                                                                                                                                                                                                                   |                  |

|                            | IOL and IOH values for 3.3 V GTL+ and 2.5 V GTL+ were corrected in Table 2-86 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions (SAR 39813).                                                                                                                                                                                            | 2-164            |

|                            | The drive strength, IOL, and IOH for 3.3 V GTL and 2.5 V GTL were changed from 25 mA to 20 mA in the following tables (SAR 37373):                                                                                                                                                                                                                                                                   |                  |

|                            | Table 2-86 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions,                                                                                                                                                                                                                                                                           | 2-164            |

|                            | Table 2-92 • Summary of I/O Timing Characteristics – Software Default Settings                                                                                                                                                                                                                                                                                                                       | 2-167            |

|                            | Table 2-96 • I/O Output Buffer Maximum Resistances 1                                                                                                                                                                                                                                                                                                                                                 | 2-169            |

|                            | Table 2-138 • Minimum and Maximum DC Input and Output Levels                                                                                                                                                                                                                                                                                                                                         | 2-199            |

|                            | Table 2-141 • Minimum and Maximum DC Input and Output Levels                                                                                                                                                                                                                                                                                                                                         | 2-200            |

|                            | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 34800): "It uses a 5 V-tolerant input buffer and push-pull output buffer."                                                                                                                                                                                                                                                   | 2-181            |

|                            | Corrected the inadvertent error in maximum values for LVPECL VIH and VIL and revised them to "3.6" in Table 2-171 • Minimum and Maximum DC Input and Output Levels, making these consistent with Table 3-1 • Absolute Maximum Ratings, and Table 3-4 • Overshoot and Undershoot Limits 1 (SAR 37687).                                                                                                | 2-211            |

|                            | The maximum frequency for global clock parameter was removed from Table 2-5 • AFS1500 Global Resource Timing through Table 2-8 • AFS090 Global Resource Timing because a frequency on the global is only an indication of what the global network can do. There are other limiters such as the SRAM, I/Os, and PLL. SmartTime software should be used to determine the design frequency (SAR 36955). | 2-16 to<br>2-17  |

| Revision 2<br>(March 2012) | The phrase "without debug" was removed from the "Soft ARM Cortex-M1 Fusion Devices (M1)" section (SAR 21390).                                                                                                                                                                                                                                                                                        | I                |

|                            | The "In-System Programming (ISP) and Security" section, "Security" section, "Flash Advantages" section, and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 34679).                                                                                | l, 1-2,<br>2-228 |

|                            | The Y security option and Licensed DPA Logo was added to the "Product Ordering Codes" section. The trademarked Licensed DPA Logo identifies that a product is covered by a DPA counter-measures license from Cryptography Research (SAR 34721).                                                                                                                                                      | III              |

|                            | The "Specifying I/O States During Programming" section is new (SAR 34693).                                                                                                                                                                                                                                                                                                                           | 1-9              |

|                            | The following information was added before Figure 2-17 • XTLOSC Macro:                                                                                                                                                                                                                                                                                                                               | 2-20             |

|                            | In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating (SAR 24119).                                                                                                                                                                                                                                          |                  |

|                            | Table 2-12 • Fusion CCC/PLL Specification was updated. A note was added indicating that when the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available (SAR 34814).                                                                                                                                                   | 2-28             |