Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | 110592                                                         |

| Number of I/O                  | 95                                                             |

| Number of Gates                | 600000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                                |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                             |

| Package / Case                 | 208-BFQFP                                                      |

| Supplier Device Package        | 208-PQFP (28x28)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/afs600-2pqg208i |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

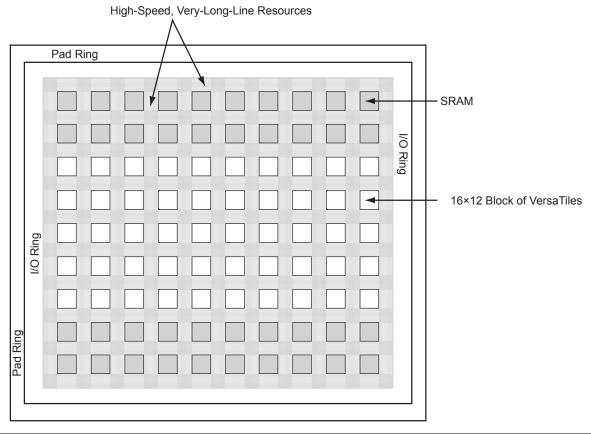

Figure 2-10 • Very-Long-Line Resources

## **Global Resource Characteristics**

## AFS600 VersaNet Topology

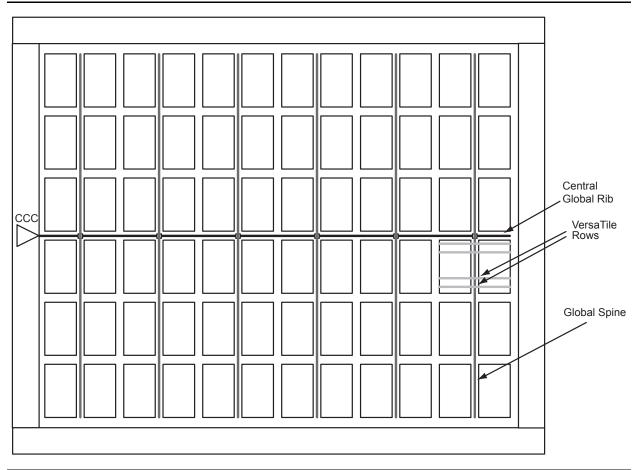

Clock delays are device-specific. Figure 2-15 is an example of a global tree used for clock routing. The global tree presented in Figure 2-15 is driven by a CCC located on the west side of the AFS600 device. It is used to drive all D-flip-flops in the device.

Figure 2-15 • Example of Global Tree Use in an AFS600 Device for Clock Routing

## PLL Macro

The PLL functionality of the clock conditioning block is supported by the PLL macro. Note that the PLL macro reference clock uses the CLKA input of the CCC block, which is only accessible from the global A[2:0] package pins. Refer to Figure 2-22 on page 2-25 for more information.

The PLL macro provides five derived clocks (three independent) from a single reference clock. The PLL feedback loop can be driven either internally or externally. The PLL macro also provides power-down input and lock output signals. During power-up, POWERDOWN should be asserted Low until VCC is up. See Figure 2-19 on page 2-23 for more information.

Inputs:

- · CLKA: selected clock input

- POWERDOWN (active low): disables PLLs. The default state is power-down on (active low).

Outputs:

- LOCK (active high): indicates that PLL output has locked on the input reference signal

- GLA, GLB, GLC: outputs to respective global networks

- YB, YC: allows output from the CCC to be routed back to the FPGA core

As previously described, the PLL allows up to five flexible and independently configurable clock outputs. Figure 2-23 on page 2-26 illustrates the various clock output options and delay elements.

As illustrated, the PLL supports three distinct output frequencies from a given input clock. Two of these (GLB and GLC) can be routed to the B and C global networks, respectively, and/or routed to the device core (YB and YC).

There are five delay elements to support phase control on all five outputs (GLA, GLB, GLC, YB, and YC).

There is also a delay element in the feedback loop that can be used to advance the clock relative to the reference clock.

The PLL macro reference clock can be driven by an INBUF macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

The PLL macro reference clock can be driven directly from the FPGA core.

The PLL macro reference clock can also be driven from an I/O routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate it from the hardwired I/O connection described earlier.

The visual PLL configuration in SmartGen, available with the Libero SoC and Designer tools, will derive the necessary internal divider ratios based on the input frequency and desired output frequencies selected by the user. SmartGen allows the user to select the various delays and phase shift values necessary to adjust the phases between the reference clock (CLKA) and the derived clocks (GLA, GLB, GLC, YB, and YC). SmartGen also allows the user to select where the input clock is coming from. SmartGen automatically instantiates the special macro, PLLINT, when needed.

## Flash Memory Block Addressing

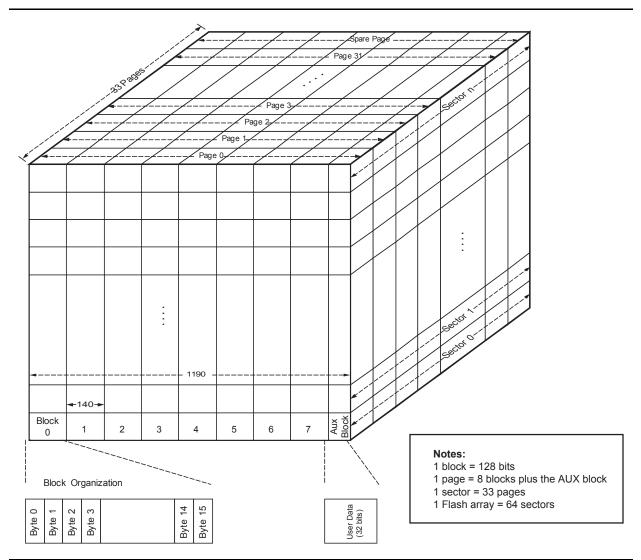

Figure 2-34 shows a graphical representation of the flash memory block.

Figure 2-34 • Flash Memory Block Organization

Each FB is partitioned into sectors, pages, blocks, and bytes. There are 64 sectors in an FB, and each sector contains 32 pages and 1 spare page. Each page contains 8 data blocks and 1 auxiliary block. Each data block contains 16 bytes of user data, and the auxiliary block contains 4 bytes of user data. Addressing for the FB is shown in Table 2-20.

### Table 2-20 • FB Address Bit Allocation ADDR[17:0]

| 17  | 12   | 11 | 7  | 6   | 4   | 3  | 0   |

|-----|------|----|----|-----|-----|----|-----|

| Sec | ctor | Pa | ge | Blo | ock | Ву | /te |

When the spare page of a sector is addressed (SPAREPAGE active), ADDR[11:7] are ignored.

When the Auxiliary block is addressed (AUXBLOCK active), ADDR[6:2] are ignored.

Note: The spare page of sector 0 is unavailable for any user data. Writes to this page will return an error, and reads will return all zeroes.

Access to the FB is controlled by the BUSY signal. The BUSY output is synchronous to the CLK signal. FB operations are only accepted in cycles where BUSY is logic 0.

### Write Operation

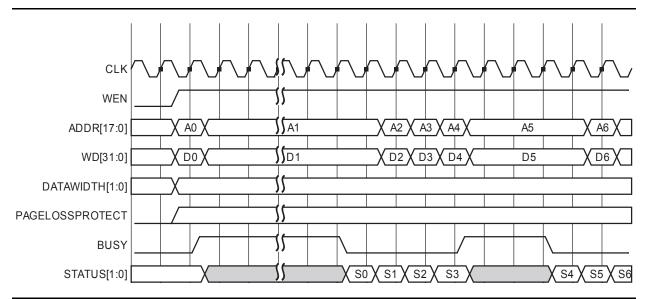

Write operations are initiated with the assertion of the WEN signal. Figure 2-35 on page 2-45 illustrates the multiple Write operations.

Figure 2-35 • FB Write Waveform

When a Write operation is initiated to a page that is currently not in the Page Buffer, the FB control logic will issue a BUSY signal to the user interface while the page is loaded from the FB Array into the Page Buffer. A Copy Page operation takes no less than 55 cycles and could take more if a Write or Unprotect Page operation is started while the NVM is busy pre-fetching a block. The basic operation is to read a block from the array into the block register (5 cycles) and then write the block register to the page buffer (1 cycle) and if necessary, when the copy is complete, reading the block being written from the page buffer into the block buffer (1 cycle). A page contains 9 blocks, so 9 blocks multiplied by 6 cycles to read/write each block, plus 1 is 55 cycles total. Subsequent writes to the same block of the page will incur no busy cycles. A write to another block in the page will assert BUSY for four cycles (five cycles when PIPE is asserted), to allow the data to be written to the Page Buffer and have the current block loaded into the Block Buffer.

Write operations are considered successful as long as the STATUS output is '00'. A non-zero STATUS indicates that an error was detected during the operation and the write was not performed. Note that the STATUS output is "sticky"; it is unchanged until another operation is started.

Only one word can be written at a time. Write word width is controlled by the DATAWIDTH bus. Users are responsible for keeping track of the contents of the Page Buffer and when to program it to the array. Just like a regular RAM, writing to random addresses is possible. Users can write into the Page Buffer in any order but will incur additional BUSY cycles. It is not necessary to modify the entire Page Buffer before saving it to nonvolatile memory.

Write errors include the following:

- 1. Attempting to write a page that is Overwrite Protected (STATUS = '01'). The write is not performed.

- 2. Attempting to write to a page that is not in the Page Buffer when Page Loss Protection is enabled (STATUS = '11'). The write is not performed.

## Table 2-25 • Flash Memory Block Timing (continued)Commercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter                  | Description                                                            | -2     | -1    | Std.  | Units |

|----------------------------|------------------------------------------------------------------------|--------|-------|-------|-------|

| t <sub>SUPGLOSSPRO</sub>   | Page Loss Protect Setup Time for the Control Logic                     | 1.69   | 1.93  | 2.27  | ns    |

| t <sub>HDPGLOSSPRO</sub>   | Page Loss Protect Hold Time for the Control Logic                      | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SUPGSTAT</sub>      | Page Status Setup Time for the Control Logic                           | 2.49   | 2.83  | 3.33  | ns    |

| t <sub>HDPGSTAT</sub>      | Page Status Hold Time for the Control Logic                            | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SUOVERWRPG</sub>    | Over Write Page Setup Time for the Control Logic                       | 1.88   | 2.14  | 2.52  | ns    |

| t <sub>HDOVERWRPG</sub>    | Over Write Page Hold Time for the Control Logic                        | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SULOCKREQUEST</sub> | Lock Request Setup Time for the Control Logic                          | 0.87   | 0.99  | 1.16  | ns    |

| t <sub>HDLOCKREQUEST</sub> | Lock Request Hold Time for the Control Logic                           | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>RECARNVM</sub>      | Reset Recovery Time                                                    | 0.94   | 1.07  | 1.25  | ns    |

| t <sub>REMARNVM</sub>      | Reset Removal Time                                                     | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>MPWARNVM</sub>      | Asynchronous Reset Minimum Pulse Width for the Control Logic           | 10.00  | 12.50 | 12.50 | ns    |

| t <sub>MPWCLKNVM</sub>     | Clock Minimum Pulse Width for the Control Logic                        | 4.00   | 5.00  | 5.00  | ns    |

|                            | Maximum Frequency for Clock for the Control Logic – for AFS1500/AFS600 | 80.00  | 80.00 | 80.00 | MHz   |

| <sup>I</sup> FMAXCLKNVM    | Maximum Frequency for Clock for the Control Logic – for AFS250/AFS090  | 100.00 | 80.00 | 80.00 | MHz   |

## FlashROM

Fusion devices have 1 kbit of on-chip nonvolatile flash memory that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core (Figure 2-45).

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports a synchronous read and can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank that is being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

The maximum FlashROM access clock is given in Table 2-26 on page 2-54. Figure 2-46 shows the timing behavior of the FlashROM access cycle—the address has to be set up on the rising edge of the clock for DOUT to be valid on the next falling edge of the clock.

If the address is unchanged for two cycles:

- D0 becomes invalid t<sub>CK2Q</sub> ns after the second rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the second falling edge.

If the address unchanged for three cycles:

- D0 becomes invalid t<sub>CK2Q</sub> ns after the second rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the second falling edge.

- D0 becomes invalid t<sub>CK2Q</sub> ns after the third rising edge of the clock.

- D0 becomes valid again  $t_{CK2Q}$  ns after the third falling edge.

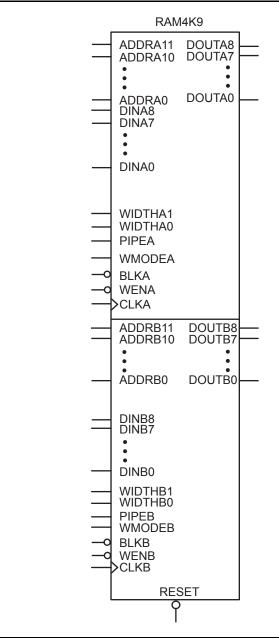

## **RAM4K9** Description

Figure 2-48 • RAM4K9

## **Timing Characteristics**

## Table 2-35 • FIFO

## Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup time                               | 1.34 | 1.52 | 1.79 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold time                                | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input data (WD) Setup time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input data (WD) Hold time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47 | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07 | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost-Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| 1                    | RESET Low to Data out Low on RD (flow-through)    | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272  | 231  | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

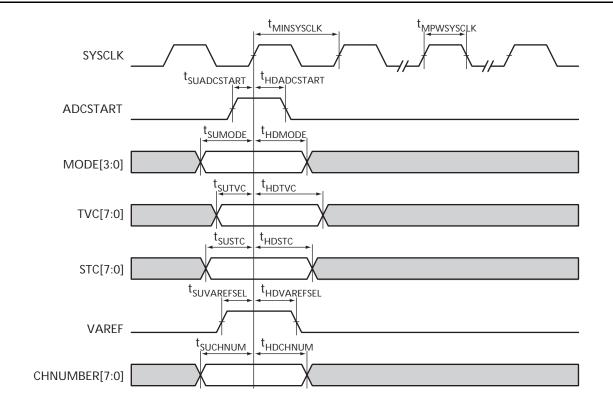

Table 2-36 describes each pin in the Analog Block. Each function within the Analog Block will be explained in detail in the following sections.

Table 2-36 • Analog Block Pin Description

| Signal Name      | Number<br>of Bits | Direction    | Function                                                                                                                                                      | Location of<br>Details |  |

|------------------|-------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|

| VAREF            | 1                 | Input/Output | Voltage reference for ADC                                                                                                                                     | ADC                    |  |

| ADCGNDREF        | 1                 | Input        | External ground reference                                                                                                                                     | ADC                    |  |

| MODE[3:0]        | 4                 | Input        | ADC operating mode                                                                                                                                            | ADC                    |  |

| SYSCLK           | 1                 | Input        | External system clock                                                                                                                                         |                        |  |

| TVC[7:0]         | 8                 | Input        | Clock divide control                                                                                                                                          | ADC                    |  |

| STC[7:0]         | 8                 | Input        | Sample time control                                                                                                                                           | ADC                    |  |

| ADCSTART         | 1                 | Input        | Start of conversion                                                                                                                                           | ADC                    |  |

| PWRDWN           | 1                 | Input        |                                                                                                                                                               |                        |  |

| ADCRESET         | 1                 | Input        | ADC resets and disables Analog Quad – active high                                                                                                             | ADC                    |  |

| BUSY             | 1                 | Output       | 1 – Running conversion                                                                                                                                        | ADC                    |  |

| CALIBRATE        | 1                 | Output       | 1 – Power-up calibration                                                                                                                                      | ADC                    |  |

| DATAVALID        | 1                 | Output       | 1 – Valid conversion result                                                                                                                                   | ADC                    |  |

| RESULT[11:0]     | 12                | Output       | Conversion result                                                                                                                                             | ADC                    |  |

| TMSTBINT         | 1                 | Input        | Internal temp. monitor strobe                                                                                                                                 | ADC                    |  |

| SAMPLE           | 1                 | Output       | <ul> <li>1 – An analog signal is actively being sampled (stays high during signal acquisition only)</li> <li>0 – No analog signal is being sampled</li> </ul> | ADC                    |  |

| VAREFSEL         | 1                 | Input        | 0 = Output internal voltage reference<br>(2.56 V) to VAREF                                                                                                    | ADC                    |  |

|                  |                   |              | 1 = Input external voltage reference<br>from VAREF and ADCGNDREF                                                                                              |                        |  |

| CHNUMBER[4:0]    | 5                 | Input        | Analog input channel select                                                                                                                                   | Input<br>multiplexer   |  |

| ACMCLK           | 1                 | Input        | ACM clock                                                                                                                                                     | ACM                    |  |

| ACMWEN           | 1                 | Input        | ACM write enable – active high                                                                                                                                | ACM                    |  |

| ACMRESET         | 1                 | Input        | ACM reset – active low                                                                                                                                        | ACM                    |  |

| ACMWDATA[7:0]    | 8                 | Input        | ACM write data                                                                                                                                                | ACM                    |  |

| ACMRDATA[7:0]    | 8                 | Output       | ACM read data                                                                                                                                                 | ACM                    |  |

| ACMADDR[7:0]     | 8                 | Input        | ACM address                                                                                                                                                   | ACM                    |  |

| CMSTB0 to CMSTB9 | 10                | Input        | Current monitor strobe – 1 per quad, active high                                                                                                              | Analog Quad            |  |

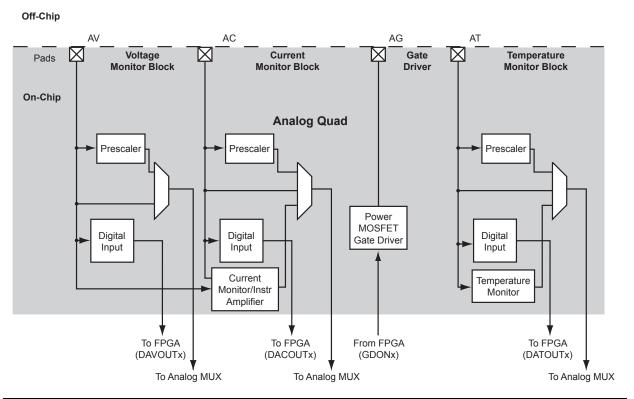

The third part of the Analog Quad is called the Gate Driver Block, and its output pin is named AG. This section is used to drive an external FET. There are two modes available: a High Current Drive mode and a Current Source Control mode. Both negative and positive voltage polarities are available, and in the current source control mode, four different current levels are available.

The fourth section of the Analog Quad is called the Temperature Monitor Block, and its input pin name is AT. This block is similar to the Voltage Monitor Block, except that it has an additional function: it can be used to monitor the temperature of an external diode-connected transistor. It has a modified prescaler and is limited to positive voltages only.

The Analog Quad can be configured during design time by Libero SoC; however, the ACM can be used to change the parameters of any of these I/Os during runtime. This type of change is referred to as a context switch. The Analog Quad is a modular structure that is replicated to generate the analog I/O resources. Each Fusion device supports between 5 and 10 Analog Quads.

The analog pads are numbered to clearly identify both the type of pad (voltage, current, gate driver, or temperature pad) and its corresponding Analog Quad (AV0, AC0, AG0, AT0, AV1, ..., AC9, AG9, and AT9). There are three types of input pads (AVx, ACx, and ATx) and one type of analog output pad (AGx). Since there can be up to 10 Analog Quads on a device, there can be a maximum of 30 analog input pads and 10 analog output pads.

Figure 2-65 • Analog Quad

### Figure 2-90 • Input Setup Time

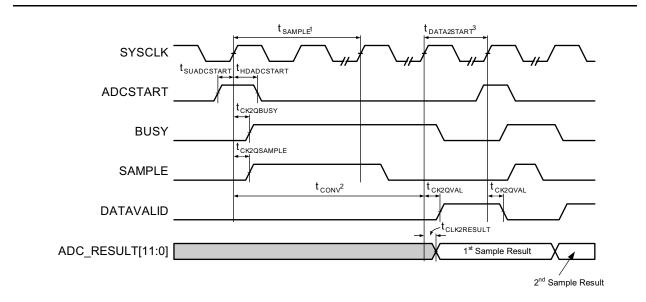

### Standard Conversion

### Notes:

1. Refer to EQ 20 on page 2-109 for the calculation on the sample time,  $t_{SAMPLE}$ .

2. See EQ 23 on page 2-109 for calculation of the conversion time,  $t_{CONV}$ .

3. Minimum time to issue an ADCSTART after DATAVALID is 1 SYSCLK period

Figure 2-91 • Standard Conversion Status Signal Timing Diagram

## Table 2-93 • Summary of I/O Timing Characteristics – Software Default SettingsCommercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,Worst-Case VCCI = I/O Standard DependentApplicable to Advanced I/Os

|                              |                     |           |                      |                         |        | r    |      |      | 1     |      |      |      |      | r    |      |       |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|------|------|------|-------|------|------|------|------|------|------|-------|

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t роит | top  | toin | tev  | teour | tzı  | tzH  | tız  | ZHţ  | tzLS | tzHS | Units |

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 12 mA               | High      | 35 pF                | -                       | 0.49   | 2.64 | 0.03 | 0.90 | 0.32  | 2.69 | 2.11 | 2.40 | 2.68 | 4.36 | 3.78 | ns    |

| 2.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | _                       | 0.49   | 2.66 | 0.03 | 0.98 | 0.32  | 2.71 | 2.56 | 2.47 | 2.57 | 4.38 | 4.23 | ns    |

| 1.8 V LVCMOS                 | 12 mA               | High      | 35 pF                | -                       | 0.49   | 2.64 | 0.03 | 0.91 | 0.32  | 2.69 | 2.27 | 2.76 | 3.05 | 4.36 | 3.94 | ns    |

| 1.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | -                       | 0.49   | 3.05 | 0.03 | 1.07 | 0.32  | 3.10 | 2.67 | 2.95 | 3.14 | 4.77 | 4.34 | ns    |

| 3.3 V PCI                    | Per PCI<br>spec     | High      | 10 pF                | 25 <sup>2</sup>         | 0.49   | 2.00 | 0.03 | 0.65 | 0.32  | 2.04 | 1.46 | 2.40 | 2.68 | 3.71 | 3.13 | ns    |

| 3.3 V PCI-X                  | Per PCI-X<br>spec   | High      | 10 pF                | 25 <sup>2</sup>         | 0.49   | 2.00 | 0.03 | 0.62 | 0.32  | 2.04 | 1.46 | 2.40 | 2.68 | 3.71 | 3.13 | ns    |

| LVDS                         | 24 mA               | High      | -                    | -                       | 0.49   | 1.37 | 0.03 | 1.20 | N/A   | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | ns    |

| LVPECL                       | 24 mA               | High      | -                    | -                       | 0.49   | 1.34 | 0.03 | 1.05 | N/A   | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | ns    |

Notes:

1. For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

2. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-123 on page 2-197 for connectivity. This resistor is not required during normal operation.

# Table 2-94 • Summary of I/O Timing Characteristics – Software Default SettingsCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V,Worst-Case VCCI = I/O Standard DependentApplicable to Standard I/Os

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t pour | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>Þ</sub> v | teour | tzı  | tzH  | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|-----------------|------------------|------------------|-------|------|------|-----------------|-----------------|-------|

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 8 mA                | High      | 35 pF                | -                       | 0.49   | 3.29            | 0.03             | 0.75             | 0.32  | 3.36 | 2.80 | 1.79            | 2.01            | ns    |

| 2.5 V LVCMOS                 | 8 mA                | High      | 35pF                 | Ι                       | 0.49   | 3.56            | 0.03             | 0.96             | 0.32  | 3.40 | 3.56 | 1.78            | 1.91            | ns    |

| 1.8 V LVCMOS                 | 4 mA                | High      | 35pF                 | Ι                       | 0.49   | 4.74            | 0.03             | 0.90             | 0.32  | 4.02 | 4.74 | 1.80            | 1.85            | ns    |

| 1.5 V LVCMOS                 | 2 mA                | High      | 35pF                 |                         | 0.49   | 5.71            | 0.03             | 1.06             | 0.32  | 4.71 | 5.71 | 1.83            | 1.83            | ns    |

Note: For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

## Table 2-96 • I/O Output Buffer Maximum Resistances <sup>1</sup> (continued)

| Standard                         | Drive Strength | R <sub>PULL-DOWN</sub><br>(ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|----------------------------------|----------------|-----------------------------------------------|---------------------------------------------|

| Applicable to Standard I/O Banks |                |                                               |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA           | 100                                           | 300                                         |

|                                  | 4 mA           | 100                                           | 300                                         |

|                                  | 6 mA           | 50                                            | 150                                         |

|                                  | 8 mA           | 50                                            | 150                                         |

| 2.5 V LVCMOS                     | 2 mA           | 100                                           | 200                                         |

|                                  | 4 mA           | 100                                           | 200                                         |

|                                  | 6 mA           | 50                                            | 100                                         |

|                                  | 8 mA           | 50                                            | 100                                         |

| 1.8 V LVCMOS                     | 2 mA           | 200                                           | 225                                         |

|                                  | 4 mA           | 100                                           | 112                                         |

| 1.5 V LVCMOS                     | 2 mA           | 200                                           | 224                                         |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

2. R<sub>(PULL-DOWN-MAX)</sub> = VOLspec / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

### Table 2-97 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|       | R <sub>(WEAK R</sub><br>(oh | PULL-UP)<br>ms) | R <sub>(WEAK PULL-DOWN)</sub> 2<br>(ohms) |       |  |  |

|-------|-----------------------------|-----------------|-------------------------------------------|-------|--|--|

| VCCI  | Min.                        | Max.            | Min.                                      | Max.  |  |  |

| 3.3 V | 10 k                        | 45 k            | 10 k                                      | 45 k  |  |  |

| 2.5 V | 11 k                        | 55 k            | 12 k                                      | 74 k  |  |  |

| 1.8 V | 18 k                        | 70 k            | 17 k                                      | 110 k |  |  |

| 1.5 V | 19 k                        | 90 k            | 19 k                                      | 140 k |  |  |

Notes:

R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>WEAK PULL-UP-MIN</sub>

R<sub>(WEAK PULL-DOWN-MAX)</sub> = VOLspec / I<sub>WEAK PULL-DOWN-MIN</sub>

# Table 2-132 • 1.5 V LVCMOS Low Slew<br/>Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCI = 1.4 V<br/>Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 12.33           | 0.04             | 1.42            | 0.43              | 11.79           | 12.33           | 2.45            | 2.32            | ns    |

|                   | -1             | 0.56              | 10.49           | 0.04             | 1.21            | 0.36              | 10.03           | 10.49           | 2.08            | 1.98            | ns    |

|                   | -2             | 0.49              | 9.21            | 0.03             | 1.06            | 0.32              | 8.81            | 9.21            | 1.83            | 1.73            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-133 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.65            | 0.04             | 1.42            | 0.43              | 6.31            | 7.65            | 2.45            | 2.45            | ns    |

|                   | -1             | 0.56              | 6.50            | 0.04             | 1.21            | 0.36              | 5.37            | 6.50            | 2.08            | 2.08            | ns    |

|                   | -2             | 0.49              | 5.71            | 0.03             | 1.06            | 0.32              | 4.71            | 5.71            | 1.83            | 1.83            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## Table 2-175 • Parameter Definitions and Measuring Nodes

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosup                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

*Note:* \*See Figure 2-138 on page 2-214 for more information.

### ATRTNx Temperature Monitor Return

AT returns are the returns for the temperature sensors. The cathode terminal of the external diodes should be connected to these pins. There is one analog return pin for every two Analog Quads. The x in the ATRTNx designator indicates the quad pairing (x = 0 for AQ1 and AQ2, x = 1 for AQ2 and AQ3, ..., x = 4 for AQ8 and AQ9). The signals that drive these pins are called out as ATRETURNxy in the software (where x and y refer to the quads that share the return signal). ATRTN is internally connected to ground. It can be left floating when it is unused. The maximum capacitance allowed across the AT pins is 500 pF.

#### GL Globals

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as Pro I/Os since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors. See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits" section on page 2-22.

Refer to the "User I/O Naming Convention" section on page 2-158 for a description of naming of global pins.

## JTAG Pins

Fusion devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the Fusion part must be supplied to allow JTAG signals to transition the Fusion device.

Isolating the JTAG power supply in a separate I/O bank gives greater flexibility with supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRST pin could be tied to GND.

#### TCK Test Clock

Test clock input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pullup/-down resistor. If JTAG is not used, Microsemi recommends tying off TCK to GND or VJTAG through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements. Refer to Table 2-183 for more information.

| VJTAG          | Tie-Off Resistance <sup>2, 3</sup> |

|----------------|------------------------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ                      |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ                      |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ                      |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                      |

Table 2-183 • Recommended Tie-Off Values for the TCK and TRST Pins

Notes:

- 1. Equivalent parallel resistance if more than one device is on JTAG chain.

- 2. The TCK pin can be pulled up/down.

- 3. The TRST pin can only be pulled down.

### TDI Test Data Input

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

#### TDO Test Data Output

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

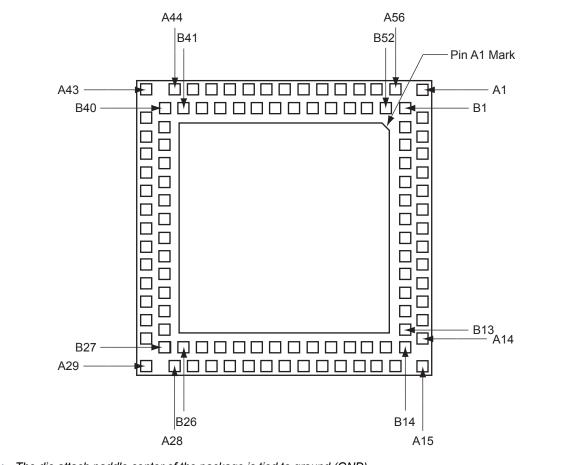

## 4 – Package Pin Assignments

## QN108

Note: The die attach paddle center of the package is tied to ground (GND).

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

Package Pin Assignments

| PQ208         |                 |                 | PQ208         |                 |                 |  |

|---------------|-----------------|-----------------|---------------|-----------------|-----------------|--|

| Pin<br>Number | AFS250 Function | AFS600 Function | Pin<br>Number | AFS250 Function | AFS600 Function |  |

| 1             | VCCPLA          | VCCPLA          | 38            | IO60NDB3V0      | GEB0/IO62NDB4V0 |  |

| 2             | VCOMPLA         | VCOMPLA         | 39            | GND             | GEA1/IO61PDB4V0 |  |

| 3             | GNDQ            | GAA2/IO85PDB4V0 | 40            | VCCIB3          | GEA0/IO61NDB4V0 |  |

| 4             | VCCIB3          | IO85NDB4V0      | 41            | GEB2/IO59PDB3V0 | GEC2/IO60PDB4V0 |  |

| 5             | GAA2/IO76PDB3V0 | GAB2/IO84PDB4V0 | 42            | IO59NDB3V0      | IO60NDB4V0      |  |

| 6             | IO76NDB3V0      | IO84NDB4V0      | 43            | GEA2/IO58PDB3V0 | VCCIB4          |  |

| 7             | GAB2/IO75PDB3V0 | GAC2/IO83PDB4V0 | 44            | IO58NDB3V0      | GNDQ            |  |

| 8             | IO75NDB3V0      | IO83NDB4V0      | 45            | VCC             | VCC             |  |

| 9             | NC              | IO77PDB4V0      | 45            | VCC             | VCC             |  |

| 10            | NC              | IO77NDB4V0      | 46            | VCCNVM          | VCCNVM          |  |

| 11            | VCC             | IO76PDB4V0      | 47            | GNDNVM          | GNDNVM          |  |

| 12            | GND             | IO76NDB4V0      | 48            | GND             | GND             |  |

| 13            | VCCIB3          | VCC             | 49            | VCC15A          | VCC15A          |  |

| 14            | IO72PDB3V0      | GND             | 50            | PCAP            | PCAP            |  |

| 15            | IO72NDB3V0      | VCCIB4          | 51            | NCAP            | NCAP            |  |

| 16            | GFA2/IO71PDB3V0 | GFA2/IO75PDB4V0 | 52            | VCC33PMP        | VCC33PMP        |  |

| 17            | IO71NDB3V0      | IO75NDB4V0      | 53            | VCC33N          | VCC33N          |  |

| 18            | GFB2/IO70PDB3V0 | GFC2/IO73PDB4V0 | 54            | GNDA            | GNDA            |  |

| 19            | IO70NDB3V0      | IO73NDB4V0      | 55            | GNDAQ           | GNDAQ           |  |

| 20            | GFC2/IO69PDB3V0 | VCCOSC          | 56            | NC              | AV0             |  |

| 21            | IO69NDB3V0      | XTAL1           | 57            | NC              | AC0             |  |

| 22            | VCC             | XTAL2           | 58            | NC              | AG0             |  |

| 23            | GND             | GNDOSC          | 59            | NC              | AT0             |  |

| 24            | VCCIB3          | GFC1/IO72PDB4V0 | 60            | NC              | ATRTN0          |  |

| 25            | GFC1/IO68PDB3V0 | GFC0/IO72NDB4V0 | 61            | NC              | AT1             |  |

| 26            | GFC0/IO68NDB3V0 | GFB1/IO71PDB4V0 | 62            | NC              | AG1             |  |

| 27            | GFB1/IO67PDB3V0 | GFB0/IO71NDB4V0 | 63            | NC              | AC1             |  |

| 28            | GFB0/IO67NDB3V0 | GFA1/IO70PDB4V0 | 64            | NC              | AV1             |  |

| 29            | VCCOSC          | GFA0/IO70NDB4V0 | 65            | AV0             | AV2             |  |

| 30            | XTAL1           | IO69PDB4V0      | 66            | AC0             | AC2             |  |

| 31            | XTAL2           | IO69NDB4V0      | 67            | AG0             | AG2             |  |

| 32            | GNDOSC          | VCC             | 68            | AT0             | AT2             |  |

| 33            | GEB1/IO62PDB3V0 | GND             | 69            | ATRTN0          | ATRTN1          |  |

| 34            | GEB0/IO62NDB3V0 | VCCIB4          | 70            | AT1             | AT3             |  |

| 35            | GEA1/IO61PDB3V0 | GEC1/IO63PDB4V0 | 71            | AG1             | AG3             |  |

| 36            | GEA0/IO61NDB3V0 | GEC0/IO63NDB4V0 | 72            | AC1             | AC3             |  |

| 37            | GEC2/IO60PDB3V0 | GEB1/IO62PDB4V0 | 73            | AV1             | AV3             |  |

Package Pin Assignments

| FG676                       |                 |  |  |  |

|-----------------------------|-----------------|--|--|--|

| Pin Number AFS1500 Function |                 |  |  |  |

| W25                         | NC              |  |  |  |

| W26                         | GND             |  |  |  |

| Y1                          | NC              |  |  |  |

| Y2                          | NC              |  |  |  |

| Y3                          | GEB1/IO89PDB4V0 |  |  |  |

| Y4                          | GEB0/IO89NDB4V0 |  |  |  |

| Y5                          | VCCIB4          |  |  |  |

| Y6                          | GEA1/IO88PDB4V0 |  |  |  |

| Y7                          | GEA0/IO88NDB4V0 |  |  |  |

| Y8                          | GND             |  |  |  |

| Y9                          | VCC33PMP        |  |  |  |

| Y10                         | NC              |  |  |  |

| Y11                         | VCC33A          |  |  |  |

| Y12                         | AG4             |  |  |  |

| Y13                         | AT4             |  |  |  |

| Y14                         | ATRTN2          |  |  |  |

| Y15                         | AT5             |  |  |  |

| Y16                         | VCC33A          |  |  |  |

| Y17                         | NC              |  |  |  |

| Y18                         | VCC33A          |  |  |  |

| Y19                         | GND             |  |  |  |

| Y20                         | TMS             |  |  |  |

| Y21                         | VJTAG           |  |  |  |

| Y22                         | VCCIB2          |  |  |  |

| Y23                         | TRST            |  |  |  |

| Y24                         | TDO             |  |  |  |

| Y25                         | NC              |  |  |  |

| Y26                         | NC              |  |  |  |

Fusion Family of Mixed Signal FPGAs

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                                                     | Page           |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Advance 1.0<br>(continued) | In Table 2-47 • ADC Characteristics in Direct Input Mode, the commercial conditions were updated and note 2 is new.                                                                                                                                                                                                                                                                         | 2-121          |

|                            | The $V_{\text{CC33ACAP}}$ signal name was changed to "XTAL1 Crystal Oscillator Circuit Input".                                                                                                                                                                                                                                                                                              | 2-228          |

|                            | Table 2-48 • Uncalibrated Analog Channel Accuracy* is new.                                                                                                                                                                                                                                                                                                                                  | 2-123          |

|                            | Table 2-49 • Calibrated Analog Channel Accuracy <sup>1,2,3</sup> is new.                                                                                                                                                                                                                                                                                                                    | 2-124          |

|                            | Table 2-50 • Analog Channel Accuracy: Monitoring Standard Positive Voltages is new.                                                                                                                                                                                                                                                                                                         | 2-125          |

|                            | In Table 2-57 • Voltage Polarity Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)*, the following I/O Bank names were changed:<br>Hot-Swap changed to Standard<br>LVDS changed to Advanced                                                                                                                                                                                        | 2-131          |

|                            | In Table 2-58 • Prescaler Op Amp Power-Down Truth Table—AV (x = 0), AC (x = 1),<br>and AT (x = 3), the following I/O Bank names were changed:<br>Hot-Swap changed to Standard<br>LVDS changed to Advanced                                                                                                                                                                                   | 2-132          |

|                            | In the title of Table 2-64 • I/O Standards Supported by Bank Type, LVDS I/O was changed to Advanced I/O.                                                                                                                                                                                                                                                                                    | 2-134          |

|                            | The title was changed from "Fusion Standard, LVDS, and Standard plus Hot-Swap I/O" to Table 2-68 • Fusion Standard and Advanced I/O Features. In addition, the table headings were all updated. The heading used to be Standard and LVDS I/O and was changed to Advanced I/O. Standard Hot-Swap was changed to just Standard.                                                               | 2-136          |

|                            | <ul> <li>This sentence was deleted from the "Slew Rate Control and Drive Strength" section:<br/>The Standard hot-swap I/Os do not support slew rate control. In addition, these references were changed:</li> <li>From: Fusion hot-swap I/O (Table 2-69 on page 2-122) To: Fusion Standard I/O</li> <li>From: Fusion LVDS I/O (Table 2-70 on page 2-122) To: Fusion Advanced I/O</li> </ul> | 2-152          |

|                            | The "Cold-Sparing Support" section was significantly updated.                                                                                                                                                                                                                                                                                                                               | 2-143          |

|                            | In the title of Table 2-75 • Fusion Standard I/O Standards—OUT_DRIVE Settings, Hot-Swap was changed to Standard.                                                                                                                                                                                                                                                                            | 2-153          |

|                            | In the title of Table 2-76 • Fusion Advanced I/O Standards—SLEW and OUT_DRIVE Settings, LVDS was changed to Advanced.                                                                                                                                                                                                                                                                       | 2-153          |

|                            | In the title of Table 2-81 • Fusion Standard and Advanced I/O Attributes vs. I/O Standard Applications, LVDS was changed to Advanced.                                                                                                                                                                                                                                                       | 2-157          |

|                            | In Figure 2-111 • Naming Conventions of Fusion Devices with Three Digital I/O<br>Banks and Figure 2-112 • Naming Conventions of Fusion Devices with Four I/O<br>Banks the following names were changed:                                                                                                                                                                                     | 2-160          |

|                            | Hot-Swap changed to Standard                                                                                                                                                                                                                                                                                                                                                                |                |

|                            | LVDS changed to Advanced                                                                                                                                                                                                                                                                                                                                                                    | 2 161          |

|                            | The Figure 2-113 • Timing Model was updated.<br>In the notes for Table 2-86 • Summary of Maximum and Minimum DC Input Levels<br>Applicable to Commercial and Industrial Conditions, T <sub>J</sub> was changed to T <sub>A</sub> .                                                                                                                                                          | 2-161<br>2-166 |