Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | -                                                               |

| Total RAM Bits                 | 36864                                                           |

| Number of I/O                  | 65                                                              |

| Number of Gates                | 250000                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                 |

| Package / Case                 | 180-WFQFN Dual Rows, Exposed Pad                                |

| Supplier Device Package        | 180-QFN (10x10)                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs250-1qng180 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

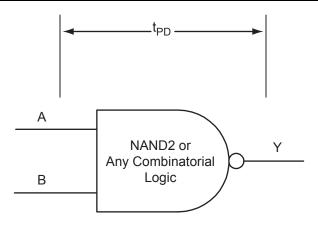

$t_{PD} = \text{MAX}(t_{PD(RR)},\,t_{PD(RF)},\,t_{PD(FF)},\,t_{PD(FR)})$  where edges are applicable for the particular combinatorial cell

Figure 2-4 • Combinatorial Timing Model and Waveforms

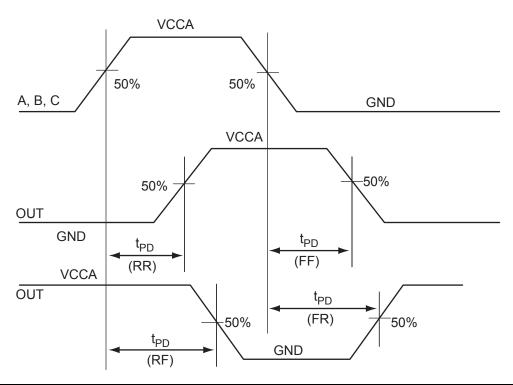

## **Real-Time Counter System**

The RTC system enables Fusion devices to support standby and sleep modes of operation to reduce power consumption in many applications.

- Sleep mode, typical 10 μA

- Standby mode (RTC running), typical 3 mA with 20 MHz

The RTC system is composed of five cores:

- RTC sub-block inside Analog Block (AB)

- Voltage Regulator and Power System Monitor (VRPSM)

- Crystal oscillator (XTLOSC); refer to the "Crystal Oscillator" section in the Fusion Clock Resources chapter of the Fusion FPGA Fabric User Guide for more detail.

- · Crystal clock; does not require instantiation in RTL

- · 1.5 V voltage regulator; does not require instantiation in RTL

All cores are powered by 3.3 V supplies, so the RTC system is operational without a 1.5 V supply during standby mode. Figure 2-27 shows their connection.

#### Notes:

- 1. Signals are hardwired internally and do not exist in the macro core.

- 2. User is only required to instantiate the VRPSM macro if the user wishes to specify PUPO behavior of the voltage regulator to be different from the default, or employ user logic to shut the voltage regulator off.

Figure 2-27 • Real-Time Counter System (not all the signals are shown for the AB macro)

2-31 Revision 6

The following signals are used to configure the RAM4K9 memory element.

#### WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 2-27).

Table 2-27 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA1, WIDTHA0                                                               | WIDTHB1, WIDTHB0 | D×W   |

|--------------------------------------------------------------------------------|------------------|-------|

| 00                                                                             | 00               | 4k×1  |

| 01                                                                             | 01               | 2k×2  |

| 10                                                                             | 10               | 1k×4  |

| 11                                                                             | 11               | 512×9 |

| Note: The aspect ratio settings are constant and cannot be changed on the fly. |                  |       |

#### **BLKA and BLKB**

These signals are active low and will enable the respective ports when asserted. When a BLKx signal is deasserted, the corresponding port's outputs hold the previous value.

#### WENA and WENB

These signals switch the RAM between read and write mode for the respective ports. A Low on these signals indicates a write operation, and a High indicates a read.

#### CLKA and CLKB

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A Low on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A High indicates a pipelined, read and data appears on the corresponding output in the next clock cycle.

## WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A Low on these signals makes the output retain data from the previous read. A High indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

#### RESET

This active low signal resets the output to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory.

#### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 2-28).

Table 2-28 • Address Pins Unused/Used for Various Supported Bus Widths

| D×W   | ADDRx   |        |  |

|-------|---------|--------|--|

| DAVV  | Unused  | Used   |  |

| 4k×1  | None    | [11:0] |  |

| 2k×2  | [11]    | [10:0] |  |

| 1k×4  | [11:10] | [9:0]  |  |

| 512×9 | [11:9]  | [8:0]  |  |

Note: The "x" in ADDRx implies A or B.

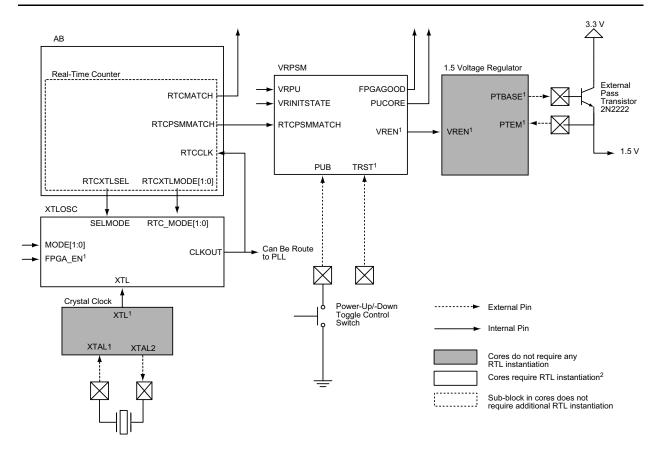

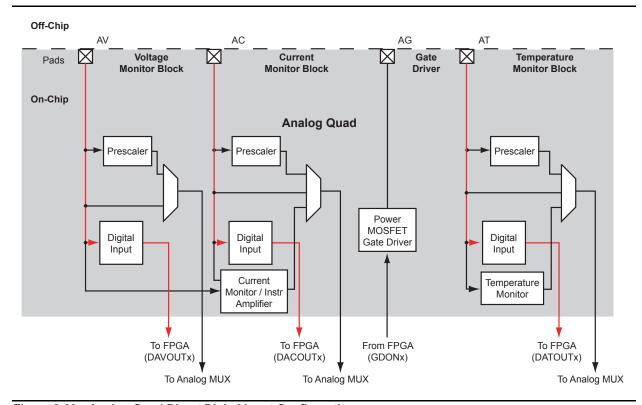

## **Direct Digital Input**

The AV, AC, and AT pads can also be configured as high-voltage digital inputs (Figure 2-69). As these pads are 12 V-tolerant, the digital input can also be up to 12 V. However, the frequency at which these pads can operate is limited to 10 MHz.

To enable one of these analog input pads to operate as a digital input, its corresponding Digital Input Enable (DENAxy) pin on the Analog Block must be pulled High, where x is either V, C, or T (for AV, AC, or AT pads, respectively) and y is in the range 0 to 9, corresponding to the appropriate Analog Quad.

When the pad is configured as a digital input, the signal will come out of the Analog Block macro on the appropriate DAxOUTy pin, where x represents the pad type (V for AV pad, C for AC pad, or T for AT pad) and y represents the appropriate Analog Quad number. Example: If the AT pad in Analog Quad 5 is configured as a digital input, it will come out on the DATOUT5 pin of the Analog Block macro.

Figure 2-69 • Analog Quad Direct Digital Input Configuration

2-85 Revision 6

EQ 16 through EQ 18 can be used to calculate the acquisition time required for a given input. The STC signal gives the number of sample periods in ADCCLK for the acquisition time of the desired signal. If the actual acquisition time is higher than the STC value, the settling time error can affect the accuracy of the ADC, because the sampling capacitor is only partially charged within the given sampling cycle. Example acquisition times are given in Table 2-44 and Table 2-45. When controlling the sample time for the ADC along with the use of the active bipolar prescaler, current monitor, or temperature monitor, the minimum sample time(s) for each must be obeyed. EQ 19 can be used to determine the appropriate value of STC.

$$VOUT = VIN(1 - e^{-t/RC})$$

EQ 16

For 0.5 LSB gain error, VOUT should be replaced with (VIN –(0.5 × LSB Value)):

You can calculate the minimum actual acquisition time by using EQ 16:

$$(VIN - 0.5 \times LSB \ Value) = VIN(1 - e^{-t/RC})$$

EQ 17

where VIN is the ADC reference voltage (VREF)

Solving EQ 17:

$$t = RC \times In (VIN / (0.5 \times LSB \ Value))$$

EQ 18

where  $R = Z_{INAD} + R_{SOURCE}$  and  $C = C_{INAD}$ .

Calculate the value of STC by using EQ 19.

$$t_{SAMPLE}$$

= (2 + STC) x (1 / ADCCLK) or  $t_{SAMPLE}$  = (2 + STC) x (ADC Clock Period)

EQ 19

where ADCCLK = ADC clock frequency in MHz.

$t_{SAMPLE}$  = 0.449 µs from bit resolution in Table 2-44.

ADC Clock frequency = 10 MHz or a 100 ns period.

STC =

$$(t_{SAMPLE} / (1 / 10 \text{ MHz})) - 2 = 4.49 - 2 = 2.49.$$

You must round up to 3 to accommodate the minimum sample time.

Table 2-44 • Acquisition Time Example with VAREF = 2.56 V

| VIN = 2.56V, R = 4K (R <sub>SOURCE</sub> ~ 0), C = 18 pF         |       |       |  |

|------------------------------------------------------------------|-------|-------|--|

| Resolution LSB Value (mV) Min. Sample/Hold Time for 0.5 LSB (μs) |       |       |  |

| 8                                                                | 10    | 0.449 |  |

| 10                                                               | 2.5   | 0.549 |  |

| 12                                                               | 0.625 | 0.649 |  |

Table 2-45 • Acquisition Time Example with VAREF = 3.3 V

| VIN = 3.3V, R = 4K (R <sub>SOURCE</sub> ~ 0), C = 18 pF          |        |       |  |

|------------------------------------------------------------------|--------|-------|--|

| Resolution LSB Value (mV) Min. Sample/Hold time for 0.5 LSB (μs) |        |       |  |

| 8                                                                | 12.891 | 0.449 |  |

| 10                                                               | 3.223  | 0.549 |  |

| 12                                                               | 0.806  | 0.649 |  |

## Sample Phase

A conversion is performed in three phases. In the first phase, the analog input voltage is sampled on the input capacitor. This phase is called sample phase. During the sample phase, the output signals BUSY and SAMPLE change from '0' to '1', indicating the ADC is busy and sampling the analog signal. The sample time can be controlled by input signals STC[7:0]. The sample time can be calculated by EQ 20. When controlling the sample time for the ADC along with the use of Prescaler or Current Monitor or Temperature Monitor, the minimum sample time for each must be obeyed.

Table 2-52 • Calibrated Analog Channel Accuracy <sup>1,2,3</sup>

Worst-Case Industrial Conditions, T<sub>J</sub> = 85°C

|                     | Condition                                                             | Total Channel Error (LSB)                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

|---------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Prescaler Range (V) | Input Voltage <sup>4</sup> (V)                                        | Negative Max.                                                         | Median                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Positive Max.       |

| ositive Range       |                                                                       | ADC in 10-Bit Mode                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

| 16                  | 0.300 to 12.0                                                         | -6                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                   |

| 8                   | 0.250 to 8.00                                                         | -6                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                   |

| 4                   | 0.200 to 4.00                                                         | <b>-7</b>                                                             | <b>–1</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                   |

| 2                   | 0.150 to 2.00                                                         | <b>-7</b>                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7                   |

| 1                   | 0.050 to 1.00                                                         | -6                                                                    | -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                   |

| 16                  | 0.300 to 16.0                                                         | <b>-</b> 5                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                   |

| 4                   | 0.100 to 4.00                                                         | <b>-7</b>                                                             | -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                   |

| egative Range       |                                                                       | Α                                                                     | DC in 10-Bit Mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ode                 |

| 16                  | -0.400 to -10.5                                                       | <b>-7</b>                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                   |

| 8                   | -0.350 to -8.00                                                       | <b>-7</b>                                                             | -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                   |

| 4                   | -0.300 to -4.00                                                       | <b>-</b> 7                                                            | -2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                   |

| 2                   | -0.250 to -2.00                                                       | <b>-7</b>                                                             | -2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                   |

| 1                   | −0.050 to −1.00                                                       | -16                                                                   | -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                  |

|                     | 16 8 4 2 11 16 4 egative Range 16 8 4 2 2 1 2 2 2 4 2 4 2 2 4 2 4 2 2 | Prescaler Range (V) Input Voltage <sup>4</sup> (V)  ositive Range  16 | Prescaler Range (V)         Input Voltage <sup>4</sup> (V)         Negative Max.           0sitive Range         A           16         0.300 to 12.0         -6           8         0.250 to 8.00         -6           4         0.200 to 4.00         -7           2         0.150 to 2.00         -7           1         0.050 to 1.00         -6           4         0.300 to 16.0         -5           4         0.100 to 4.00         -7           egative Range         A           16         -0.400 to -10.5         -7           8         -0.350 to -8.00         -7           4         -0.300 to -4.00         -7           2         -0.250 to -2.00         -7 | Prescaler Range (V) |

#### Notes:

- 1. Channel Accuracy includes prescaler and ADC accuracies. For 12-bit mode, multiply the LSB count by 4. For 8-bit mode, divide the LSB count by 4. Overall accuracy remains the same.

- 2. Requires enabling Analog Calibration using SmartGen Analog System Builder. For further details, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

- 3. Calibrated with two-point calibration methodology, using 20% and 80% full-scale points.

- 4. The lower limit of the input voltage is determined by the prescaler input offset.

2-123 Revision 6

Table 2-61 details the settings available to either power down or enable the prescaler associated with the analog inputs AV, AC, and AT.

Table 2-61 • Prescaler Op Amp Power-Down Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[7] | Prescaler Op Amp |  |

|---------------------|------------------|--|

| 0                   | Power-down       |  |

| 1                   | Operational      |  |

Table 2-62 details the settings available to enable the Current Monitor Block associated with the AC pin.

### Table 2-62 • Current Monitor Input Switch Control Truth Table—AV (x = 0)

| Control Lines B0[4] | Current Monitor Input Switch |  |

|---------------------|------------------------------|--|

| 0                   | Off                          |  |

| 1                   | On                           |  |

Table 2-63 details the settings available to configure the drive strength of the gate drive when not in high-drive mode.

### Table 2-63 • Low-Drive Gate Driver Current Truth Table (AG)

| Control Lines B2[3] | Control Lines B2[2] | Current (μA) |

|---------------------|---------------------|--------------|

| 0                   | 0                   | 1            |

| 0                   | 1                   | 3            |

| 1                   | 0                   | 10           |

| 1                   | 1                   | 30           |

Table 2-64 details the settings available to set the polarity of the gate driver (either p-channel- or n-channel-type devices).

## Table 2-64 • Gate Driver Polarity Truth Table (AG)

| Control Lines B2[6] | Gate Driver Polarity |  |

|---------------------|----------------------|--|

| 0                   | Positive             |  |

| 1                   | Negative             |  |

Table 2-65 details the settings available to turn on the Gate Driver and set whether high-drive mode is on or off.

## Table 2-65 • Gate Driver Control Truth Table (AG)

| Control Lines B2[7] | GDON | Gate Driver   |

|---------------------|------|---------------|

| 0                   | 0    | Off           |

| 0                   | 1    | Low drive on  |

| 1                   | 0    | Off           |

| 1                   | 1    | High drive on |

Table 2-66 details the settings available to turn on and off the chip internal temperature monitor.

Note: For the internal temperature monitor to function, Bit 0 of Byte 2 for all 10 Quads must be set.

#### Table 2-66 • Internal Temperature Monitor Control Truth Table

| Control Lines B2[0] | PDTMB | Chip Internal Temperature Monitor |

|---------------------|-------|-----------------------------------|

| 0                   | 0     | Off                               |

| 1                   | 1     | On                                |

2-131 Revision 6

## **I/O Registers**

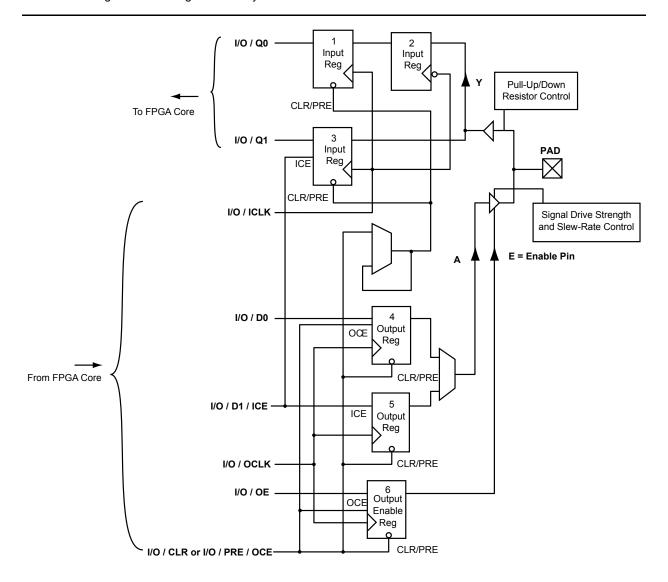

Each I/O module contains several input, output, and enable registers. Refer to Figure 2-100 for a simplified representation of the I/O block.

The number of input registers is selected by a set of switches (not shown in Figure 2-100) between registers to implement single or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user.

A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy some rules.

Note: Fusion I/Os have registers to support DDR functionality (see the "Double Data Rate (DDR) Support" section on page 2-139 for more information).

Figure 2-100 • I/O Block Logical Representation

Fusion Family of Mixed Signal FPGAs

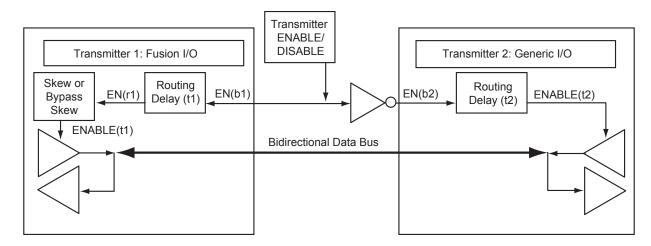

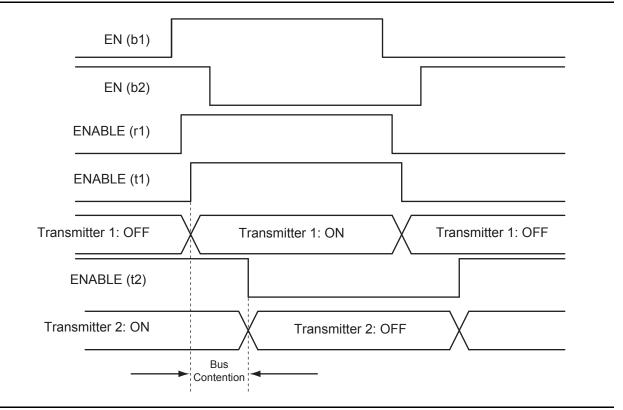

At the system level, the skew circuit can be used in applications where transmission activities on bidirectional data lines need to be coordinated. This circuit, when selected, provides a timing margin that can prevent bus contention and subsequent data loss or transmitter overstress due to transmitter-to-transmitter current shorts. Figure 2-110 presents an example of the skew circuit implementation in a bidirectional communication system. Figure 2-111 shows how bus contention is created, and Figure 2-112 on page 2-151 shows how it can be avoided with the skew circuit.

Figure 2-110 • Example of Implementation of Skew Circuits in Bidirectional Transmission Systems Using Fusion Devices

Figure 2-111 • Timing Diagram (bypasses skew circuit)

Table 2-96 • I/O Output Buffer Maximum Resistances <sup>1</sup> (continued)

| Standard                      | Drive Strength              | R <sub>PULL-DOWN</sub> (ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|-------------------------------|-----------------------------|--------------------------------------------|---------------------------------------------|

| HSTL (I)                      | 8 mA                        | 50                                         | 50                                          |

| HSTL (II)                     | 15 mA                       | 25                                         | 25                                          |

| SSTL2 (I)                     | 17 mA                       | 27                                         | 31                                          |

| SSTL2 (II)                    | 21 mA                       | 13                                         | 15                                          |

| SSTL3 (I)                     | 16 mA                       | 44                                         | 69                                          |

| SSTL3 (II)                    | 24 mA                       | 18                                         | 32                                          |

| Applicable to Advanced I/O Ba | nks                         | 1                                          |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS    | 2 mA                        | 100                                        | 300                                         |

|                               | 4 mA                        | 100                                        | 300                                         |

|                               | 6 mA                        | 50                                         | 150                                         |

|                               | 8 mA                        | 50                                         | 150                                         |

|                               | 12 mA                       | 25                                         | 75                                          |

|                               | 16 mA                       | 17                                         | 50                                          |

|                               | 24 mA                       | 11                                         | 33                                          |

| 2.5 V LVCMOS                  | 2 mA                        | 100                                        | 200                                         |

|                               | 4 mA                        | 100                                        | 200                                         |

|                               | 6 mA                        | 50                                         | 100                                         |

|                               | 8 mA                        | 50                                         | 100                                         |

|                               | 12 mA                       | 25                                         | 50                                          |

|                               | 16 mA                       | 20                                         | 40                                          |

|                               | 24 mA                       | 11                                         | 22                                          |

| 1.8 V LVCMOS                  | 2 mA                        | 200                                        | 225                                         |

|                               | 4 mA                        | 100                                        | 112                                         |

|                               | 6 mA                        | 50                                         | 56                                          |

|                               | 8 mA                        | 50                                         | 56                                          |

|                               | 12 mA                       | 20                                         | 22                                          |

|                               | 16 mA                       | 20                                         | 22                                          |

| 1.5 V LVCMOS                  | 2 mA                        | 200                                        | 224                                         |

|                               | 4 mA                        | 100                                        | 112                                         |

|                               | 6 mA                        | 67                                         | 75                                          |

|                               | 8 mA                        | 33                                         | 37                                          |

|                               | 12 mA                       | 33                                         | 37                                          |

| 3.3 V PCI/PCI-X               | Per PCI/PCI-X specification | 25                                         | 75                                          |

### Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

<sup>2.</sup>  $R_{(PULL-DOWN-MAX)} = VOLspec / I_{OLspec}$

<sup>3.</sup> R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

Table 2-98 • I/O Short Currents IOSH/IOSL (continued)

|                                  | Drive Strength              | IOSH (mA)* | IOSL (mA)* |

|----------------------------------|-----------------------------|------------|------------|

| 2.5 V LVCMOS                     | 2 mA                        | 16         | 18         |

|                                  | 4 mA                        | 16         | 18         |

|                                  | 6 mA                        | 32         | 37         |

|                                  | 8 mA                        | 32         | 37         |

|                                  | 12 mA                       | 65         | 74         |

|                                  | 16 mA                       | 83         | 87         |

|                                  | 24 mA                       | 169        | 124        |

| 1.8 V LVCMOS                     | 2 mA                        | 9          | 11         |

|                                  | 4 mA                        | 17         | 22         |

|                                  | 6 mA                        | 35         | 44         |

|                                  | 8 mA                        | 45         | 51         |

|                                  | 12 mA                       | 91         | 74         |

|                                  | 16 mA                       | 91         | 74         |

| 1.5 V LVCMOS                     | 2 mA                        | 13         | 16         |

|                                  | 4 mA                        | 25         | 33         |

|                                  | 6 mA                        | 32         | 39         |

|                                  | 8 mA                        | 66         | 55         |

|                                  | 12 mA                       | 66         | 55         |

| 3.3 V PCI/PCI-X                  | Per PCI/PCI-X specification | 103        | 109        |

| Applicable to Standard I/O Banks |                             |            |            |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA                        | 25         | 27         |

|                                  | 4 mA                        | 25         | 27         |

|                                  | 6 mA                        | 51         | 54         |

|                                  | 8 mA                        | 51         | 54         |

| 2.5 V LVCMOS                     | 2 mA                        | 16         | 18         |

|                                  | 4 mA                        | 16         | 18         |

|                                  | 6 mA                        | 32         | 37         |

|                                  | 8 mA                        | 32         | 37         |

| 1.8 V LVCMOS                     | 2 mA                        | 9          | 11         |

|                                  | 4 mA                        | 17         | 22         |

| 1.5 V LVCMOS                     | 2 mA                        | 13         | 16         |

Note:  $*T_J = 100$ °C

The length of time an I/O can with stand IOSH/IOSL events depends on the junction temperature. The reliability data below is based on a 3.3 V, 36 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than six months to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

2-173 Revision 6

## Differential I/O Characteristics

Configuration of the I/O modules as a differential pair is handled by the Microsemi Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with these standards.

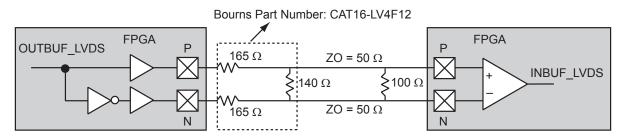

#### **LVDS**

Low-Voltage Differential Signal (ANSI/TIA/EIA-644) is a high-speed differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-134. The building blocks of the LVDS transmitter—receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Figure 2-134 • LVDS Circuit Diagram and Board-Level Implementation

| Table 2-168 • Minimum ar | nd Maximum | DC Input and | Output Levels |

|--------------------------|------------|--------------|---------------|

|--------------------------|------------|--------------|---------------|

| DC Parameter       | Description                 | Min.  | Тур.  | Max.  | Units |

|--------------------|-----------------------------|-------|-------|-------|-------|

| VCCI               | Supply Voltage              | 2.375 | 2.5   | 2.625 | V     |

| VOL                | Output Low Voltage          | 0.9   | 1.075 | 1.25  | V     |

| VOH                | Input High Voltage          | 1.25  | 1.425 | 1.6   | V     |

| IOL <sup>1</sup>   | Output Low Voltage          | 0.65  | 0.91  | 1.16  | mA    |

| IOH <sup>1</sup>   | Output High Voltage         | 0.65  | 0.91  | 1.16  | mA    |

| VI                 | Input Voltage               | 0     |       | 2.925 | V     |

| IIL <sup>2,3</sup> | Input Low Voltage           |       |       | 10    | μΑ    |

| IIH <sup>2,4</sup> | Input High Voltage          |       |       | 10    | μΑ    |

| VODIFF             | Differential Output Voltage | 250   | 350   | 450   | mV    |

| VOCM               | Output Common Mode Voltage  | 1.125 | 1.25  | 1.375 | V     |

| VICM               | Input Common Mode Voltage   | 0.05  | 1.25  | 2.35  | V     |

| VIDIFF             | Input Differential Voltage  | 100   | 350   |       | mV    |

## Notes:

- 1. IOL/IOH defined by VODIFF/(Resistor Network)

- 2. Currents are measured at 85°C junction temperature.

- 3. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

2-209 Revision 6

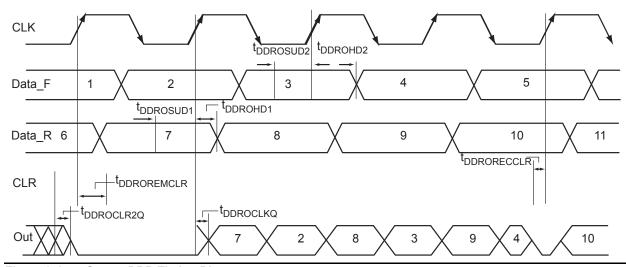

Figure 2-145 • Output DDR Timing Diagram

## **Timing Characteristics**

Table 2-182 • Output DDR Propagation Delays Commercial Temperature Range Conditions:  $T_J = 70$ °C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                           | -2   | <b>-1</b> | Std. | Units |

|-------------------------|-------------------------------------------------------|------|-----------|------|-------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out of DDR for Output DDR                    | 0.70 | 0.80      | 0.94 | ns    |

| t <sub>DDROSUD1</sub>   | Data_F Data Setup for Output DDR                      | 0.38 | 0.43      | 0.51 | ns    |

| t <sub>DDROSUD2</sub>   | Data_R Data Setup for Output DDR                      | 0.38 | 0.43      | 0.51 | ns    |

| t <sub>DDROHD1</sub>    | Data_F Data Hold for Output DDR                       | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>DDROHD2</sub>    | Data_R Data Hold for Output DDR                       | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out for Output DDR              | 0.80 | 0.91      | 1.07 | ns    |

| t <sub>DDROREMCLR</sub> | Asynchronous Clear Removal Time for Output DDR        | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>DDRORECCLR</sub> | Asynchronous Clear Recovery Time for Output DDR       | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>DDROWCLR1</sub>  | Asynchronous Clear Minimum Pulse Width for Output DDR | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>DDROCKMPWH</sub> | Clock Minimum Pulse Width High for the Output DDR     | 0.36 | 0.41      | 0.48 | ns    |

| t <sub>DDROCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output DDR      | 0.32 | 0.37      | 0.43 | ns    |

| F <sub>DDOMAX</sub>     | Maximum Frequency for the Output DDR                  | 1404 | 1232      | 1048 | MHz   |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### XTAL2 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

## **Security**

Fusion devices have a built-in 128-bit AES decryption core. The decryption core facilitates highly secure, in-system programming of the FPGA core array fabric and the FlashROM. The FlashROM and the FPGA core fabric can be programmed independently from each other, allowing the FlashROM to be updated without the need for change to the FPGA core fabric. The AES master key is stored in on-chip nonvolatile memory (flash). The AES master key can be preloaded into parts in a security-protected programming environment (such as the Microsemi in-house programming center), and then "blank" parts can be shipped to an untrusted programming or manufacturing center for final personalization with an AES-encrypted bitstream. Late stage product changes or personalization can be implemented easily and with high level security by simply sending a STAPL file with AES-encrypted data. Highly secure remote field updates over public networks (such as the Internet) are possible by sending and programming a STAPL file with AES-encrypted data. For more information, refer to the *Fusion Security* application note.

## 128-Bit AES Decryption

The 128-bit AES standard (FIPS-197) block cipher is the National Institute of Standards and Technology (NIST) replacement for DES (Data Encryption Standard FIPS46-2). AES has been designed to protect sensitive government information well into the 21st century. It replaces the aging DES, which NIST adopted in 1977 as a Federal Information Processing Standard used by federal agencies to protect sensitive, unclassified information. The 128-bit AES standard has  $3.4 \times 10^{38}$  possible 128-bit key variants, and it has been estimated that it would take 1,000 trillion years to crack 128-bit AES cipher text using exhaustive techniques. Keys are stored (protected with security) in Fusion devices in nonvolatile flash memory. All programming files sent to the device can be authenticated by the part prior to programming to ensure that bad programming data is not loaded into the part that may possibly damage it. All programming verification is performed on-chip, ensuring that the contents of Fusion devices remain as secure as possible.

AES decryption can also be used on the 1,024-bit FlashROM to allow for remote updates of the FlashROM contents. This allows for easy support of subscription model products and protects them with measures designed to provide the highest level of security available. See the application note *Fusion Security* for more details.

## AES for Flash Memory

AES decryption can also be used on the flash memory blocks. This provides the best available security during update of the flash memory blocks. During runtime, the encrypted data can be clocked in via the JTAG interface. The data can be passed through the internal AES decryption engine, and the decrypted data can then be stored in the flash memory block.

## **Programming**

Programming can be performed using various programming tools, such as Silicon Sculptor II (BP Micro Systems) or FlashPro3 (Microsemi).

The user can generate STP programming files from the Designer software and can use these files to program a device.

Fusion devices can be programmed in-system. During programming, VCCOSC is needed in order to power the internal 100 MHz oscillator. This oscillator is used as a source for the 20 MHz oscillator that is used to drive the charge pump for programming.

Table 3-12 • Summary of I/O Input Buffer Power (per pin)—Default I/O Software Settings (continued)

|                                  | VCCI (V) | Static Power<br>PDC7 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (μW/MHz) <sup>2</sup> |

|----------------------------------|----------|----------------------------------------|---------------------------------------------|

| Applicable to Advanced I/O Banks | <u>'</u> |                                        | •                                           |

| Single-Ended                     |          |                                        |                                             |

| 3.3 V LVTTL/LVCMOS               | 3.3      | _                                      | 16.69                                       |

| 2.5 V LVCMOS                     | 2.5      | _                                      | 5.12                                        |

| 1.8 V LVCMOS                     | 1.8      | _                                      | 2.13                                        |

| 1.5 V LVCMOS (JESD8-11)          | 1.5      | _                                      | 1.45                                        |

| 3.3 V PCI                        | 3.3      | _                                      | 18.11                                       |

| 3.3 V PCI-X                      | 3.3      | _                                      | 18.11                                       |

| Differential                     |          |                                        |                                             |

| LVDS                             | 2.5      | 2.26                                   | 1.20                                        |

| LVPECL                           | 3.3      | 5.72                                   | 1.87                                        |

| Applicable to Standard I/O Banks | <u> </u> |                                        |                                             |

| 3.3 V LVTTL/LVCMOS               | 3.3      | _                                      | 16.79                                       |

| 2.5 V LVCMOS                     | 2.5      | _                                      | 5.19                                        |

| 1.8 V LVCMOS                     | 1.8      | _                                      | 2.18                                        |

| 1.5 V LVCMOS (JESD8-11)          | 1.5      | _                                      | 1.52                                        |

## Notes:

- 1. PDC7 is the static power (where applicable) measured on VCCI.

- 2. PAC9 is the total dynamic power measured on VCC and VCCI.

3-19 Revision 6

$$P_{S-CELL} = N_{S-CELL} * (PAC5 + (\alpha_1 / 2) * PAC6) * F_{CLK}$$

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 3-16 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

## Standby Mode and Sleep Mode

P<sub>S-CELL</sub> = 0 W

## Combinatorial Cells Dynamic Contribution—P<sub>C-CELL</sub>

## **Operating Mode**

$P_{C-CELL} = N_{C-CELL} * (\alpha_1 / 2) * PAC7 * F_{CLK}$

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 3-16 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

## Standby Mode and Sleep Mode

P<sub>C-CELL</sub> = 0 W

Routing Net Dynamic Contribution—P<sub>NET</sub>

#### **Operating Mode**

$P_{NET} = (N_{S-CELL} + N_{C-CELL}) * (\alpha_1 / 2) * PAC8 * F_{CLK}$

N<sub>S-CELL</sub> is the number VersaTiles used as sequential modules in the design.

N<sub>C-CFLL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 3-16 on page 3-27.

F<sub>Cl K</sub> is the global clock signal frequency.

### Standby Mode and Sleep Mode

$P_{NET} = 0 W$

### I/O Input Buffer Dynamic Contribution—PINPUTS

## **Operating Mode**

$P_{INPUTS} = N_{INPUTS} * (\alpha_2 / 2) * PAC9 * F_{CLK}$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 3-16 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

## Standby Mode and Sleep Mode

P<sub>INPUTS</sub> = 0 W

## I/O Output Buffer Dynamic Contribution—POUTPUTS

#### Operating Mode

$P_{OUTPUTS} = N_{OUTPUTS} * (\alpha_2 / 2) * \beta_1 * PAC10 * F_{CLK}$

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 3-16 on page 3-27.

$eta_{\text{1}}$  is the I/O buffer enable rate—guidelines are provided in Table 3-17 on page 3-27.

F<sub>CLK</sub> is the global clock signal frequency.

## Standby Mode and Sleep Mode

P<sub>OUTPUTS</sub> = 0 W

3-25 Revision 6

## Package Pin Assignments

| QN180      |                 |                 |  |  |

|------------|-----------------|-----------------|--|--|

| Pin Number | AFS090 Function | AFS250 Function |  |  |

| C21        | AG2             | AG2             |  |  |

| C22        | NC              | NC              |  |  |

| C23        | NC              | NC              |  |  |

| C24        | NC              | NC              |  |  |

| C25        | NC              | AT5             |  |  |

| C26        | GNDAQ           | GNDAQ           |  |  |

| C27        | NC              | NC              |  |  |

| C28        | NC              | NC              |  |  |

| C29        | NC              | NC              |  |  |

| C30        | NC              | NC              |  |  |

| C31        | GND             | GND             |  |  |

| C32        | NC              | NC              |  |  |

| C33        | NC              | NC              |  |  |

| C34        | NC              | NC              |  |  |

| C35        | GND             | GND             |  |  |

| C36        | GDB0/IO39NPB1V0 | GDA0/IO54NPB1V0 |  |  |

| C37        | GDA1/IO37NSB1V0 | GDC0/IO52NSB1V0 |  |  |

| C38        | GCA0/IO36NDB1V0 | GCA0/IO49NDB1V0 |  |  |

| C39        | GCB1/IO35PPB1V0 | GCB1/IO48PPB1V0 |  |  |

| C40        | GND             | GND             |  |  |

| C41        | GCA2/IO32NPB1V0 | IO41NPB1V0      |  |  |

| C42        | GBB2/IO31NDB1V0 | IO40NDB1V0      |  |  |

| C43        | NC              | NC              |  |  |

| C44        | NC              | GBA1/IO39RSB0V0 |  |  |

| C45        | NC              | GBB0/IO36RSB0V0 |  |  |

| C46        | GND             | GND             |  |  |

| C47        | NC              | IO30RSB0V0      |  |  |

| C48        | IO22RSB0V0      | IO27RSB0V0      |  |  |

| C49        | GND             | GND             |  |  |

| C50        | IO13RSB0V0      | IO16RSB0V0      |  |  |

| C51        | IO09RSB0V0      | IO12RSB0V0      |  |  |

| C52        | IO06RSB0V0      | IO09RSB0V0      |  |  |

| C53        | GND             | GND             |  |  |

| C54        | NC              | GAB1/IO03RSB0V0 |  |  |

| C55        | NC              | GAA0/IO00RSB0V0 |  |  |

| C56        | NC              | NC              |  |  |

| QN180      |                 |                 |  |  |

|------------|-----------------|-----------------|--|--|

| Pin Number | AFS090 Function | AFS250 Function |  |  |

| D1         | NC              | NC              |  |  |

| D2         | NC              | NC              |  |  |

| D3         | NC              | NC              |  |  |

| D4         | NC              | NC              |  |  |

4-6 Revision 6

|            |                 | FG256           |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| A1         | GND             | GND             | GND             | GND              |

| A2         | VCCIB0          | VCCIB0          | VCCIB0          | VCCIB0           |

| A3         | GAB0/IO02RSB0V0 | GAA0/IO00RSB0V0 | GAA0/IO01NDB0V0 | GAA0/IO01NDB0V0  |

| A4         | GAB1/IO03RSB0V0 | GAA1/IO01RSB0V0 | GAA1/IO01PDB0V0 | GAA1/IO01PDB0V0  |

| A5         | GND             | GND             | GND             | GND              |

| A6         | IO07RSB0V0      | IO11RSB0V0      | IO10PDB0V1      | IO07PDB0V1       |

| A7         | IO10RSB0V0      | IO14RSB0V0      | IO12PDB0V1      | IO13PDB0V2       |

| A8         | IO11RSB0V0      | IO15RSB0V0      | IO12NDB0V1      | IO13NDB0V2       |

| A9         | IO16RSB0V0      | IO24RSB0V0      | IO22NDB1V0      | IO24NDB1V0       |

| A10        | IO17RSB0V0      | IO25RSB0V0      | IO22PDB1V0      | IO24PDB1V0       |

| A11        | IO18RSB0V0      | IO26RSB0V0      | IO24NDB1V1      | IO29NDB1V1       |

| A12        | GND             | GND             | GND             | GND              |

| A13        | GBC0/IO25RSB0V0 | GBA0/IO38RSB0V0 | GBA0/IO28NDB1V1 | GBA0/IO42NDB1V2  |

| A14        | GBA0/IO29RSB0V0 | IO32RSB0V0      | IO29NDB1V1      | IO43NDB1V2       |

| A15        | VCCIB0          | VCCIB0          | VCCIB1          | VCCIB1           |

| A16        | GND             | GND             | GND             | GND              |

| B1         | VCOMPLA         | VCOMPLA         | VCOMPLA         | VCOMPLA          |

| B2         | VCCPLA          | VCCPLA          | VCCPLA          | VCCPLA           |

| В3         | GAA0/IO00RSB0V0 | IO07RSB0V0      | IO00NDB0V0      | IO00NDB0V0       |

| B4         | GAA1/IO01RSB0V0 | IO06RSB0V0      | IO00PDB0V0      | IO00PDB0V0       |

| B5         | NC              | GAB1/IO03RSB0V0 | GAB1/IO02PPB0V0 | GAB1/IO02PPB0V0  |

| В6         | IO06RSB0V0      | IO10RSB0V0      | IO10NDB0V1      | IO07NDB0V1       |

| B7         | VCCIB0          | VCCIB0          | VCCIB0          | VCCIB0           |

| B8         | IO12RSB0V0      | IO16RSB0V0      | IO18NDB1V0      | IO22NDB1V0       |

| B9         | IO13RSB0V0      | IO17RSB0V0      | IO18PDB1V0      | IO22PDB1V0       |

| B10        | VCCIB0          | VCCIB0          | VCCIB1          | VCCIB1           |

| B11        | IO19RSB0V0      | IO27RSB0V0      | IO24PDB1V1      | IO29PDB1V1       |

| B12        | GBB0/IO27RSB0V0 | GBC0/IO34RSB0V0 | GBC0/IO26NPB1V1 | GBC0/IO40NPB1V2  |

| B13        | GBC1/IO26RSB0V0 | GBA1/IO39RSB0V0 | GBA1/IO28PDB1V1 | GBA1/IO42PDB1V2  |

| B14        | GBA1/IO30RSB0V0 | IO33RSB0V0      | IO29PDB1V1      | IO43PDB1V2       |

| B15        | NC              | NC              | VCCPLB          | VCCPLB           |

| B16        | NC              | NC              | VCOMPLB         | VCOMPLB          |

| C1         | VCCIB3          | V <b>CCI</b> B3 | VCCIB4          | VCCIB4           |

| C2         | GND             | GND             | GND             | GND              |

| C3         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| C4         | NC              | NC              | VCCIB0          | VCCIB0           |

| C5         | VCCIB0          | VCCIB0          | VCCIB0          | VCCIB0           |

| L.         |                 |                 |                 |                  |

Fusion Family of Mixed Signal FPGAs

|               | FG484           |                  |  |  |  |

|---------------|-----------------|------------------|--|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |  |

| P21           | IO51PDB2V0      | IO73PDB2V0       |  |  |  |

| P22           | IO49NDB2V0      | IO71NDB2V0       |  |  |  |

| R1            | IO69PDB4V0      | IO102PDB4V0      |  |  |  |

| R2            | IO69NDB4V0      | IO102NDB4V0      |  |  |  |

| R3            | VCCIB4          | VCCIB4           |  |  |  |

| R4            | IO64PDB4V0      | IO91PDB4V0       |  |  |  |

| R5            | IO64NDB4V0      | IO91NDB4V0       |  |  |  |

| R6            | NC              | IO92PDB4V0       |  |  |  |

| R7            | GND             | GND              |  |  |  |

| R8            | GND             | GND              |  |  |  |

| R9            | VCC33A          | VCC33A           |  |  |  |

| R10           | GNDA            | GNDA             |  |  |  |

| R11           | VCC33A          | VCC33A           |  |  |  |

| R12           | GNDA            | GNDA             |  |  |  |

| R13           | VCC33A          | VCC33A           |  |  |  |

| R14           | GNDA            | GNDA             |  |  |  |

| R15           | VCC             | VCC              |  |  |  |

| R16           | GND             | GND              |  |  |  |

| R17           | NC              | IO74NDB2V0       |  |  |  |

| R18           | GDA0/IO54NDB2V0 | GDA0/IO81NDB2V0  |  |  |  |

| R19           | GDB0/IO53NDB2V0 | GDB0/IO80NDB2V0  |  |  |  |

| R20           | VCCIB2          | VCCIB2           |  |  |  |

| R21           | IO50NDB2V0      | IO75NDB2V0       |  |  |  |

| R22           | IO50PDB2V0      | IO75PDB2V0       |  |  |  |

| T1            | NC              | IO100PPB4V0      |  |  |  |

| T2            | GND             | GND              |  |  |  |

| Т3            | IO66PDB4V0      | IO95PDB4V0       |  |  |  |

| T4            | IO66NDB4V0      | IO95NDB4V0       |  |  |  |

| T5            | VCCIB4          | VCCIB4           |  |  |  |

| T6            | NC              | IO92NDB4V0       |  |  |  |

| T7            | GNDNVM          | GNDNVM           |  |  |  |

| T8            | GNDA            | GNDA             |  |  |  |

| Т9            | NC              | NC               |  |  |  |

| T10           | AV4             | AV4              |  |  |  |

| T11           | NC              | NC               |  |  |  |

|               | FG484           |                  |  |  |  |

|---------------|-----------------|------------------|--|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |  |

| T12           | AV5             | AV5              |  |  |  |

| T13           | AC5             | AC5              |  |  |  |

| T14           | NC              | NC               |  |  |  |

| T15           | GNDA            | GNDA             |  |  |  |

| T16           | NC              | IO77PPB2V0       |  |  |  |

| T17           | NC              | IO74PDB2V0       |  |  |  |

| T18           | VCCIB2          | VCCIB2           |  |  |  |

| T19           | IO55NDB2V0      | IO82NDB2V0       |  |  |  |

| T20           | GDA2/IO55PDB2V0 | GDA2/IO82PDB2V0  |  |  |  |

| T21           | GND             | GND              |  |  |  |

| T22           | GDC1/IO52PDB2V0 | GDC1/IO79PDB2V0  |  |  |  |

| U1            | IO67PDB4V0      | IO98PDB4V0       |  |  |  |

| U2            | IO67NDB4V0      | IO98NDB4V0       |  |  |  |

| U3            | GEC1/IO63PDB4V0 | GEC1/IO90PDB4V0  |  |  |  |

| U4            | GEC0/IO63NDB4V0 | GEC0/IO90NDB4V0  |  |  |  |

| U5            | GND             | GND              |  |  |  |

| U6            | VCCNVM          | VCCNVM           |  |  |  |

| U7            | VCCIB4          | VCCIB4           |  |  |  |

| U8            | VCC15A          | VCC15A           |  |  |  |

| U9            | GNDA            | GNDA             |  |  |  |

| U10           | AC4             | AC4              |  |  |  |

| U11           | VCC33A          | VCC33A           |  |  |  |

| U12           | GNDA            | GNDA             |  |  |  |

| U13           | AG5             | AG5              |  |  |  |

| U14           | GNDA            | GNDA             |  |  |  |

| U15           | PUB             | PUB              |  |  |  |

| U16           | VCCIB2          | VCCIB2           |  |  |  |

| U17           | TDI             | TDI              |  |  |  |

| U18           | GND             | GND              |  |  |  |

| U19           | IO57NDB2V0      | IO84NDB2V0       |  |  |  |

| U20           | GDC2/IO57PDB2V0 | GDC2/IO84PDB2V0  |  |  |  |

| U21           | NC              | IO77NPB2V0       |  |  |  |

| U22           | GDC0/IO52NDB2V0 | GDC0/IO79NDB2V0  |  |  |  |

| V1            | GEB1/IO62PDB4V0 | GEB1/IO89PDB4V0  |  |  |  |

| V2            | GEB0/IO62NDB4V0 | GEB0/IO89NDB4V0  |  |  |  |

| FG484         |                 |                  |  |  |

|---------------|-----------------|------------------|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |

| V3            | VCCIB4          | VCCIB4           |  |  |

| V4            | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  |  |  |

| V5            | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  |  |  |

| V6            | GND             | GND              |  |  |

| V7            | VCC33PMP        | VCC33PMP         |  |  |

| V8            | NC              | NC               |  |  |

| V9            | VCC33A          | VCC33A           |  |  |

| V10           | AG4             | AG4              |  |  |

| V11           | AT4             | AT4              |  |  |

| V12           | ATRTN2          | ATRTN2           |  |  |

| V13           | AT5             | AT5              |  |  |

| V14           | VCC33A          | VCC33A           |  |  |

| V15           | NC              | NC               |  |  |

| V16           | VCC33A          | VCC33A           |  |  |

| V17           | GND             | GND              |  |  |

| V18           | TMS             | TMS              |  |  |

| V19           | VJTAG           | VJTAG            |  |  |

| V20           | VCCIB2          | VCCIB2           |  |  |

| V21           | TRST            | TRST             |  |  |

| V22           | TDO             | TDO              |  |  |

| W1            | NC              | IO93PDB4V0       |  |  |

| W2            | GND             | GND              |  |  |

| W3            | NC              | IO93NDB4V0       |  |  |

| W4            | GEB2/IO59PDB4V0 | GEB2/IO86PDB4V0  |  |  |

| W5            | IO59NDB4V0      | IO86NDB4V0       |  |  |

| W6            | AV0             | AV0              |  |  |

| W7            | GNDA            | GNDA             |  |  |

| W8            | AV1             | AV1              |  |  |

| W9            | AV2             | AV2              |  |  |

| W10           | GNDA            | GNDA             |  |  |

| W11           | AV3             | AV3              |  |  |

| W12           | AV6             | AV6              |  |  |

| W13           | GNDA            | GNDA             |  |  |

| W14           | AV7             | AV7              |  |  |

| W15           | AV8             | AV8              |  |  |

| FG484         |                 |                  |

|---------------|-----------------|------------------|

| Pin<br>Number | AFS600 Function | AFS1500 Function |

| W16           | GNDA            | GNDA             |

| W17           | AV9             | AV9              |

| W18           | VCCIB2          | VCCIB2           |

| W19           | NC              | IO68PPB2V0       |

| W20           | TCK             | TCK              |

| W21           | GND             | GND              |

| W22           | NC              | IO76PPB2V0       |

| Y1            | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |

| Y2            | IO60NDB4V0      | IO87NDB4V0       |

| Y3            | GEA2/IO58PDB4V0 | GEA2/IO85PDB4V0  |

| Y4            | IO58NDB4V0      | IO85NDB4V0       |

| Y5            | NCAP            | NCAP             |

| Y6            | AC0             | AC0              |

| Y7            | VCC33A          | VCC33A           |

| Y8            | AC1             | AC1              |

| Y9            | AC2             | AC2              |

| Y10           | VCC33A          | VCC33A           |

| Y11           | AC3             | AC3              |

| Y12           | AC6             | AC6              |

| Y13           | VCC33A          | VCC33A           |

| Y14           | AC7             | AC7              |

| Y15           | AC8             | AC8              |

| Y16           | VCC33A          | VCC33A           |

| Y17           | AC9             | AC9              |

| Y18           | ADCGNDREF       | ADCGNDREF        |

| Y19           | PTBASE          | PTBASE           |

| Y20           | GNDNVM          | GNDNVM           |

| Y21           | VCCNVM          | VCCNVM           |

| Y22           | VPUMP           | VPUMP            |

4-26 Revision 6