Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                  |

|--------------------------------|------------------------------------------------------------------|

| Product Status                 | Obsolete                                                         |

| Number of LABs/CLBs            | -                                                                |

| Number of Logic Elements/Cells | -                                                                |

| Total RAM Bits                 | 36864                                                            |

| Number of I/O                  | 65                                                               |

| Number of Gates                | 250000                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                                  |

| Mounting Type                  | Surface Mount                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                               |

| Package / Case                 | 180-WFQFN Dual Rows, Exposed Pad                                 |

| Supplier Device Package        | 180-QFN (10x10)                                                  |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs250-1qng180i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

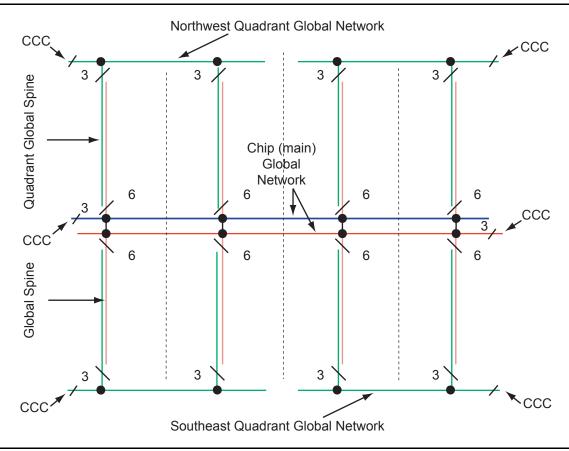

Figure 2-12 • Global Network Architecture

Table 2-4 • Globals/Spines/Rows by Device

|                                        | AFS090 | AFS250 | AFS600 | AFS1500 |

|----------------------------------------|--------|--------|--------|---------|

| Global VersaNets (trees)*              | 9      | 9      | 9      | 9       |

| VersaNet Spines/Tree                   | 4      | 8      | 12     | 20      |

| Total Spines                           | 36     | 72     | 108    | 180     |

| VersaTiles in Each Top or Bottom Spine | 384    | 768    | 1,152  | 1,920   |

| Total VersaTiles                       | 2,304  | 6,144  | 13,824 | 38,400  |

Note: \*There are six chip (main) globals and three globals per quadrant.

# **Clock Aggregation**

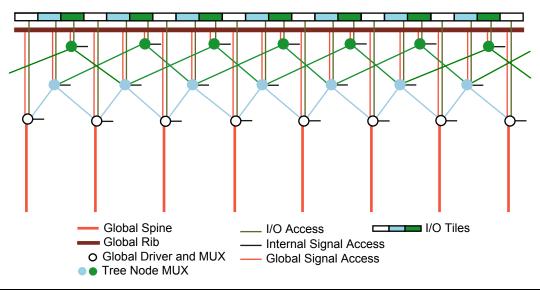

Clock aggregation allows for multi-spine clock domains. A MUX tree provides the necessary flexibility to allow long lines or I/Os to access domains of one, two, or four global spines. Signal access to the clock aggregation system is achieved through long-line resources in the central rib, and also through local resources in the north and south ribs, allowing I/Os to feed directly into the clock system. As Figure 2-14 indicates, this access system is contiguous.

There is no break in the middle of the chip for north and south I/O VersaNet access. This is different from the quadrant clocks, located in these ribs, which only reach the middle of the rib. Refer to the *Using Global Resources in Actel Fusion Devices* application note.

Figure 2-14 • Clock Aggregation Tree Architecture

Table 2-7 • AFS250 Global Resource Timing

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                               | -2   |                   | -1                |                   | Std.              |                   | Units  |

|----------------------|-------------------------------------------|------|-------------------|-------------------|-------------------|-------------------|-------------------|--------|

| Parameter            | Description                               |      | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Ullits |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.89 | 1.12              | 1.02              | 1.27              | 1.20              | 1.50              | ns     |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.88 | 1.14              | 1.00              | 1.30              | 1.17              | 1.53              | ns     |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |      |                   |                   |                   |                   |                   | ns     |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |      |                   |                   |                   |                   |                   | ns     |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |      | 0.26              |                   | 0.30              |                   | 0.35              | ns     |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-8 • AFS090 Global Resource Timing

Commercial Temperature Range Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V

| Davameter            | Decemention                               | -    | 2                 | _                 | 1                 | S                 | Units             |       |

|----------------------|-------------------------------------------|------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

| Parameter            | Description                               |      | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.84 | 1.07              | 0.96              | 1.21              | 1.13              | 1.43              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.83 | 1.10              | 0.95              | 1.25              | 1.12              | 1.47              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |      |                   |                   |                   |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |      |                   |                   |                   |                   |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |      | 0.27              |                   | 0.30              |                   | 0.36              | ns    |

### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-17 Revision 6

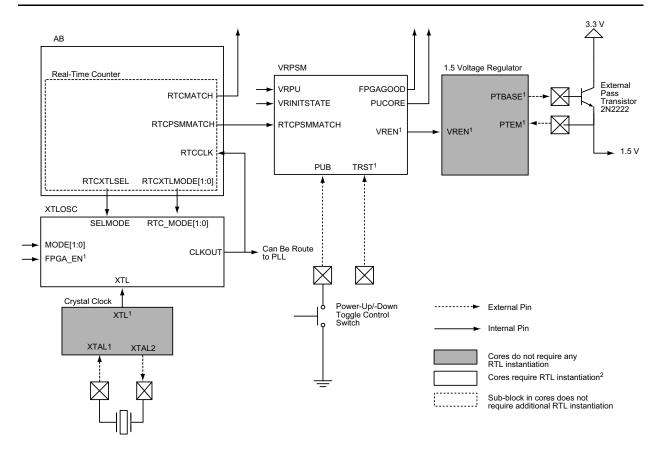

# **Real-Time Counter System**

The RTC system enables Fusion devices to support standby and sleep modes of operation to reduce power consumption in many applications.

- Sleep mode, typical 10 μA

- Standby mode (RTC running), typical 3 mA with 20 MHz

The RTC system is composed of five cores:

- RTC sub-block inside Analog Block (AB)

- Voltage Regulator and Power System Monitor (VRPSM)

- Crystal oscillator (XTLOSC); refer to the "Crystal Oscillator" section in the Fusion Clock Resources chapter of the Fusion FPGA Fabric User Guide for more detail.

- · Crystal clock; does not require instantiation in RTL

- · 1.5 V voltage regulator; does not require instantiation in RTL

All cores are powered by 3.3 V supplies, so the RTC system is operational without a 1.5 V supply during standby mode. Figure 2-27 shows their connection.

### Notes:

- 1. Signals are hardwired internally and do not exist in the macro core.

- 2. User is only required to instantiate the VRPSM macro if the user wishes to specify PUPO behavior of the voltage regulator to be different from the default, or employ user logic to shut the voltage regulator off.

Figure 2-27 • Real-Time Counter System (not all the signals are shown for the AB macro)

2-31 Revision 6

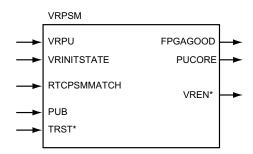

# **Voltage Regulator and Power System Monitor (VRPSM)**

The VRPSM macro controls the power-up state of the FPGA. The power-up bar (PUB) pin can turn on the voltage regulator when set to 0. TRST can enable the voltage regulator when deasserted, allowing the FPGA to power-up when user want access to JTAG ports. The inputs VRINITSTATE and RTCPSMMATCH come from the flash bits and RTC, and can also power up the FPGA.

Note: \*Signals are hardwired internally and do not exist in the macro core.

Figure 2-30 • VRPSM Macro

Table 2-17 • VRPSM Signal Descriptions

| Signal Name      | Width   | Direction    | Function                                                                                                                                   |

|------------------|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| VRPU             | 1       | In           | Voltage Regulator Power-Up                                                                                                                 |

|                  |         |              | 0 – Voltage regulator disabled. PUB must be floated or pulled up, and the TRST<br>pin must be grounded to disable the voltage regulator.   |

|                  |         |              | 1 – Voltage regulator enabled                                                                                                              |

| VRINITSTATE      | 1       | In           | Voltage Regulator Initial State                                                                                                            |

|                  |         |              | Defines the voltage Regulator status upon power-up of the 3.3 V. The signal is configured by Libero SoC when the VRPSM macro is generated. |

|                  |         |              | Tie off to 1 – Voltage regulator enables when 3.3 V is powered.                                                                            |

|                  |         |              | Tie off to 0 – Voltage regulator disables when 3.3 V is powered.                                                                           |

| RTCPSMMATCH      | 1       | In           | RTC Power System Management Match                                                                                                          |

|                  |         |              | Connect from RTCPSMATCH signal from RTC in AB                                                                                              |

|                  |         |              | 0 transition to 1 turns on the voltage regulator                                                                                           |

| PUB              | 1       | In           | External pin, built-in weak pull-up                                                                                                        |

|                  |         |              | Power-Up Bar                                                                                                                               |

|                  |         |              | 0 – Enables voltage regulator at all times                                                                                                 |

| TRST*            | 1       | In           | External pin, JTAG Test Reset                                                                                                              |

|                  |         |              | 1 – Enables voltage regulator at all times                                                                                                 |

| FPGAGOOD         | 1       | Out          | Indicator that the FPGA is powered and functional                                                                                          |

|                  |         |              | No need to connect if it is not used.                                                                                                      |

|                  |         |              | 1 – Indicates that the FPGA is powered up and functional.                                                                                  |

|                  |         |              | 0 – Not possible to read by FPGA since it has already powered off.                                                                         |

| PUCORE           | 1       | Out          | Power-Up Core                                                                                                                              |

|                  |         |              | Inverted signal of PUB. No need to connect if it is not used.                                                                              |

| VREN*            | 1       | Out          | Voltage Regulator Enable                                                                                                                   |

|                  |         |              | Connected to 1.5 V voltage regulator in Fusion device internally.                                                                          |

|                  |         |              | 0 – Voltage regulator disables                                                                                                             |

|                  |         |              | 1 – Voltage regulator enables                                                                                                              |

| Note: *Signals a | re hard | wired intern | ally and do not exist in the macro core.                                                                                                   |

# 1.5 V Voltage Regulator

The  $1.5\,\text{V}$  voltage regulator uses an external pass transistor to generate  $1.5\,\text{V}$  from a  $3.3\,\text{V}$  supply. The base of the pass transistor is tied to PTBASE, the collector is tied to  $3.3\,\text{V}$ , and an emitter is tied to PTBASE and the  $1.5\,\text{V}$  supplies of the Fusion device. Figure 2-27 on page 2-31 shows the hook-up of the  $1.5\,\text{V}$  voltage regulator to an external pass transistor.

Microsemi recommends using a PN2222A or 2N2222A transistor. The gain of such a transistor is approximately 25, with a maximum base current of 20 mA. The maximum current that can be supported is 0.5 A. Transistors with different gain can also be used for different current requirements.

Table 2-18 • Electrical Characteristics VCC33A = 3.3 V

| Symbol  | Parameter         | Condition |                           | Min   | Typical | Max   | Units |

|---------|-------------------|-----------|---------------------------|-------|---------|-------|-------|

| VOUT    | Output Voltage    | Tj = 25°C |                           | 1.425 | 1.5     | 1.575 | V     |

| ICC33A  | Operation Current | Tj = 25°C | ILOAD = 1 mA              |       | 11      |       | mA    |

|         |                   |           | ILOAD = 100 mA            |       | 11      |       | mA    |

|         |                   |           | ILOAD = 0.5 A             |       | 30      |       | mA    |

| ΔVOUT   | Load Regulation   | Tj = 25°C | ILOAD = 1 mA to 0.5 A     |       | 90      |       | mV    |

|         | Line Regulation   | Tj = 25°C | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 1 mA              |       | 10.6    |       | mV/V  |

|         |                   |           | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 100 mA            |       | 12.1    |       | mV/V  |

| ΔVOUT   |                   |           | VCC33A = 2.97 V to 3.63 V |       | 40.0    |       |       |

|         |                   |           | ILOAD = 500 mA            |       | 10.6    |       | mV/V  |

|         | Dropout Voltage*  | Tj = 25°C | ILOAD = 1 mA              |       | 0.63    |       | V     |

|         |                   |           | ILOAD = 100 mA            |       | 0.84    |       | V     |

|         |                   |           | ILOAD = 0.5 A             |       | 1.35    |       | V     |

| IPTBASE | PTBase Current    | Tj = 25°C | ILOAD = 1 mA              |       | 48      |       | μΑ    |

|         |                   |           | ILOAD = 100 mA            |       | 736     |       | μA    |

|         |                   |           | ILOAD = 0.5 A             |       | 12      | 20    | mA    |

Note: \*Data collected with 2N2222A.

RAM512X18 exhibits slightly different behavior from RAM4K9, as it has dedicated read and write ports.

#### WW and RW

These signals enable the RAM to be configured in one of the two allowable aspect ratios (Table 2-30).

Table 2-30 • Aspect Ratio Settings for WW[1:0]

| WW[1:0] | RW[1:0] | D×W      |

|---------|---------|----------|

| 01      | 01      | 512×9    |

| 10      | 10      | 256×18   |

| 00, 11  | 00, 11  | Reserved |

### WD and RD

These are the input and output data signals, and they are 18 bits wide. When a 512×9 aspect ratio is used for write, WD[17:9] are unused and must be grounded. If this aspect ratio is used for read, then RD[17:9] are undefined.

### WADDR and RADDR

These are read and write addresses, and they are nine bits wide. When the 256×18 aspect ratio is used for write or read, WADDR[8] or RADDR[8] are unused and must be grounded.

#### WCLK and RCLK

These signals are the write and read clocks, respectively. They are both active high.

#### WEN and REN

These signals are the write and read enables, respectively. They are both active low by default. These signals can be configured as active high.

#### RESET

This active low signal resets the output to zero, disables reads and/or writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory.

### **PIPE**

This signal is used to specify pipelined read on the output. A Low on PIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A High indicates a pipelined read, and data appears on the output in the next clock cycle.

### Clocking

The dual-port SRAM blocks are only clocked on the rising edge. SmartGen allows falling-edge-triggered clocks by adding inverters to the netlist, hence achieving dual-port SRAM blocks that are clocked on either edge (rising or falling). For dual-port SRAM, each port can be clocked on either edge or by separate clocks, by port.

Fusion devices support inversion (bubble pushing) throughout the FPGA architecture, including the clock input to the SRAM modules. Inversions added to the SRAM clock pin on the design schematic or in the HDL code will be automatically accounted for during design compile without incurring additional delay in the clock path.

The two-port SRAM can be clocked on the rising edge or falling edge of WCLK and RCLK.

If negative-edge RAM and FIFO clocking is selected for memory macros, clock edge inversion management (bubble pushing) is automatically used within the Fusion development tools, without performance penalty.

2-61 Revision 6

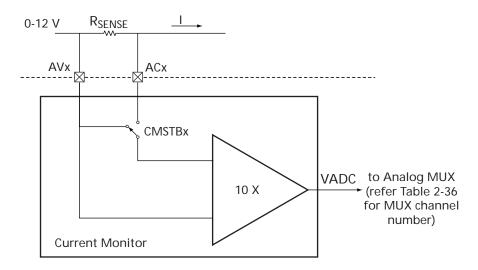

Figure 2-72 • Positive Current Monitor

Care must be taken when choosing the right resistor for current measurement application. Note that because of the  $10\times$  amplification, the maximum measurable difference between the AV and AC pads is  $V_{AREF}$  / 10. A larger AV-to-AC voltage drop will result in ADC saturation; that is, the digital code put out by the ADC will stay fixed at the full scale value. Therefore, the user must select the external sense resistor appropriately. Table 2-38 shows recommended resistor values for different current measurement ranges. When choosing resistor values for a system, there is a trade-off between measurement accuracy and power consumption. Choosing a large resistor will increase the voltage drop and hence increase accuracy of the measurement; however the larger voltage drop dissipates more power (P =  $1^2 \times R$ ).

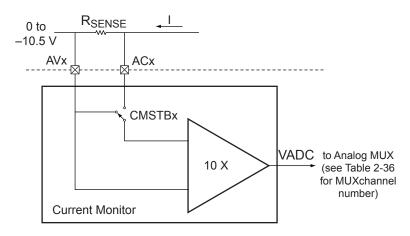

The Current Monitor is a unipolar system, meaning that the differential voltage swing must be from 0 V to  $V_{AREF}/10$ . Therefore, the Current Monitor only supports differential voltage where  $|V_{AV}-V_{AC}|$  is greater than 0 V. This results in the requirement that the potential of the AV pad must be larger than the potential of the AC pad. This is straightforward for positive voltage systems. For a negative voltage system, it means that the AV pad must be "more negative" than the AC pad. This is shown in Figure 2-73.

In this case, both the AV pad and the AC pad are configured for negative operations and the output of the differential amplifier still falls between 0 V and  $V_{AREF}$  as required.

Table 2-37 • Recommended Resistor for Different Current Range Measurement

| Current Range     | Recommended Minimum Resistor Value (Ohms) |

|-------------------|-------------------------------------------|

| > 5 mA – 10 mA    | 10 – 20                                   |

| > 10 mA – 20 mA   | 5 – 10                                    |

| > 20 mA – 50 mA   | 2.5 – 5                                   |

| > 50 mA – 100 mA  | 1 – 2                                     |

| > 100 mA – 200 mA | 0.5 – 1                                   |

| > 200 mA – 500 mA | 0.3 – 0.5                                 |

| > 500 mA – 1 A    | 0.1 – 0.2                                 |

| > 1 A – 2 A       | 0.05 – 0.1                                |

| > 2 A – 4 A       | 0.025 – 0.05                              |

| > 4 A – 8 A       | 0.0125 – 0.025                            |

| > 8 A – 12 A      | 0.00625 – 0.02                            |

Figure 2-73 • Negative Current Monitor

### **Terminology**

### Accuracy

The accuracy of Fusion Current Monitor is  $\pm 2$  mV minimum plus 5% of the differential voltage at the input. The input accuracy can be translated to error at the ADC output by using EQ 4. The 10 V/V gain is the gain of the Current Monitor Circuit, as described in the "Current Monitor" section on page 2-86. For 8-bit mode, N = 8,  $V_{AREF} = 2.56$  V, zero differential voltage between AV and AC, the Error ( $E_{ADC}$ ) is equal to 2 LSBs.

$$E_{ADC} = (2mV + 0.05 |V_{AV} - V_{AC}|) \times (10V) / V \times \frac{2^{N}}{V_{AREF}}$$

EQ4

where

N is the number of bits

$V_{AREF}$  is the Reference voltage

$V_{AV}$  is the voltage at AV pad

$V_{AC}$  is the voltage at AC pad

2-89 Revision 6

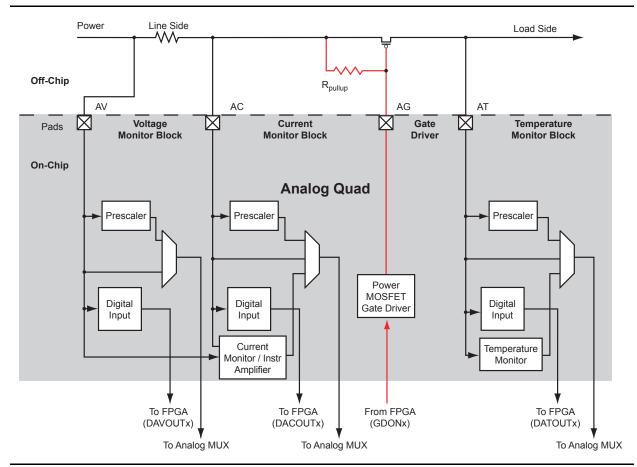

### Gate Driver

The Fusion Analog Quad includes a Gate Driver connected to the Quad's AG pin (Figure 2-74). Designed to work with external p- or n-channel MOSFETs, the Gate driver is a configurable current sink or source and requires an external pull-up or pull-down resistor. The AG supports 4 selectable gate drive levels: 1  $\mu$ A, 3  $\mu$ A, 10  $\mu$ A, and 30  $\mu$ A (Figure 2-75 on page 2-91). The AG also supports a High Current Drive mode in which it can sink 20 mA; in this mode the switching rate is approximately 1.3 MHz with 100 ns turn-on time and 600 ns turn-off time. Modeled on an open-drain-style output, it does not output a voltage level without an appropriate pull-up or pull-down resistor. If 1 V is forced on the drain, the current sinking/sourcing will exceed the ability of the transistor, and the device could be damaged.

The AG pad is turned on via the corresponding GDONx pin in the Analog Block macro, where x is the number of the corresponding Analog Quad for the AG pad to be enabled (GDON0 to GDON9).

Figure 2-74 • Gate Driver

The gate-to-source voltage ( $V_{gs}$ ) of the external MOSFET is limited to the programmable drive current times the external pull-up or pull-down resistor value (EQ 5).

$$V_{as} \le I_a \times (R_{pullup} \text{ or } R_{pulldown})$$

EQ 5

# **Hot-Swap Support**

Hot-swapping (also called hot plugging) is the operation of hot insertion or hot removal of a card in (or from) a powered-up system. The levels of hot-swap support and examples of related applications are described in Table 2-74. The I/Os also need to be configured in hot insertion mode if hot plugging compliance is required.

Table 2-74 • Levels of Hot-Swap Support

| Hot<br>Swapping<br>Level | Description                     | Power<br>Applied<br>to Device | Bus State                                                                                                                   | Card<br>Ground<br>Connection                                                                        | Device<br>Circuitry<br>Connected<br>to Bus Pins    |                                                                                                                                                                                                      | Compliance of Fusion Devices                                        |

|--------------------------|---------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 1                        | Cold-swap                       | No                            | -                                                                                                                           | _                                                                                                   | _                                                  | System and card with Microsemi FPGA chip are powered down, then card gets plugged into system, then power supplies are turned on for system but not for FPGA on card.                                |                                                                     |

| 2                        | Hot-swap<br>while reset         | Yes                           | Held in<br>reset state                                                                                                      | Must be made<br>and<br>maintained for<br>1 ms before,<br>during, and<br>after insertion/<br>removal | _                                                  | In PCI hot plug specification, reset control circuitry isolates the card busses until the card supplies are at their nominal operating levels and stable.                                            | Compliant I/Os can but do not have to be set to hot insertion mode. |

| 3                        | Hot-swap<br>while bus<br>idle   | Yes                           | Held idle<br>(no ongoing<br>I/O<br>processes<br>during<br>insertion/re<br>moval)                                            | Same as<br>Level 2                                                                                  | glitch-free<br>during<br>power-up or<br>power-down | Board bus shared with card bus is "frozen," and there is no toggling activity on bus. It is critical that the logic states set on the bus signal do not get disturbed during card insertion/removal. | set to hot                                                          |

| 4                        | Hot-swap on<br>an active<br>bus | Yes                           | Bus may<br>have active<br>I/O<br>processes<br>ongoing,<br>but device<br>being<br>inserted or<br>removed<br>must be<br>idle. | Same as<br>Level 2                                                                                  | Same as<br>Level 3                                 | There is activity on<br>the system bus, and it<br>is critical that the logic<br>states set on the bus<br>signal do not get<br>disturbed during card<br>insertion/removal.                            |                                                                     |

2-141 Revision 6

# **Electrostatic Discharge (ESD) Protection**

Fusion devices are tested per JEDEC Standard JESD22-A114-B.

Fusion devices contain clamp diodes at every I/O, global, and power pad. Clamp diodes protect all device pads against damage from ESD as well as from excessive voltage transients.

Each I/O has two clamp diodes. One diode has its positive (P) side connected to the pad and its negative (N) side connected to VCCI. The second diode has its P side connected to GND and its N side connected to the pad. During operation, these diodes are normally biased in the Off state, except when transient voltage is significantly above VCCI or below GND levels.

By selecting the appropriate I/O configuration, the diode is turned on or off. Refer to Table 2-75 and Table 2-76 on page 2-143 for more information about I/O standards and the clamp diode.

The second diode is always connected to the pad, regardless of the I/O configuration selected.

Table 2-75 • Fusion Standard and Advanced I/O - Hot-Swap and 5 V Input Tolerance Capabilities

|                                                             | Clamp Diode     |              | Hot Insertion   |              | 5 V Input 1      | Folerance <sup>1</sup> | Innut           | Output   |

|-------------------------------------------------------------|-----------------|--------------|-----------------|--------------|------------------|------------------------|-----------------|----------|

| I/O Assignment                                              | Standard<br>I/O | Advanced I/O | Standard<br>I/O | Advanced I/O | Standard<br>I/O  | Advanced I/O           | Input<br>Buffer | Buffer   |

| 3.3 V LVTTL/LVCMOS                                          | No              | Yes          | Yes             | No           | Yes <sup>1</sup> | Yes <sup>1</sup>       | Enabled/l       | Disabled |

| 3.3 V PCI, 3.3 V PCI-X                                      | N/A             | Yes          | N/A             | No           | N/A              | Yes <sup>1</sup>       | Enabled/l       | Disabled |

| LVCMOS 2.5 V                                                | No              | Yes          | Yes             | No           | No               | No                     | Enabled/I       | Disabled |

| LVCMOS 2.5 V / 5.0 V                                        | N/A             | Yes          | N/A             | No           | N/A              | Yes <sup>2</sup>       | Enabled/I       | Disabled |

| LVCMOS 1.8 V                                                | No              | Yes          | Yes             | No           | No               | No                     | Enabled/I       | Disabled |

| LVCMOS 1.5 V                                                | No              | Yes          | Yes             | No           | No               | No                     | Enabled/I       | Disabled |

| Differential,<br>LVDS/BLVDS/M-<br>LVDS/ LVPECL <sup>3</sup> | N/A             | Yes          | N/A             | No           | N/A              | No                     | Enabled/l       | Disabled |

### Notes:

- 1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

- 2. Can be implemented with an external resistor and an internal clamp diode.

- 3. Bidirectional LVPECL buffers are not supported. I/Os can be configured as either input buffers or output buffers.

Table 2-76 • Fusion Pro I/O - Hot-Swap and 5 V Input Tolerance Capabilities

| I/O Assignment                                      | Clamp<br>Diode | Hot<br>Insertion | 5 V Input<br>Tolerance | Input Buffer | Output Buffer |

|-----------------------------------------------------|----------------|------------------|------------------------|--------------|---------------|

| 3.3 V LVTTL/LVCMOS                                  | No             | Yes              | Yes <sup>1</sup>       | Enabled      | l/Disabled    |

| 3.3 V PCI, 3.3 V PCI-X                              | Yes            | No               | Yes <sup>1</sup>       | Enabled      | l/Disabled    |

| LVCMOS 2.5 V 3                                      | No             | Yes              | No                     | Enabled      | l/Disabled    |

| LVCMOS 2.5 V / 5.0 V <sup>3</sup>                   | Yes            | No               | Yes <sup>2</sup>       | Enabled      | l/Disabled    |

| LVCMOS 1.8 V                                        | No             | Yes              | No                     | Enabled      | l/Disabled    |

| LVCMOS 1.5 V                                        | No             | Yes              | No                     | Enabled      | l/Disabled    |

| Voltage-Referenced Input Buffer                     | No             | Yes              | No                     | Enabled      | l/Disabled    |

| Differential, LVDS/BLVDS/M-LVDS/LVPECL <sup>4</sup> | No             | Yes              | No                     | Enabled      | l/Disabled    |

### Notes:

- 1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

- 2. Can be implemented with an external resistor and an internal clamp diode.

- In the SmartGen, FlashROM, Flash Memory System Builder, and Analog System Builder User Guide, select the LVCMOS5 macro for the LVCMOS 2.5 V / 5.0 V I/O standard or the LVCMOS25 macro for the LVCMOS 2.5 V I/O standard

- 4. Bidirectional LVPECL buffers are not supported. I/Os can be configured as either input buffers or output buffers.

2-143 Revision 6

Table 2-96 • I/O Output Buffer Maximum Resistances 1 (continued)

| Standard                         | Drive Strength | R <sub>PULL-DOWN</sub> (ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |  |  |  |  |  |

|----------------------------------|----------------|--------------------------------------------|---------------------------------------------|--|--|--|--|--|

| Applicable to Standard I/O Banks |                |                                            |                                             |  |  |  |  |  |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA           | 100                                        | 300                                         |  |  |  |  |  |

|                                  | 4 mA           | 100                                        | 300                                         |  |  |  |  |  |

|                                  | 6 mA           | 50                                         | 150                                         |  |  |  |  |  |

|                                  | 8 mA           | 50                                         | 150                                         |  |  |  |  |  |

| 2.5 V LVCMOS                     | 2 mA           | 100                                        | 200                                         |  |  |  |  |  |

|                                  | 4 mA           | 100                                        | 200                                         |  |  |  |  |  |

|                                  | 6 mA           | 50                                         | 100                                         |  |  |  |  |  |

|                                  | 8 mA           | 50                                         | 100                                         |  |  |  |  |  |

| 1.8 V LVCMOS                     | 2 mA           | 200                                        | 225                                         |  |  |  |  |  |

|                                  | 4 mA           | 100                                        | 112                                         |  |  |  |  |  |

| 1.5 V LVCMOS                     | 2 mA           | 200                                        | 224                                         |  |  |  |  |  |

### Notes:

- 2.  $R_{(PULL-DOWN-MAX)} = VOLspec / I_{OLspec}$

- 3.  $R_{(PULL-UP-MAX)} = (VCCImax VOHspec) / IOHspec$

Table 2-97 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|       | R <sub>(WEAK</sub> | PULL-UP)<br>nms) | R <sub>(WEAK PULL-DOWN)</sub> <sup>2</sup> (ohms) |       |  |

|-------|--------------------|------------------|---------------------------------------------------|-------|--|

| VCCI  | Min.               | Max.             | Min.                                              | Max.  |  |

| 3.3 V | 10 k               | 45 k             | 10 k                                              | 45 k  |  |

| 2.5 V | 11 k               | 55 k             | 12 k                                              | 74 k  |  |

| 1.8 V | 18 k               | 70 k             | 17 k                                              | 110 k |  |

| 1.5 V | 19 k               | 90 k             | 19 k                                              | 140 k |  |

### Notes:

- 1.  $R_{(WEAK\ PULL\ -UP\ -MAX)} = (VCCImax VOHspec) / I_{WEAK\ PULL\ -UP\ -MIN}$ 2.  $R_{(WEAK\ PULL\ -DOWN\ -MAX)} = VOLspec / I_{WEAK\ PULL\ -DOWN\ -MIN}$

2-171 Revision 6

<sup>1.</sup> These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

Table 2-99 • Short Current Event Duration before Failure

| Temperature | Time Before Failure |

|-------------|---------------------|

| -40°C       | >20 years           |

| 0°C         | >20 years           |

| 25°C        | >20 years           |

| 70°C        | 5 years             |

| 85°C        | 2 years             |

| 100°C       | 6 months            |

Table 2-100 • Schmitt Trigger Input Hysteresis

Hysteresis Voltage Value (typ.) for Schmitt Mode Input Buffers

| Input Buffer Configuration                          | Hysteresis Value (typ.) |

|-----------------------------------------------------|-------------------------|

| 3.3 V LVTTL/LVCMOS/PCI/PCI-X (Schmitt trigger mode) | 240 mV                  |

| 2.5 V LVCMOS (Schmitt trigger mode)                 | 140 mV                  |

| 1.8 V LVCMOS (Schmitt trigger mode)                 | 80 mV                   |

| 1.5 V LVCMOS (Schmitt trigger mode)                 | 60 mV                   |

### Table 2-101 • I/O Input Rise Time, Fall Time, and Related I/O Reliability

| Input Buffer                            | Input Rise/Fall Time (min.) | Input Rise/Fall Time (max.)                                              | Reliability      |

|-----------------------------------------|-----------------------------|--------------------------------------------------------------------------|------------------|

| LVTTL/LVCMOS (Schmitt trigger disabled) | No requirement              | 10 ns*                                                                   | 20 years (100°C) |

| LVTTL/LVCMOS (Schmitt trigger enabled)  | No requirement              | No requirement, but input noise voltage cannot exceed Schmitt hysteresis | 20 years (100°C) |

| HSTL/SSTL/GTL                           | No requirement              | 10 ns*                                                                   | 10 years (100°C) |

| LVDS/BLVDS/M-LVDS/LVPECL                | No requirement              | 10 ns*                                                                   | 10 years (100°C) |

Note: \* The maximum input rise/fall time is related only to the noise induced into the input buffer trace. If the noise is low, the rise time and fall time of input buffers, when Schmitt trigger is disabled, can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure there is no excessive noise coupling into input signals.

Fusion Family of Mixed Signal FPGAs

Table 2-106 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 3.0 V

Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zhs</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 10.26           | 0.04             | 1.20            | 0.43              | 10.45           | 8.90            | 2.64            | 2.46            | 12.68            | 11.13            | ns    |

|                   | -1             | 0.56              | 8.72            | 0.04             | 1.02            | 0.36              | 8.89            | 7.57            | 2.25            | 2.09            | 10.79            | 9.47             | ns    |

|                   | -2             | 0.49              | 7.66            | 0.03             | 0.90            | 0.32              | 7.80            | 6.64            | 1.98            | 1.83            | 9.47             | 8.31             | ns    |

| 8 mA              | Std.           | 0.66              | 7.27            | 0.04             | 1.20            | 0.43              | 7.41            | 6.28            | 2.98            | 3.04            | 9.65             | 8.52             | ns    |

|                   | -1             | 0.56              | 6.19            | 0.04             | 1.02            | 0.36              | 6.30            | 5.35            | 2.54            | 2.59            | 8.20             | 7.25             | ns    |

|                   | -2             | 0.49              | 5.43            | 0.03             | 0.90            | 0.32              | 5.53            | 4.69            | 2.23            | 2.27            | 7.20             | 6.36             | ns    |

| 12 mA             | Std.           | 0.66              | 5.58            | 0.04             | 1.20            | 0.43              | 5.68            | 4.87            | 3.21            | 3.42            | 7.92             | 7.11             | ns    |

|                   | -1             | 0.56              | 4.75            | 0.04             | 1.02            | 0.36              | 4.84            | 4.14            | 2.73            | 2.91            | 6.74             | 6.05             | ns    |

|                   | -2             | 0.49              | 4.17            | 0.03             | 0.90            | 0.32              | 4.24            | 3.64            | 2.39            | 2.55            | 5.91             | 5.31             | ns    |

| 16 mA             | Std.           | 0.66              | 5.21            | 0.04             | 1.20            | 0.43              | 5.30            | 4.56            | 3.26            | 3.51            | 7.54             | 6.80             | ns    |

|                   | -1             | 0.56              | 4.43            | 0.04             | 1.02            | 0.36              | 4.51            | 3.88            | 2.77            | 2.99            | 6.41             | 5.79             | ns    |

|                   | -2             | 0.49              | 3.89            | 0.03             | 0.90            | 0.32              | 3.96            | 3.41            | 2.43            | 2.62            | 5.63             | 5.08             | ns    |

| 24 mA             | Std.           | 0.66              | 4.85            | 0.04             | 1.20            | 0.43              | 4.94            | 4.54            | 3.32            | 3.88            | 7.18             | 6.78             | ns    |

|                   | -1             | 0.56              | 4.13            | 0.04             | 1.02            | 0.36              | 4.20            | 3.87            | 2.82            | 3.30            | 6.10             | 5.77             | ns    |

|                   | -2             | 0.49              | 3.62            | 0.03             | 0.90            | 0.32              | 3.69            | 3.39            | 2.48            | 2.90            | 5.36             | 5.06             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

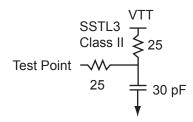

### SSTL3 Class II

Stub-Speed Terminated Logic for 3.3 V memory bus standard (JESD8-8). Fusion devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-165 • Minimum and Maximum DC Input and Output Levels

| SSTL3 Class II |           | VIL VIH    |            | VIH       |           | VIH        |    | VOH | IOL                     | ЮН                      | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|----------------|-----------|------------|------------|-----------|-----------|------------|----|-----|-------------------------|-------------------------|-------------------------|-------------------------|------------------|------------------|

| Drive Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |                  |                  |

| 21 mA          | -0.3      | VREF - 0.2 | VREF + 0.2 | 3.6       | 0.5       | VCCI - 0.9 | 21 | 21  | 109                     | 103                     | 10                      | 10                      |                  |                  |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

Figure 2-133 • AC Loading

Table 2-166 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF - 0.2    | VREF + 0.2     | 1.5                  | 1.5             | 1.485          | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

### **Timing Characteristics**

Table 2-167 • SSTL3- Class II

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.5 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.07            | 0.04             | 1.25            | 0.43              | 2.10            | 1.67            |                 |                 | 4.34             | 3.91             | ns    |

| <b>-1</b>      | 0.56              | 1.76            | 0.04             | 1.06            | 0.36              | 1.79            | 1.42            |                 |                 | 3.69             | 3.32             | ns    |

| -2             | 0.49              | 1.54            | 0.03             | 0.93            | 0.32              | 1.57            | 1.25            |                 |                 | 3.24             | 2.92             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### XTAL2 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

# **Security**

Fusion devices have a built-in 128-bit AES decryption core. The decryption core facilitates highly secure, in-system programming of the FPGA core array fabric and the FlashROM. The FlashROM and the FPGA core fabric can be programmed independently from each other, allowing the FlashROM to be updated without the need for change to the FPGA core fabric. The AES master key is stored in on-chip nonvolatile memory (flash). The AES master key can be preloaded into parts in a security-protected programming environment (such as the Microsemi in-house programming center), and then "blank" parts can be shipped to an untrusted programming or manufacturing center for final personalization with an AES-encrypted bitstream. Late stage product changes or personalization can be implemented easily and with high level security by simply sending a STAPL file with AES-encrypted data. Highly secure remote field updates over public networks (such as the Internet) are possible by sending and programming a STAPL file with AES-encrypted data. For more information, refer to the *Fusion Security* application note.

## 128-Bit AES Decryption

The 128-bit AES standard (FIPS-197) block cipher is the National Institute of Standards and Technology (NIST) replacement for DES (Data Encryption Standard FIPS46-2). AES has been designed to protect sensitive government information well into the 21st century. It replaces the aging DES, which NIST adopted in 1977 as a Federal Information Processing Standard used by federal agencies to protect sensitive, unclassified information. The 128-bit AES standard has  $3.4 \times 10^{38}$  possible 128-bit key variants, and it has been estimated that it would take 1,000 trillion years to crack 128-bit AES cipher text using exhaustive techniques. Keys are stored (protected with security) in Fusion devices in nonvolatile flash memory. All programming files sent to the device can be authenticated by the part prior to programming to ensure that bad programming data is not loaded into the part that may possibly damage it. All programming verification is performed on-chip, ensuring that the contents of Fusion devices remain as secure as possible.

AES decryption can also be used on the 1,024-bit FlashROM to allow for remote updates of the FlashROM contents. This allows for easy support of subscription model products and protects them with measures designed to provide the highest level of security available. See the application note *Fusion Security* for more details.

### AES for Flash Memory

AES decryption can also be used on the flash memory blocks. This provides the best available security during update of the flash memory blocks. During runtime, the encrypted data can be clocked in via the JTAG interface. The data can be passed through the internal AES decryption engine, and the decrypted data can then be stored in the flash memory block.

# **Programming**

Programming can be performed using various programming tools, such as Silicon Sculptor II (BP Micro Systems) or FlashPro3 (Microsemi).

The user can generate STP programming files from the Designer software and can use these files to program a device.

Fusion devices can be programmed in-system. During programming, VCCOSC is needed in order to power the internal 100 MHz oscillator. This oscillator is used as a source for the 20 MHz oscillator that is used to drive the charge pump for programming.

# Power per I/O Pin

Table 3-12 • Summary of I/O Input Buffer Power (per pin)—Default I/O Software Settings

|                                           | VCCI (V) | Static Power PDC7 (mW) <sup>1</sup> | Dynamic Power PAC9 (μW/MHz) <sup>2</sup> |

|-------------------------------------------|----------|-------------------------------------|------------------------------------------|

| Applicable to Pro I/O Banks               |          |                                     | •                                        |

| Single-Ended                              |          |                                     |                                          |

| 3.3 V LVTTL/LVCMOS                        | 3.3      | _                                   | 17.39                                    |

| 3.3 V LVTTL/LVCMOS – Schmitt trigger      | 3.3      | _                                   | 25.51                                    |

| 2.5 V LVCMOS                              | 2.5      | _                                   | 5.76                                     |

| 2.5 V LVCMOS – Schmitt trigger            | 2.5      | _                                   | 7.16                                     |

| 1.8 V LVCMOS                              | 1.8      | _                                   | 2.72                                     |

| 1.8 V LVCMOS – Schmitt trigger            | 1.8      | _                                   | 2.80                                     |

| 1.5 V LVCMOS (JESD8-11)                   | 1.5      | _                                   | 2.08                                     |

| 1.5 V LVCMOS (JESD8-11) – Schmitt trigger | 1.5      | _                                   | 2.00                                     |

| 3.3 V PCI                                 | 3.3      | _                                   | 18.82                                    |

| 3.3 V PCI – Schmitt trigger               | 3.3      | _                                   | 20.12                                    |

| 3.3 V PCI-X                               | 3.3      | _                                   | 18.82                                    |

| 3.3 V PCI-X – Schmitt trigger             | 3.3      | _                                   | 20.12                                    |

| Voltage-Referenced                        |          |                                     | -                                        |

| 3.3 V GTL                                 | 3.3      | 2.90                                | 8.23                                     |

| 2.5 V GTL                                 | 2.5      | 2.13                                | 4.78                                     |

| 3.3 V GTL+                                | 3.3      | 2.81                                | 4.14                                     |

| 2.5 V GTL+                                | 2.5      | 2.57                                | 3.71                                     |

| HSTL (I)                                  | 1.5      | 0.17                                | 2.03                                     |

| HSTL (II)                                 | 1.5      | 0.17                                | 2.03                                     |

| SSTL2 (I)                                 | 2.5      | 1.38                                | 4.48                                     |

| SSTL2 (II)                                | 2.5      | 1.38                                | 4.48                                     |

| SSTL3 (I)                                 | 3.3      | 3.21                                | 9.26                                     |

| SSTL3 (II)                                | 3.3      | 3.21                                | 9.26                                     |

| Differential                              |          |                                     | •                                        |

| LVDS                                      | 2.5      | 2.26                                | 1.50                                     |

| LVPECL                                    | 3.3      | 5.71                                | 2.17                                     |

### Notes:

<sup>1.</sup> PDC7 is the static power (where applicable) measured on VCCI.

<sup>2.</sup> PAC9 is the total dynamic power measured on VCC and VCCI.

Table 3-13 • Summary of I/O Output Buffer Power (per pin)—Default I/O Software Settings<sup>1</sup> (continued)

|                                 | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC8 (mW) <sup>2</sup> | Dynamic Power PAC10 (μW/MHz) <sup>3</sup> |

|---------------------------------|------------------------|----------|----------------------------------------|-------------------------------------------|

| Differential                    |                        |          |                                        |                                           |

| LVDS                            | -                      | 2.5      | 7.74                                   | 88.92                                     |

| LVPECL                          | -                      | 3.3      | 19.54                                  | 166.52                                    |

| Applicable to Standard I/O Banl | (S                     |          |                                        |                                           |

| Single-Ended                    |                        |          |                                        |                                           |

| 3.3 V LVTTL / 3.3 V LVCMOS      | 35                     | 3.3      | -                                      | 431.08                                    |

| 2.5 V LVCMOS                    | 35                     | 2.5      | -                                      | 247.36                                    |

| 1.8 V LVCMOS                    | 35                     | 1.8      | -                                      | 128.46                                    |

| 1.5 V LVCMOS (JESD8-11)         | 35                     | 1.5      | -                                      | 89.46                                     |

### Notes:

- 1. Dynamic power consumption is given for standard load and software-default drive strength and output slew.

- 2. PDC8 is the static power (where applicable) measured on VCCI.

- 3. PAC10 is the total dynamic power measured on VCC and VCCI.

3-21 Revision 6

|            |                 | FG256           |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| C7         | IO09RSB0V0      | IO12RSB0V0      | IO06NDB0V0      | IO09NDB0V1       |

| C8         | IO14RSB0V0      | IO22RSB0V0      | IO16PDB1V0      | IO23PDB1V0       |

| C9         | IO15RSB0V0      | IO23RSB0V0      | IO16NDB1V0      | IO23NDB1V0       |

| C10        | IO22RSB0V0      | IO30RSB0V0      | IO25NDB1V1      | IO31NDB1V1       |

| C11        | IO20RSB0V0      | IO31RSB0V0      | IO25PDB1V1      | IO31PDB1V1       |

| C12        | VCCIB0          | VCCIB0          | VCCIB1          | VCCIB1           |

| C13        | GBB1/IO28RSB0V0 | GBC1/IO35RSB0V0 | GBC1/IO26PPB1V1 | GBC1/IO40PPB1V2  |

| C14        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| C15        | GND             | GND             | GND             | GND              |

| C16        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| D1         | GFC2/IO50NPB3V0 | IO75NDB3V0      | IO84NDB4V0      | IO124NDB4V0      |

| D2         | GFA2/IO51NDB3V0 | GAB2/IO75PDB3V0 | GAB2/IO84PDB4V0 | GAB2/IO124PDB4V0 |

| D3         | GAC2/IO51PDB3V0 | IO76NDB3V0      | IO85NDB4V0      | IO125NDB4V0      |

| D4         | GAA2/IO52PDB3V0 | GAA2/IO76PDB3V0 | GAA2/IO85PDB4V0 | GAA2/IO125PDB4V0 |

| D5         | GAB2/IO52NDB3V0 | GAB0/IO02RSB0V0 | GAB0/IO02NPB0V0 | GAB0/IO02NPB0V0  |

| D6         | GAC0/IO04RSB0V0 | GAC0/IO04RSB0V0 | GAC0/IO03NDB0V0 | GAC0/IO03NDB0V0  |

| D7         | IO08RSB0V0      | IO13RSB0V0      | IO06PDB0V0      | IO09PDB0V1       |

| D8         | NC              | IO20RSB0V0      | IO14NDB0V1      | IO15NDB0V2       |

| D9         | NC              | IO21RSB0V0      | IO14PDB0V1      | IO15PDB0V2       |

| D10        | IO21RSB0V0      | IO28RSB0V0      | IO23PDB1V1      | IO37PDB1V2       |

| D11        | IO23RSB0V0      | GBB0/IO36RSB0V0 | GBB0/IO27NDB1V1 | GBB0/IO41NDB1V2  |

| D12        | NC              | NC              | VCCIB1          | VCCIB1           |

| D13        | GBA2/IO31PDB1V0 | GBA2/IO40PDB1V0 | GBA2/IO30PDB2V0 | GBA2/IO44PDB2V0  |

| D14        | GBB2/IO31NDB1V0 | IO40NDB1V0      | IO30NDB2V0      | IO44NDB2V0       |

| D15        | GBC2/IO32PDB1V0 | GBB2/IO41PDB1V0 | GBB2/IO31PDB2V0 | GBB2/IO45PDB2V0  |

| D16        | GCA2/IO32NDB1V0 | IO41NDB1V0      | IO31NDB2V0      | IO45NDB2V0       |

| E1         | GND             | GND             | GND             | GND              |

| E2         | GFB0/IO48NPB3V0 | IO73NDB3V0      | IO81NDB4V0      | IO118NDB4V0      |

| E3         | GFB2/IO50PPB3V0 | IO73PDB3V0      | IO81PDB4V0      | IO118PDB4V0      |

| E4         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| E5         | NC              | IO74NPB3V0      | IO83NPB4V0      | IO123NPB4V0      |

| E6         | NC              | IO08RSB0V0      | IO04NPB0V0      | IO05NPB0V1       |

| E7         | GND             | GND             | GND             | GND              |

| E8         | NC              | IO18RSB0V0      | IO08PDB0V1      | IO11PDB0V1       |

| E9         | NC              | NC              | IO20NDB1V0      | IO27NDB1V1       |

| E10        | GND             | GND             | GND             | GND              |

| E11        | IO24RSB0V0      | GBB1/IO37RSB0V0 | GBB1/IO27PDB1V1 | GBB1/IO41PDB1V2  |

| E12        | NC              | IO50PPB1V0      | IO33PSB2V0      | IO48PSB2V0       |

|            | 1               | I               |                 | 1                |

4-13 Revision 6