Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | -                                                               |

| Total RAM Bits                 | 36864                                                           |

| Number of I/O                  | 93                                                              |

| Number of Gates                | 250000                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                              |

| Package / Case                 | 208-BFQFP                                                       |

| Supplier Device Package        | 208-PQFP (28x28)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs250-2pq208i |

|                                |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Fusion Device Family Overview

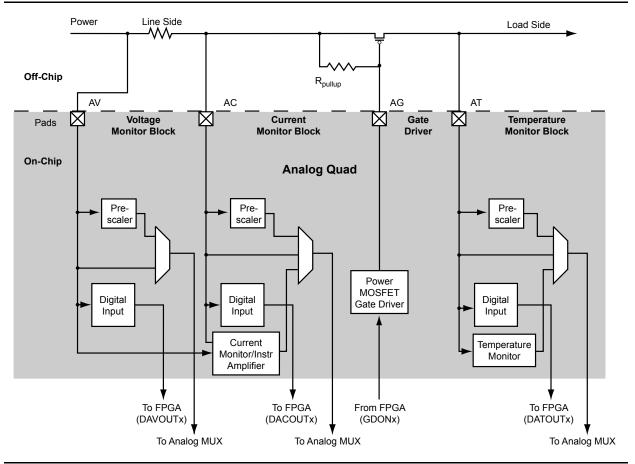

With Fusion, Microsemi also introduces the Analog Quad I/O structure (Figure 1-1). Each quad consists of three analog inputs and one gate driver. Each quad can be configured in various built-in circuit combinations, such as three prescaler circuits, three digital input circuits, a current monitor circuit, or a temperature monitor circuit. Each prescaler has multiple scaling factors programmed by FPGA signals to support a large range of analog inputs with positive or negative polarity. When the current monitor circuit is selected, two adjacent analog inputs measure the voltage drop across a small external sense resistor. For more information, refer to the "Analog System Characteristics" section on page 2-117. Built-in operational amplifiers amplify small voltage signals for accurate current measurement. One analog input in each quad can be connected to an external temperature monitor diode. In addition to the external temperature monitor diode(s), a Fusion device can monitor an internal temperature diode using dedicated channel 31 of the ADCMUX.

Figure 1-1 on page 1-5 illustrates a typical use of the Analog Quad I/O structure. The Analog Quad shown is configured to monitor and control an external power supply. The AV pad measures the source of the power supply. The AC pad measures the voltage drop across an external sense resistor to calculate current. The AG MOSFET gate driver pad turns the external MOSFET on and off. The AT pad measures the load-side voltage level.

Figure 1-1 • Analog Quad

### **No-Glitch MUX (NGMUX)**

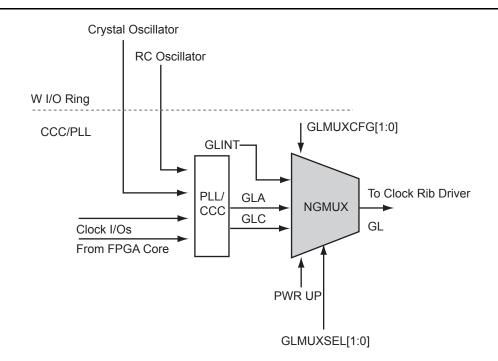

Positioned downstream from the PLL/CCC blocks, the NGMUX provides a special switching sequence between two asynchronous clock domains that prevents generating any unwanted narrow clock pulses. The NGMUX is used to switch the source of a global between three different clock sources. Allowable inputs are either two PLL/CCC outputs or a PLL/CCC output and a regular net, as shown in Figure 2-24. The GLMUXCFG[1:0] configuration bits determine the source of the CLK inputs (i.e., internal signal or GLC). These are set by SmartGen during design but can also be changed by dynamically reconfiguring the PLL. The GLMUXSEL[1:0] bits control which clock source is passed through the NGMUX to the global network (GL). See Table 2-13.

### Figure 2-24 • NGMUX

| Table 2-13 • NGMUX Configuration and | Selection Table |

|--------------------------------------|-----------------|

|--------------------------------------|-----------------|

| GLMUXCFG[1:0] | GLMUXSEL[1:0] |   | Selected Input Signal | MUX Type     |

|---------------|---------------|---|-----------------------|--------------|

| 00            | Х             | 0 | GLA                   | 2-to-1 GLMUX |

| 00            | Х             | 1 | GLC                   | 2-10-1 GEWOX |

| 01            | Х             | 0 | GLA                   | 2-to-1 GLMUX |

| - 01          | Х             | 1 | GLINT                 | 2-10-1 GEMOX |

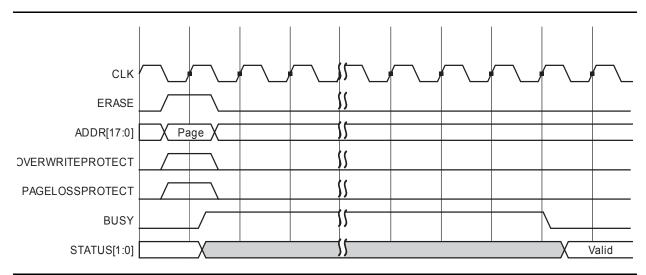

### Erase Page Operation

The Erase Page operation is initiated when the ERASEPAGE pin is asserted. The Erase Page operation allows the user to erase (set user data to zero) any page within the FB.

The use of the OVERWRITEPAGE and PAGELOSSPROTECT pins is the same for erase as for a Program Page operation.

As with the Program Page operation, a STATUS of '01' indicates that the addressed page is not erased.

A waveform for an Erase Page operation is shown in Figure 2-37.

Erase errors include the following:

- 1. Attempting to erase a page that is Overwrite Protected (STATUS = '01')

- 2. Attempting to erase a page that is not in the Page Buffer when the Page Buffer has entered Page Loss Protection mode (STATUS = '01')

- 3. The Write Count of the erased page exceeding the Write Threshold defined in the part specification (STATUS = '11')

- 4. The ECC Logic determining that there is an uncorrectable error within the erased page (STATUS = '10')

Figure 2-37 • FB Erase Page Waveform

Device Architecture

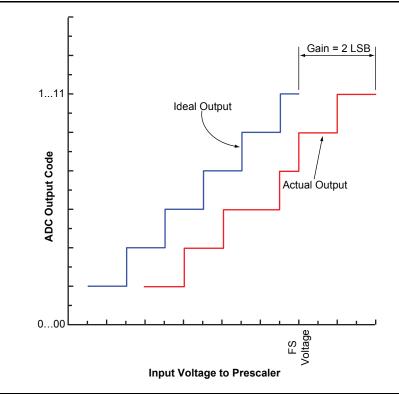

### Gain Error

The gain error of an ADC indicates how well the slope of an actual transfer function matches the slope of the ideal transfer function. Gain error is usually expressed in LSB or as a percent of full-scale (%FSR). Gain error is the full-scale error minus the offset error (Figure 2-84).

Figure 2-84 • Gain Error

### Gain Error Drift

Gain-error drift is the variation in gain error due to a change in ambient temperature, typically expressed in ppm/°C.

|                      | Calibrated Typical Error per Positive Prescaler Setting <sup>1</sup> (%FSR) |                        |                |          |                |                |                | Direct ADC <sup>2,3</sup><br>(%FSR) |  |

|----------------------|-----------------------------------------------------------------------------|------------------------|----------------|----------|----------------|----------------|----------------|-------------------------------------|--|

| Input Voltage<br>(V) | 16 V (AT)                                                                   | 16 V (12 V)<br>(AV/AC) | 8 V<br>(AV/AC) | 4 V (AT) | 4 V<br>(AV/AC) | 2 V<br>(AV/AC) | 1 V<br>(AV/AC) | VAREF = 2.56 V                      |  |

| 15                   | 1                                                                           |                        |                |          |                |                |                |                                     |  |

| 14                   | 1                                                                           |                        |                |          |                |                |                |                                     |  |

| 12                   | 1                                                                           | 1                      |                |          |                |                |                |                                     |  |

| 5                    | 2                                                                           | 2                      | 1              |          |                |                |                |                                     |  |

| 3.3                  | 2                                                                           | 2                      | 1              | 1        | 1              |                |                |                                     |  |

| 2.5                  | 3                                                                           | 2                      | 1              | 1        | 1              |                |                | 1                                   |  |

| 1.8                  | 4                                                                           | 4                      | 1              | 1        | 1              | 1              |                | 1                                   |  |

| 1.5                  | 5                                                                           | 5                      | 2              | 2        | 2              | 1              |                | 1                                   |  |

| 1.2                  | 7                                                                           | 6                      | 2              | 2        | 2              | 1              |                | 1                                   |  |

| 0.9                  | 9                                                                           | 9                      | 4              | 3        | 3              | 1              | 1              | 1                                   |  |

# Table 2-53 • Analog Channel Accuracy: Monitoring Standard Positive Voltages Typical Conditions, T<sub>A</sub> = 25°C

Notes:

1. Requires enabling Analog Calibration using SmartGen Analog System Builder. For further details, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

2. Direct ADC mode using an external VAREF of 2.56V±4.6mV, without Analog Calibration macro.

3. For input greater than 2.56 V, the ADC output will saturate. A higher VAREF or prescaler usage is recommended.

### Examples

### Calculating Accuracy for an Uncalibrated Analog Channel

### Formula

For a given prescaler range, EQ 30 gives the output voltage.

Output Voltage = (Channel Output Offset in V) + (Input Voltage x Channel Gain)

EQ 30

### where

Channel Output offset in V = Channel Input offset in LSBs x Equivalent voltage per LSB Channel Gain Factor = 1 + (% Channel Gain / 100)

### Example

Input Voltage = 5 V Chosen Prescaler range = 8 V range Refer to Table 2-51 on page 2-122.

Max. Output Voltage = (Max Positive input offset) + (Input Voltage x Max Positive Channel Gain)

Max. Positive input offset = (21 LSB) x (8 mV per LSB in 10-bit mode) Max. Positive input offset = 166 mV Max. Positive Gain Error = +3% Max. Positive Channel Gain = 1 + (+3% / 100) Max. Positive Channel Gain = 1.03 Max. Output Voltage = (166 mV) + (5 V x 1.03) Max. Output Voltage = **5.316 V**

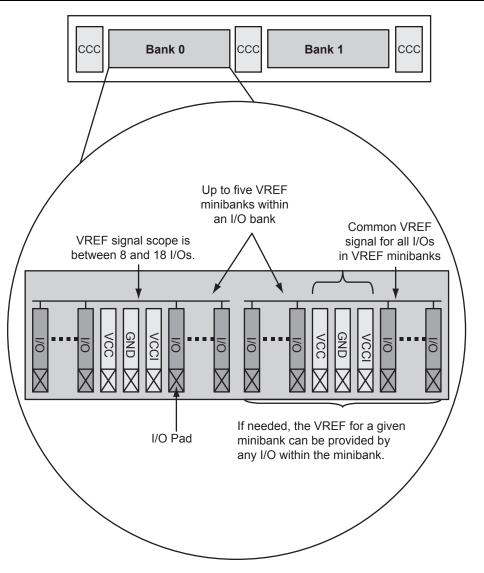

Figure 2-99 • Fusion Pro I/O Bank Detail Showing VREF Minibanks (north side of AFS600 and AFS1500)

| I/O Bank     | Single-Ended I/O Standards                                                                        | Differential I/O<br>Standards | Voltage-Referenced                                                                                          | Hot-<br>Swap |

|--------------|---------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------|--------------|

| Standard I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V                          | _                             | -                                                                                                           | Yes          |

| Advanced I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | -                                                                                                           | -            |

| Pro I/O      | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | GTL+2.5 V / 3.3 V, GTL 2.5 V / 3.3 V,<br>HSTL Class I and II, SSTL2 Class I<br>and II, SSTL3 Class I and II | Yes          |

# Features Supported on Pro I/Os

Table 2-72 lists all features supported by transmitter/receiver for single-ended and differential I/Os.

### Table 2-72 • Fusion Pro I/O Features

| Feature                                             | Description                                                                                                                                                                                                                            |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-ended and voltage-<br>referenced transmitter | <ul> <li>Hot insertion in every mode except PCI or 5 V input tolerant (these modes use<br/>clamp diodes and do not allow hot insertion)</li> </ul>                                                                                     |

| features                                            | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                                         |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                                                             |

|                                                     | Two slew rates                                                                                                                                                                                                                         |

|                                                     | <ul> <li>Skew between output buffer enable/disable time: 2 ns delay (rising edge) and<br/>0 ns delay (falling edge); see "Selectable Skew between Output Buffer<br/>Enable/Disable Time" on page 2-149 for more information</li> </ul> |

|                                                     | Five drive strengths                                                                                                                                                                                                                   |

|                                                     | 5 V-tolerant receiver ("5 V Input Tolerance" section on page 2-144)                                                                                                                                                                    |

|                                                     | <ul> <li>LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs ("5 V Output<br/>Tolerance" section on page 2-148)</li> </ul>                                                                                                       |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

| Single-ended receiver features                      | Schmitt trigger option                                                                                                                                                                                                                 |

|                                                     | ESD protection                                                                                                                                                                                                                         |

|                                                     | <ul> <li>Programmable delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                             |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Separate ground planes, GND/GNDQ, for input buffers only to avoid output-<br/>induced noise in the input circuitry</li> </ul>                                                                                                 |

| Voltage-referenced differential receiver features   | <ul> <li>Programmable Delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                             |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Separate ground planes, GND/GNDQ, for input buffers only to avoid output-<br/>induced noise in the input circuitry</li> </ul>                                                                                                 |

| CMOS-style LVDS, BLVDS,<br>M-LVDS, or LVPECL        | <ul> <li>Two I/Os and external resistors are used to provide a CMOS-style LVDS,<br/>BLVDS, M-LVDS, or LVPECL transmitter solution.</li> </ul>                                                                                          |

| transmitter                                         | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                                         |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                                                             |

|                                                     | Fast slew rate                                                                                                                                                                                                                         |

| LVDS/LVPECL differential                            | ESD protection                                                                                                                                                                                                                         |

| receiver features                                   | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Programmable delay: 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                                               |

|                                                     | <ul> <li>Separate input buffer ground and power planes to avoid output-induced noise<br/>in the input circuitry</li> </ul>                                                                                                             |

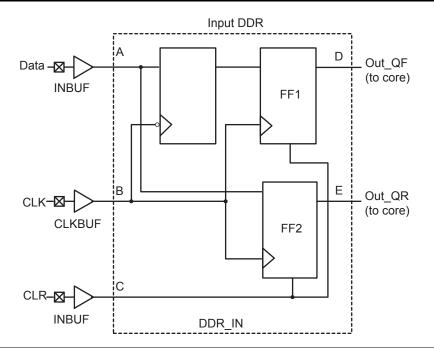

# DDR Module Specifications

Input DDR Module

### Figure 2-142 • Input DDR Timing Model

### Table 2-179 • Parameter Definitions

| Parameter Name                              | Parameter Definition         | Measuring Nodes (from, to) |

|---------------------------------------------|------------------------------|----------------------------|

| t <sub>DDRICLKQ1</sub>                      | Clock-to-Out Out_QR          | B, D                       |

| t <sub>DDRICLKQ2</sub>                      | Clock-to-Out Out_QF          | B, E                       |

| t <sub>DDRISUD</sub>                        | Data Setup Time of DDR Input | A, B                       |

| t <sub>DDRIHD</sub>                         | Data Hold Time of DDR Input  | A, B                       |

| t <sub>DDRICLR2Q1</sub>                     | Clear-to-Out Out_QR          | C, D                       |

| t <sub>DDRICLR2Q2</sub> Clear-to-Out Out_QF |                              | C, E                       |

| t <sub>DDRIREMCLR</sub> Clear Removal       |                              | С, В                       |

| t <sub>DDRIRECCLR</sub>                     | Clear Recovery               | С, В                       |

# **Pin Descriptions**

### **Supply Pins**

GND Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

### GNDQ Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ needs to always be connected on the board to GND. Note: In FG256, FG484, and FG676 packages, GNDQ and GND pins are connected within the package and are labeled as GND pins in the respective package pin assignment tables.

### ADCGNDREF Analog Reference Ground

Analog ground reference used by the ADC. This pad should be connected to a quiet analog ground.

### GNDA Ground (analog)

Quiet ground supply voltage to the Analog Block of Fusion devices. The use of a separate analog ground helps isolate the analog functionality of the Fusion device from any digital switching noise. A 0.2 V maximum differential voltage between GND and GNDA/GNDQ should apply to system implementation.

### GNDAQ Ground (analog quiet)

Quiet ground supply voltage to the analog I/O of Fusion devices. The use of a separate analog ground helps isolate the analog functionality of the Fusion device from any digital switching noise. A 0.2 V maximum differential voltage between GND and GNDA/GNDQ should apply to system implementation. Note: In FG256, FG484, and FG676 packages, GNDAQ and GNDA pins are connected within the package and are labeled as GNDA pins in the respective package pin assignment tables.

### GNDNVM Flash Memory Ground

Ground supply used by the Fusion device's flash memory block module(s).

### GNDOSC Oscillator Ground

Ground supply for both integrated RC oscillator and crystal oscillator circuit.

### VCC15A Analog Power Supply (1.5 V)

1.5 V clean analog power supply input for use by the 1.5 V portion of the analog circuitry.

### VCC33A Analog Power Supply (3.3 V)

3.3 V clean analog power supply input for use by the 3.3 V portion of the analog circuitry.

### VCC33N Negative 3.3 V Output

This is the -3.3 V output from the voltage converter. A 2.2  $\mu$ F capacitor must be connected from this pin to ground.

### VCC33PMP Analog Power Supply (3.3 V)

3.3 V clean analog power supply input for use by the analog charge pump. To avoid high current draw, VCC33PMP should be powered up simultaneously with or after VCC33A.

### VCCNVM Flash Memory Block Power Supply (1.5 V)

1.5 V power supply input used by the Fusion device's flash memory block module(s). To avoid high current draw, VCC should be powered up before or simultaneously with VCCNVM.

### VCCOSC Oscillator Power Supply (3.3 V)

Power supply for both integrated RC oscillator and crystal oscillator circuit. The internal 100 MHz oscillator, powered by the VCCOSC pin, is needed for device programming, operation of the VDDN33 pump, and eNVM operation. VCCOSC is off only when VCCA is off. VCCOSC must be powered whenever the Fusion device needs to function.

## **Thermal Characteristics**

### Introduction

The temperature variable in the Microsemi Designer software refers to the junction temperature, not the ambient, case, or board temperatures. This is an important distinction because dynamic and static power consumption will cause the chip's junction temperature to be higher than the ambient, case, or board temperatures. EQ 1 through EQ 3 give the relationship between thermal resistance, temperature gradient, and power.

$$\theta_{\mathsf{J}\mathsf{A}} = \frac{\mathsf{T}_{\mathsf{J}} - \theta_{\mathsf{A}}}{\mathsf{P}}$$

EQ 1

$$\theta_{\mathsf{JB}} = \frac{\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{B}}}{\mathsf{P}}$$

EQ 2

EQ 3

$$\theta_{JC} = \frac{T_J - T_C}{P}$$

where

- $\theta_{JA}$  = Junction-to-air thermal resistance

- $\theta_{JB}$  = Junction-to-board thermal resistance

- $\theta_{JC}$  = Junction-to-case thermal resistance

- T<sub>J</sub> = Junction temperature

- T<sub>A</sub> = Ambient temperature

- T<sub>B</sub> = Board temperature (measured 1.0 mm away from the package edge)

T<sub>C</sub> = Case temperature

P = Total power dissipated by the device

### Table 3-6 • Package Thermal Resistance

|               |           | $\theta_{JA}$ |         |      |               |       |

|---------------|-----------|---------------|---------|------|---------------|-------|

| Product       | Still Air | 1.0 m/s       | 2.5 m/s | θJC  | $\theta_{JB}$ | Units |

| AFS090-QN108  | 34.5      | 30.0          | 27.7    | 8.1  | 16.7          | °C/W  |

| AFS090-QN180  | 33.3      | 27.6          | 25.7    | 9.2  | 21.2          | °C/W  |

| AFS250-QN180  | 32.2      | 26.5          | 24.7    | 5.7  | 15.0          | °C/W  |

| AFS250-PQ208  | 42.1      | 38.4          | 37      | 20.5 | 36.3          | °C/W  |

| AFS600-PQ208  | 23.9      | 21.3          | 20.48   | 6.1  | 16.5          | °C/W  |

| AFS090-FG256  | 37.7      | 33.9          | 32.2    | 11.5 | 29.7          | °C/W  |

| AFS250-FG256  | 33.7      | 30.0          | 28.3    | 9.3  | 24.8          | °C/W  |

| AFS600-FG256  | 28.9      | 25.2          | 23.5    | 6.8  | 19.9          | °C/W  |

| AFS1500-FG256 | 23.3      | 19.6          | 18.0    | 4.3  | 14.2          | °C/W  |

| AFS600-FG484  | 21.8      | 18.2          | 16.7    | 7.7  | 16.8          | °C/W  |

| AFS1500-FG484 | 21.6      | 16.8          | 15.2    | 5.6  | 14.9          | °C/W  |

| AFS1500-FG676 | TBD       | TBD           | TBD     | TBD  | TBD           | °C/W  |

| Parameter          | Description                | Conditions                                                                       | Temp.                  | Min | Тур  | Max | Unit |

|--------------------|----------------------------|----------------------------------------------------------------------------------|------------------------|-----|------|-----|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current    | Operational standby <sup>4</sup> ,                                               | T <sub>J</sub> = 25°C  |     | 4.8  | 10  | mA   |

|                    |                            | VCC = 1.575 V                                                                    | T <sub>J</sub> = 85°C  |     | 8.2  | 30  | mA   |

|                    |                            |                                                                                  | T <sub>J</sub> = 100°C |     | 15   | 50  | mA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VCC = 0 V              |                        |     | 0    | 0   | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies      | Operational standby <sup>4</sup> ,                                               | T <sub>J</sub> = 25°C  |     | 9.8  | 13  | mA   |

|                    | current                    | VCC33 = 3.63 V                                                                   | T <sub>J</sub> = 85°C  |     | 9.8  | 14  | mA   |

|                    |                            |                                                                                  | T <sub>J</sub> = 100°C |     | 10.8 | 15  | mA   |

|                    |                            | Operational standby, only<br>Analog Quad and –3.3 V<br>output ON, VCC33 = 3.63 V | T <sub>J</sub> = 25°C  |     | 0.29 | 2   | mA   |

|                    |                            |                                                                                  | T <sub>J</sub> = 85°C  |     | 0.31 | 2   | mA   |

|                    |                            |                                                                                  | T <sub>J</sub> = 100°C |     | 0.45 | 2   | mA   |

|                    |                            | Standby mode <sup>5</sup> , VCC33 = 3.63V                                        | T <sub>J</sub> = 25°C  |     | 2.9  | 3.0 | mA   |

|                    |                            |                                                                                  | T <sub>J</sub> = 85°C  |     | 2.9  | 3.1 | mA   |

|                    |                            |                                                                                  | T <sub>J</sub> = 100°C |     | 3.5  | 6   | mA   |

|                    |                            | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                                         | T <sub>J</sub> = 25°C  |     | 19   | 18  | μΑ   |

|                    |                            |                                                                                  | T <sub>J</sub> = 85°C  |     | 19   | 20  | μA   |

|                    |                            |                                                                                  | T <sub>J</sub> = 100°C |     | 24   | 25  | μA   |

| ICCI <sup>3</sup>  | I/O quiescent current      | Operational standby <sup>6</sup> ,<br>VCCIx = 3.63 V                             | T <sub>J</sub> = 25°C  |     | 266  | 437 | μΑ   |

|                    |                            |                                                                                  | T <sub>J</sub> = 85°C  |     | 266  | 437 | μΑ   |

|                    |                            |                                                                                  | T <sub>J</sub> = 100°C |     | 266  | 437 | μA   |

| IJTAG              | JTAG I/O quiescent current | Operational standby <sup>4</sup> ,                                               | T <sub>J</sub> = 25°C  |     | 80   | 100 | μA   |

|                    |                            | VJTAG = 3.63 V                                                                   | T <sub>J</sub> = 85°C  |     | 80   | 100 | μA   |

|                    |                            |                                                                                  | T <sub>J</sub> = 100°C |     | 80   | 100 | μA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VJTAG = 0 V            |                        |     | 0    | 0   | μA   |

Notes:

1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, and ICCI2.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTA G = VPUMP = 0 V.

| Parameter          | Description                | Conditions                                                                      | Temp.                  | Min | Тур  | Мах | Unit |

|--------------------|----------------------------|---------------------------------------------------------------------------------|------------------------|-----|------|-----|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current    | Operational standby <sup>4</sup> ,                                              | T <sub>J</sub> = 25°C  |     | 5    | 7.5 | mA   |

|                    |                            | VCC = 1.575 V                                                                   | T <sub>J</sub> = 85°C  |     | 6.5  | 20  | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 14   | 48  | mA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , V <sub>CC</sub> = 0 V |                        |     | 0    | 0   | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies      | Operational standby <sup>4</sup> ,                                              | T <sub>J</sub> = 25°C  |     | 9.8  | 12  | mA   |

|                    | current                    | VCC33 = 3.63 V                                                                  | T <sub>J</sub> = 85°C  |     | 9.8  | 12  | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 10.7 | 15  | mA   |

|                    |                            | Operational standby, only                                                       | T <sub>J</sub> = 25°C  |     | 0.30 | 2   | mA   |

|                    |                            | Analog Quad and –3.3 V<br>output ON, VCC33 = 3.63 V                             | T <sub>J</sub> = 85°C  |     | 0.30 | 2   | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 0.45 | 2   | mA   |

|                    |                            | Standby mode <sup>5</sup> ,<br>VCC33 = 3.63 V                                   | T <sub>J</sub> = 25°C  |     | 2.9  | 2.9 | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 2.9  | 3.0 | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 3.5  | 6   | mA   |

|                    |                            | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                                        | T <sub>J</sub> = 25°C  |     | 17   | 18  | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 18   | 20  | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 24   | 25  | μA   |

| ICCI <sup>3</sup>  | I/O quiescent current      | Operational standby <sup>6</sup> ,<br>VCCIx = 3.63 V                            | T <sub>J</sub> = 25°C  |     | 260  | 437 | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 260  | 437 | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 260  | 437 | μA   |

| IJTAG              | JTAG I/O quiescent current | Operational standby <sup>4</sup> ,<br>VJTAG = 3.63 V                            | T <sub>J</sub> = 25°C  |     | 80   | 100 | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 80   | 100 | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 80   | 100 | μA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VJTAG = 0 V           |                        |     | 0    | 0   | μA   |

| IPP                | Programming supply current | Non-programming mode,<br>VPUMP = 3.63 V                                         | T <sub>J</sub> = 25°C  |     | 37   | 80  | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 37   | 80  | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 80   | 100 | μA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VPUMP = 0 V           |                        |     | 0    | 0   | μA   |

Notes:

1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, and ICCI2.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

# **Microsemi**

Package Pin Assignments

|            | QN108           | QN108      |                 | QN108                     |                 |

|------------|-----------------|------------|-----------------|---------------------------|-----------------|

| Pin Number | AFS090 Function | Pin Number | AFS090 Function | Pin Number AFS090 Functio |                 |

| A1         | NC              | A39        | GND             | B21                       | AC2             |

| A2         | GNDQ            | A40        | GCB1/IO35PDB1V0 | B22                       | ATRTN1          |

| A3         | GAA2/IO52PDB3V0 | A41        | GCB2/IO33PDB1V0 | B23                       | AG3             |

| A4         | GND             | A42        | GBA2/IO31PDB1V0 | B24                       | AV3             |

| A5         | GFA1/IO47PDB3V0 | A43        | NC              | B25                       | VCC33A          |

| A6         | GEB1/IO45PDB3V0 | A44        | GBA1/IO30RSB0V0 | B26                       | VAREF           |

| A7         | VCCOSC          | A45        | GBB1/IO28RSB0V0 | B27                       | PUB             |

| A8         | XTAL2           | A46        | GND             | B28                       | VCC33A          |

| A9         | GEA1/IO44PPB3V0 | A47        | VCC             | B29                       | PTBASE          |

| A10        | GEA0/IO44NPB3V0 | A48        | GBC1/IO26RSB0V0 | B30                       | VCCNVM          |

| A11        | GEB2/IO42PDB3V0 | A49        | IO21RSB0V0      | B31                       | VCC             |

| A12        | VCCNVM          | A50        | IO19RSB0V0      | B32                       | TDI             |

| A13        | VCC15A          | A51        | IO09RSB0V0      | B33                       | TDO             |

| A14        | PCAP            | A52        | GAC0/IO04RSB0V0 | B34                       | VJTAG           |

| A15        | NC              | A53        | VCCIB0          | B35                       | GDC0/IO38NDB1V  |

| A16        | GNDA            | A54        | GND             |                           | 0               |

| A17        | AV0             | A55        | GAB0/IO02RSB0V0 | B36                       | VCCIB1          |

| A18        | AG0             | A56        | GAA0/IO00RSB0V0 | B37                       | GCB0/IO35NDB1V0 |

| A19        | ATRTN0          | B1         | VCOMPLA         | B38                       | GCC2/IO33NDB1V  |

| A20        | AT1             | B2         | VCCIB3          |                           | 0               |

| A21        | AC1             | B3         | GAB2/IO52NDB3V0 | B39                       | GBB2/IO31NDB1V0 |

| A22        | AV2             | B4         | VCCIB3          | B40                       | VCCIB1          |

| A23        | AG2             | B5         | GFA0/IO47NDB3V0 | B41                       | GNDQ            |

| A24        | AT2             | B6         | GEB0/IO45NDB3V0 | B42                       | GBA0/IO29RSB0V0 |

| A25        | AT3             | B7         | XTAL1           | B43                       | VCCIB0          |

| A26        | AC3             | B8         | GNDOSC          | B44                       | GBB0/IO27RSB0V0 |

| A27        | GNDAQ           | B9         | GEC2/IO43PSB3V0 | B45                       | GBC0/IO25RSB0V0 |

| A28        | ADCGNDREF       | B10        | GEA2/IO42NDB3V0 | B46                       | IO20RSB0V0      |

| A29        | NC              | B11        | VCC             | B47                       | IO10RSB0V0      |

| A30        | GNDA            | B12        | GNDNVM          | B48                       | GAC1/IO05RSB0V0 |

| A31        | PTEM            | B13        | NCAP            | B49                       | GAB1/IO03RSB0V0 |

| A32        | GNDNVM          | B14        | VCC33PMP        | B50                       | VCC             |

| A33        | VPUMP           | B15        | VCC33N          | B51                       | GAA1/IO01RSB0V0 |

| A34        | тск             | B16        | GNDAQ           | B52                       | VCCPLA          |

| A35        | TMS             | B17        | AC0             |                           |                 |

| A36        | TRST            | B18        | AT0             |                           |                 |

| A37        | GDB1/IO39PSB1V0 | B19        | AG1             |                           |                 |

| A38        | GDC1/IO38PDB1V0 | B20        | AV1             |                           |                 |

Package Pin Assignments

| PQ208         |                 |                 | PQ208         |                 |                 |  |

|---------------|-----------------|-----------------|---------------|-----------------|-----------------|--|

| Pin<br>Number | AFS250 Function | AFS600 Function | Pin<br>Number | AFS250 Function | AFS600 Function |  |

| 147           | GCC1/IO47PDB1V0 | IO39NDB2V0      | 184           | IO18RSB0V0      | IO10PPB0V1      |  |

| 148           | IO42NDB1V0      | GCA2/IO39PDB2V0 | 185           | IO17RSB0V0      | IO09PPB0V1      |  |

| 149           | GBC2/IO42PDB1V0 | IO31NDB2V0      | 186           | IO16RSB0V0      | IO10NPB0V1      |  |

| 150           | VCCIB1          | GBB2/IO31PDB2V0 | 187           | IO15RSB0V0      | IO09NPB0V1      |  |

| 151           | GND             | IO30NDB2V0      | 188           | VCCIB0          | IO08PPB0V1      |  |

| 152           | VCC             | GBA2/IO30PDB2V0 | 189           | GND             | IO07PPB0V1      |  |

| 153           | IO41NDB1V0      | VCCIB2          | 190           | VCC             | IO08NPB0V1      |  |

| 154           | GBB2/IO41PDB1V0 | GNDQ            | 191           | IO14RSB0V0      | IO07NPB0V1      |  |

| 155           | IO40NDB1V0      | VCOMPLB         | 192           | IO13RSB0V0      | IO06PPB0V0      |  |

| 156           | GBA2/IO40PDB1V0 | VCCPLB          | 193           | IO12RSB0V0      | IO05PPB0V0      |  |

| 157           | GBA1/IO39RSB0V0 | VCCIB1          | 194           | IO11RSB0V0      | IO06NPB0V0      |  |

| 158           | GBA0/IO38RSB0V0 | GNDQ            | 195           | IO10RSB0V0      | IO04PPB0V0      |  |

| 159           | GBB1/IO37RSB0V0 | GBB1/IO27PPB1V1 | 196           | IO09RSB0V0      | IO05NPB0V0      |  |

| 160           | GBB0/IO36RSB0V0 | GBA1/IO28PPB1V1 | 197           | IO08RSB0V0      | IO04NPB0V0      |  |

| 161           | GBC1/IO35RSB0V0 | GBB0/IO27NPB1V1 | 198           | IO07RSB0V0      | GAC1/IO03PDB0V0 |  |

| 162           | VCCIB0          | GBA0/IO28NPB1V1 | 199           | IO06RSB0V0      | GAC0/IO03NDB0V0 |  |

| 163           | GND             | VCCIB1          | 200           | GAC1/IO05RSB0V0 | VCCIB0          |  |

| 164           | VCC             | GND             | 201           | VCCIB0          | GND             |  |

| 165           | GBC0/IO34RSB0V0 | VCC             | 202           | GND             | VCC             |  |

| 166           | IO33RSB0V0      | GBC1/IO26PDB1V1 | 203           | VCC             | GAB1/IO02PDB0V0 |  |

| 167           | IO32RSB0V0      | GBC0/IO26NDB1V1 | 204           | GAC0/IO04RSB0V0 | GAB0/IO02NDB0V0 |  |

| 168           | IO31RSB0V0      | IO24PPB1V1      | 205           | GAB1/IO03RSB0V0 | GAA1/IO01PDB0V0 |  |

| 169           | IO30RSB0V0      | IO23PPB1V1      | 206           | GAB0/IO02RSB0V0 | GAA0/IO01NDB0V0 |  |

| 170           | IO29RSB0V0      | IO24NPB1V1      | 207           | GAA1/IO01RSB0V0 | GNDQ            |  |

| 171           | IO28RSB0V0      | IO23NPB1V1      | 208           | GAA0/IO00RSB0V0 | VCCIB0          |  |

| 172           | IO27RSB0V0      | IO22PPB1V0      |               |                 |                 |  |

| 173           | IO26RSB0V0      | IO21PPB1V0      |               |                 |                 |  |

| 174           | IO25RSB0V0      | IO22NPB1V0      |               |                 |                 |  |

| 175           | VCCIB0          | IO21NPB1V0      |               |                 |                 |  |

| 176           | GND             | IO20PSB1V0      |               |                 |                 |  |

| 177           | VCC             | IO19PSB1V0      |               |                 |                 |  |

| 178           | IO24RSB0V0      | IO14NSB0V1      |               |                 |                 |  |

| 179           | IO23RSB0V0      | IO12PDB0V1      |               |                 |                 |  |

| 180           | IO22RSB0V0      | IO12NDB0V1      |               |                 |                 |  |

| 181           | IO21RSB0V0      | VCCIB0          |               |                 |                 |  |

| 182           | IO20RSB0V0      | GND             |               |                 |                 |  |

| 183           | IO19RSB0V0      | VCC             |               |                 |                 |  |

| FG256      |                 |                 |                 |                  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |

| A1         | GND             | GND             | GND             | GND              |  |

| A2         | VCCIB0          | VCCIB0          | VCCIB0          | VCCIB0           |  |

| A3         | GAB0/IO02RSB0V0 | GAA0/IO00RSB0V0 | GAA0/IO01NDB0V0 | GAA0/IO01NDB0V0  |  |

| A4         | GAB1/IO03RSB0V0 | GAA1/IO01RSB0V0 | GAA1/IO01PDB0V0 | GAA1/IO01PDB0V0  |  |

| A5         | GND             | GND             | GND             | GND              |  |

| A6         | IO07RSB0V0      | IO11RSB0V0      | IO10PDB0V1      | IO07PDB0V1       |  |

| A7         | IO10RSB0V0      | IO14RSB0V0      | IO12PDB0V1      | IO13PDB0V2       |  |

| A8         | IO11RSB0V0      | IO15RSB0V0      | IO12NDB0V1      | IO13NDB0V2       |  |

| A9         | IO16RSB0V0      | IO24RSB0V0      | IO22NDB1V0      | IO24NDB1V0       |  |

| A10        | IO17RSB0V0      | IO25RSB0V0      | IO22PDB1V0      | IO24PDB1V0       |  |

| A11        | IO18RSB0V0      | IO26RSB0V0      | IO24NDB1V1      | IO29NDB1V1       |  |

| A12        | GND             | GND             | GND             | GND              |  |

| A13        | GBC0/IO25RSB0V0 | GBA0/IO38RSB0V0 | GBA0/IO28NDB1V1 | GBA0/IO42NDB1V2  |  |

| A14        | GBA0/IO29RSB0V0 | IO32RSB0V0      | IO29NDB1V1      | IO43NDB1V2       |  |

| A15        | VCCIB0          | VCCIB0          | VCCIB1          | VCCIB1           |  |

| A16        | GND             | GND             | GND             | GND              |  |

| B1         | VCOMPLA         | VCOMPLA         | VCOMPLA         | VCOMPLA          |  |

| B2         | VCCPLA          | VCCPLA          | VCCPLA          | VCCPLA           |  |

| B3         | GAA0/IO00RSB0V0 | IO07RSB0V0      | IO00NDB0V0      | IO00NDB0V0       |  |

| B4         | GAA1/IO01RSB0V0 | IO06RSB0V0      | IO00PDB0V0      | IO00PDB0V0       |  |

| B5         | NC              | GAB1/IO03RSB0V0 | GAB1/IO02PPB0V0 | GAB1/IO02PPB0V0  |  |

| B6         | IO06RSB0V0      | IO10RSB0V0      | IO10NDB0V1      | IO07NDB0V1       |  |

| B7         | VCCIB0          | VCCIB0          | VCCIB0          | VCCIB0           |  |

| B8         | IO12RSB0V0      | IO16RSB0V0      | IO18NDB1V0      | IO22NDB1V0       |  |

| B9         | IO13RSB0V0      | IO17RSB0V0      | IO18PDB1V0      | IO22PDB1V0       |  |

| B10        | VCCIB0          | VCCIB0          | VCCIB1          | VCCIB1           |  |

| B11        | IO19RSB0V0      | IO27RSB0V0      | IO24PDB1V1      | IO29PDB1V1       |  |

| B12        | GBB0/IO27RSB0V0 | GBC0/IO34RSB0V0 | GBC0/IO26NPB1V1 | GBC0/IO40NPB1V2  |  |

| B13        | GBC1/IO26RSB0V0 | GBA1/IO39RSB0V0 | GBA1/IO28PDB1V1 | GBA1/IO42PDB1V2  |  |

| B14        | GBA1/IO30RSB0V0 | IO33RSB0V0      | IO29PDB1V1      | IO43PDB1V2       |  |

| B15        | NC              | NC              | VCCPLB          | VCCPLB           |  |

| B16        | NC              | NC              | VCOMPLB         | VCOMPLB          |  |

| C1         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |  |

| C2         | GND             | GND             | GND             | GND              |  |

| C3         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |  |

| C4         | NC              | NC              | VCCIB0          | VCCIB0           |  |

| C5         | VCCIB0          | VCCIB0          | VCCIB0          | VCCIB0           |  |

| C6         | GAC1/IO05RSB0V0 | GAC1/IO05RSB0V0 | GAC1/IO03PDB0V0 | GAC1/IO03PDB0V0  |  |

# **Microsemi**

Package Pin Assignments

|            | FG676            |            | FG676            |                             | FG676  |

|------------|------------------|------------|------------------|-----------------------------|--------|

| Pin Number | AFS1500 Function | Pin Number | AFS1500 Function | Pin Number AFS1500 Function |        |

| A1         | NC               | AA11       | AV2              | AB21                        | PTBASE |

| A2         | GND              | AA12       | GNDA             | AB22                        | GNDNVM |

| A3         | NC               | AA13       | AV3              | AB23                        | VCCNVM |

| A4         | NC               | AA14       | AV6              | AB24                        | VPUMP  |

| A5         | GND              | AA15       | GNDA             | AB25                        | NC     |

| A6         | NC               | AA16       | AV7              | AB26                        | GND    |

| A7         | NC               | AA17       | AV8              | AC1                         | NC     |

| A8         | GND              | AA18       | GNDA             | AC2                         | NC     |

| A9         | IO17NDB0V2       | AA19       | AV9              | AC3                         | NC     |

| A10        | IO17PDB0V2       | AA20       | VCCIB2           | AC4                         | GND    |

| A11        | GND              | AA21       | IO68PPB2V0       | AC5                         | VCCIB4 |

| A12        | IO18NDB0V2       | AA22       | ТСК              | AC6                         | VCCIB4 |

| A13        | IO18PDB0V2       | AA23       | GND              | AC7                         | PCAP   |

| A14        | IO20NDB0V2       | AA24       | IO76PPB2V0       | AC8                         | AG0    |

| A15        | IO20PDB0V2       | AA25       | VCCIB2           | AC9                         | GNDA   |

| A16        | GND              | AA26       | NC               | AC10                        | AG1    |

| A17        | IO21PDB0V2       | AB1        | GND              | AC11                        | AG2    |

| A18        | IO21NDB0V2       | AB2        | NC               | AC12                        | GNDA   |

| A19        | GND              | AB3        | GEC2/IO87PDB4V0  | AC13                        | AG3    |

| A20        | IO39NDB1V2       | AB4        | IO87NDB4V0       | AC14                        | AG6    |

| A21        | IO39PDB1V2       | AB5        | GEA2/IO85PDB4V0  | AC15                        | GNDA   |

| A22        | GND              | AB6        | IO85NDB4V0       | AC16                        | AG7    |

| A23        | NC               | AB7        | NCAP             | AC17                        | AG8    |

| A24        | NC               | AB8        | AC0              | AC18                        | GNDA   |

| A25        | GND              | AB9        | VCC33A           | AC19                        | AG9    |

| A26        | NC               | AB10       | AC1              | AC20                        | VAREF  |

| AA1        | NC               | AB11       | AC2              | AC21                        | VCCIB2 |

| AA2        | VCCIB4           | AB12       | VCC33A           | AC22                        | PTEM   |

| AA3        | IO93PDB4V0       | AB13       | AC3              | AC23                        | GND    |

| AA4        | GND              | AB14       | AC6              | AC24                        | NC     |

| AA5        | IO93NDB4V0       | AB15       | VCC33A           | AC25                        | NC     |

| AA6        | GEB2/IO86PDB4V0  | AB16       | AC7              | AC26                        | NC     |

| AA7        | IO86NDB4V0       | AB17       | AC8              | AD1                         | NC     |

| AA8        | AV0              | AB18       | VCC33A           | AD2                         | NC     |

| AA9        | GNDA             | AB19       | AC9              | AD3                         | GND    |

| AA10       | AV1              | AB20       | ADCGNDREF        | AD4                         | NC     |

Microsemi -Fusion Family of Mixed Signal FPGAs

|            | FG676            |            | FG676            |

|------------|------------------|------------|------------------|

| Pin Number | AFS1500 Function | Pin Number | AFS1500 Function |

| AD5        | IO94NPB4V0       | AE15       | GNDA             |

| AD6        | GND              | AE16       | NC               |

| AD7        | VCC33N           | AE17       | NC               |

| AD8        | AT0              | AE18       | GNDA             |

| AD9        | ATRTN0           | AE19       | NC               |

| AD10       | AT1              | AE20       | NC               |

| AD11       | AT2              | AE21       | NC               |

| AD12       | ATRTN1           | AE22       | NC               |

| AD13       | AT3              | AE23       | NC               |

| AD14       | AT6              | AE24       | NC               |

| AD15       | ATRTN3           | AE25       | GND              |

| AD16       | AT7              | AE26       | GND              |

| AD17       | AT8              | AF1        | NC               |

| AD18       | ATRTN4           | AF2        | GND              |

| AD19       | AT9              | AF3        | NC               |

| AD20       | VCC33A           | AF4        | NC               |

| AD21       | GND              | AF5        | NC               |

| AD22       | IO76NPB2V0       | AF6        | NC               |

| AD23       | NC               | AF7        | NC               |

| AD24       | GND              | AF8        | NC               |

| AD25       | NC               | AF9        | VCC33A           |

| AD26       | NC               | AF10       | NC               |

| AE1        | GND              | AF11       | NC               |

| AE2        | GND              | AF12       | VCC33A           |

| AE3        | NC               | AF13       | NC               |

| AE4        | NC               | AF14       | NC               |

| AE5        | NC               | AF15       | VCC33A           |

| AE6        | NC               | AF16       | NC               |

| AE7        | NC               | AF17       | NC               |

| AE8        | NC               | AF18       | VCC33A           |

| AE9        | GNDA             | AF19       | NC               |

| AE10       | NC               | AF20       | NC               |

| AE11       | NC               | AF21       | NC               |

| AE12       | GNDA             | AF22       | NC               |

| AE13       | NC               | AF23       | NC               |

| AE14       | NC               | AF24       | NC               |

| FG676      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AFS1500 Function |  |  |  |

| AF25       | GND              |  |  |  |

| AF26       | NC               |  |  |  |

| B1         | GND              |  |  |  |

| B2         | GND              |  |  |  |

| B3         | NC               |  |  |  |

| B4         | NC               |  |  |  |

| B5         | NC               |  |  |  |

| B6         | VCCIB0           |  |  |  |

| B7         | NC               |  |  |  |

| B8         | NC               |  |  |  |

| B9         | VCCIB0           |  |  |  |

| B10        | IO15NDB0V2       |  |  |  |

| B11        | IO15PDB0V2       |  |  |  |

| B12        | VCCIB0           |  |  |  |

| B13        | IO19NDB0V2       |  |  |  |

| B14        | IO19PDB0V2       |  |  |  |

| B15        | VCCIB1           |  |  |  |

| B16        | IO25NDB1V0       |  |  |  |

| B17        | IO25PDB1V0       |  |  |  |

| B18        | VCCIB1           |  |  |  |

| B19        | IO33NDB1V1       |  |  |  |

| B20        | IO33PDB1V1       |  |  |  |

| B21        | VCCIB1           |  |  |  |

| B22        | NC               |  |  |  |

| B23        | NC               |  |  |  |

| B24        | NC               |  |  |  |

| B25        | GND              |  |  |  |

| B26        | GND              |  |  |  |

| C1         | NC               |  |  |  |

| C2         | NC               |  |  |  |

| C3         | GND              |  |  |  |

| C4         | NC               |  |  |  |

| C5         | GAA1/IO01PDB0V0  |  |  |  |

| C6         | GAB0/IO02NDB0V0  |  |  |  |

| C7         | GAB1/IO02PDB0V0  |  |  |  |

| C8         | IO07NDB0V1       |  |  |  |

Datasheet Information

| Revision                  | Changes                                                                                                                                                                                                                                                                                                                                                                                    | Page                      |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Revision 2<br>(continued) | A note was added to Figure 2-27 • Real-Time Counter System (not all the signals are shown for the AB macro) stating that the user is only required to instantiate the VRPSM macro if the user wishes to specify PUPO behavior of the voltage regulator to be different from the default, or employ user logic to shut the voltage regulator off (SAR 21773).                               |                           |

|                           | VPUMP was incorrectly represented as VPP in several places. This was corrected to VPUMP in the "Standby and Sleep Mode Circuit Implementation" section and Table 3-8 • AFS1500 Quiescent Supply Current Characteristics through Table 3-11 • AFS090 Quiescent Supply Current Characteristics (21963).                                                                                      | 2-32, 3-10                |

|                           | Additional information was added to the Flash Memory Block "Write Operation" section, including an explanation of the fact that a copy-page operation takes no less than 55 cycles (SAR 26338).                                                                                                                                                                                            | 2-45                      |

|                           | The "FlashROM" section was revised to refer to Figure 2-46 • FlashROM Timing Diagram and Table 2-26 • FlashROM Access Time rather than stating 20 MHz as the maximum FlashROM access clock and 10 ns as the time interval for D0 to become valid or invalid (SAR 22105).                                                                                                                   | 2-53, 2-54                |

|                           | The following figures were deleted (SAR 29991). Reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 34862).                                                                                                                                                |                           |

|                           | Figure 2-55 • Write Access after Write onto Same Address                                                                                                                                                                                                                                                                                                                                   |                           |

|                           | Figure 2-56 • Read Access after Write onto Same Address                                                                                                                                                                                                                                                                                                                                    |                           |

|                           | Figure 2-57 • Write Access after Read onto Same Address                                                                                                                                                                                                                                                                                                                                    |                           |

|                           | The port names in the SRAM "Timing Waveforms", "Timing Characteristics", SRAM tables, Figure 2-55 • RAM Reset. Applicable to both RAM4K9 and RAM512x18., and the FIFO "Timing Characteristics" tables were revised to ensure consistency with the software names (SAR 35753).                                                                                                              | 2-66,                     |

|                           | In several places throughout the datasheet, GNDREF was corrected to ADCGNDREF (SAR 20783):                                                                                                                                                                                                                                                                                                 |                           |

|                           | Figure 2-64 • Analog Block Macro                                                                                                                                                                                                                                                                                                                                                           | 2-77                      |

|                           | Table 2-36 • Analog Block Pin Description                                                                                                                                                                                                                                                                                                                                                  | 2-78                      |

|                           | "ADC Operation" section                                                                                                                                                                                                                                                                                                                                                                    | 2-104                     |

|                           | The following note was added below Figure 2-78 • Timing Diagram for the Temperature Monitor Strobe Signal:                                                                                                                                                                                                                                                                                 | 2-93                      |

|                           | When the IEEE 1149.1 Boundary Scan EXTEST instruction is executed, the AG pad drive strength ceases and becomes a $1\mu A$ sink into the Fusion device. (SAR 24796).                                                                                                                                                                                                                       |                           |

|                           | The "Analog-to-Digital Converter Block" section was extensively revised, reorganizing the information and adding the "ADC Theory of Operation" section and "Acquisition Time or Sample Time Control" section. The "ADC Example" section was reworked and corrected (SAR 20577).                                                                                                            | 2-96                      |

|                           | Table 2-49 • Analog Channel Specifications was modified to include calibrated and uncalibrated values for offset (AFS090 and AFS250) for the external and internal temperature monitors. The "Offset" section was revised accordingly and now references Table 2-49 • Analog Channel Specifications (SARs 22647, 27015).                                                                   |                           |

|                           | The "Intra-Conversion" section and "Injected Conversion" section had definitions incorrectly interchanged and have been corrected. Figure 2-92 • Intra-Conversion Timing Diagram and Figure 2-93 • Injected Conversion Timing Diagram were also incorrectly interchanged and have been replaced correctly. Reference in the figure notes to EQ 10 has been corrected to EQ 23 (SAR 20547). | 2-110,<br>2-113,<br>2-113 |

Fusion Family of Mixed Signal FPGAs

| Revision                    | Changes                                                                                                                                                                                                                                    | Page            |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Advance v0.8<br>(continued) | This sentence was updated in the "No-Glitch MUX (NGMUX)" section to delete GLA:<br>The GLMUXCFG[1:0] configuration bits determine the source of the CLK inputs (i.e., internal signal or GLC).                                             |                 |

|                             | In Table 2-13 • NGMUX Configuration and Selection Table, 10 and 11 were deleted.                                                                                                                                                           | 2-32            |

|                             | The method to enable sleep mode was updated for bit 0 in Table 2-16 • RTC Control/Status Register.                                                                                                                                         | 2-38            |

|                             | S2 was changed to D2 in Figure 2-39 • Read Waveform (Pipe Mode, 32-bit access) for RD[31:0] was updated.                                                                                                                                   | 2-51            |

|                             | The definitions for bits 2 and 3 were updated in Table 2-24 • Page Status Bit Definition.                                                                                                                                                  | 2-52            |

|                             | Figure 2-46 • FlashROM Timing Diagram was updated.                                                                                                                                                                                         | 2-58            |

|                             | Table 2-26 • FlashROM Access Time is new.                                                                                                                                                                                                  | 2-58            |

|                             | Figure 2-55 • Write Access After Write onto Same Address, Figure 2-56 • Read Access After Write onto Same Address, and Figure 2-57 • Write Access After Read onto Same Address are new.                                                    |                 |

|                             | Table 2-31 • RAM4K9 and Table 2-32 • RAM512X18 were updated.                                                                                                                                                                               | 2-71, 2-72      |

|                             | The VAREF and SAMPLE functions were updated in Table 2-36 • Analog Block Pin Description.                                                                                                                                                  | 2-82            |

|                             | The title of Figure 2-72 • Timing Diagram for Current Monitor Strobe was updated to add the word "positive."                                                                                                                               | 2-91            |

|                             | The "Gate Driver" section was updated to give information about the switching rate in High Current Drive mode.                                                                                                                             | 2-94            |

|                             | The "ADC Description" section was updated to include information about the SAMPLE and BUSY signals and the maximum frequencies for SYSCLK and ADCCLK. EQ 2 was updated to add parentheses around the entire expression in the denominator. |                 |

|                             | Table 2-46 $\cdot$ Analog Channel Specifications and Table 2-47 $\cdot$ ADC Characteristics in Direct Input Mode were updated.                                                                                                             | 2-118,<br>2-121 |

|                             | The note was removed from Table 2-55 • Analog Multiplexer Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3).                                                                                                                              | 2-131           |

|                             | Table 2-63 • Internal Temperature Monitor Control Truth Table is new.                                                                                                                                                                      | 2-132           |

|                             | The "Cold-Sparing Support" section was updated to add information about cases where current draw can occur.                                                                                                                                | 2-143           |

|                             | Figure 2-104 • Solution 4 was updated.                                                                                                                                                                                                     | 2-147           |

|                             | Table 2-75 • Fusion Standard I/O Standards—OUT_DRIVE Settings was updated.                                                                                                                                                                 | 2-153           |

|                             | The "GNDA Ground (analog)" section and "GNDAQ Ground (analog quiet)" section were updated to add information about maximum differential voltage.                                                                                           | 2-224           |

|                             | The "V_{AREF} Analog Reference Voltage" section and "VPUMP Programming Supply Voltage" section were updated.                                                                                                                               | 2-226           |

|                             | The "V_{CCPLA/B} PLL Supply Voltage" section was updated to include information about the east and west PLLs.                                                                                                                              | 2-225           |

|                             | The V <sub>COMPLF</sub> pin description was deleted.                                                                                                                                                                                       | N/A             |

|                             | The "Axy Analog Input/Output" section was updated with information about grounding and floating the pin.                                                                                                                                   | 2-226           |

Fusion Family of Mixed Signal FPGAs

| Revision                    | Changes                                                                                                                                                                                  | Page  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance v0.6<br>(continued) | The "Analog-to-Digital Converter Block" section was updated with the following statement:<br>"All results are MSB justified in the ADC."                                                 | 2-99  |