Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                  |

|--------------------------------|------------------------------------------------------------------|

| Product Status                 | Obsolete                                                         |

| Number of LABs/CLBs            | -                                                                |

| Number of Logic Elements/Cells | -                                                                |

| Total RAM Bits                 | 36864                                                            |

| Number of I/O                  | 93                                                               |

| Number of Gates                | 250000                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                                  |

| Mounting Type                  | Surface Mount                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                               |

| Package / Case                 | 208-BFQFP                                                        |

| Supplier Device Package        | 208-PQFP (28x28)                                                 |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs250-2pqg208i |

|                                |                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Global Clocking**

Fusion devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there are on-chip oscillators as well as a comprehensive global clock distribution network.

The integrated RC oscillator generates a 100 MHz clock. It is used internally to provide a known clock source to the flash memory read and write control. It can also be used as a source for the PLLs.

The crystal oscillator supports the following operating modes:

- Crystal (32.768 KHz to 20 MHz)

- Ceramic (500 KHz to 8 MHz)

- RC (32.768 KHz to 4 MHz)

Each VersaTile input and output port has access to nine VersaNets: six main and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via MUXes. The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

## Digital I/Os with Advanced I/O Standards

The Fusion family of FPGAs features a flexible digital I/O structure, supporting a range of voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V). Fusion FPGAs support many different digital I/O standards, both single-ended and differential.

The I/Os are organized into banks, with four or five banks per device. The configuration of these banks determines the I/O standards supported. The banks along the east and west sides of the device support the full range of I/O standards (single-ended and differential). The south bank supports the Analog Quads (analog I/O). In the family's two smaller devices, the north bank supports multiple single-ended digital I/O standards. In the family's larger devices, the north bank is divided into two banks of digital Pro I/Os, supporting a wide variety of single-ended, differential, and voltage-referenced I/O standards.

Each I/O module contains several input, output, and enable registers. These registers allow the implementation of the following applications:

- Single-Data-Rate (SDR) applications

- Double-Data-Rate (DDR) applications—DDR LVDS I/O for chip-to-chip communications

- Fusion banks support LVPECL, LVDS, BLVDS, and M-LVDS with 20 multi-drop points.

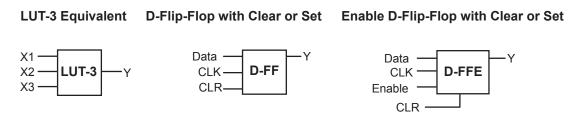

## VersaTiles

The Fusion core consists of VersaTiles, which are also used in the successful ProASIC3 family. The Fusion VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- Latch with clear or set

- D-flip-flop with clear or set and optional enable

Refer to Figure 1-2 for the VersaTile configuration arrangement.

## CCC and PLL Characteristics

## **Timing Characteristics**

## Table 2-12 • Fusion CCC/PLL Specification

| Parameter                                                          | Min.                        | Тур.             | Max.                         | Unit |

|--------------------------------------------------------------------|-----------------------------|------------------|------------------------------|------|

| Clock Conditioning Circuitry Input Frequency fIN_CCC               | 1.5                         |                  | 350                          | MHz  |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub> | 0.75                        |                  | 350                          | MHz  |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>      |                             | 160 <sup>3</sup> |                              | ps   |

| Number of Programmable Values in Each Programmable Delay Block     |                             |                  | 32                           |      |

| Input Period Jitter                                                |                             |                  | 1.5                          | ns   |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | Max Pea                     | k-to-Peak P      | eriod Jitter                 |      |

|                                                                    | 1 Global<br>Network<br>Used |                  | 3 Global<br>Networks<br>Used |      |

| 0.75 MHz to 24 MHz                                                 | 1.00%                       |                  | 1.00%                        |      |

| 24 MHz to 100 MHz                                                  | 1.50%                       |                  | 1.50%                        |      |

| 100 MHz to 250 MHz                                                 | 2.25%                       |                  | 2.25%                        |      |

| 250 MHz to 350 MHz                                                 | 3.50%                       |                  | 3.50%                        |      |

| Acquisition Time LockControl = 0                                   |                             |                  | 300                          | μs   |

| LockControl = 1                                                    |                             |                  | 6.0                          | ms   |

| Tracking Jitter <sup>4</sup> LockControl = 0                       |                             |                  | 1.6                          | ns   |

| LockControl = 1                                                    |                             |                  | 0.8                          | ns   |

| Output Duty Cycle                                                  | 48.5                        |                  | 51.5                         | %    |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>         | 0.6                         |                  | 5.56                         | ns   |

| Delay Range in Block: Programmable Delay 2 <sup>1, 2</sup>         | 0.025                       |                  | 5.56                         | ns   |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                  |                             | 2.2              |                              | ns   |

Notes:

1. This delay is a function of voltage and temperature. See Table 3-7 on page 3-9 for deratings.

2.  $T_J = 25^{\circ}C$ , VCC = 1.5 V

3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help associated with the core for more information.

4. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by period jitter parameter. Data operations are performed in widths of 1 to 4 bytes. A write to a location in a page that is not already in the Page Buffer will cause the page to be read from the FB Array and stored in the Page Buffer. The block that was addressed during the write will be put into the Block Buffer, and the data written by WD will overwrite the data in the Block Buffer. After the data is written to the Block Buffer, the Block Buffer is then written to the Page Buffer to keep both buffers in sync. Subsequent writes to the same block will overwrite the Block Buffer and the Page Buffer. A write to another block in the page will cause the addressed block to be loaded from the Page Buffer, and the write will be performed as described previously.

The data width can be selected dynamically via the DATAWIDTH input bus. The truth table for the data width settings is detailed in Table 2-21. The minimum resolvable address is one 8-bit byte. For data widths greater than 8 bits, the corresponding address bits are ignored—when DATAWIDTH = 0 (2 bytes), ADDR[0] is ignored, and when DATAWIDTH = '10' or '11' (4 bytes), ADDR[1:0] are ignored. Data pins are LSB-oriented and unused WD data pins must be grounded.

### Table 2-21 • Data Width Settings

| DATAWIDTH[1:0] | Data Width     |

|----------------|----------------|

| 00             | 1 byte [7:0]   |

| 01             | 2 byte [15:0]  |

| 10, 11         | 4 bytes [31:0] |

## Flash Memory Block Protection

## Page Loss Protection

When the PAGELOSSPROTECT pin is set to logic 1, it prevents writes to any page other than the current page in the Page Buffer until the page is either discarded or programmed.

A write to another page while the current page is Page Loss Protected will return a STATUS of '11'.

## **Overwrite Protection**

Any page that is Overwrite Protected will result in the STATUS being set to '01' when an attempt is made to either write, program, or erase it. To set the Overwrite Protection state for a page, set the OVERWRITEPROTECT pin when a Program operation is undertaken. To clear the Overwrite Protect state for a given page, an Unprotect Page operation must be performed on the page, and then the page must be programmed with the OVERWRITEPROTECT pin cleared to save the new page.

## LOCKREQUEST

The LOCKREQUEST signal is used to give the user interface control over simultaneous access of the FB from both the User and JTAG interfaces. When LOCKREQUEST is asserted, the JTAG interface will hold off any access attempts until LOCKREQUEST is deasserted.

## Flash Memory Block Operations

## FB Operation Priority

The FB provides for priority of operations when multiple actions are requested simultaneously. Table 2-22 shows the priority order (priority 0 is the highest).

| Operation             | Priority |

|-----------------------|----------|

| System Initialization | 0        |

| FB Reset              | 1        |

| Read                  | 2        |

| Write                 | 3        |

| Erase Page            | 4        |

| Program               | 5        |

| Unprotect Page        | 6        |

| Discard Page          | 7        |

## DINA and DINB

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 2-29).

## **DOUTA and DOUTB**

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 2-29). The output data on unused pins is undefined.

Table 2-29 • Unused/Used Input and Output Data Pins for Various Supported Bus Widths

| D×W   | DINx/DOUTx |       |  |  |  |  |

|-------|------------|-------|--|--|--|--|

| D~W   | Unused     | Used  |  |  |  |  |

| 4k×1  | [8:1]      | [0]   |  |  |  |  |

| 2k×2  | [8:2]      | [1:0] |  |  |  |  |

| 1k×4  | [8:4]      | [3:0] |  |  |  |  |

| 512×9 | None       | [8:0] |  |  |  |  |

Note: The "x" in DINx and DOUTx implies A or B.

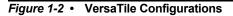

The rate at which the gate voltage of the external MOSFET slews is determined by the current,  $I_g$ , sourced or sunk by the AG pin and the gate-to-source capacitance,  $C_{GS}$ , of the external MOSFET. As an approximation, the slew rate is given by EQ 6.

$$dv/dt = I_g / C_{GS}$$

EQ 6

$C_{GS}$  is not a fixed capacitance but, depending on the circuitry connected to its drain terminal, can vary significantly during the course of a turn-on or turn-off transient. Thus, EQ 6 on page 2-91 can only be used for a first-order estimate of the switching speed of the external MOSFET.

Figure 2-75 • Gate Driver Example

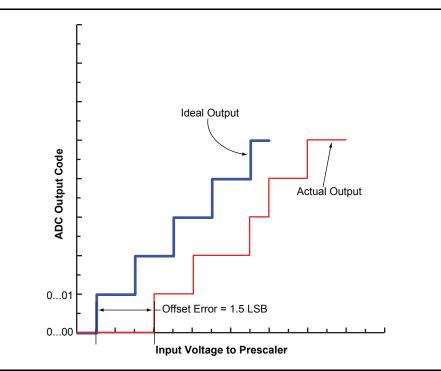

### **Offset Error**

Offset error indicates how well the actual transfer function matches the ideal transfer function at a single point. For an ideal ADC, the first transition occurs at 0.5 LSB above zero. The offset voltage is measured by applying an analog input such that the ADC outputs all zeroes and increases until the first transition occurs (Figure 2-86).

Figure 2-86 • Offset Error

#### Resolution

ADC resolution is the number of bits used to represent an analog input signal. To more accurately replicate the analog signal, resolution needs to be increased.

## Sampling Rate

Sampling rate or sample frequency, specified in samples per second (sps), is the rate at which an ADC acquires (samples) the analog input.

## SNR – Signal-to-Noise Ratio

SNR is the ratio of the amplitude of the desired signal to the amplitude of the noise signals at a given point in time. For a waveform perfectly reconstructed from digital samples, the theoretical maximum SNR (EQ 14) is the ratio of the full-scale analog input (RMS value) to the RMS quantization error (residual error). The ideal, theoretical minimum ADC noise is caused by quantization error only and results directly from the ADC's resolution (N bits):

$$SNR_{dB[MAX]} = 6.02_{dB} \times N + 1.76_{dB}$$

EQ 14

## SINAD – Signal-to-Noise and Distortion

SINAD is the ratio of the rms amplitude to the mean value of the root-sum-square of the all other spectral components, including harmonics, but excluding DC. SINAD is a good indication of the overall dynamic performance of an ADC because it includes all components which make up noise and distortion.

## **Total Harmonic Distortion**

THD measures the distortion content of a signal, and is specified in decibels relative to the carrier (dBc). THD is the ratio of the RMS sum of the selected harmonics of the input signal to the fundamental itself. Only harmonics within the Nyquist limit are included in the measurement.

## ADC Interface Timing

## Table 2-48 • ADC Interface Timing Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                | Description                                    | -2     | -1     | Std.   | Units |

|--------------------------|------------------------------------------------|--------|--------|--------|-------|

| t <sub>SUMODE</sub>      | Mode Pin Setup Time                            | 0.56   | 0.64   | 0.75   | ns    |

| t <sub>HDMODE</sub>      | Mode Pin Hold Time                             | 0.26   | 0.29   | 0.34   | ns    |

| t <sub>SUTVC</sub>       | Clock Divide Control (TVC) Setup Time          | 0.68   | 0.77   | 0.90   | ns    |

| t <sub>HDTVC</sub>       | Clock Divide Control (TVC) Hold Time           | 0.32   | 0.36   | 0.43   | ns    |

| t <sub>SUSTC</sub>       | Sample Time Control (STC) Setup Time           | 1.58   | 1.79   | 2.11   | ns    |

| t <sub>HDSTC</sub>       | Sample Time Control (STC) Hold Time            | 1.27   | 1.45   | 1.71   | ns    |

| t <sub>SUVAREFSEL</sub>  | Voltage Reference Select (VAREFSEL) Setup Time | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>HDVAREFSEL</sub>  | Voltage Reference Select (VAREFSEL) Hold Time  | 0.67   | 0.76   | 0.89   | ns    |

| t <sub>SUCHNUM</sub>     | Channel Select (CHNUMBER) Setup Time           | 0.90   | 1.03   | 1.21   | ns    |

| t <sub>HDCHNUM</sub>     | Channel Select (CHNUMBER) Hold Time            | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>SUADCSTART</sub>  | Start of Conversion (ADCSTART) Setup Time      | 0.75   | 0.85   | 1.00   | ns    |

| t <sub>HDADCSTART</sub>  | Start of Conversion (ADCSTART) Hold Time       | 0.43   | 0.49   | 0.57   | ns    |

| t <sub>CK2QBUSY</sub>    | Busy Clock-to-Q                                | 1.33   | 1.51   | 1.78   | ns    |

| t <sub>CK2QCAL</sub>     | Power-Up Calibration Clock-to-Q                | 0.63   | 0.71   | 0.84   | ns    |

| t <sub>CK2QVAL</sub>     | Valid Conversion Result Clock-to-Q             | 3.12   | 3.55   | 4.17   | ns    |

| t <sub>CK2QSAMPLE</sub>  | Sample Clock-to-Q                              | 0.22   | 0.25   | 0.30   | ns    |

| t <sub>CK2QRESULT</sub>  | Conversion Result Clock-to-Q                   | 2.53   | 2.89   | 3.39   | ns    |

| t <sub>CLR2QBUSY</sub>   | Busy Clear-to-Q                                | 2.06   | 2.35   | 2.76   | ns    |

| t <sub>CLR2QCAL</sub>    | Power-Up Calibration Clear-to-Q                | 2.15   | 2.45   | 2.88   | ns    |

| t <sub>CLR2QVAL</sub>    | Valid Conversion Result Clear-to-Q             | 2.41   | 2.74   | 3.22   | ns    |

| t <sub>CLR2QSAMPLE</sub> | Sample Clear-to-Q                              | 2.17   | 2.48   | 2.91   | ns    |

| t <sub>CLR2QRESULT</sub> | Conversion result Clear-to-Q                   | 2.25   | 2.56   | 3.01   | ns    |

| t <sub>RECCLR</sub>      | Recovery Time of Clear                         | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>REMCLR</sub>      | Removal Time of Clear                          | 0.63   | 0.72   | 0.84   | ns    |

| t <sub>MPWSYSCLK</sub>   | Clock Minimum Pulse Width for the ADC          | 4.00   | 4.00   | 4.00   | ns    |

| t <sub>FMAXSYSCLK</sub>  | Clock Maximum Frequency for the ADC            | 100.00 | 100.00 | 100.00 | MHz   |

# Table 2-49 • Analog Channel Specifications (continued)Commercial Temperature Range Conditions, TJ = 85°C (unless noted otherwise),Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter                                      | Description                    | Condition                                                     | Min. | Тур. | Max. | Units |  |

|------------------------------------------------|--------------------------------|---------------------------------------------------------------|------|------|------|-------|--|

| Temperature Mo                                 | onitor Using Analog Pad        | AT                                                            |      |      | 1    |       |  |

| External                                       | Resolution                     | 8-bit ADC                                                     |      |      | 4    | °C    |  |

| Temperature<br>Monitor                         |                                | 10-bit ADC                                                    |      |      | 1    | °C    |  |

| (external diode                                |                                | 12-bit ADC                                                    |      | C    | ).25 | °C    |  |

| 2N3904,<br>T <sub>J</sub> = 25°C) <sup>4</sup> | Systematic Offset <sup>5</sup> | AFS090, AFS250, AFS600,<br>AFS1500, uncalibrated <sup>7</sup> |      | 5    |      |       |  |

|                                                |                                | AFS090, AFS250, AFS600,<br>AFS1500, calibrated <sup>7</sup>   |      | ±5   |      |       |  |

|                                                | Accuracy                       |                                                               |      | ±3   | ±5   | °C    |  |

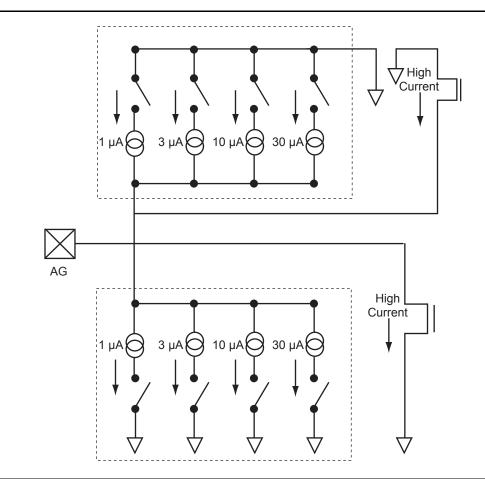

|                                                | External Sensor Source         | High level, TMSTBx = 0                                        |      | 10   |      | μA    |  |

|                                                | Current                        | Low level, TMSTBx = 1                                         |      | 100  |      | μA    |  |

|                                                | Max Capacitance on AT pad      |                                                               |      |      | 1.3  | nF    |  |

| Internal                                       | Resolution                     | 8-bit ADC                                                     | 4    |      |      | °C    |  |

| Temperature<br>Monitor                         |                                | 10-bit ADC                                                    | 1    |      |      | °C    |  |

| Wornton                                        |                                | 12-bit ADC                                                    | 0.25 |      |      | °C    |  |

|                                                | Systematic Offset <sup>5</sup> | AFS090 <sup>7</sup>                                           |      | 5    |      |       |  |

|                                                |                                | AFS250, AFS600, AFS1500 <sup>7</sup>                          |      | 11   |      |       |  |

|                                                | Accuracy                       |                                                               |      | ±3   | ±5   | °C    |  |

| t <sub>TMSHI</sub>                             | Strobe High time               |                                                               | 10   |      | 105  | μs    |  |

| t <sub>TMSLO</sub>                             | Strobe Low time                |                                                               | 5    |      |      | μs    |  |

| t <sub>TMSSET</sub>                            | Settling time                  |                                                               | 5    |      |      | μs    |  |

Notes:

1. VRSM is the maximum voltage drop across the current sense resistor.

2. Analog inputs used as digital inputs can tolerate the same voltage limits as the corresponding analog pad. There is no reliability concern on digital inputs as long as VIND does not exceed these limits.

3. VIND is limited to VCC33A + 0.2 to allow reaching 10 MHz input frequency.

- 4. An averaging of 1,024 samples (LPF setting in Analog System Builder) is required and the maximum capacitance allowed across the AT pins is 500 pF.

- 5. The temperature offset is a fixed positive value.

- 6. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

- 7. When using SmartGen Analog System Builder, CalibIP is required to obtain specified offset. For further details on CalibIP, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

## User I/Os

## Introduction

Fusion devices feature a flexible I/O structure, supporting a range of mixed voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V) through a bank-selectable voltage. Table 2-68, Table 2-69, Table 2-70, and Table 2-71 on page 2-135 show the voltages and the compatible I/O standards. I/Os provide programmable slew rates, drive strengths, weak pull-up, and weak pull-down circuits. 3.3 V PCI and 3.3 V PCI-X are 5 V–tolerant. See the "5 V Input Tolerance" section on page 2-144 for possible implementations of 5 V tolerance.

All I/Os are in a known state during power-up, and any power-up sequence is allowed without current impact. Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section on page 3-5 for more information. In low power standby or sleep mode (VCC is OFF, VCC33A is ON, VCCI is ON) or when the resource is not used, digital inputs are tristated, digital outputs are tristated, and digital bibufs (input/output) are tristated.

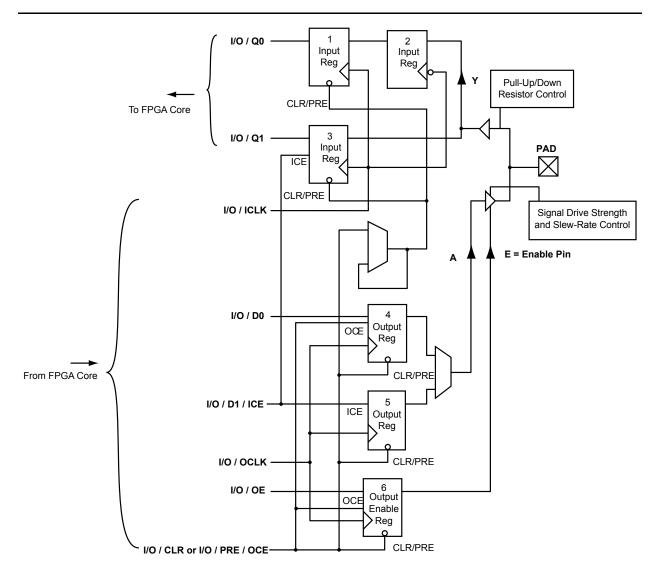

I/O Tile

The Fusion I/O tile provides a flexible, programmable structure for implementing a large number of I/O standards. In addition, the registers available in the I/O tile in selected I/O banks can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 2-99 on page 2-133). The registers can also be used to support the JESD-79C DDR standard within the I/O structure (see the "Double Data Rate (DDR) Support" section on page 2-139 for more information).

As depicted in Figure 2-100 on page 2-138, all I/O registers share one CLR port. The output register and output enable register share one CLK port. Refer to the "I/O Registers" section on page 2-138 for more information.

## I/O Banks and I/O Standards Compatibility

The digital I/Os are grouped into I/O voltage banks. There are three digital I/O banks on the AFS090 and AFS250 devices and four digital I/O banks on the AFS600 and AFS1500 devices. Figure 2-113 on page 2-158 and Figure 2-114 on page 2-159 show the bank configuration by device. The north side of the I/O in the AFS600 and AFS1500 devices comprises two banks of Pro I/Os. The Pro I/Os support a wide number of voltage-referenced I/O standards in addition to the multitude of single-ended and differential I/O standards common throughout all Microsemi digital I/Os. Each I/O voltage bank has dedicated I/O supply and ground voltages (VCCI/GNDQ for input buffers and VCCI/GND for output buffers). Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank. Table 2-69 and Table 2-70 on page 2-134 show the required voltage compatibility values for each of these voltages.

For more information about I/O and global assignments to I/O banks, refer to the specific pin table of the device in the "Package Pin Assignments" on page 4-1 and the "User I/O Naming Convention" section on page 2-158.

Each Pro I/O bank is divided into minibanks. Any user I/O in a VREF minibank (a minibank is the region of scope of a VREF pin) can be configured as a VREF pin (Figure 2-99 on page 2-133). Only one VREF pin is needed to control the entire VREF minibank. The location and scope of the VREF minibanks can be determined by the I/O name. For details, see the "User I/O Naming Convention" section on page 2-158.

Table 2-70 on page 2-134 shows the I/O standards supported by Fusion devices and the corresponding voltage levels.

I/O standards are compatible if the following are true:

- Their VCCI values are identical.

- If both of the standards need a VREF, their VREF values must be identical (Pro I/O only).

## **I/O Registers**

Each I/O module contains several input, output, and enable registers. Refer to Figure 2-100 for a simplified representation of the I/O block.

The number of input registers is selected by a set of switches (not shown in Figure 2-100) between registers to implement single or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user.

A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy some rules.

Note: Fusion I/Os have registers to support DDR functionality (see the "Double Data Rate (DDR) Support" section on page 2-139 for more information).

Figure 2-100 • I/O Block Logical Representation

## **5 V Input Tolerance**

I/Os can support 5 V input tolerance when LVTTL 3.3 V, LVCMOS 3.3 V, LVCMOS 2.5 V / 5 V, and LVCMOS 2.5 V configurations are used (see Table 2-77 on page 2-147 for more details). There are four recommended solutions (see Figure 2-103 to Figure 2-106 on page 2-146 for details of board and macro setups) to achieve 5 V receiver tolerance. All the solutions meet a common requirement of limiting the voltage at the input to 3.6 V or less. In fact, the I/O absolute maximum voltage rating is 3.6 V, and any voltage above 3.6 V may cause long-term gate oxide failures.

## Solution 1

The board-level design needs to ensure that the reflected waveform at the pad does not exceed the limits provided in Table 3-4 on page 3-4. This is a long-term reliability requirement.

This scheme will also work for a 3.3 V PCI / PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the two external resistors, as explained below. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

The following are some examples of possible resistor values (based on a simplified simulation model with no line effects and 10  $\Omega$  transmitter output resistance, where Rtx\_out\_high = (VCCI – VOH) / IOH, Rtx\_out\_low = VOL / IOL).

Example 1 (high speed, high current):

Rtx\_out\_high = Rtx\_out\_low = 10  $\Omega$

R1 = 36  $\Omega$  (±5%), P(r1)min = 0.069  $\Omega$

R2 = 82  $\Omega$  (±5%), P(r2)min = 0.158  $\Omega$

Imax\_tx = 5.5 V / (82 \* 0.95 + 36 \* 0.95 + 10) = 45.04 mA

t<sub>RISE</sub> = t<sub>FALL</sub> = 0.85 ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

t<sub>RISE</sub> = t<sub>FALL</sub> = 4 ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

Example 2 (low-medium speed, medium current):

Rtx\_out\_high = Rtx\_out\_low = 10  $\Omega$

R1 = 220 Ω (±5%), P(r1)min = 0.018 Ω

R2 = 390  $\Omega$  (±5%), P(r2)min = 0.032  $\Omega$

Imax\_tx = 5.5 V / (220 \* 0.95 + 390 \* 0.95 + 10) = 9.17 mA

t<sub>RISE</sub> = t<sub>FALL</sub> = 4 ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

t<sub>RISE</sub> = t<sub>FALL</sub> = 20 ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

Other values of resistors are also allowed as long as the resistors are sized appropriately to limit the voltage at the receiving end to 2.5 V < Vin(rx) < 3.6 V when the transmitter sends a logic 1. This range of Vin\_dc(rx) must be assured for any combination of transmitter supply (5 V ± 0.5 V), transmitter output resistance, and board resistor tolerances.

## Table 2-107 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 7.66            | 0.04             | 1.20            | 0.43              | 7.80            | 6.59            | 2.65            | 2.61            | 10.03            | 8.82             | ns    |

|                   | -1             | 0.56              | 6.51            | 0.04             | 1.02            | 0.36              | 6.63            | 5.60            | 2.25            | 2.22            | 8.54             | 7.51             | ns    |

|                   | -2             | 0.49              | 5.72            | 0.03             | 0.90            | 0.32              | 5.82            | 4.92            | 1.98            | 1.95            | 7.49             | 6.59             | ns    |

| 8 mA              | Std.           | 0.66              | 4.91            | 0.04             | 1.20            | 0.43              | 5.00            | 4.07            | 2.99            | 3.20            | 7.23             | 6.31             | ns    |

|                   | -1             | 0.56              | 4.17            | 0.04             | 1.02            | 0.36              | 4.25            | 3.46            | 2.54            | 2.73            | 6.15             | 5.36             | ns    |

|                   | -2             | 0.49              | 3.66            | 0.03             | 0.90            | 0.32              | 3.73            | 3.04            | 2.23            | 2.39            | 5.40             | 4.71             | ns    |

| 12 mA             | Std.           | 0.66              | 3.53            | 0.04             | 1.20            | 0.43              | 3.60            | 2.82            | 3.21            | 3.58            | 5.83             | 5.06             | ns    |

|                   | -1             | 0.56              | 3.00            | 0.04             | 1.02            | 0.36              | 3.06            | 2.40            | 2.73            | 3.05            | 4.96             | 4.30             | ns    |

|                   | -2             | 0.49              | 2.64            | 0.03             | 0.90            | 0.32              | 2.69            | 2.11            | 2.40            | 2.68            | 4.36             | 3.78             | ns    |

| 16 mA             | Std.           | 0.66              | 3.33            | 0.04             | 1.20            | 0.43              | 3.39            | 2.56            | 3.26            | 3.68            | 5.63             | 4.80             | ns    |

|                   | -1             | 0.56              | 2.83            | 0.04             | 1.02            | 0.36              | 2.89            | 2.18            | 2.77            | 3.13            | 4.79             | 4.08             | ns    |

|                   | -2             | 0.49              | 2.49            | 0.03             | 0.90            | 0.32              | 2.53            | 1.91            | 2.44            | 2.75            | 4.20             | 3.58             | ns    |

| 24 mA             | Std.           | 0.66              | 3.08            | 0.04             | 1.20            | 0.43              | 3.13            | 2.12            | 3.32            | 4.06            | 5.37             | 4.35             | ns    |

|                   | -1             | 0.56              | 2.62            | 0.04             | 1.02            | 0.36              | 2.66            | 1.80            | 2.83            | 3.45            | 4.57             | 3.70             | ns    |

|                   | -2             | 0.49              | 2.30            | 0.03             | 0.90            | 0.32              | 2.34            | 1.58            | 2.48            | 3.03            | 4.01             | 3.25             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## Table 2-108 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 9.46            | 0.04             | 1.00            | 0.43              | 9.64            | 8.54            | 2.07            | 2.04            | ns    |

|                   | -1             | 0.56              | 8.05            | 0.04             | 0.85            | 0.36              | 8.20            | 7.27            | 1.76            | 1.73            | ns    |

|                   | -2             | 0.49              | 7.07            | 0.03             | 0.75            | 0.32              | 7.20            | 6.38            | 1.55            | 1.52            | ns    |

| 4 mA              | Std.           | 0.66              | 9.46            | 0.04             | 1.00            | 0.43              | 9.64            | 8.54            | 2.07            | 2.04            | ns    |

|                   | -1             | 0.56              | 8.05            | 0.04             | 0.85            | 0.36              | 8.20            | 7.27            | 1.76            | 1.73            | ns    |

|                   | -2             | 0.49              | 7.07            | 0.03             | 0.75            | 0.32              | 7.20            | 6.38            | 1.55            | 1.52            | ns    |

| 6 mA              | Std.           | 0.66              | 6.57            | 0.04             | 1.00            | 0.43              | 6.69            | 5.98            | 2.40            | 2.57            | ns    |

|                   | -1             | 0.56              | 5.59            | 0.04             | 0.85            | 0.36              | 5.69            | 5.09            | 2.04            | 2.19            | ns    |

|                   | -2             | 0.49              | 4.91            | 0.03             | 0.75            | 0.32              | 5.00            | 4.47            | 1.79            | 1.92            | ns    |

| 8 mA              | Std.           | 0.66              | 6.57            | 0.04             | 1.00            | 0.43              | 6.69            | 5.98            | 2.40            | 2.57            | ns    |

|                   | -1             | 0.56              | 5.59            | 0.04             | 0.85            | 0.36              | 5.69            | 5.09            | 2.04            | 2.19            | ns    |

|                   | -2             | 0.49              | 4.91            | 0.03             | 0.75            | 0.32              | 5.00            | 4.47            | 1.79            | 1.92            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### VCC Core Supply Voltage

Supply voltage to the FPGA core, nominally 1.5 V. VCC is also required for powering the JTAG state machine, in addition to VJTAG. Even when a Fusion device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the Fusion device.

#### VCCIBx I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are either four (AFS090 and AFS250) or five (AFS600 and AFS1500) I/O banks on the Fusion devices plus a dedicated VJTAG bank.

Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCI pins tied to GND.

#### VCCPLA/B PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V, where A and B refer to the PLL. AFS090 and AFS250 each have a single PLL. The AFS600 and AFS1500 devices each have two PLLs. Microsemi recommends tying VCCPLX to VCC and using proper filtering circuits to decouple VCC noise from PLL.

If unused, VCCPLA/B should be tied to GND.

#### VCOMPLA/B Ground for West and East PLL

VCOMPLA is the ground of the west PLL (CCC location F) and VCOMPLB is the ground of the east PLL (CCC location C).

#### VJTAG JTAG Supply Voltage

Fusion devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a Fusion device is in a JTAG chain of interconnected boards and it is desired to power down the board containing the Fusion device, this may be done provided both VJTAG and VCC to the Fusion part remain powered; otherwise, JTAG signals will not be able to transition the Fusion device, even in bypass mode.

#### VPUMP Programming Supply Voltage

Fusion devices support single-voltage ISP programming of the configuration flash and FlashROM. For programming, VPUMP should be in the 3.3 V +/-5% range. During normal device operation, VPUMP can be left floating or can be tied to any voltage between 0 V and 3.6 V.

When the VPUMP pin is tied to ground, it shuts off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

## **IEEE 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/Os" section on page 2-132 for more details.

## **Timing Characteristics**

## Table 2-186 • JTAG 1532

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | -2    | -1    | Std.  | Units |

|----------------------|-----------------------------|-------|-------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 0.50  | 0.57  | 0.67  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 1.00  | 1.13  | 1.33  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 0.50  | 0.57  | 0.67  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 1.00  | 1.13  | 1.33  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 6.00  | 6.80  | 8.00  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 20.00 | 22.67 | 26.67 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 25.00 | 22.00 | 19.00 | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.20  | 0.23  | 0.27  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | TBD   | TBD   | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## 3 – DC and Power Characteristics

## **General Specifications**

## **Operating Conditions**

Stresses beyond those listed in Table 3-1 may cause permanent damage to the device.

Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating ranges specified in Table 3-2 on page 3-3.

| Symbol   | Parameter                                  | Commercial                      | Industrial                                                                                  | Units |  |  |

|----------|--------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------|-------|--|--|

| VCC      | DC core supply voltage                     | -0.3 to 1.65                    | -0.3 to 1.65                                                                                | V     |  |  |

| VJTAG    | JTAG DC voltage                            | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

| VPUMP    | Programming voltage                        | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

| VCCPLL   | Analog power supply (PLL)                  | -0.3 to 1.65                    | -0.3 to 1.65                                                                                | V     |  |  |

| VCCI     | DC I/O output buffer supply voltage        | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

| VI       | I/O input voltage <sup>1</sup>             | enabled)<br>–0.3 V to (VCCI + 1 | –0.3 V to (VCCI + 1 V) or 3.6 V, whichever voltage is lower (when I/O hot-insertion mode is |       |  |  |

| VCC33A   | +3.3 V power supply                        | -0.3 to 3.75 <sup>2</sup>       | -0.3 to 3.75 <sup>2</sup>                                                                   | V     |  |  |

| VCC33PMP | +3.3 V power supply                        | -0.3 to 3.75 <sup>2</sup>       | -0.3 to 3.75 <sup>2</sup>                                                                   | V     |  |  |

| VAREF    | Voltage reference for ADC                  | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

| VCC15A   | Digital power supply for the analog system | -0.3 to 1.65                    | -0.3 to 1.65                                                                                | V     |  |  |

| VCCNVM   | Embedded flash power supply                | -0.3 to 1.65                    | -0.3 to 1.65                                                                                | V     |  |  |

| VCCOSC   | Oscillator power supply                    | -0.3 to 3.75                    | -0.3 to 3.75                                                                                | V     |  |  |

### Table 3-1 • Absolute Maximum Ratings

Notes:

1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-4.

2. Analog data not valid beyond 3.65 V.

3. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

4. For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.

DC and Power Characteristics

| Parameter | Description                    | Conditions                                                            | Temp.                  | Min. | Тур. | Max. | Unit |

|-----------|--------------------------------|-----------------------------------------------------------------------|------------------------|------|------|------|------|

| IJTAG     | JTAG I/O quiescent<br>current  | Operational standby <sup>4</sup> ,<br>VJTAG = 3.63 V                  | T <sub>J</sub> = 25°C  |      | 80   | 100  | μA   |

|           |                                |                                                                       | T <sub>J</sub> = 85°C  |      | 80   | 100  | μA   |

|           |                                |                                                                       | T <sub>J</sub> = 100°C |      | 80   | 100  | μA   |

|           |                                | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VJTAG = 0 V |                        |      | 0    | 0    | μA   |

| IPP       | Programming supply current     | Non-programming mode,<br>VPUMP = 3.63 V                               | T <sub>J</sub> = 25°C  |      | 39   | 80   | μA   |

|           |                                |                                                                       | T <sub>J</sub> = 85°C  |      | 40   | 80   | μA   |

|           |                                |                                                                       | T <sub>J</sub> = 100°C |      | 40   | 80   | μA   |

|           |                                | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VPUMP = 0 V |                        |      | 0    | 0    | μA   |

| ICCNVM    | Embedded NVM<br>current        | Reset asserted, V <sub>CCNVM</sub> = 1.575 V                          | T <sub>J</sub> = 25°C  |      | 50   | 150  | μA   |

|           |                                |                                                                       | T <sub>J</sub> =85°C   |      | 50   | 150  | μA   |

|           |                                |                                                                       | T <sub>J</sub> = 100°C |      | 50   | 150  | μA   |

| ICCPLL    | 1.5 V PLL quiescent<br>current | Operational standby<br>, VCCPLL = 1.575 V                             | T <sub>J</sub> = 25°C  |      | 130  | 200  | μA   |

|           |                                |                                                                       | T <sub>J</sub> = 85°C  |      | 130  | 200  | μA   |

|           |                                |                                                                       | T <sub>J</sub> = 100°C |      | 130  | 200  | μA   |

| Table 3-8 | • AFS1500 Quiescent Supply Current Characteristics (continued) |

|-----------|----------------------------------------------------------------|

|-----------|----------------------------------------------------------------|

Notes:

1. ICC is the 1.5 V power supplies, ICC and ICC15A.

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

DC and Power Characteristics

| Table 3-10 • AFS250 Quiescent Supply Current | Characteristics (continued) |

|----------------------------------------------|-----------------------------|

|----------------------------------------------|-----------------------------|

| Parameter | Description                 | Conditions                                                            | Temp.                  | Min | Тур | Мах | Unit |

|-----------|-----------------------------|-----------------------------------------------------------------------|------------------------|-----|-----|-----|------|

| IPP       | Programming supply current  | Non-programming mode,<br>VPUMP = 3.63 V                               | T <sub>J</sub> = 25°C  |     | 37  | 80  | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 85°C  |     | 37  | 80  | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 80  | 100 | μA   |

|           |                             | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VPUMP = 0 V |                        |     | 0   | 0   | μA   |

| ICCNVM    | Embedded NVM current        | Reset asserted,<br>VCCNVM = 1.575 V                                   | T <sub>J</sub> = 25°C  |     | 10  | 40  | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 85°C  |     | 14  | 40  | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 14  | 40  | μA   |

| ICCPLL    | 1.5 V PLL quiescent current | Operational standby,<br>VCCPLL = 1.575 V                              | T <sub>J</sub> = 25°C  |     | 65  | 100 | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 85°C  |     | 65  | 100 | μA   |

|           |                             |                                                                       | T <sub>J</sub> = 100°C |     | 65  | 100 | μA   |

Notes:

- 1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, and ICCI2.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTA G = VPUMP = 0 V.

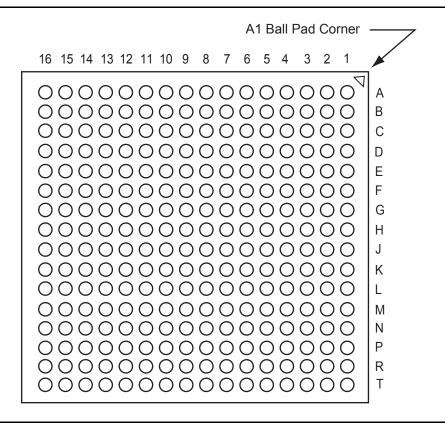

## FG256

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

|            |                 | FG256           |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| K9         | VCC             | VCC             | VCC             | VCC              |

| K10        | GND             | GND             | GND             | GND              |

| K11        | NC              | GDC2/IO57PPB1V0 | GDC2/IO57PPB2V0 | GDC2/IO84PPB2V0  |

| K12        | GND             | GND             | GND             | GND              |

| K13        | NC              | GDA0/IO54NDB1V0 | GDA0/IO54NDB2V0 | GDA0/IO81NDB2V0  |

| K14        | NC              | GDA2/IO55PPB1V0 | GDA2/IO55PPB2V0 | GDA2/IO82PPB2V0  |

| K15        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| K16        | NC              | GDB1/IO53PPB1V0 | GDB1/IO53PPB2V0 | GDB1/IO80PPB2V0  |

| L1         | NC              | GEC1/IO63PDB3V0 | GEC1/IO63PDB4V0 | GEC1/IO90PDB4V0  |

| L2         | NC              | GEC0/IO63NDB3V0 | GEC0/IO63NDB4V0 | GEC0/IO90NDB4V0  |

| L3         | NC              | GEB1/IO62PDB3V0 | GEB1/IO62PDB4V0 | GEB1/IO89PDB4V0  |

| L4         | NC              | GEB0/IO62NDB3V0 | GEB0/IO62NDB4V0 | GEB0/IO89NDB4V0  |

| L5         | NC              | IO60NDB3V0      | IO60NDB4V0      | IO87NDB4V0       |

| L6         | NC              | GEC2/IO60PDB3V0 | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |

| L7         | GNDA            | GNDA            | GNDA            | GNDA             |

| L8         | AC0             | AC0             | AC2             | AC2              |

| L9         | AV2             | AV2             | AV4             | AV4              |

| L10        | AC3             | AC3             | AC5             | AC5              |

| L11        | PTEM            | PTEM            | PTEM            | PTEM             |

| L12        | TDO             | TDO             | TDO             | TDO              |

| L13        | VJTAG           | VJTAG           | VJTAG           | VJTAG            |

| L14        | NC              | IO57NPB1V0      | IO57NPB2V0      | IO84NPB2V0       |

| L15        | GDB2/IO41PPB1V0 | GDB2/IO56PPB1V0 | GDB2/IO56PPB2V0 | GDB2/IO83PPB2V0  |

| L16        | NC              | IO55NPB1V0      | IO55NPB2V0      | IO82NPB2V0       |

| M1         | GND             | GND             | GND             | GND              |

| M2         | NC              | GEA1/IO61PDB3V0 | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  |

| M3         | NC              | GEA0/IO61NDB3V0 | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  |

| M4         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| M5         | NC              | IO58NPB3V0      | IO58NPB4V0      | IO85NPB4V0       |

| M6         | NC              | NC              | AV0             | AV0              |

| M7         | NC              | NC              | AC1             | AC1              |

| M8         | AG1             | AG1             | AG3             | AG3              |

| M9         | AC2             | AC2             | AC4             | AC4              |

| M10        | AC4             | AC4             | AC6             | AC6              |

| M11        | NC              | AG5             | AG7             | AG7              |

| M12        | VPUMP           | VPUMP           | VPUMP           | VPUMP            |

| M13        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| M14        | TMS             | TMS             | TMS             | TMS              |

## **5 – Datasheet Information**

## **List of Changes**

The following table lists critical changes that were made in each revision of the Fusion datasheet.

| Revision                     | Changes                                                                                                                                                                                                                                                                                 | Page            |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 6<br>(March 2014)   | Note added for the discontinuance of QN108 and QN180 packages to the "Package I/Os: Single-/Double-Ended (Analog)" table and the "Temperature Grade Offerings" table (SAR 55113, PDN 1306).                                                                                             |                 |

|                              | Updated details about page programming time in the "Program Operation" section (SAR 49291).                                                                                                                                                                                             |                 |

|                              | ADC_START changed to ADCSTART in the "ADC Operation" section (SAR 44104).                                                                                                                                                                                                               | 2-104           |

| Revision 5<br>(January 2014) | Calibrated offset values (AFS090, AFS250) of the external temperature monitor in Table 2-49 • Analog Channel Specifications have been updated (SAR 51464).                                                                                                                              |                 |

|                              | Specifications for the internal temperature monitor in<br>Table 2-49 • Analog Channel Specifications have been updated (SAR 50870).                                                                                                                                                     | 2-117           |

| Revision 4<br>(January 2013) | The "Product Ordering Codes" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43177).                                                               |                 |

|                              | The note in Table 2-12 • Fusion CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42563).                                                                                                            |                 |

|                              | Table 2-49 • Analog Channel Specifications was modified to update the uncalibrated offset values (AFS250) of the external and internal temperature monitors (SAR 43134).                                                                                                                |                 |

|                              | In Table 2-57 • Prescaler Control Truth Table—AV ( $x = 0$ ), AC ( $x = 1$ ), and AT ( $x = 3$ ), changed the column heading from 'Full-Scale Voltage' to 'Full Scale Voltage in 10-Bit Mode', and added and updated Notes as required (SAR 20812).                                     | 2-130           |

|                              | The values for the Speed Grade (-1 and Std.) for FDDRIMAX (Table 2-180 • Input DDR Propagation Delays) and values for the Speed Grade (-2 and Std.) for FDDOMAX (Table 2-182 • Output DDR Propagation Delays) had been inadvertently interchanged. This has been rectified (SAR 38514). | 2-220,<br>2-222 |

|                              | Added description about what happens if a user connects VAREF to an external 3.3 V on their board to the "VAREF Analog Reference Voltage" section (SAR 35188).                                                                                                                          | 2-225           |

|                              | Added a note to Table 3-2 • Recommended Operating Conditions1 (SAR 43429):<br>The programming temperature range supported is $T_{ambient} = 0^{\circ}C$ to 85°C.                                                                                                                        | 3-3             |

|                              | Added the Package Thermal details for AFS600-PQ208 and AFS250-PQ208 to Table 3-6 • Package Thermal Resistance (SAR 37816). Deleted the Die Size column from the table (SAR 43503).                                                                                                      | 3-7             |

|                              | Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 42495).                                                                                                                                                              | NA              |

|                              | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                            |                 |

| Revision 3                   | Microblade U1AFS250 and U1AFS1500 devices were added to the product tables.                                                                                                                                                                                                             | I – IV          |

| (nuguəi 2012)                | A sentence pertaining to the analog I/Os was added to the "Specifying I/O States During Programming" section (SAR 34831).                                                                                                                                                               | 1-9             |

| (August 2012)                | A sentence pertaining to the analog I/Os was added to the "Specifying I/O State                                                                                                                                                                                                         |                 |