Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                  |

|--------------------------------|------------------------------------------------------------------|

| Product Status                 | Obsolete                                                         |

| Number of LABs/CLBs            | -                                                                |

| Number of Logic Elements/Cells | -                                                                |

| Total RAM Bits                 | 36864                                                            |

| Number of I/O                  | 65                                                               |

| Number of Gates                | 250000                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                                  |

| Mounting Type                  | Surface Mount                                                    |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                               |

| Package / Case                 | 180-WFQFN Dual Rows, Exposed Pad                                 |

| Supplier Device Package        | 180-QFN (10x10)                                                  |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs250-2qng180i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **RC** Oscillator

The RC oscillator is an on-chip free-running clock source generating a 100 MHz clock. It can be used as a source clock for both on-chip and off-chip resources. When used in conjunction with the Fusion PLL and CCC circuits, the RC oscillator clock source can be used to generate clocks of varying frequency and phase.

The Fusion RC oscillator is very accurate at  $\pm 1\%$  over commercial temperature ranges and and  $\pm 3\%$  over industrial temperature ranges. It is an automated clock, requiring no setup or configuration by the user. It requires only that the power and GNDOSC pins be connected; no external components are required. The RC oscillator can be used to drive either a PLL or another internal signal.

### RC Oscillator Characteristics

Table 2-9 • Electrical Characteristics of RC Oscillator

| Parameter          | Description         | Conditions                                                                                | Min. | Тур. | Max. | Units |

|--------------------|---------------------|-------------------------------------------------------------------------------------------|------|------|------|-------|

|                    | Operating Frequency |                                                                                           |      | 100  |      | MHz   |

|                    | Accuracy            | Temperature: 0°C to 85°C<br>Voltage: 3.3 V ± 5%                                           |      | 1    |      | %     |

|                    |                     | Temperature: –40°C to 125°C<br>Voltage: 3.3 V ± 5%                                        |      | 3    |      | %     |

| F <sub>RC</sub>    | Output Jitter       | Period Jitter (at 5 k cycles)                                                             |      | 100  |      | ps    |

| - KC               |                     | Cycle–Cycle Jitter (at 5 k cycles)                                                        |      | 100  |      | ps    |

|                    |                     | Period Jitter (at 5 k cycles) with 1 KHz / 300 mV peak-to-peak noise on power supply      |      | 150  |      | ps    |

|                    |                     | Cycle–Cycle Jitter (at 5 k cycles) with 1 KHz / 300 mV peak-to-peak noise on power supply |      | 150  |      | ps    |

|                    | Output Duty Cycle   |                                                                                           |      | 50   |      | %     |

| I <sub>DYNRC</sub> | Operating Current   |                                                                                           |      | 1    |      | mA    |

2-19 Revision 6

# **Modes of Operation**

# Standby Mode

Standby mode allows periodic power-up and power-down of the FPGA fabric. In standby mode, the real-time counter and crystal block are ON. The FPGA is not powered by disabling the 1.5 V voltage regulator. The 1.5 V voltage regulator can be enabled when the preset count is matched. Refer to the "Real-Time Counter (part of AB macro)" section for details. To enter standby mode, the RTC must be first configured and enabled. Then VRPSM is shut off by deasserting the VRPU signal. The 1.5 V voltage regulator is then disabled, and shuts off the 1.5 V output.

# Sleep Mode

In sleep mode, the real-time counter and crystal blocks are OFF. The 1.5 V voltage regulator inside the VRPSM can only be enabled by the PUB or TRST pin. Refer to the "Voltage Regulator and Power System Monitor (VRPSM)" section on page 2-36 for details on power-up and power-down of the 1.5 V voltage regulator.

# Standby and Sleep Mode Circuit Implementation

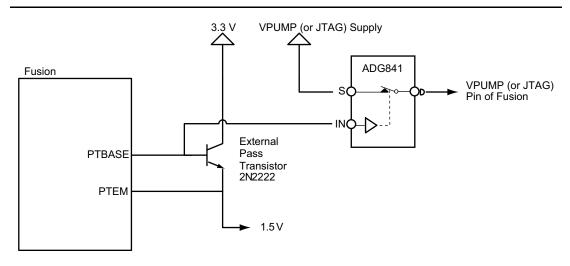

For extra power savings, VJTAG and VPUMP should be at the same voltage as VCC, floated or ground, during standby and sleep modes. Note that when VJTAG is not powered, the 1.5 V voltage regulator cannot be enabled through TRST.

VPUMP and VJTAG can be controlled through an external switch. Microsemi recommends ADG839, ADG849, or ADG841 as possible switches. Figure 2-28 shows the implementation for controlling VPUMP. The IN signal of the switch can be connected to PTBASE of the Fusion device. VJTAG can be controlled in same manner.

Figure 2-28 • Implementation to Control VPUMP

Revision 6 2-32

# **Embedded Memories**

Fusion devices include four types of embedded memory: flash block, FlashROM, SRAM, and FIFO.

# **Flash Memory Block**

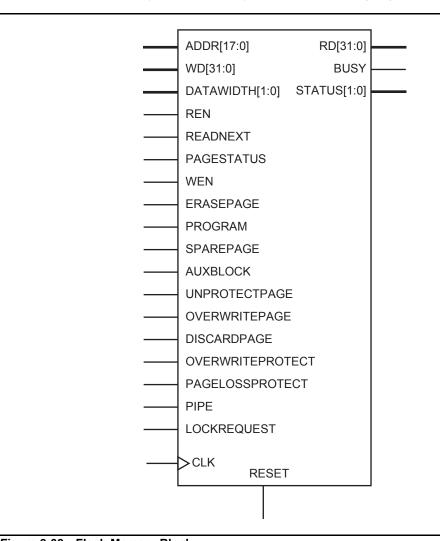

Fusion is the first FPGA that offers a flash memory block (FB). Each FB block stores 2 Mbits of data. The flash memory block macro is illustrated in Figure 2-32. The port pin name and descriptions are detailed on Table 2-19 on page 2-40. All flash memory block signals are active high, except for CLK and active low RESET. All flash memory operations are synchronous to the rising edge of CLK.

Figure 2-32 • Flash Memory Block

2-39 Revision 6

The following signals are used to configure the RAM4K9 memory element.

#### WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 2-27).

Table 2-27 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA1, WIDTHA0                                                               | WIDTHB1, WIDTHB0 | D×W  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|------------------|------|--|--|--|--|--|--|

| 00                                                                             | 00               | 4k×1 |  |  |  |  |  |  |

| 01                                                                             | 01               | 2k×2 |  |  |  |  |  |  |

| 10                                                                             | 10               | 1k×4 |  |  |  |  |  |  |

| 11 11 512×9                                                                    |                  |      |  |  |  |  |  |  |

| Note: The aspect ratio settings are constant and cannot be changed on the fly. |                  |      |  |  |  |  |  |  |

#### **BLKA and BLKB**

These signals are active low and will enable the respective ports when asserted. When a BLKx signal is deasserted, the corresponding port's outputs hold the previous value.

#### WENA and WENB

These signals switch the RAM between read and write mode for the respective ports. A Low on these signals indicates a write operation, and a High indicates a read.

#### CLKA and CLKB

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A Low on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A High indicates a pipelined, read and data appears on the corresponding output in the next clock cycle.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A Low on these signals makes the output retain data from the previous read. A High indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

#### RESET

This active low signal resets the output to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory.

#### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 2-28).

Table 2-28 • Address Pins Unused/Used for Various Supported Bus Widths

| D×W   | ADDRx   |        |  |  |  |  |  |  |  |

|-------|---------|--------|--|--|--|--|--|--|--|

| DAVV  | Unused  | Used   |  |  |  |  |  |  |  |

| 4k×1  | None    | [11:0] |  |  |  |  |  |  |  |

| 2k×2  | [11]    | [10:0] |  |  |  |  |  |  |  |

| 1k×4  | [11:10] | [9:0]  |  |  |  |  |  |  |  |

| 512×9 | [11:9]  | [8:0]  |  |  |  |  |  |  |  |

Note: The "x" in ADDRx implies A or B.

Revision 6 2-58

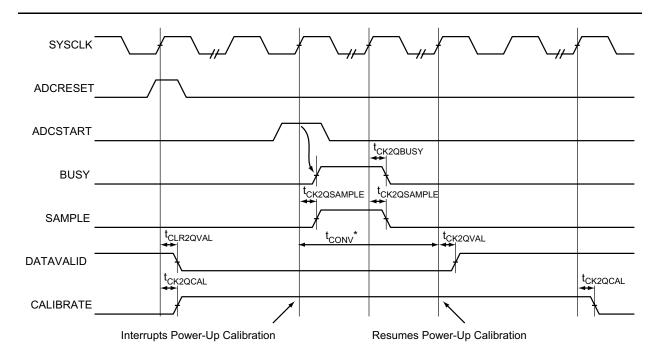

#### Intra-Conversion

Note:  $^*t_{CONV}$  represents the conversion time of the second conversion. See EQ 23 on page 2-109 for calculation of the conversion time,  $t_{CONV}$ .

Figure 2-92 • Intra-Conversion Timing Diagram

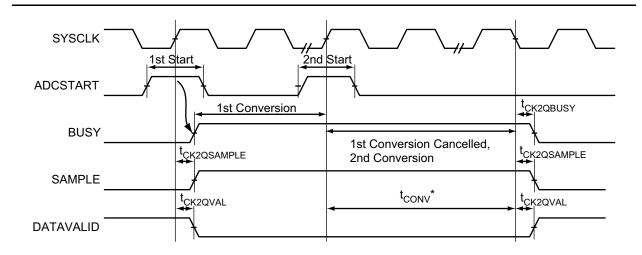

### Injected Conversion

Note: \*See EQ 23 on page 2-109 for calculation on the conversion time,  $t_{CONV}$ .

Figure 2-93 • Injected Conversion Timing Diagram

2-113 Revision 6

Table 2-85 • Fusion Pro I/O Attributes vs. I/O Standard Applications

|                      | ı                  | 1                       | ı                         | 1        | 1                      | ı                | ı                     | ı                           | ı                            | ı             |

|----------------------|--------------------|-------------------------|---------------------------|----------|------------------------|------------------|-----------------------|-----------------------------|------------------------------|---------------|

| I/O Standards        | SLEW (output only) | OUT_DRIVE (output only) | SKEW (all macros with OE) | RES_PULL | OUT_LOAD (output only) | COMBINE_REGISTER | IN_DELAY (input only) | ω IN_DELAY_VAL (input only) | SCHMITT_TRIGGER (input only) | HOT_SWAPPABLE |

| LVTTL/LVCMOS 3.3 V   | 3                  | 3                       | 3                         | 3        | 3                      | 3                | 3                     | 3                           | 3                            | 3             |

| LVCMOS 2.5 V         | 3                  | 3                       | 3                         | 3        | 3                      | 3                | 3                     | 3                           | 3                            | 3             |

| LVCMOS 2.5/5.0 V     | 3                  | 3                       | 3                         | 3        | 3                      | 3                | 3                     | 3                           | 3                            | 3             |

| LVCMOS 1.8 V         | 3                  | 3                       | 3                         | 3        | 3                      | 3                | 3                     | 3                           | 3                            | 3             |

| LVCMOS 1.5 V         | 3                  | 3                       | 3                         | 3        | 3                      | 3                | 3                     | 3                           | 3                            | 3             |

| PCI (3.3 V)          |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              |               |

| PCI-X (3.3 V)        | 3                  |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              |               |

| GTL+ (3.3 V)         |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              | 3             |

| GTL+ (2.5 V)         |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              | 3             |

| GTL (3.3 V)          |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              | 3             |

| GTL (2.5 V)          |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              | 3             |

| HSTL Class I         |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              | 3             |

| HSTL Class II        |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              | 3             |

| SSTL2 Class I and II |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              | 3             |

| SSTL3 Class I and II |                    |                         | 3                         |          | 3                      | 3                | 3                     | 3                           |                              | 3             |

| LVDS, BLVDS, M-LVDS  |                    |                         | 3                         |          |                        | 3                | 3                     | 3                           |                              | 3             |

| LVPECL               |                    |                         |                           |          |                        | 3                | 3                     | 3                           |                              | 3             |

2-157 Revision 6

# Table 2-113 • 2.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.60              | 8.82            | 0.04             | 1.51            | 1.66             | 0.43              | 8.13            | 8.82            | 2.72            | 2.29            | 10.37            | 11.05            | ns    |

|                   | -1             | 0.51              | 7.50            | 0.04             | 1.29            | 1.41             | 0.36              | 6.92            | 7.50            | 2.31            | 1.95            | 8.82             | 9.40             | ns    |

|                   | -2             | 0.45              | 6.58            | 0.03             | 1.13            | 1.24             | 0.32              | 6.07            | 6.58            | 2.03            | 1.71            | 7.74             | 8.25             | ns    |

| 8 mA              | Std.           | 0.60              | 5.27            | 0.04             | 1.51            | 1.66             | 0.43              | 5.27            | 5.27            | 3.10            | 3.03            | 7.50             | 7.51             | ns    |

|                   | -1             | 0.51              | 4.48            | 0.04             | 1.29            | 1.41             | 0.36              | 4.48            | 4.48            | 2.64            | 2.58            | 6.38             | 6.38             | ns    |

|                   | -2             | 0.45              | 3.94            | 0.03             | 1.13            | 1.24             | 0.32              | 3.93            | 3.94            | 2.32            | 2.26            | 5.60             | 5.61             | ns    |

| 12 mA             | Std.           | 0.66              | 3.74            | 0.04             | 1.51            | 1.66             | 0.43              | 3.81            | 3.49            | 3.37            | 3.49            | 6.05             | 5.73             | ns    |

|                   | <b>–</b> 1     | 0.56              | 3.18            | 0.04             | 1.29            | 1.41             | 0.36              | 3.24            | 2.97            | 2.86            | 2.97            | 5.15             | 4.87             | ns    |

|                   | -2             | 0.49              | 2.80            | 0.03             | 1.13            | 1.24             | 0.32              | 2.85            | 2.61            | 2.51            | 2.61            | 4.52             | 4.28             | ns    |

| 16 mA             | Std.           | 0.66              | 3.53            | 0.04             | 1.51            | 1.66             | 0.43              | 3.59            | 3.12            | 3.42            | 3.62            | 5.83             | 5.35             | ns    |

|                   | -1             | 0.56              | 3.00            | 0.04             | 1.29            | 1.41             | 0.36              | 3.06            | 2.65            | 2.91            | 3.08            | 4.96             | 4.55             | ns    |

|                   | -2             | 0.49              | 2.63            | 0.03             | 1.13            | 1.24             | 0.32              | 2.68            | 2.33            | 2.56            | 2.71            | 4.35             | 4.00             | ns    |

| 24 mA             | Std.           | 0.66              | 3.26            | 0.04             | 1.51            | 1.66             | 0.43              | 3.32            | 2.48            | 3.49            | 4.11            | 5.56             | 4.72             | ns    |

|                   | -1             | 0.56              | 2.77            | 0.04             | 1.29            | 1.41             | 0.36              | 2.83            | 2.11            | 2.97            | 3.49            | 4.73             | 4.01             | ns    |

|                   | -2             | 0.49              | 2.44            | 0.03             | 1.13            | 1.24             | 0.32              | 2.48            | 1.85            | 2.61            | 3.07            | 4.15             | 3.52             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-183 Revision 6

Table 2-130 • 1.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 1.4 V

Applicable to Advanced I/Os

| Dation            | 0              |                   |                 |                  |                 |                   |                 |                 |          |                 |                  |                  |       |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|----------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | $t_{LZ}$ | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

| 2 mA              | Std.           | 0.66              | 12.78           | 0.04             | 1.31            | 0.43              | 12.81           | 12.78           | 3.40     | 2.64            | 15.05            | 15.02            | ns    |

|                   | <b>–</b> 1     | 0.56              | 10.87           | 0.04             | 1.11            | 0.36              | 10.90           | 10.87           | 2.89     | 2.25            | 12.80            | 12.78            | ns    |

|                   | -2             | 0.49              | 9.55            | 0.03             | 0.98            | 0.32              | 9.57            | 9.55            | 2.54     | 1.97            | 11.24            | 11.22            | ns    |

| 4 mA              | Std.           | 0.66              | 10.01           | 0.04             | 1.31            | 0.43              | 10.19           | 9.55            | 3.75     | 3.27            | 12.43            | 11.78            | ns    |

|                   | <b>–</b> 1     | 0.56              | 8.51            | 0.04             | 1.11            | 0.36              | 8.67            | 8.12            | 3.19     | 2.78            | 10.57            | 10.02            | ns    |

|                   | -2             | 0.49              | 7.47            | 0.03             | 0.98            | 0.32              | 7.61            | 7.13            | 2.80     | 2.44            | 9.28             | 8.80             | ns    |

| 8 mA              | Std.           | 0.66              | 9.33            | 0.04             | 1.31            | 0.43              | 9.51            | 8.89            | 3.83     | 3.43            | 11.74            | 11.13            | ns    |

|                   | <b>–</b> 1     | 0.56              | 7.94            | 0.04             | 1.11            | 0.36              | 8.09            | 7.56            | 3.26     | 2.92            | 9.99             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.97            | 0.03             | 0.98            | 0.32              | 7.10            | 6.64            | 2.86     | 2.56            | 8.77             | 8.31             | ns    |

| 12 mA             | Std.           | 0.66              | 8.91            | 0.04             | 1.31            | 0.43              | 9.07            | 8.89            | 3.95     | 4.05            | 11.31            | 11.13            | ns    |

|                   | <b>–1</b>      | 0.56              | 7.58            | 0.04             | 1.11            | 0.36              | 7.72            | 7.57            | 3.36     | 3.44            | 9.62             | 9.47             | ns    |

|                   | -2             | 0.49              | 6.65            | 0.03             | 0.98            | 0.32              | 6.78            | 6.64            | 2.95     | 3.02            | 8.45             | 8.31             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-131 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 8.36            | 0.04             | 1.44            | 0.43              | 6.82            | 8.36            | 3.39            | 2.77            | 9.06             | 10.60            | ns    |

|                   | -1             | 0.56              | 7.11            | 0.04             | 1.22            | 0.36              | 5.80            | 7.11            | 2.88            | 2.35            | 7.71             | 9.02             | ns    |

|                   | -2             | 0.49              | 6.24            | 0.03             | 1.07            | 0.32              | 5.10            | 6.24            | 2.53            | 2.06            | 6.76             | 7.91             | ns    |

| 4 mA              | Std.           | 0.66              | 5.31            | 0.04             | 1.44            | 0.43              | 4.85            | 5.31            | 3.74            | 3.40            | 7.09             | 7.55             | ns    |

|                   | -1             | 0.56              | 4.52            | 0.04             | 1.22            | 0.36              | 4.13            | 4.52            | 3.18            | 2.89            | 6.03             | 6.42             | ns    |

|                   | -2             | 0.49              | 3.97            | 0.03             | 1.07            | 0.32              | 3.62            | 3.97            | 2.79            | 2.54            | 5.29             | 5.64             | ns    |

| 8 mA              | Std.           | 0.66              | 4.67            | 0.04             | 1.44            | 0.43              | 4.55            | 4.67            | 3.82            | 3.56            | 6.78             | 6.90             | ns    |

|                   | -1             | 0.56              | 3.97            | 0.04             | 1.22            | 0.36              | 3.87            | 3.97            | 3.25            | 3.03            | 5.77             | 5.87             | ns    |

|                   | -2             | 0.49              | 3.49            | 0.03             | 1.07            | 0.32              | 3.40            | 3.49            | 2.85            | 2.66            | 5.07             | 5.16             | ns    |

| 12 mA             | Std.           | 0.66              | 4.08            | 0.04             | 1.44            | 0.43              | 4.15            | 3.58            | 3.94            | 4.20            | 6.39             | 5.81             | ns    |

|                   | -1             | 0.56              | 3.47            | 0.04             | 1.22            | 0.36              | 3.53            | 3.04            | 3.36            | 3.58            | 5.44             | 4.95             | ns    |

|                   | -2             | 0.49              | 3.05            | 0.03             | 1.07            | 0.32              | 3.10            | 2.67            | 2.95            | 3.14            | 4.77             | 4.34             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-195 Revision 6

#### 3.3 V PCI, 3.3 V PCI-X

The Peripheral Component Interface for 3.3 V standard specifies support for 33 MHz and 66 MHz PCI Bus applications.

Table 2-134 • Minimum and Maximum DC Input and Output Levels

| 3.3 V PCI/PCI-X       | V              | IL        | V         | IH        | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup> |

|-----------------------|----------------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-------------------------|------------------|

| Drive Strength        | Min.<br>V      | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μA <sup>4</sup>  |

| Per PCI specification | Per PCI curves |           |           |           |           |           |     |    |                         | 10                      | 10                      |                  |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

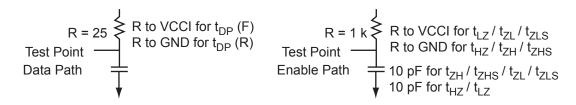

AC loadings are defined per the PCI/PCI-X specifications for the datapath; Microsemi loadings for enable path characterization are described in Figure 2-123.

Figure 2-123 • AC Loading

AC loadings are defined per PCI/PCI-X specifications for the data path; Microsemi loading for tristate is described in Table 2-135.

Table 2-135 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V)                | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------------------|-----------------|------------------------|

| 0             | 3.3            | 0.285 * VCCI for t <sub>DP(R)</sub> | -               | 10                     |

|               |                | 0.615 * VCCI for t <sub>DP(F)</sub> |                 |                        |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

2-197 Revision 6

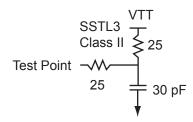

#### SSTL3 Class II

Stub-Speed Terminated Logic for 3.3 V memory bus standard (JESD8-8). Fusion devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-165 • Minimum and Maximum DC Input and Output Levels

| SSTL3 Class II |           | VIL        | VIH        |           | VOL       | VOH        | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|----------------|-----------|------------|------------|-----------|-----------|------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 21 mA          | -0.3      | VREF - 0.2 | VREF + 0.2 | 3.6       | 0.5       | VCCI - 0.9 | 21  | 21 | 109                     | 103                     | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

Figure 2-133 • AC Loading

Table 2-166 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF - 0.2    | VREF + 0.2     | 1.5                  | 1.5             | 1.485          | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-167 • SSTL3- Class II

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.5 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zhs</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.07            | 0.04             | 1.25            | 0.43              | 2.10            | 1.67            |                 |                 | 4.34             | 3.91             | ns    |

| -1             | 0.56              | 1.76            | 0.04             | 1.06            | 0.36              | 1.79            | 1.42            |                 |                 | 3.69             | 3.32             | ns    |

| -2             | 0.49              | 1.54            | 0.03             | 0.93            | 0.32              | 1.57            | 1.25            |                 |                 | 3.24             | 2.92             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

> Revision 6 2-208

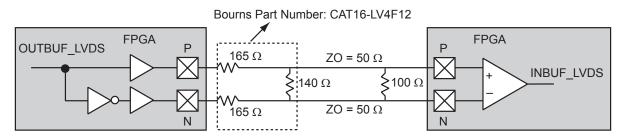

### Differential I/O Characteristics

Configuration of the I/O modules as a differential pair is handled by the Microsemi Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with these standards.

#### **LVDS**

Low-Voltage Differential Signal (ANSI/TIA/EIA-644) is a high-speed differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-134. The building blocks of the LVDS transmitter—receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Figure 2-134 • LVDS Circuit Diagram and Board-Level Implementation

| Table 2-168 • Minimum ar | nd Maximum | DC Input and | Output Levels |

|--------------------------|------------|--------------|---------------|

|--------------------------|------------|--------------|---------------|

| DC Parameter       | Description                 | Min.  | Тур.  | Max.  | Units |

|--------------------|-----------------------------|-------|-------|-------|-------|

| VCCI               | Supply Voltage              | 2.375 | 2.5   | 2.625 | V     |

| VOL                | Output Low Voltage          | 0.9   | 1.075 | 1.25  | V     |

| VOH                | Input High Voltage          | 1.25  | 1.425 | 1.6   | V     |

| IOL <sup>1</sup>   | Output Low Voltage          | 0.65  | 0.91  | 1.16  | mA    |

| IOH <sup>1</sup>   | Output High Voltage         | 0.65  | 0.91  | 1.16  | mA    |

| VI                 | Input Voltage               | 0     |       | 2.925 | V     |

| IIL <sup>2,3</sup> | Input Low Voltage           |       |       | 10    | μА    |

| IIH <sup>2,4</sup> | Input High Voltage          |       |       | 10    | μА    |

| VODIFF             | Differential Output Voltage | 250   | 350   | 450   | mV    |

| VOCM               | Output Common Mode Voltage  | 1.125 | 1.25  | 1.375 | V     |

| VICM               | Input Common Mode Voltage   | 0.05  | 1.25  | 2.35  | V     |

| VIDIFF             | Input Differential Voltage  | 100   | 350   |       | mV    |

#### Notes:

- 1. IOL/IOH defined by VODIFF/(Resistor Network)

- 2. Currents are measured at 85°C junction temperature.

- 3. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

2-209 Revision 6

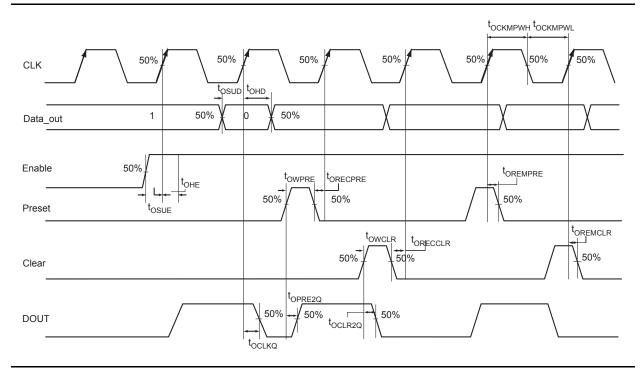

# **Output Register**

Figure 2-140 • Output Register Timing Diagram

**Timing Characteristics**

Table 2-177 • Output Data Register Propagation Delays

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | -2   | <b>–1</b> | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|-----------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 0.59 | 0.67      | 0.79 | ns    |

| tosud                | Data Setup Time for the Output Data Register                         | 0.31 | 0.36      | 0.42 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | 0.00      | 0.00 | ns    |

| tosuE                | Enable Setup Time for the Output Data Register                       | 0.44 | 0.50      | 0.59 | ns    |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                        | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.80 | 0.91      | 1.07 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.80 | 0.91      | 1.07 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | 0.00      | 0.00 | ns    |

| torecclr             | Asynchronous Clear Recovery Time for the Output Data Register        | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.22 | 0.25      | 0.30 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.36 | 0.41      | 0.48 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.32 | 0.37      | 0.43 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-217 Revision 6

Table 3-2 • Recommended Operating Conditions<sup>1</sup>

| Symbol              | Parameter <sup>2</sup>              |                               | Commercial     | Industrial     | Units |

|---------------------|-------------------------------------|-------------------------------|----------------|----------------|-------|

| $T_J$               | Junction temperature                |                               | 0 to +85       | -40 to +100    | °C    |

| VCC                 | 1.5 V DC core supply voltage        |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VJTAG               | JTAG DC voltage                     |                               | 1.4 to 3.6     | 1.4 to 3.6     | V     |

| VPUMP               | Programming voltage                 | Programming mode <sup>3</sup> | 3.15 to 3.45   | 3.15 to 3.45   | V     |

|                     |                                     | Operation <sup>4</sup>        | 0 to 3.6       | 0 to 3.6       | V     |

| VCCPLL              | Analog power supply (PLL)           |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCI                | 1.5 V DC supply voltage             |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

|                     | 1.8 V DC supply voltage             |                               | 1.7 to 1.9     | 1.7 to 1.9     | V     |

|                     | 2.5 V DC supply voltage             |                               | 2.3 to 2.7     | 2.3 to 2.7     | V     |

|                     | 3.3 V DC supply voltage             |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

|                     | LVDS differential I/O               |                               | 2.375 to 2.625 | 2.375 to 2.625 | V     |

|                     | LVPECL differential I/O             |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

| VCC33A              | +3.3 V power supply                 |                               | 2.97 to 3.63   | 2.97 to 3.63   | V     |

| VCC33PMP            | +3.3 V power supply                 |                               | 2.97 to 3.63   | 2.97 to 3.63   | V     |

| VAREF               | Voltage reference for ADC           |                               | 2.527 to 2.593 | 2.527 to 2.593 | V     |

| VCC15A <sup>5</sup> | Digital power supply for the analog | system                        | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCNVM              | Embedded flash power supply         |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCOSC              | Oscillator power supply             |                               | 2.97 to 3.63   | 2.97 to 3.63   | V     |

| AV, AC <sup>6</sup> | Unpowered, ADC reset asserted or    | unconfigured                  | -10.5 to 12.0  | -10.5 to 11.6  | V     |

|                     | Analog input (+16 V to +2 V presca  | ller range)                   | -0.3 to 12.0   | -0.3 to 11.6   | V     |

|                     | Analog input (+1 V to + 0.125 V pre | escaler range)                | -0.3 to 3.6    | -0.3 to 3.6    | V     |

|                     | Analog input (–16 V to –2 V presca  | ler range)                    | -10.5 to 0.3   | -10.5 to 0.3   | V     |

|                     | Analog input (-1 V to -0.125 V pres | scaler range)                 | -3.6 to 0.3    | -3.6 to 0.3    | V     |

|                     | Analog input (direct input to ADC)  |                               | -0.3 to 3.6    | -0.3 to 3.6    | V     |

|                     | Digital input                       |                               | -0.3 to 12.0   | -0.3 to 11.6   | V     |

| AG <sup>6</sup>     | Unpowered, ADC reset asserted or    | unconfigured                  | -10.5 to 12.0  | -10.5 to 11.6  | V     |

|                     | Low Current Mode (1 µA, 3 µA, 10    | μΑ, 30 μΑ)                    | -0.3 to 12.0   | -0.3 to 11.6   | V     |

|                     | Low Current Mode (-1 μA, -3 μA, -   | -10 μΑ, –30 μΑ)               | -10.5 to 0.3   | -10.5 to 0.3   | V     |

|                     | High Current Mode <sup>7</sup>      |                               | -10.5 to 12.0  | -10.5 to 11.6  | V     |

| AT <sup>6</sup>     | Unpowered, ADC reset asserted or    | unconfigured                  | -0.3 to 15.5   | -0.3 to 14.5   | V     |

|                     | Analog input (+16 V, +4 V prescale  | r range)                      | -0.3 to 15.5   | -0.3 to 14.5   | V     |

|                     | Analog input (direct input to ADC)  |                               | -0.3 to 3.6    | -0.3 to 3.6    | V     |

|                     | Digital input                       |                               | -0.3 to 15.5   | -0.3 to 14.5   | V     |

#### Notes:

- 1. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-85 on page 2-157.

- 2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 3. The programming temperature range supported is  $T_{ambient}$  = 0°C to 85°C.

- 4. VPUMP can be left floating during normal operation (not programming mode).

- 5. Violating the V<sub>CC15A</sub> recommended voltage supply during an embedded flash program cycle can corrupt the page being programmed.

- 6. The input voltage may overshoot by up to 500 mV above the Recommended Maximum (150 mV in Direct mode), provided the duration of the overshoot is less than 50% of the operating lifetime of the device.

- 7. The AG pad should also conform to the limits as specified in Table 2-48 on page 2-114.

3-3 Revision 6

# **Calculating Power Dissipation**

# **Quiescent Supply Current**

Table 3-8 • AFS1500 Quiescent Supply Current Characteristics

| Parameter          | Description             | Conditions                                                                       | Temp.                  | Min. | Тур. | Max. | Unit |

|--------------------|-------------------------|----------------------------------------------------------------------------------|------------------------|------|------|------|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current | Operational standby <sup>4</sup> ,                                               | $T_J = 25^{\circ}C$    |      | 20   | 40   | mA   |

|                    |                         | VCC = 1.575 V                                                                    | T <sub>J</sub> = 85°C  |      | 32   | 65   | mA   |

|                    |                         |                                                                                  | T <sub>J</sub> = 100°C |      | 59   | 120  | mA   |

|                    |                         | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VCC = 0 V              |                        |      | 0    | 0    | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies   | Operational standby <sup>4</sup> ,                                               | $T_J = 25^{\circ}C$    |      | 9.8  | 13   | mA   |

|                    | current                 | VCC33 = 3.63 V                                                                   | T <sub>J</sub> = 85°C  |      | 10.7 | 14   | mA   |

|                    |                         |                                                                                  | T <sub>J</sub> = 100°C |      | 10.8 | 15   | mA   |

|                    |                         | Operational standby, only Analog<br>Quad and –3.3 V output ON,<br>VCC33 = 3.63 V | T <sub>J</sub> = 25°C  |      | 0.31 | 2    | mA   |

|                    |                         |                                                                                  | T <sub>J</sub> = 85°C  |      | 0.35 | 2    | mA   |

|                    |                         |                                                                                  | T <sub>J</sub> = 100°C |      | 0.45 | 2    | mA   |

|                    |                         | Standby mode <sup>5</sup> , VCC33 = 3.63 V                                       | T <sub>J</sub> = 25°C  |      | 2.9  | 3.6  | mA   |

|                    |                         |                                                                                  | T <sub>J</sub> = 85°C  |      | 2.9  | 4    | mA   |

|                    |                         |                                                                                  | T <sub>J</sub> = 100°C |      | 3.3  | 6    | mA   |

|                    |                         | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                                         | $T_J = 25^{\circ}C$    |      | 17   | 19   | μΑ   |

|                    |                         |                                                                                  | T <sub>J</sub> = 85°C  |      | 18   | 20   | μΑ   |

|                    |                         |                                                                                  | T <sub>J</sub> = 100°C |      | 24   | 25   | μΑ   |

| ICCI <sup>3</sup>  | I/O quiescent current   | Operational standby <sup>4</sup> ,                                               | T <sub>J</sub> = 25°C  |      | 417  | 649  | μΑ   |

|                    |                         | Standby mode, and Sleep Mode <sup>6</sup> , VCCIx = 3.63 V                       | T <sub>J</sub> = 85°C  |      | 417  | 649  | μΑ   |

|                    |                         |                                                                                  | T <sub>J</sub> = 100°C |      | 417  | 649  | μΑ   |

#### Notes:

- 1. ICC is the 1.5 V power supplies, ICC and ICC15A.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

Revision 6 3-10

# Methodology

# Total Power Consumption—P<sub>TOTAL</sub>

#### Operating Mode, Standby Mode, and Sleep Mode

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

### Total Static Power Consumption—P<sub>STAT</sub>

### **Operating Mode**

$P_{STAT}$  = PDC1 + ( $N_{NVM-BLOCKS}$  \* PDC4) + PDC5+ ( $N_{QUADS}$  \* PDC6) + ( $N_{INPUTS}$  \* PDC7) + ( $N_{OUTPUTS}$  \* PDC8) + ( $N_{PLLS}$  \* PDC9)

$N_{\mbox{\scriptsize NVM-BLOCKS}}$  is the number of NVM blocks available in the device.

N<sub>QUADS</sub> is the number of Analog Quads used in the design.

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$N_{\mbox{\scriptsize OUTPUTS}}$  is the number of I/O output buffers used in the design.

N<sub>PLLS</sub> is the number of PLLs available in the device.

#### Standby Mode

$P_{STAT} = PDC2$

#### Sleep Mode

$P_{STAT} = PDC3$

### Total Dynamic Power Consumption—PDYN

#### **Operating Mode**

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub> + P<sub>NVM</sub>+ P<sub>XTL-OSC</sub> + P<sub>RC-OSC</sub> + P<sub>AB</sub>

# Standby Mode

$P_{DYN} = P_{XTL-OSC}$

### Sleep Mode

$P_{DYN} = 0 W$

# Global Clock Dynamic Contribution—P<sub>CLOCK</sub>

#### **Operating Mode**

P<sub>CLOCK</sub> = (PAC1 + N<sub>SPINE</sub> \* PAC2 + N<sub>ROW</sub> \* PAC3 + N<sub>S-CELL</sub> \* PAC4) \* F<sub>CLK</sub>

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *Fusion and Extended Temperature Fusion FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *Fusion and Extended Temperature Fusion FPGA Fabric User's Guide*.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

#### Standby Mode and Sleep Mode

P<sub>CLOCK</sub> = 0 W

# Sequential Cells Dynamic Contribution—P<sub>S-CELL</sub>

#### **Operating Mode**

Revision 6 3-24

# Package Pin Assignments

| FG676      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AFS1500 Function |  |  |  |

| L17        | VCCIB2           |  |  |  |

| L18        | GCB2/IO60PDB2V0  |  |  |  |

| L19        | IO58NDB2V0       |  |  |  |

| L20        | IO57NDB2V0       |  |  |  |

| L21        | IO59NDB2V0       |  |  |  |

| L22        | GCC2/IO61PDB2V0  |  |  |  |

| L23        | IO55PPB2V0       |  |  |  |

| L24        | IO56PDB2V0       |  |  |  |

| L25        | IO55NPB2V0       |  |  |  |

| L26        | GND              |  |  |  |

| M1         | NC               |  |  |  |

| M2         | VCCIB4           |  |  |  |

| M3         | GFC2/IO108PDB4V0 |  |  |  |

| M4         | GND              |  |  |  |

| M5         | IO109NDB4V0      |  |  |  |

| M6         | IO110NDB4V0      |  |  |  |

| M7         | GND              |  |  |  |

| M8         | IO104NDB4V0      |  |  |  |

| M9         | IO111NDB4V0      |  |  |  |

| M10        | GND              |  |  |  |

| M11        | ∨cc              |  |  |  |

| M12        | GND              |  |  |  |

| M13        | VCC              |  |  |  |

| M14        | GND              |  |  |  |

| M15        | VCC              |  |  |  |

| M16        | GND              |  |  |  |

| M17        | GND              |  |  |  |

| M18        | IO60NDB2V0       |  |  |  |

| M19        | IO58PDB2V0       |  |  |  |

| M20        | GND              |  |  |  |

| M21        | IO68NPB2V0       |  |  |  |

| M22        | IO61NDB2V0       |  |  |  |

| M23        | GND              |  |  |  |

| M24        | IO56NDB2V0       |  |  |  |

| M25        | VCCIB2           |  |  |  |

| M26        | IO65PDB2V0       |  |  |  |

|            |                  |  |  |  |

|            | FG676            |  |  |  |  |

|------------|------------------|--|--|--|--|

| Pin Number | AFS1500 Function |  |  |  |  |

| N1         | NC               |  |  |  |  |

| N2         | NC               |  |  |  |  |

| N3         | IO108NDB4V0      |  |  |  |  |

| N4         | vccosc           |  |  |  |  |

| N5         | VCCIB4           |  |  |  |  |

| N6         | XTAL2            |  |  |  |  |

| N7         | GFC1/IO107PDB4V0 |  |  |  |  |

| N8         | VCCIB4           |  |  |  |  |

| N9         | GFB1/IO106PDB4V0 |  |  |  |  |

| N10        | VCCIB4           |  |  |  |  |

| N11        | GND              |  |  |  |  |

| N12        | VCC              |  |  |  |  |

| N13        | GND              |  |  |  |  |

| N14        | VCC              |  |  |  |  |

| N15        | GND              |  |  |  |  |

| N16        | VCC              |  |  |  |  |

| N17        | VCCIB2           |  |  |  |  |

| N18        | IO70PDB2V0       |  |  |  |  |

| N19        | VCCIB2           |  |  |  |  |

| N20        | IO69PDB2V0       |  |  |  |  |

| N21        | GCA1/IO64PDB2V0  |  |  |  |  |

| N22        | VCCIB2           |  |  |  |  |

| N23        | GCC0/IO62NDB2V0  |  |  |  |  |

| N24        | GCC1/IO62PDB2V0  |  |  |  |  |

| N25        | IO66PDB2V0       |  |  |  |  |

| N26        | IO65NDB2V0       |  |  |  |  |

| P1         | NC               |  |  |  |  |

| P2         | NC               |  |  |  |  |

| P3         | IO103PDB4V0      |  |  |  |  |

| P4         | XTAL1            |  |  |  |  |

| P5         | VCCIB4           |  |  |  |  |

| P6         | GNDOSC           |  |  |  |  |

| P7         | GFC0/IO107NDB4V0 |  |  |  |  |

| P8         | VCCIB4           |  |  |  |  |

| P9         | GFB0/IO106NDB4V0 |  |  |  |  |

| P10        | VCCIB4           |  |  |  |  |

|            |                  |  |  |  |  |

| FG676      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AFS1500 Function |  |  |  |

| P11        | VCC              |  |  |  |

| P12        | GND              |  |  |  |

| P13        | VCC              |  |  |  |

| P14        | GND              |  |  |  |

| P15        | VCC              |  |  |  |

| P16        | GND              |  |  |  |

| P17        | VCCIB2           |  |  |  |

| P18        | IO70NDB2V0       |  |  |  |

| P19        | VCCIB2           |  |  |  |

| P20        | IO69NDB2V0       |  |  |  |

| P21        | GCA0/IO64NDB2V0  |  |  |  |

| P22        | VCCIB2           |  |  |  |

| P23        | GCB0/IO63NDB2V0  |  |  |  |

| P24        | GCB1/IO63PDB2V0  |  |  |  |

| P25        | IO66NDB2V0       |  |  |  |

| P26        | IO67PDB2V0       |  |  |  |

| R1         | NC               |  |  |  |

| R2         | VCCIB4           |  |  |  |

| R3         | IO103NDB4V0      |  |  |  |

| R4         | GND              |  |  |  |

| R5         | IO101PDB4V0      |  |  |  |

| R6         | IO100NPB4V0      |  |  |  |

| R7         | GND              |  |  |  |

| R8         | IO99PDB4V0       |  |  |  |

| R9         | IO97PDB4V0       |  |  |  |

| R10        | GND              |  |  |  |

| R11        | GND              |  |  |  |

| R12        | VCC              |  |  |  |

| R13        | GND              |  |  |  |

| R14        | VCC              |  |  |  |

| R15        | GND              |  |  |  |

| R16        | VCC              |  |  |  |

| R17        | GND              |  |  |  |

| R18        | GDB2/IO83PDB2V0  |  |  |  |

| R19        | IO78PDB2V0       |  |  |  |

| R20        | GND              |  |  |  |

4-32 Revision 6

# 5 - Datasheet Information

# **List of Changes**

The following table lists critical changes that were made in each revision of the Fusion datasheet.

| Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page             |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Revision 6<br>(March 2014)   | Note added for the discontinuance of QN108 and QN180 packages to the "Package I/Os: Single-/Double-Ended (Analog)" table and the "Temperature Grade Offerings" table (SAR 55113, PDN 1306).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | II and IV        |

|                              | Updated details about page programming time in the "Program Operation" section (SAR 49291).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-46             |

|                              | ADC_START changed to ADCSTART in the "ADC Operation" section (SAR 44104).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-104            |

| Revision 5<br>(January 2014) | Calibrated offset values (AFS090, AFS250) of the external temperature monitor in Table 2-49 • Analog Channel Specifications have been updated (SAR 51464).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-117            |

|                              | Specifications for the internal temperature monitor in Table 2-49 • Analog Channel Specifications have been updated (SAR 50870).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-117            |

| Revision 4<br>(January 2013) | The "Product Ordering Codes" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43177).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | III              |

|                              | The note in Table 2-12 • Fusion CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42563).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-28             |

|                              | Table 2-49 • Analog Channel Specifications was modified to update the uncalibrated offset values (AFS250) of the external and internal temperature monitors (SAR 43134).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-117            |

|                              | In Table 2-57 • Prescaler Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3), changed the column heading from 'Full-Scale Voltage' to 'Full Scale Voltage in 10-Bit Mode', and added and updated Notes as required (SAR 20812).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-130            |

|                              | The values for the Speed Grade (-1 and Std.) for FDDRIMAX (Table 2-180 • Input DDR Propagation Delays) and values for the Speed Grade (-2 and Std.) for FDDOMAX (Table 2-182 • Output DDR Propagation Delays) had been inadvertently interchanged. This has been rectified (SAR 38514).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-220,<br>2-222  |

|                              | Added description about what happens if a user connects VAREF to an external 3.3 V on their board to the "VAREF Analog Reference Voltage" section (SAR 35188).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-225            |

|                              | Added a note to Table 3-2 • Recommended Operating Conditions1 (SAR 43429): The programming temperature range supported is T <sub>ambient</sub> = 0°C to 85°C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-3              |

|                              | Added the Package Thermal details for AFS600-PQ208 and AFS250-PQ208 to Table 3-6 • Package Thermal Resistance (SAR 37816). Deleted the Die Size column from the table (SAR 43503).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-7              |

|                              | Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 42495).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NA               |

|                              | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |

| Revision 3                   | Microblade U1AFS250 and U1AFS1500 devices were added to the product tables.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I – IV           |

| (August 2012)                | A sentence pertaining to the analog I/Os was added to the "Specifying I/O States During Programming" section (SAR 34831).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-9              |

| Revision 3<br>(August 2012)  | V on their board to the "VAREF Analog Reference Voltage" section (SAR 35188).  Added a note to Table 3-2 • Recommended Operating Conditions1 (SAR 43429): The programming temperature range supported is T <sub>ambient</sub> = 0°C to 85°C.  Added the Package Thermal details for AFS600-PQ208 and AFS250-PQ208 to Table 3-6 • Package Thermal Resistance (SAR 37816). Deleted the Die Size column from the table (SAR 43503).  Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 42495).  Live at Power-Up (LAPU) has been replaced with 'Instant On'.  Microblade U1AFS250 and U1AFS1500 devices were added to the product tables.  A sentence pertaining to the analog I/Os was added to the "Specifying I/O States" | 3-3<br>3-7<br>NA |

Revision 6 5-1

# Fusion Family of Mixed Signal FPGAs

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page              |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| v2.0, Revision 1<br>(continued) | The data in the 2.5 V LCMOS and LVCMOS 2.5 V / 5.0 V rows were updated in Table 2-75 • Fusion Standard and Advanced I/O – Hot-Swap and 5 V Input Tolerance Capabilities.                                                                                                                                                                                                                                                                                                                                                | 2-143             |