Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | 36864                                                          |

| Number of I/O                  | 65                                                             |

| Number of Gates                | 250000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                                |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                |

| Package / Case                 | 180-WFQFN Dual Rows, Exposed Pad                               |

| Supplier Device Package        | 180-QFN (10x10)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs250-qng180 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

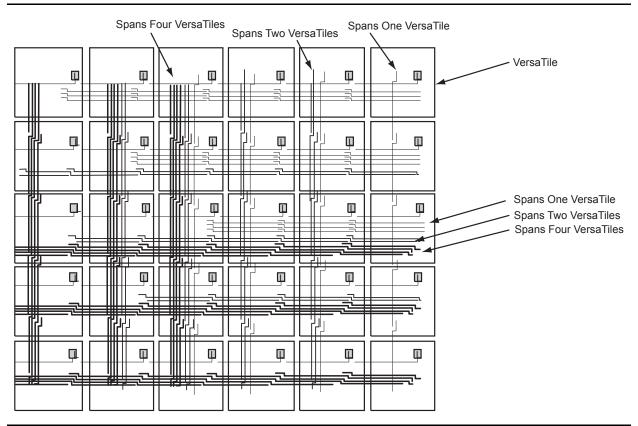

Figure 2-9 • Efficient Long-Line Resources

2-9 Revision 6

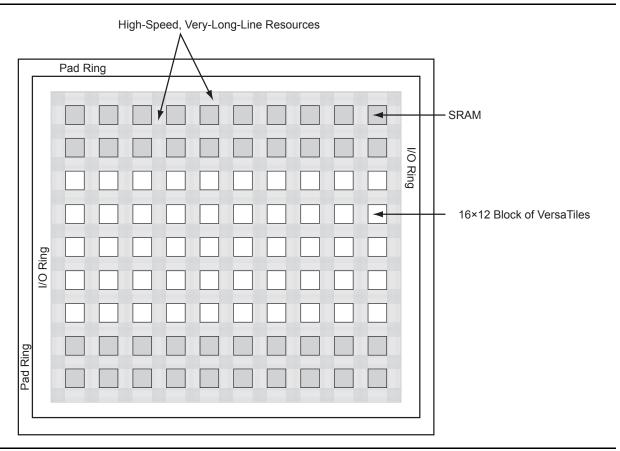

Figure 2-10 • Very-Long-Line Resources

# **Clock Conditioning Circuits**

In Fusion devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations.

The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides.

Each CCC can implement up to three independent global buffers (with or without programmable delay), or a PLL function (programmable frequency division/multiplication, phase shift, and delays) with up to three global outputs. Unused global outputs of a PLL can be used to implement independent global buffers, up to a maximum of three global outputs for a given CCC.

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, and CLKC-GLC) of a given CCC.

A PLL macro uses the CLKA CCC input to drive its reference clock. It uses the GLA and, optionally, the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global output cannot be reused if the YB (or YC) output is used (Figure 2-19). Refer to the "PLL Macro" section on page 2-27 for more information.

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

- · The FPGA core

The CCC block is fully configurable, either via flash configuration bits set in the programming bitstream or through an asynchronous interface. This asynchronous interface is dynamically accessible from inside the Fusion device to permit changes of parameters (such as divide ratios) during device operation. To increase the versatility and flexibility of the clock conditioning system, the CCC configuration is determined either by the user during the design process, with configuration data being stored in flash memory as part of the device programming procedure, or by writing data into a dedicated shift register during normal device operation. This latter mode allows the user to dynamically reconfigure the CCC without the need for core programming. The shift register is accessed through a simple serial interface. Refer to the "UJTAG Applications in Microsemi's Low-Power Flash Devices" chapter of the *Fusion FPGA Fabric User Guide* and the "CCC and PLL Characteristics" section on page 2-28 for more information.

# **Timing Characteristics**

Table 2-35 • FIFO Commercial Temperature Range Conditions:  $T_J = 70$  °C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                       | -2   | <b>–1</b> | Std. | Units |

|----------------------|---------------------------------------------------|------|-----------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup time                               | 1.34 | 1.52      | 1.79 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold time                                | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>BKS</sub>     | BLK Setup time                                    | 0.19 | 0.22      | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold time                                     | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>DS</sub>      | Input data (WD) Setup time                        | 0.18 | 0.21      | 0.25 | ns    |

| t <sub>DH</sub>      | Input data (WD) Hold time                         | 0.00 | 0.00      | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (flow-through) | 2.17 | 2.47      | 2.90 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.94 | 1.07      | 1.26 | ns    |

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96      | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86      | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05      | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93      | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost-Empty/Full Flag Valid         | 6.13 | 6.98      | 8.20 | ns    |

| +                    | RESET Low to Data out Low on RD (flow-through)    | 0.92 | 1.05      | 1.23 | ns    |

| <sup>t</sup> RSTBQ   | RESET Low to Data out Low on RD (pipelined)       | 0.92 | 1.05      | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33      | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71      | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24      | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle time                                  | 3.23 | 3.68      | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency for FIFO                        | 310  | 272       | 231  | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-75 Revision 6

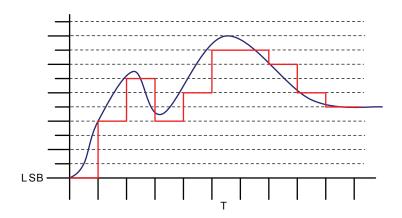

This process results in a binary approximation of VIN. Generally, there is a fixed interval T, the sampling period, between the samples. The inverse of the sampling period is often referred to as the sampling frequency  $f_S = 1 / T$ . The combined effect is illustrated in Figure 2-82.

Figure 2-82 • Conversion Example

Figure 2-82 demonstrates that if the signal changes faster than the sampling rate can accommodate, or if the actual value of VIN falls between counts in the result, this information is lost during the conversion. There are several techniques that can be used to address these issues.

First, the sampling rate must be chosen to provide enough samples to adequately represent the input signal. Based on the Nyquist-Shannon Sampling Theorem, the minimum sampling rate must be at least twice the frequency of the highest frequency component in the target signal (Nyquist Frequency). For example, to recreate the frequency content of an audio signal with up to 22 KHz bandwidth, the user must sample it at a minimum of 44 ksps. However, as shown in Figure 2-82, significant post-processing of the data is required to interpolate the value of the waveform during the time between each sample.

Similarly, to re-create the amplitude variation of a signal, the signal must be sampled with adequate resolution. Continuing with the audio example, the dynamic range of the human ear (the ratio of the amplitude of the threshold of hearing to the threshold of pain) is generally accepted to be 135 dB, and the dynamic range of a typical symphony orchestra performance is around 85 dB. Most commercial recording media provide about 96 dB of dynamic range using 16-bit sample resolution. But 16-bit fidelity does not necessarily mean that you need a 16-bit ADC. As long as the input is sampled at or above the Nyquist Frequency, post-processing techniques can be used to interpolate intermediate values and reconstruct the original input signal to within desired tolerances.

If sophisticated digital signal processing (DSP) capabilities are available, the best results are obtained by implementing a reconstruction filter, which is used to interpolate many intermediate values with higher resolution than the original data. Interpolating many intermediate values increases the effective number of samples, and higher resolution increases the effective number of bits in the sample. In many cases, however, it is not cost-effective or necessary to implement such a sophisticated reconstruction algorithm. For applications that do not require extremely fine reproduction of the input signal, alternative methods can enhance digital sampling results with relatively simple post-processing. The details of such techniques are out of the scope of this chapter; refer to the *Improving ADC Results through Oversampling and Post-Processing of Data* white paper for more information.

2-99 Revision 6

### Intra-Conversion

Performing a conversion during power-up calibration is possible but should be avoided, since the performance is not guaranteed, as shown in Table 2-49 on page 2-117. This is described as intra-conversion. Figure 2-92 on page 2-113 shows intra-conversion, (conversion that starts during power-up calibration).

### Injected Conversion

A conversion can be interrupted by another conversion. Before the current conversion is finished, a second conversion can be started by issuing a pulse on signal ADCSTART. When a second conversion is issued before the current conversion is completed, the current conversion would be dropped and the ADC would start the second conversion on the rising edge of the SYSCLK. This is known as injected conversion. Since the ADC is synchronous, the minimum time to issue a second conversion is two clock cycles of SYSCLK after the previous one. Figure 2-93 on page 2-113 shows injected conversion, (conversion that starts before a previously started conversion is finished). The total time for calibration still remains 3,840 ADCCLK cycles.

## ADC Example

This example shows how to choose the correct settings to achieve the fastest sample time in 10-bit mode for a system that runs at 66 MHz. Assume the acquisition times defined in Table 2-44 on page 2-108 for 10-bit mode, which gives  $0.549 \mu s$  as a minimum hold time.

The period of SYSCLK:  $t_{SYSCLK}$  = 1/66 MHz = 0.015  $\mu s$

Choosing TVC between 1 and 33 will meet the maximum and minimum period for the ADCCLK requirement. A higher TVC leads to a higher ADCCLK period.

The minimum TVC is chosen so that  $t_{distrib}$  and  $t_{post-cal}$  can be run faster. The period of ADCCLK with a TVC of 1 can be computed by EQ 24.

$$t_{ADCCLK} = 4 \times (1 + TVC) \times t_{SYSCLK} = 4 \times (1 + 1) \times 0.015 \ \mu s = 0.12 \ \mu s$$

EQ 24

The STC value can now be computed by using the minimum sample/hold time from Table 2-44 on page 2-108, as shown in EQ 25.

STC =

$$\frac{t_{\text{sample}}}{t_{\Delta DCCLK}} - 2 = \frac{0.549 \,\mu\text{s}}{0.12 \,\mu\text{s}} - 2 = 4.575 - 2 = 2.575$$

EQ 25

You must round up to 3 to accommodate the minimum sample time requirement. The actual sample time,  $t_{\text{sample}}$ , with an STC of 3, is now equal to 0.6  $\mu$ s, as shown in EQ 26

$$t_{\text{sample}} = (2 + \text{STC}) \times t_{\text{ADCCLK}} = (2 + 3) \times t_{\text{ADCCLK}} = 5 \times 0.12 \ \mu \text{s} = 0.6 \ \mu \text{s}$$

EQ 26

Microsemi recommends post-calibration for temperature drift over time, so post-calibration is enabled.

The post-calibration time,  $t_{\text{post-cal}}$ , can be computed by EQ 27. The post-calibration time is 0.24  $\mu s$ .

$$t_{post-cal} = 2 \times t_{ADCCLK} = 0.24 \mu s$$

EQ 27

The distribution time,  $t_{distrib}$ , is equal to 1.2  $\mu$ s and can be computed as shown in EQ 28 (N is number of bits, referring back to EQ 8 on page 2-94).

$$t_{distrib} = N \times t_{ADCCLK} = 10 \times 0.12 = 1.2 \mu s$$

EQ 28

The total conversion time can now be summated, as shown in EQ 29 (referring to EQ 23 on page 2-109).

$$t_{sync}$$

read +  $t_{sample}$  +  $t_{distrib}$  +  $t_{post-cal}$  +  $t_{sync}$  write = (0.015 + 0.60 + 1.2 + 0.24 + 0.015)  $\mu s$  = 2.07  $\mu s$

EQ 29

# **ADC Interface Timing**

Table 2-48 • ADC Interface Timing

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                | Description                                    | -2     | -1     | Std.   | Units |

|--------------------------|------------------------------------------------|--------|--------|--------|-------|

| t <sub>SUMODE</sub>      | Mode Pin Setup Time                            | 0.56   | 0.64   | 0.75   | ns    |

| t <sub>HDMODE</sub>      | Mode Pin Hold Time                             | 0.26   | 0.29   | 0.34   | ns    |

| t <sub>sutvc</sub>       | Clock Divide Control (TVC) Setup Time          | 0.68   | 0.77   | 0.90   | ns    |

| t <sub>HDTVC</sub>       | Clock Divide Control (TVC) Hold Time           | 0.32   | 0.36   | 0.43   | ns    |

| t <sub>sustc</sub>       | Sample Time Control (STC) Setup Time           | 1.58   | 1.79   | 2.11   | ns    |

| t <sub>HDSTC</sub>       | Sample Time Control (STC) Hold Time            | 1.27   | 1.45   | 1.71   | ns    |

| t <sub>SUVAREFSEL</sub>  | Voltage Reference Select (VAREFSEL) Setup Time | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>HDVAREFSEL</sub>  | Voltage Reference Select (VAREFSEL) Hold Time  | 0.67   | 0.76   | 0.89   | ns    |

| tsuchnum                 | Channel Select (CHNUMBER) Setup Time           | 0.90   | 1.03   | 1.21   | ns    |

| t <sub>HDCHNUM</sub>     | Channel Select (CHNUMBER) Hold Time            | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>SUADCSTART</sub>  | Start of Conversion (ADCSTART) Setup Time      | 0.75   | 0.85   | 1.00   | ns    |

| t <sub>HDADCSTART</sub>  | Start of Conversion (ADCSTART) Hold Time       | 0.43   | 0.49   | 0.57   | ns    |

| t <sub>CK2QBUSY</sub>    | Busy Clock-to-Q                                | 1.33   | 1.51   | 1.78   | ns    |

| t <sub>CK2QCAL</sub>     | Power-Up Calibration Clock-to-Q                | 0.63   | 0.71   | 0.84   | ns    |

| t <sub>CK2QVAL</sub>     | Valid Conversion Result Clock-to-Q             | 3.12   | 3.55   | 4.17   | ns    |

| t <sub>CK2QSAMPLE</sub>  | Sample Clock-to-Q                              | 0.22   | 0.25   | 0.30   | ns    |

| t <sub>CK2QRESULT</sub>  | Conversion Result Clock-to-Q                   | 2.53   | 2.89   | 3.39   | ns    |

| t <sub>CLR2QBUSY</sub>   | Busy Clear-to-Q                                | 2.06   | 2.35   | 2.76   | ns    |

| t <sub>CLR2QCAL</sub>    | Power-Up Calibration Clear-to-Q                | 2.15   | 2.45   | 2.88   | ns    |

| t <sub>CLR2QVAL</sub>    | Valid Conversion Result Clear-to-Q             | 2.41   | 2.74   | 3.22   | ns    |

| t <sub>CLR2QSAMPLE</sub> | Sample Clear-to-Q                              | 2.17   | 2.48   | 2.91   | ns    |

| t <sub>CLR2QRESULT</sub> | Conversion result Clear-to-Q                   | 2.25   | 2.56   | 3.01   | ns    |

| t <sub>RECCLR</sub>      | Recovery Time of Clear                         | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>REMCLR</sub>      | Removal Time of Clear                          | 0.63   | 0.72   | 0.84   | ns    |

| t <sub>MPWSYSCLK</sub>   | Clock Minimum Pulse Width for the ADC          | 4.00   | 4.00   | 4.00   | ns    |

| t <sub>FMAXSYSCLK</sub>  | Clock Maximum Frequency for the ADC            | 100.00 | 100.00 | 100.00 | MHz   |

Table 2-54 • ACM Address Decode Table for Analog Quad (continued)

| ACMADDR [7:0] in Decimal                                                                    | Name       | Description                                       | Associated<br>Peripheral |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|------------|---------------------------------------------------|--------------------------|--|--|--|--|--|--|

| 73                                                                                          | MATCHREG1  | Match register bits 15:8                          | RTC                      |  |  |  |  |  |  |

| 74                                                                                          | MATCHREG2  | Match register bits 23:16                         | RTC                      |  |  |  |  |  |  |

| 75                                                                                          | MATCHREG3  | Match register bits 31:24                         | RTC                      |  |  |  |  |  |  |

| 76                                                                                          | MATCHREG4  | Match register bits 39:32                         | RTC                      |  |  |  |  |  |  |

| 80                                                                                          | MATCHBITS0 | Individual match bits 7:0                         | RTC                      |  |  |  |  |  |  |

| 81                                                                                          | MATCHBITS1 | Individual match bits 15:8                        | RTC                      |  |  |  |  |  |  |

| 82                                                                                          | MATCHBITS2 | Individual match bits 23:16                       | RTC                      |  |  |  |  |  |  |

| 83                                                                                          | MATCHBITS3 | Individual match bits 31:24                       | RTC                      |  |  |  |  |  |  |

| 84                                                                                          | MATCHBITS4 | Individual match bits 39:32                       | RTC                      |  |  |  |  |  |  |

| 88                                                                                          | CTRL_STAT  | Control (write) / Status (read) register bits 7:0 | RTC                      |  |  |  |  |  |  |

| Note: ACMADDR bytes 1 to 40 pertain to the Analog Quads; bytes 64 to 89 pertain to the RTC. |            |                                                   |                          |  |  |  |  |  |  |

# **ACM Characteristics<sup>1</sup>**

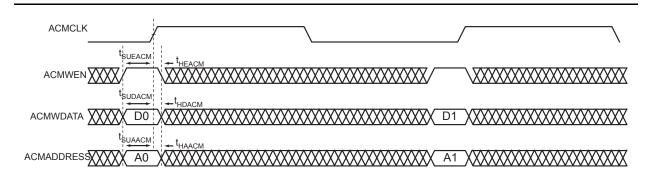

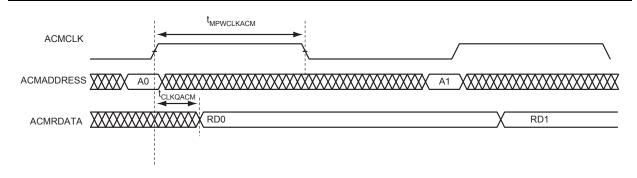

Figure 2-97 • ACM Write Waveform

Figure 2-98 • ACM Read Waveform

2-127 Revision 6

<sup>1.</sup> When addressing the RTC addresses (i.e., ACMADDR 64 to 89), there is no timing generator, and the rc\_osc, byte\_en, and aq\_wen signals have no impact.

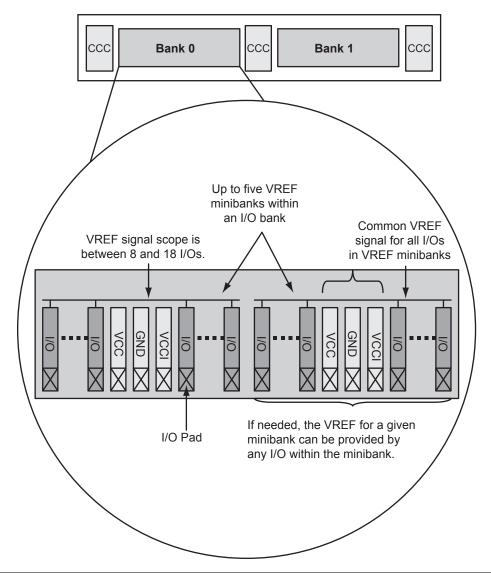

Figure 2-99 • Fusion Pro I/O Bank Detail Showing VREF Minibanks (north side of AFS600 and AFS1500)

Table 2-67 • I/O Standards Supported by Bank Type

| I/O Bank     | Single-Ended I/O Standards                                                                        | Differential I/O<br>Standards | Voltage-Referenced                                                                                    | Hot-<br>Swap |

|--------------|---------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|--------------|

| Standard I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V                          | _                             | _                                                                                                     | Yes          |

| Advanced I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | _                                                                                                     | _            |

| Pro I/O      | LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V / 1.8 V / 1.5 V, LVCMOS 2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X       | LVPECL and<br>LVDS            | GTL+2.5 V / 3.3 V, GTL 2.5 V / 3.3 V, HSTL Class I and II, SSTL2 Class I and II, SSTL3 Class I and II | Yes          |

2-133 Revision 6

# Features Supported on Pro I/Os

Table 2-72 lists all features supported by transmitter/receiver for single-ended and differential I/Os.

### Table 2-72 • Fusion Pro I/O Features

| Feature                                             | Description                                                                                                                                                                                                                            |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-ended and voltage-<br>referenced transmitter | <ul> <li>Hot insertion in every mode except PCI or 5 V input tolerant (these modes use<br/>clamp diodes and do not allow hot insertion)</li> </ul>                                                                                     |

| features                                            | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                                         |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                                                             |

|                                                     | Two slew rates                                                                                                                                                                                                                         |

|                                                     | <ul> <li>Skew between output buffer enable/disable time: 2 ns delay (rising edge) and<br/>0 ns delay (falling edge); see "Selectable Skew between Output Buffer<br/>Enable/Disable Time" on page 2-149 for more information</li> </ul> |

|                                                     | Five drive strengths                                                                                                                                                                                                                   |

|                                                     | 5 V-tolerant receiver ("5 V Input Tolerance" section on page 2-144)                                                                                                                                                                    |

|                                                     | <ul> <li>LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs ("5 V Output<br/>Tolerance" section on page 2-148)</li> </ul>                                                                                                       |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

| Single-ended receiver features                      | Schmitt trigger option                                                                                                                                                                                                                 |

|                                                     | ESD protection                                                                                                                                                                                                                         |

|                                                     | <ul> <li>Programmable delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                             |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Separate ground planes, GND/GNDQ, for input buffers only to avoid output-<br/>induced noise in the input circuitry</li> </ul>                                                                                                 |

| Voltage-referenced differential receiver features   | <ul> <li>Programmable Delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                             |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Separate ground planes, GND/GNDQ, for input buffers only to avoid output-<br/>induced noise in the input circuitry</li> </ul>                                                                                                 |

| CMOS-style LVDS, BLVDS, M-LVDS, or LVPECL           | <ul> <li>Two I/Os and external resistors are used to provide a CMOS-style LVDS,<br/>BLVDS, M-LVDS, or LVPECL transmitter solution.</li> </ul>                                                                                          |

| transmitter                                         | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                                         |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                                                             |

|                                                     | Fast slew rate                                                                                                                                                                                                                         |

| LVDS/LVPECL differential                            | ESD protection                                                                                                                                                                                                                         |

| receiver features                                   | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Programmable delay: 0.625 ns with '000' setting, 6.575 ns with '111' setting,<br/>0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                                           |

|                                                     | Separate input buffer ground and power planes to avoid output-induced noise in the input circuitry                                                                                                                                     |

Table 2-96 • I/O Output Buffer Maximum Resistances <sup>1</sup> (continued)

| Standard                      | Drive Strength              | R <sub>PULL-DOWN</sub> (ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|-------------------------------|-----------------------------|--------------------------------------------|---------------------------------------------|

| HSTL (I)                      | 8 mA                        | 50                                         | 50                                          |

| HSTL (II)                     | 15 mA                       | 25                                         | 25                                          |

| SSTL2 (I)                     | 17 mA                       | 27                                         | 31                                          |

| SSTL2 (II)                    | 21 mA                       | 13                                         | 15                                          |

| SSTL3 (I)                     | 16 mA                       | 44                                         | 69                                          |

| SSTL3 (II)                    | 24 mA                       | 18                                         | 32                                          |

| Applicable to Advanced I/O Ba | nks                         | 1                                          |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS    | 2 mA                        | 100                                        | 300                                         |

|                               | 4 mA                        | 100                                        | 300                                         |

|                               | 6 mA                        | 50                                         | 150                                         |

|                               | 8 mA                        | 50                                         | 150                                         |

|                               | 12 mA                       | 25                                         | 75                                          |

|                               | 16 mA                       | 17                                         | 50                                          |

|                               | 24 mA                       | 11                                         | 33                                          |

| 2.5 V LVCMOS                  | 2 mA                        | 100                                        | 200                                         |

|                               | 4 mA                        | 100                                        | 200                                         |

|                               | 6 mA                        | 50                                         | 100                                         |

|                               | 8 mA                        | 50                                         | 100                                         |

|                               | 12 mA                       | 25                                         | 50                                          |

|                               | 16 mA                       | 20                                         | 40                                          |

|                               | 24 mA                       | 11                                         | 22                                          |

| 1.8 V LVCMOS                  | 2 mA                        | 200                                        | 225                                         |

|                               | 4 mA                        | 100                                        | 112                                         |

|                               | 6 mA                        | 50                                         | 56                                          |

|                               | 8 mA                        | 50                                         | 56                                          |

|                               | 12 mA                       | 20                                         | 22                                          |

|                               | 16 mA                       | 20                                         | 22                                          |

| 1.5 V LVCMOS                  | 2 mA                        | 200                                        | 224                                         |

|                               | 4 mA                        | 100                                        | 112                                         |

|                               | 6 mA                        | 67                                         | 75                                          |

|                               | 8 mA                        | 33                                         | 37                                          |

|                               | 12 mA                       | 33                                         | 37                                          |

| 3.3 V PCI/PCI-X               | Per PCI/PCI-X specification | 25                                         | 75                                          |

### Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

<sup>2.</sup>  $R_{(PULL-DOWN-MAX)} = VOLspec / I_{OLspec}$

<sup>3.</sup> R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

### 2.5 V LVCMOS

Low-Voltage CMOS for 2.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 2.5 V applications.

Table 2-110 • Minimum and Maximum DC Input and Output Levels

| 2.5 V<br>LVCMOS   | v          | IL        | V         | IH        | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|------------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V  | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| Applicable to     | Pro I/O Ba | nks       |           |           |           | •         | •   |    |                         |                         |                         |                         |

| 4 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10                      | 10                      |

| 8 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10                      | 10                      |

| 12 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 12  | 12 | 74                      | 65                      | 10                      | 10                      |

| 16 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 16  | 16 | 87                      | 83                      | 10                      | 10                      |

| 24 mA             | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 24  | 24 | 124                     | 169                     | 10                      | 10                      |

| Applicable to     | Advanced   | I/O Bank  | s         |           |           | •         |     |    |                         |                         |                         |                         |

| 2 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 2   | 2  | 18                      | 16                      | 10                      | 10                      |

| 4 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10                      | 10                      |

| 6 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 6   | 6  | 37                      | 32                      | 10                      | 10                      |

| 8 mA              | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10                      | 10                      |

| 12 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 12  | 12 | 74                      | 65                      | 10                      | 10                      |

| 16 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 16  | 16 | 87                      | 83                      | 10                      | 10                      |

| 24 mA             | -0.3       | 0.7       | 1.7       | 2.7       | 0.7       | 1.7       | 24  | 24 | 124                     | 169                     | 10                      | 10                      |

| Applicable to     | Standard   | /O Banks  |           |           |           | •         |     |    |                         |                         |                         |                         |

| 2 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 2   | 2  | 18                      | 16                      | 10                      | 10                      |

| 4 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4  | 18                      | 16                      | 10                      | 10                      |

| 6 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 6   | 6  | 37                      | 32                      | 10                      | 10                      |

| 8 mA              | -0.3       | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8  | 37                      | 32                      | 10                      | 10                      |

### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

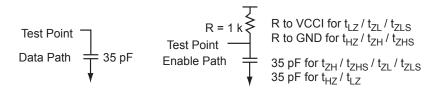

Figure 2-120 • AC Loading

Table 2-111 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 2.5            | 1.2                  | _               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

2-181 Revision 6

### 1.8 V LVCMOS

Low-Voltage CMOS for 1.8 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.8 V applications. It uses a 1.8 V input buffer and push-pull output buffer.

Table 2-118 • Minimum and Maximum DC Input and Output Levels

| 1.8 V<br>LVCMOS   |            | VIL           | VIH         |           | VOL       | VOH         | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|------------|---------------|-------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V  | Max.<br>V     | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| Applicable        | to Pro I/0 | O Banks       |             |           |           |             |     |    |                         |                         | •                       |                         |

| 2 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 2   | 2  | 11                      | 9                       | 10                      | 10                      |

| 4 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 4   | 4  | 22                      | 17                      | 10                      | 10                      |

| 6 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 6   | 6  | 44                      | 35                      | 10                      | 10                      |

| 8 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 8   | 8  | 51                      | 45                      | 10                      | 10                      |

| 12 mA             | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 3.6       | 0.45      | VCCI-0.45   | 12  | 12 | 74                      | 91                      | 10                      | 10                      |

| 16 mA             | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 16  | 16 | 74                      | 91                      | 10                      | 10                      |

| Applicable        | to Advar   | nced I/O Bank | (S          |           |           |             |     |    |                         |                         | •                       |                         |

| 2 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 2   | 2  | 11                      | 9                       | 10                      | 10                      |

| 4 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 4   | 4  | 22                      | 17                      | 10                      | 10                      |

| 6 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 6   | 6  | 44                      | 35                      | 10                      | 10                      |

| 8 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 8   | 8  | 51                      | 45                      | 10                      | 10                      |

| 12 mA             | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 1.9       | 0.45      | VCCI-0.45   | 12  | 12 | 74                      | 91                      | 10                      | 10                      |

| 16 mA             | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 1.9       | 0.45      | VCCI - 0.45 | 16  | 16 | 74                      | 91                      | 10                      | 10                      |

| Applicable        | to Stand   | ard I/O Banks | 5           |           | •         | •           |     |    |                         |                         |                         |                         |

| 2 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 3.6       | 0.45      | VCCI - 0.45 | 2   | 2  | 11                      | 9                       | 10                      | 10                      |

| 4 mA              | -0.3       | 0.35 * VCCI   | 0.65 * VCCI | 3.6       | 0.45      | VCCI-0.45   | 4   | 4  | 22                      | 17                      | 10                      | 10                      |

| Notes:            |            |               |             |           |           |             |     |    |                         |                         |                         |                         |

### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

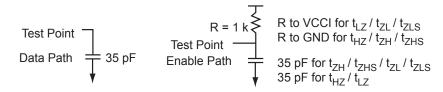

Figure 2-121 • AC Loading

Table 2-119 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input Low (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|---------------|----------------------|-----------------|------------------------|

| 0             | 1.8           | 0.9                  | _               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

2-187 Revision 6

### SSTL2 Class I

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). Fusion devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-156 • Minimum and Maximum DC Input and Output Levels

| SSTL2 Class I     |           | VIL        | VIH        |           | VOL       | VOH         | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|------------|------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 15 mA             | -0.3      | VREF - 0.2 | VREF + 0.2 | 3.6       | 0.54      | VCCI - 0.62 | 15  | 15 | 87                      | 83                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

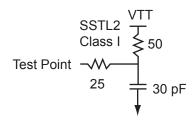

### Figure 2-130 • AC Loading

Table 2-157 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF - 0.2    | VREF + 0.2     | 1.25                 | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

### **Timing Characteristics**

Table 2-158 • SSTL 2 Class I

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.25 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.13            | 0.04             | 1.33            | 0.43              | 2.17            | 1.85            |                 |                 | 4.40             | 4.08             | ns    |

| <b>-1</b>      | 0.56              | 1.81            | 0.04             | 1.14            | 0.36              | 1.84            | 1.57            |                 |                 | 3.74             | 3.47             | ns    |

| -2             | 0.49              | 1.59            | 0.03             | 1.00            | 0.32              | 1.62            | 1.38            |                 |                 | 3.29             | 3.05             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-205 Revision 6

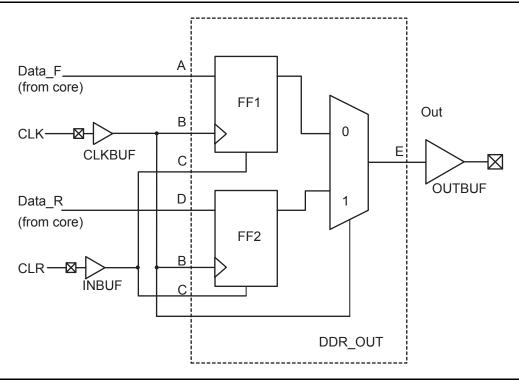

# **Output DDR**

Figure 2-144 • Output DDR Timing Model

Table 2-181 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (From, To) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | C, B                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | C, B                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | A, B                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | A, B                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

2-221 Revision 6

### ATRTN*x* Temperature Monitor Return

*AT returns* are the returns for the temperature sensors. The cathode terminal of the external diodes should be connected to these pins. There is one analog return pin for every two Analog Quads. The x in the ATRTNx designator indicates the quad pairing (x = 0 for AQ1 and AQ2, x = 1 for AQ2 and AQ3, ..., x = 4 for AQ8 and AQ9). The signals that drive these pins are called out as ATRETURNxy in the software (where x and y refer to the quads that share the return signal). ATRTN is internally connected to ground. It can be left floating when it is unused. The maximum capacitance allowed across the AT pins is 500 pF.

#### GL Globals

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as Pro I/Os since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors. See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits" section on page 2-22.

Refer to the "User I/O Naming Convention" section on page 2-158 for a description of naming of global pins.

### **JTAG Pins**

Fusion devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the Fusion part must be supplied to allow JTAG signals to transition the Fusion device.

Isolating the JTAG power supply in a separate I/O bank gives greater flexibility with supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRST pin could be tied to GND.

#### TCK Test Clock

Test clock input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pull-up/-down resistor. If JTAG is not used, Microsemi recommends tying off TCK to GND or VJTAG through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements. Refer to Table 2-183 for more information.

Table 2-183 • Recommended Tie-Off Values for the TCK and TRST Pins

| VJTAG          | Tie-Off Resistance <sup>2, 3</sup> |

|----------------|------------------------------------|

| VJTAG at 3.3 V | 200 $\Omega$ to 1 k $\Omega$       |

| VJTAG at 2.5 V | 200 $\Omega$ to 1 k $\Omega$       |

| VJTAG at 1.8 V | 500 $\Omega$ to 1 k $\Omega$       |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                      |

### Notes:

- 1. Equivalent parallel resistance if more than one device is on JTAG chain.

- 2. The TCK pin can be pulled up/down.

- 3. The TRST pin can only be pulled down.

### TDI Test Data Input

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

### TDO Test Data Output

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

# RC Oscillator Dynamic Contribution—P<sub>RC-OSC</sub>

### **Operating Mode**

P<sub>RC-OSC</sub> = PAC19

Standby Mode and Sleep Mode

$P_{RC-OSC} = 0 W$

### Analog System Dynamic Contribution—PAR

### **Operating Mode**

$P_{AB} = PAC20$

Standby Mode and Sleep Mode

$P_{AB} = 0 W$

### Guidelines

### **Toggle Rate Definition**

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that the net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100%, as all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ..

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + ... 0.78125%) / 8.

### **Enable Rate Definition**

Output enable rate is the average percentage of time during which tristate outputs are enabled. When non-tristate output buffers are used, the enable rate should be 100%.

Table 3-16 • Toggle Rate Guidelines Recommended for Power Calculation

| Component  | Definition                       | Guideline |

|------------|----------------------------------|-----------|

| $\alpha_1$ | Toggle rate of VersaTile outputs | 10%       |

| $\alpha_2$ | I/O buffer toggle rate           | 10%       |

### Table 3-17 • Enable Rate Guidelines Recommended for Power Calculation

| Component | Definition                           | Guideline |

|-----------|--------------------------------------|-----------|

| $\beta_1$ | I/O output buffer enable rate        | 100%      |

| $\beta_2$ | RAM enable rate for read operations  | 12.5%     |

| $\beta_3$ | RAM enable rate for write operations | 12.5%     |

| $\beta_4$ | NVM enable rate for read operations  | 0%        |

3-27 Revision 6

Fusion Family of Mixed Signal FPGAs

|               | PQ208           |                 |  |  |  |

|---------------|-----------------|-----------------|--|--|--|

| Pin<br>Number | AFS250 Function | AFS600 Function |  |  |  |

| 74            | AV2             | AV4             |  |  |  |

| 75            | AC2             | AC4             |  |  |  |

| 76            | AG2             | AG4             |  |  |  |

| 77            | AT2             | AT4             |  |  |  |

| 78            | ATRTN1          | ATRTN2          |  |  |  |

| 79            | AT3             | AT5             |  |  |  |

| 80            | AG3             | AG5             |  |  |  |

| 81            | AC3             | AC5             |  |  |  |

| 82            | AV3             | AV5             |  |  |  |

| 83            | AV4             | AV6             |  |  |  |

| 84            | AC4             | AC6             |  |  |  |

| 85            | AG4             | AG6             |  |  |  |

| 86            | AT4             | AT6             |  |  |  |

| 87            | ATRTN2          | ATRTN3          |  |  |  |

| 88            | AT5             | AT7             |  |  |  |

| 89            | AG5             | AG7             |  |  |  |

| 90            | AC5             | AC7             |  |  |  |

| 91            | AV5             | AV7             |  |  |  |

| 92            | NC              | AV8             |  |  |  |

| 93            | NC              | AC8             |  |  |  |

| 94            | NC              | AG8             |  |  |  |

| 95            | NC              | AT8             |  |  |  |

| 96            | NC              | ATRTN4          |  |  |  |

| 97            | NC              | AT9             |  |  |  |

| 98            | NC              | AG9             |  |  |  |

| 99            | NC              | AC9             |  |  |  |

| 100           | NC              | AV9             |  |  |  |

| 101           | GNDAQ           | GNDAQ           |  |  |  |

| 102           | VCC33A          | VCC33A          |  |  |  |

| 103           | ADCGNDREF       | ADCGNDREF       |  |  |  |

| 104           | VAREF           | VAREF           |  |  |  |

| 105           | PUB             | PUB             |  |  |  |

| 106           | VCC33A          | VCC33A          |  |  |  |

| 107           | GNDA            | GNDA            |  |  |  |

| 108           | PTEM            | PTEM            |  |  |  |

| 109           | PTBASE          | PTBASE          |  |  |  |

| 110           | GNDNVM          | GNDNVM          |  |  |  |

| PQ208           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                 | AFS600 Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                 | VCCNVM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                 | VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                 | VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                 | VPUMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| GNDQ            | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| VCCIB1          | TCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TCK             | TDI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TDI             | TMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TMS             | TDO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| TDO             | TRST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| TRST            | VJTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| VJTAG           | IO57NDB2V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| IO57NDB1V0      | GDC2/IO57PDB2V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| GDC2/IO57PDB1V0 | IO56NDB2V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| IO56NDB1V0      | GDB2/IO56PDB2V0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |