Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

# Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Obsolete                                                       |

| Number of LABs/CLBs            | -                                                              |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | 110592                                                         |

| Number of I/O                  | 95                                                             |

| Number of Gates                | 600000                                                         |

| Voltage - Supply               | 1.425V ~ 1.575V                                                |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                |

| Package / Case                 | 208-BFQFP                                                      |

| Supplier Device Package        | 208-PQFP (28x28)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs600-1pq208 |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Related Documents**

# Datasheet

Core8051 www.microsemi.com/soc/ipdocs/Core8051\_DS.pdf

# **Application Notes**

Fusion FlashROM http://www.microsemi.com/soc/documents/Fusion\_FROM\_AN.pdf Fusion SRAM/FIFO Blocks http://www.microsemi.com/soc/documents/Fusion\_RAM\_FIFO\_AN.pdf Using DDR in Fusion Devices http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129938 Fusion Security http://www.microsemi.com/soc/documents/Fusion\_Security\_AN.pdf Using Fusion RAM as Multipliers http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129940

# Handbook

Cortex-M1 Handbook www.microsemi.com/soc/documents/CortexM1\_HB.pdf

# **User Guides**

Designer User Guide http://www.microsemi.com/soc/documents/designer\_UG.pdf Fusion FPGA Fabric User Guide http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=130817 IGLOO, ProASIC3, SmartFusion and Fusion Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen, FlashROM, Flash Memory System Builder, and Analog System Builder User Guide http://www.microsemi.com/soc/documents/genguide\_ug.pdf

# **White Papers**

Fusion Technology http://www.microsemi.com/soc/documents/Fusion\_Tech\_WP.pdf

# **Routing Architecture**

The routing structure of Fusion devices is designed to provide high performance through a flexible four-level hierarchy of routing resources: ultra-fast local resources; efficient long-line resources; high-speed very-long-line resources; and the high-performance VersaNet networks.

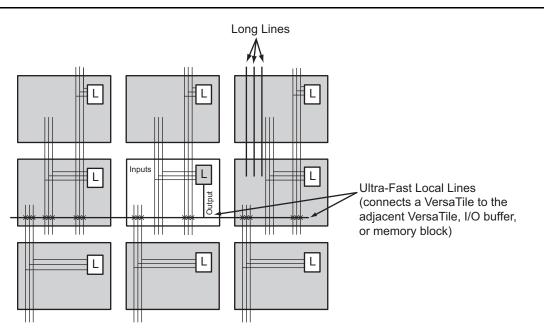

The ultra-fast local resources are dedicated lines that allow the output of each VersaTile to connect directly to every input of the eight surrounding VersaTiles (Figure 2-8). The exception to this is that the SET/CLR input of a VersaTile configured as a D-flip-flop is driven only by the VersaNet global network.

The efficient long-line resources provide routing for longer distances and higher-fanout connections. These resources vary in length (spanning one, two, or four VersaTiles), run both vertically and horizontally, and cover the entire Fusion device (Figure 2-9 on page 2-9). Each VersaTile can drive signals onto the efficient long-line resources, which can access every input of every VersaTile. Active buffers are inserted automatically by routing software to limit loading effects.

The high-speed very-long-line resources, which span the entire device with minimal delay, are used to route very long or high-fanout nets: length  $\pm 12$  VersaTiles in the vertical direction and length  $\pm 16$  in the horizontal direction from a given core VersaTile (Figure 2-10 on page 2-10). Very long lines in Fusion devices, like those in ProASIC3 devices, have been enhanced. This provides a significant performance boost for long-reach signals.

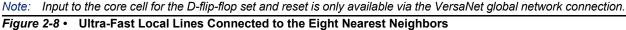

The high-performance VersaNet global networks are low-skew, high-fanout nets that are accessible from external pins or from internal logic (Figure 2-11 on page 2-11). These nets are typically used to distribute clocks, reset signals, and other high-fanout nets requiring minimum skew. The VersaNet networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically, with signals accessing every input on all VersaTiles.

| Figure 2-12 • Global Network Architecture | ; |

|-------------------------------------------|---|

|-------------------------------------------|---|

# Table 2-4 • Globals/Spines/Rows by Device

|                                        | AFS090 | AFS250 | AFS600 | AFS1500 |

|----------------------------------------|--------|--------|--------|---------|

| Global VersaNets (trees)*              | 9      | 9      | 9      | 9       |

| VersaNet Spines/Tree                   | 4      | 8      | 12     | 20      |

| Total Spines                           | 36     | 72     | 108    | 180     |

| VersaTiles in Each Top or Bottom Spine | 384    | 768    | 1,152  | 1,920   |

| Total VersaTiles                       | 2,304  | 6,144  | 13,824 | 38,400  |

Note: \*There are six chip (main) globals and three globals per quadrant.

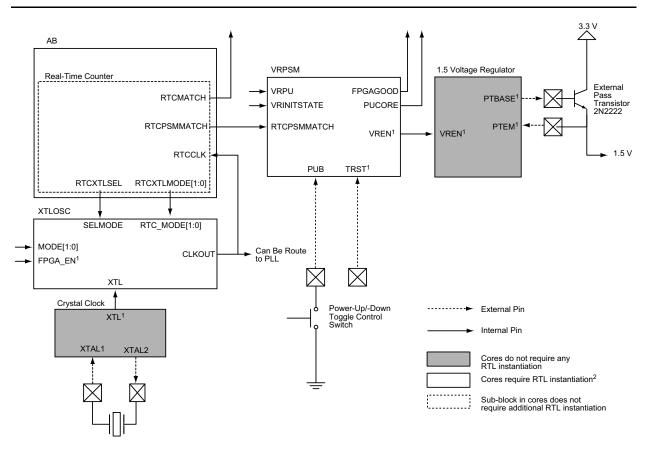

# **Real-Time Counter System**

The RTC system enables Fusion devices to support standby and sleep modes of operation to reduce power consumption in many applications.

- Sleep mode, typical 10 µA

- · Standby mode (RTC running), typical 3 mA with 20 MHz

The RTC system is composed of five cores:

- RTC sub-block inside Analog Block (AB)

- Voltage Regulator and Power System Monitor (VRPSM)

- Crystal oscillator (XTLOSC); refer to the "Crystal Oscillator" section in the Fusion Clock Resources chapter of the *Fusion FPGA Fabric User Guide* for more detail.

- Crystal clock; does not require instantiation in RTL

- 1.5 V voltage regulator; does not require instantiation in RTL

All cores are powered by 3.3 V supplies, so the RTC system is operational without a 1.5 V supply during standby mode. Figure 2-27 shows their connection.

#### Notes:

- 1. Signals are hardwired internally and do not exist in the macro core.

- 2. User is only required to instantiate the VRPSM macro if the user wishes to specify PUPO behavior of the voltage regulator to be different from the default, or employ user logic to shut the voltage regulator off.

Figure 2-27 • Real-Time Counter System (not all the signals are shown for the AB macro)

# **Modes of Operation**

# Standby Mode

Standby mode allows periodic power-up and power-down of the FPGA fabric. In standby mode, the real-time counter and crystal block are ON. The FPGA is not powered by disabling the 1.5 V voltage regulator. The 1.5 V voltage regulator can be enabled when the preset count is matched. Refer to the "Real-Time Counter (part of AB macro)" section for details. To enter standby mode, the RTC must be first configured and enabled. Then VRPSM is shut off by deasserting the VRPU signal. The 1.5 V voltage regulator is then disabled, and shuts off the 1.5 V output.

# Sleep Mode

In sleep mode, the real-time counter and crystal blocks are OFF. The 1.5 V voltage regulator inside the VRPSM can only be enabled by the PUB or TRST pin. Refer to the "Voltage Regulator and Power System Monitor (VRPSM)" section on page 2-36 for details on power-up and power-down of the 1.5 V voltage regulator.

# Standby and Sleep Mode Circuit Implementation

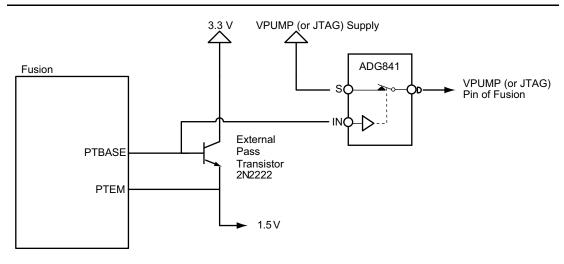

For extra power savings, VJTAG and VPUMP should be at the same voltage as VCC, floated or ground, during standby and sleep modes. Note that when VJTAG is not powered, the 1.5 V voltage regulator cannot be enabled through TRST.

VPUMP and VJTAG can be controlled through an external switch. Microsemi recommends ADG839, ADG849, or ADG841 as possible switches. Figure 2-28 shows the implementation for controlling VPUMP. The IN signal of the switch can be connected to PTBASE of the Fusion device. VJTAG can be controlled in same manner.

Figure 2-28 • Implementation to Control VPUMP

# Table 2-16 • RTC Control/Status Register

| Bit | Name         | Description                                                                                                                                                                                                           | Default<br>Value |

|-----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 7   | rtc_rst      | RTC Reset                                                                                                                                                                                                             |                  |

|     |              | 1 – Resets the RTC                                                                                                                                                                                                    |                  |

|     |              | 0 – Deassert reset on after two ACM_CLK cycle.                                                                                                                                                                        |                  |

| 6   | cntr_en      | Counter Enable                                                                                                                                                                                                        | 0                |

|     |              | 1 – Enables the counter; rtc_rst must be deasserted as well. First counter increments after 64 RTCCLK positive edges.                                                                                                 |                  |

|     |              | 0 – Disables the crystal prescaler but does not reset the counter value. Counter value can only be updated when the counter is disabled.                                                                              |                  |

| 5   | vr_en_mat    | Voltage Regulator Enable on Match                                                                                                                                                                                     | 0                |

|     |              | 1 – Enables RTCMATCH and RTCPSMMATCH to output 1 when the counter value equals the Match Register value. This enables the 1.5 V voltage regulator when RTCPSMMATCH connects to the RTCPSMMATCH signal in VRPSM.       |                  |

|     |              | 0 – RTCMATCH and RTCPSMMATCH output 0 at all times.                                                                                                                                                                   |                  |

| 4:3 | xt_mode[1:0] | Crystal Mode                                                                                                                                                                                                          | 00               |

|     |              | Controls RTCXTLMODE[1:0]. Connects to RTC_MODE signal in XTLOSC. XTL_MODE uses this value when xtal_en is 1. See the "Crystal Oscillator" section on page 2-20 for mode configuration.                                |                  |

| 2   | rst_cnt_omat | Reset Counter on Match                                                                                                                                                                                                | 0                |

|     |              | 1 – Enables the sync clear of the counter when the counter value equals the Match Register value. The counter clears on the rising edge of the clock. If all the Match Registers are set to 0, the clear is disabled. |                  |

|     |              | 0 – Counter increments indefinitely                                                                                                                                                                                   |                  |

| 1   | rstb_cnt     | Counter Reset, active Low                                                                                                                                                                                             | 0                |

|     |              | 0 - Resets the 40-bit counter value                                                                                                                                                                                   |                  |

| 0   | xtal_en      | Crystal Enable                                                                                                                                                                                                        | 0                |

|     |              | Controls RTCXTLSEL. Connects to SELMODE signal in XTLOSC.                                                                                                                                                             |                  |

|     |              | 0 – XTLOSC enables control by FPGA_EN; xt_mode is not used. Sleep mode requires this bit to equal 0.                                                                                                                  |                  |

|     |              | 1 – Enables XTLOSC, XTL_MODE control by xt_mode                                                                                                                                                                       |                  |

|     |              | Standby mode requires this bit to be set to 1.                                                                                                                                                                        |                  |

|     |              | See the "Crystal Oscillator" section on page 2-20 for further details on SELMODE configuration.                                                                                                                       |                  |

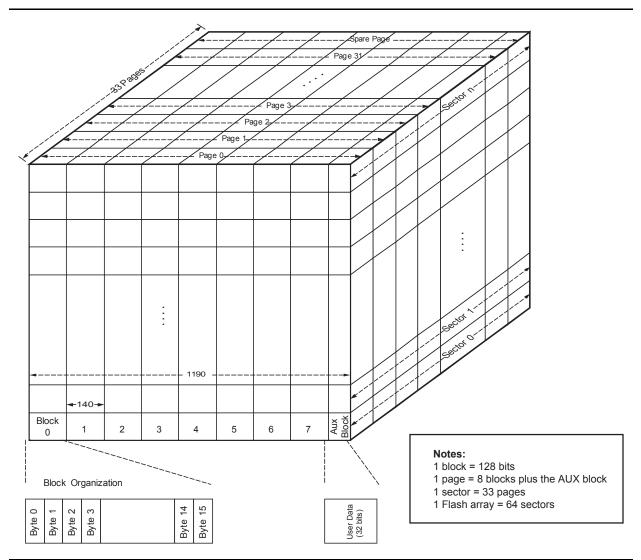

# Flash Memory Block Addressing

Figure 2-34 shows a graphical representation of the flash memory block.

Figure 2-34 • Flash Memory Block Organization

Each FB is partitioned into sectors, pages, blocks, and bytes. There are 64 sectors in an FB, and each sector contains 32 pages and 1 spare page. Each page contains 8 data blocks and 1 auxiliary block. Each data block contains 16 bytes of user data, and the auxiliary block contains 4 bytes of user data. Addressing for the FB is shown in Table 2-20.

#### Table 2-20 • FB Address Bit Allocation ADDR[17:0]

| 17  | 12   | 11   | 7 | 6   | 4   | 3  | 0   |

|-----|------|------|---|-----|-----|----|-----|

| Sec | ctor | Page |   | Blo | ock | Ву | /te |

When the spare page of a sector is addressed (SPAREPAGE active), ADDR[11:7] are ignored.

When the Auxiliary block is addressed (AUXBLOCK active), ADDR[6:2] are ignored.

Note: The spare page of sector 0 is unavailable for any user data. Writes to this page will return an error, and reads will return all zeroes.

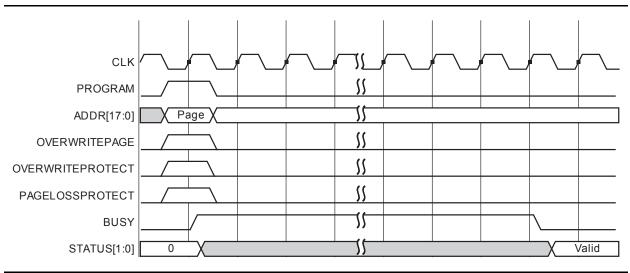

# **Program Operation**

A Program operation is initiated by asserting the PROGRAM signal on the interface. Program operations save the contents of the Page Buffer to the FB Array. Due to the technologies inherent in the FB, the total programming (including erase) time per page of the eNVM is 6.8 ms. While the FB is writing the data to the array, the BUSY signal will be asserted.

During a Program operation, the sector and page addresses on ADDR are compared with the stored address for the page (and sector) in the Page Buffer. If there is a mismatch between the two addresses, the Program operation will be aborted and an error will be reported on the STATUS output.

It is possible to write the Page Buffer to a different page in memory. When asserting the PROGRAM pin, if OVERWRITEPAGE is asserted as well, the FB will write the contents of the Page Buffer to the sector and page designated on the ADDR inputs if the destination page is not Overwrite Protected.

A Program operation can be utilized to either modify the contents of the page in the flash memory block or change the protections for the page. Setting the OVERWRITEPROTECT bit on the interface while asserting the PROGRAM pin will put the page addressed into Overwrite Protect Mode. Overwrite Protect Mode safeguards a page from being inadvertently overwritten during subsequent Program or Erase operations.

Program operations that result in a STATUS value of '01' do not modify the addressed page. For all other values of STATUS, the addressed page is modified. Program errors include the following:

- 1. Attempting to program a page that is Overwrite Protected (STATUS = '01')

- 2. Attempting to program a page that is not in the Page Buffer when the Page Buffer has entered Page Loss Protection Mode (STATUS = '01')

- Attempting to perform a program with OVERWRITEPAGE set when the page addressed has been Overwrite Protected (STATUS = '01')

- 4. The Write Count of the page programmed exceeding the Write Threshold defined in the part specification (STATUS = '11')

- 5. The ECC Logic determining that there is an uncorrectable error within the programmed page (STATUS = '10')

- 6. Attempting to program a page that is **not** in the Page Buffer when OVERWRITEPAGE is not set and the page in the Page Buffer is modified (STATUS = '01')

- 7. Attempting to program the page in the Page Buffer when the Page Buffer is **not** modified

The waveform for a Program operation is shown in Figure 2-36.

# Figure 2-36 • FB Program Waveform

Note: OVERWRITEPAGE is only sampled when the PROGRAM or ERASEPAGE pins are asserted. OVERWRITEPAGE is ignored in all other operations.

Conversely, when writing 4-bit values and reading 9-bit values, the ninth bit of a read operation will be undefined. The RAM blocks employ little-endian byte order for read and write operations.

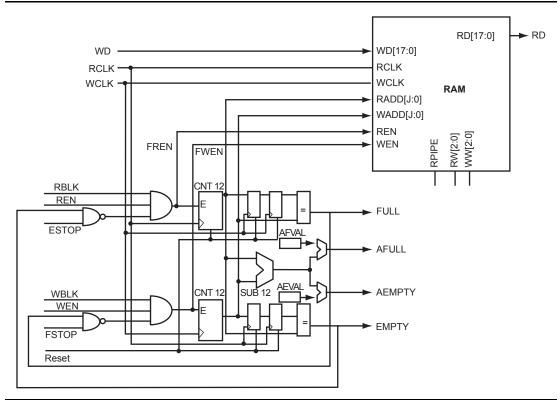

Figure 2-47 • Fusion RAM Block with Embedded FIFO Controller

### *Table 2-32* • RAM512X18

# Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                        | -2   | -1   | Std. | Units |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                 | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                  | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                | 0.09 | 0.10 | 0.12 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                 | 0.06 | 0.07 | 0.08 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained)                                                               | 2.16 | 2.46 | 2.89 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                     |      | 1.02 | 1.20 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge |      | 0.43 | 0.38 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address—Applicable to Opening Edge |      | 0.50 | 0.44 | ns    |

| + 1                   | RESET Low to data out Low on RD (flow-through)                                                                     | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>RSTBQ</sub> 1  | RESET Low to data out Low on RD (pipelined)                                                                        | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                      | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                     | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                          |      | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                   | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                  | 310  | 272  | 231  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

2. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

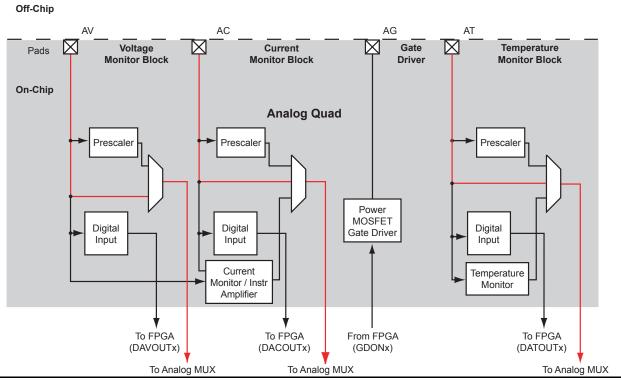

# Voltage Monitor

The Fusion Analog Quad offers a robust set of voltage-monitoring capabilities unique in the FPGA industry. The Analog Quad comprises three analog input pads— Analog Voltage (AV), Analog Current (AC), and Analog Temperature (AT)—and a single gate driver output pad, Analog Gate (AG). There are many common characteristics among the analog input pads. Each analog input can be configured to connect directly to the input MUX of the ADC. When configured in this manner (Figure 2-66), there will be no prescaling of the input signal. Care must be taken in this mode not to drive the ADC into saturation by applying an input voltage greater than the reference voltage. The internal reference voltage of the ADC is 2.56 V. Optionally, an external reference can be supplied by the user. The external reference can be a maximum of 3.3 V DC.

Figure 2-66 • Analog Quad Direct Connect

The Analog Quad offers a wide variety of prescaling options to enable the ADC to resolve the input signals. Figure 2-67 shows the path through the Analog Quad for a signal that is to be prescaled prior to conversion. The ADC internal reference voltage and the prescaler factors were selected to make both prescaling and postscaling of the signals easy binary calculations (refer to Table 2-57 on page 2-130 for details). When an analog input pad is configured with a prescaler, there will be a 1 M $\Omega$  resistor to ground. This occurs even when the device is in power-down mode. In low power standby or sleep mode (VCC is OFF, VCC33A is ON, VCCI is ON) or when the resource is not used, analog inputs are pulled down to ground through a 1 M $\Omega$  resistor. The gate driver output is floating (or tristated), and there is no extra current on VCC33A.

These scaling factors hold true whether the particular pad is configured to accept a positive or negative voltage. Note that whereas the AV and AC pads support the same prescaling factors, the AT pad supports a reduced set of prescaling factors and supports positive voltages only.

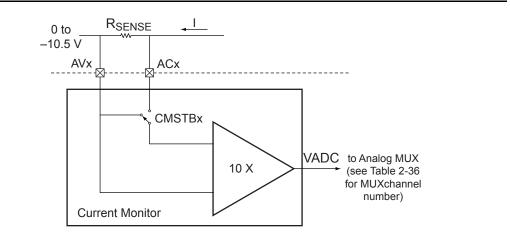

Figure 2-73 • Negative Current Monitor

## Terminology

### Accuracy

The accuracy of Fusion Current Monitor is  $\pm 2 \text{ mV}$  minimum plus 5% of the differential voltage at the input. The input accuracy can be translated to error at the ADC output by using EQ 4. The 10 V/V gain is the gain of the Current Monitor Circuit, as described in the "Current Monitor" section on page 2-86. For 8-bit mode, N = 8,  $V_{AREF} = 2.56$  V, zero differential voltage between AV and AC, the Error ( $E_{ADC}$ ) is equal to 2 LSBs.

$$E_{ADC} = (2mV + 0.05 |V_{AV} - V_{AC}|) \times (10V) / V \times \frac{2^{N}}{V_{AREF}}$$

EQ 4

where

N is the number of bits

$V_{AREF}$  is the Reference voltage

$V_{AV}$  is the voltage at AV pad

V<sub>AC</sub> is the voltage at AC pad

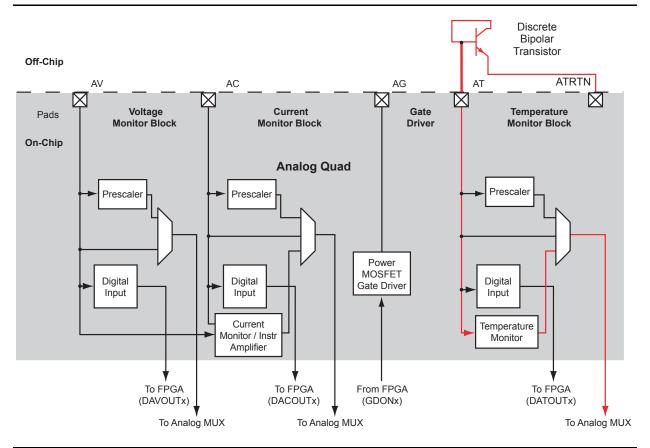

# **Temperature Monitor**

The final pin in the Analog Quad is the Analog Temperature (AT) pin. The AT pin is used to implement an accurate temperature monitor in conjunction with an external diode-connected bipolar transistor (Figure 2-76). For improved temperature measurement accuracy, it is important to use the ATRTN pin for the return path of the current sourced by the AT pin. Each ATRTN pin is shared between two adjacent Analog Quads. Additionally, if not used for temperature monitoring, the AT pin can provide functionality similar to that of the AV pad. However, in this mode only positive voltages can be applied to the AT pin, and only two prescaler factors are available (16 V and 4 V ranges—refer to Table 2-57 on page 2-130).

Figure 2-76 • Temperature Monitor Quad

# Analog Quad ACM Description

Table 2-56 maps out the ACM space associated with configuration of the Analog Quads within the Analog Block. Table 2-56 shows the byte assignment within each quad and the function of each bit within each byte. Subsequent tables will explain each bit setting and how it corresponds to a particular configuration. After 3.3 V and 1.5 V are applied to Fusion, Analog Quad configuration registers are loaded with default settings until the initialization and configuration state machine changes them to user-defined settings.

| Byte     | Bit | Signal (Bx) | Function                            | Default Setting       |

|----------|-----|-------------|-------------------------------------|-----------------------|

| Byte 0   | 0   | B0[0]       | Scaling factor control – prescaler  | Highest voltage range |

| (AV)     | 1   | B0[1]       |                                     |                       |

|          | 2   | B0[2]       |                                     |                       |

|          | 3   | B0[3]       | Analog MUX select                   | Prescaler             |

|          | 4   | B0[4]       | Current monitor switch              | Off                   |

|          | 5   | B0[5]       | Direct analog input switch          | Off                   |

|          | 6   | B0[6]       | Selects V-pad polarity              | Positive              |

|          | 7   | B0[7]       | Prescaler op amp mode               | Power-down            |

| Byte 1   | 0   | B1[0]       | Scaling factor control – prescaler  | Highest voltage range |

| (AC)     | 1   | B1[1]       |                                     |                       |

|          | 2   | B1[2]       |                                     |                       |

|          | 3   | B1[3]       | Analog MUX select                   | Prescaler             |

|          | 4   | B1[4]       |                                     |                       |

|          | 5   | B1[5]       | Direct analog input switch          | Off                   |

|          | 6   | B1[6]       | Selects C-pad polarity              | Positive              |

|          | 7   | B1[7]       | Prescaler op amp mode               | Power-down            |

| Byte 2 0 |     | B2[0]       | Internal chip temperature monitor * | Off                   |

| (AG)     | 1   | B2[1]       | Spare                               | -                     |

|          | 2   | B2[2]       | Current drive control               | Lowest current        |

|          | 3   | B2[3]       |                                     |                       |

|          | 4   | B2[4]       | Spare                               | -                     |

|          | 5   | B2[5]       | Spare                               | -                     |

|          | 6   | B2[6]       | Selects G-pad polarity              | Positive              |

|          | 7   | B2[7]       | Selects low/high drive              | Low drive             |

| Byte 3   | 0   | B3[0]       | Scaling factor control – prescaler  | Highest voltage range |

| (AT)     | 1   | B3[1]       |                                     |                       |

|          | 2   | B3[2]       |                                     |                       |

|          | 3   | B3[3]       | Analog MUX select                   | Prescaler             |

|          | 4   | B3[4]       |                                     |                       |

|          | 5   | B3[5]       | Direct analog input switch          | Off                   |

|          | 6   | B3[6]       | -                                   | -                     |

|          | 7   | B3[7]       | Prescaler op amp mode               | Power-down            |

Note: \*For the internal temperature monitor to function, Bit 0 of Byte 2 for all 10 Quads must be set.

Table 2-57 details the settings available to control the prescaler values of the AV, AC, and AT pins. Note that the AT pin has a reduced number of available prescaler values.

| Control Lines<br>Bx[2:0] | Scaling<br>Factor, Pad to<br>ADC Input | LSB for an<br>8-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>10-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>12-Bit<br>Conversion <sup>1</sup><br>(mV) | Full-Scale<br>Voltage in<br>10-Bit<br>Mode <sup>2</sup> | Range Name |

|--------------------------|----------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|------------|

| 000 <sup>3</sup>         | 0.15625                                | 64                                                     | 16                                                     | 4                                                      | 16.368 V                                                | 16 V       |

| 001                      | 0.3125                                 | 32                                                     | 8                                                      | 2                                                      | 8.184 V                                                 | 8 V        |

| 010 <sup>3</sup>         | 0.625                                  | 16                                                     | 4                                                      | 1                                                      | 4.092 V                                                 | 4 V        |

| 011                      | 1.25                                   | 8                                                      | 2                                                      | 0.5                                                    | 2.046 V                                                 | 2 V        |

| 100                      | 2.5                                    | 4                                                      | 1                                                      | 0.25                                                   | 1.023 V                                                 | 1 V        |

| 101                      | 5.0                                    | 2                                                      | 0.5                                                    | 0.125                                                  | 0.5115 V                                                | 0.5 V      |

| 110                      | 10.0                                   | 1                                                      | 0.25                                                   | 0.0625                                                 | 0.25575 V                                               | 0.25 V     |

| 111                      | 20.0                                   | 0.5                                                    | 0.125                                                  | 0.03125                                                | 0.127875 V                                              | 0.125 V    |

Table 2-57 • Prescaler Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

Notes:

1. LSB voltage equivalences assume VAREF = 2.56 V.

2. Full Scale voltage for n-bit mode: ((2<sup>n</sup>) - 1) x (LSB for a n-bit Conversion)

3. These are the only valid ranges for the Temperature Monitor Block Prescaler.

Table 2-58 details the settings available to control the MUX within each of the AV, AC, and AT circuits. This MUX determines whether the signal routed to the ADC is the direct analog input, prescaled signal, or output of either the Current Monitor Block or the Temperature Monitor Block.

Table 2-58 • Analog Multiplexer Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[4] | Control Lines Bx[3] | ADC Connected To                      |

|---------------------|---------------------|---------------------------------------|

| 0                   | 0                   | Prescaler                             |

| 0                   | 1                   | Direct input                          |

| 1                   | 0                   | Current amplifier temperature monitor |

| 1                   | 1                   | Not valid                             |

Table 2-59 details the settings available to control the Direct Analog Input switch for the AV, AC, and AT pins.

## *Table 2-59* • Direct Analog Input Switch Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[5] | Direct Input Switch |

|---------------------|---------------------|

| 0                   | Off                 |

| 1                   | On                  |

Table 2-60 details the settings available to control the polarity of the signals coming to the AV, AC, and AT pins. Note that the only valid setting for the AT pin is logic 0 to support positive voltages.

## Table 2-60 • Voltage Polarity Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)\*

| Control Lines Bx[6] | Input Signal Polarity |

|---------------------|-----------------------|

| 0                   | Positive              |

| 1                   | Negative              |

Note: \*The B3[6] signal for the AT pad should be kept at logic 0 to accept only positive voltages.

| I/O Standard                  | Input/Output Supply<br>Voltage (VCCI_TYP) | Input Reference Voltage<br>(VREF_TYP) | Board Termination Voltage<br>(VTT_TYP) |

|-------------------------------|-------------------------------------------|---------------------------------------|----------------------------------------|

| LVTTL/LVCMOS 3.3 V            | 3.30 V                                    | -                                     | -                                      |

| LVCMOS 2.5 V                  | 2.50 V                                    | _                                     | -                                      |

| LVCMOS 2.5 V / 5.0 V<br>Input | 2.50 V                                    | -                                     | -                                      |

| LVCMOS 1.8 V                  | 1.80 V                                    | _                                     | -                                      |

| LVCMOS 1.5 V                  | 1.50 V                                    | _                                     | -                                      |

| PCI 3.3 V                     | 3.30 V                                    | _                                     | -                                      |

| PCI-X 3.3 V                   | 3.30 V                                    | _                                     | -                                      |

| GTL+ 3.3 V                    | 3.30 V                                    | 1.00 V                                | 1.50 V                                 |

| GTL+ 2.5 V                    | 2.50 V                                    | 1.00 V                                | 1.50 V                                 |

| GTL 3.3 V                     | 3.30 V                                    | 0.80 V                                | 1.20 V                                 |

| GTL 2.5 V                     | 2.50 V                                    | 0.80 V                                | 1.20 V                                 |

| HSTL Class I                  | 1.50 V                                    | 0.75 V                                | 0.75 V                                 |

| HSTL Class II                 | 1.50 V                                    | 0.75 V                                | 0.75 V                                 |

| SSTL3 Class I                 | 3.30 V                                    | 1.50 V                                | 1.50 V                                 |

| SSTL3 Class II                | 3.30 V                                    | 1.50 V                                | 1.50 V                                 |

| SSTL2 Class I                 | 2.50 V                                    | 1.25 V                                | 1.25 V                                 |

| SSTL2 Class II                | 2.50 V                                    | 1.25 V                                | 1.25 V                                 |

| LVDS, BLVDS, M-LVDS           | 2.50 V                                    | -                                     | -                                      |

| LVPECL                        | 3.30 V                                    | -                                     | -                                      |

# Table 2-83 • Fusion Pro I/O Supported Standards and Corresponding VREF and VTT Voltages

# Table 2-122 • 1.8 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade  | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.            | 0.66              | 15.53           | 0.04             | 1.31            | 0.43              | 14.11           | 15.53           | 2.78            | 1.60            | 16.35            | 17.77            | ns    |

|                   | -1              | 0.56              | 13.21           | 0.04             | 1.11            | 0.36              | 12.01           | 13.21           | 2.36            | 1.36            | 13.91            | 15.11            | ns    |

|                   | -2 <sup>2</sup> | 0.49              | 11.60           | 0.03             | 0.98            | 0.32              | 10.54           | 11.60           | 2.07            | 1.19            | 12.21            | 13.27            | ns    |

| 4 mA              | Std.            | 0.66              | 10.48           | 0.04             | 1.31            | 0.43              | 10.41           | 10.48           | 3.23            | 2.73            | 12.65            | 12.71            | ns    |

|                   | -1              | 0.56              | 8.91            | 0.04             | 1.11            | 0.36              | 8.86            | 8.91            | 2.75            | 2.33            | 10.76            | 10.81            | ns    |

|                   | -2              | 0.49              | 7.82            | 0.03             | 0.98            | 0.32              | 7.77            | 7.82            | 2.41            | 2.04            | 9.44             | 9.49             | ns    |

| 8 mA              | Std.            | 0.66              | 8.05            | 0.04             | 1.31            | 0.43              | 8.20            | 7.84            | 3.54            | 3.27            | 10.43            | 10.08            | ns    |

|                   | -1              | 0.56              | 6.85            | 0.04             | 1.11            | 0.36              | 6.97            | 6.67            | 3.01            | 2.78            | 8.88             | 8.57             | ns    |

|                   | -2              | 0.49              | 6.01            | 0.03             | 0.98            | 0.32              | 6.12            | 5.86            | 2.64            | 2.44            | 7.79             | 7.53             | ns    |

| 12 mA             | Std.            | 0.66              | 7.50            | 0.04             | 1.31            | 0.43              | 7.64            | 7.30            | 3.61            | 3.41            | 9.88             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.38            | 0.04             | 1.11            | 0.36              | 6.50            | 6.21            | 3.07            | 2.90            | 8.40             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.60            | 0.03             | 0.98            | 0.32              | 5.71            | 5.45            | 2.69            | 2.55            | 7.38             | 7.12             | ns    |

| 16 mA             | Std.            | 0.66              | 7.29            | 0.04             | 1.31            | 0.43              | 7.23            | 7.29            | 3.71            | 3.95            | 9.47             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.20            | 0.04             | 1.11            | 0.36              | 6.15            | 6.20            | 3.15            | 3.36            | 8.06             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.45            | 0.03             | 0.98            | 0.32              | 5.40            | 5.45            | 2.77            | 2.95            | 7.07             | 7.12             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

# 3.3 V PCI, 3.3 V PCI-X

The Peripheral Component Interface for 3.3 V standard specifies support for 33 MHz and 66 MHz PCI Bus applications.

Table 2-134 • Minimum and Maximum DC Input and Output Levels

| 3.3 V PCI/PCI-X       | VIL       |                | V         | VIH       |           | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-----------------------|-----------|----------------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength        | Min.<br>V | Max.<br>V      | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| Per PCI specification |           | Per PCI curves |           |           |           |           |     |     |                         | 10                      | 10               |                  |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

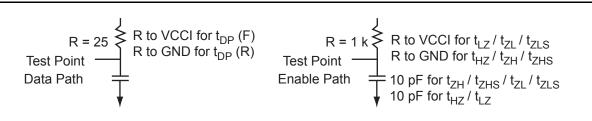

AC loadings are defined per the PCI/PCI-X specifications for the datapath; Microsemi loadings for enable path characterization are described in Figure 2-123.

## Figure 2-123 • AC Loading

AC loadings are defined per PCI/PCI-X specifications for the data path; Microsemi loading for tristate is described in Table 2-135.

#### Table 2-135 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V)                | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------------------|-----------------|------------------------|

| 0             | 3.3            | 0.285 * VCCI for t <sub>DP(R)</sub> | _               | 10                     |

|               |                | 0.615 * VCCI for t <sub>DP(F)</sub> |                 |                        |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

# SSTL3 Class I

Stub-Speed Terminated Logic for 3.3 V memory bus standard (JESD8-8). Fusion devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-162 • Minimum and Maximum DC Input and Output Levels

| SSTL3 Class I     | I VIL     |            | VIH        |           | VOL       | VOH        | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|------------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 14 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.7       | VCCI – 1.1 | 14  | 14  | 54                      | 51                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

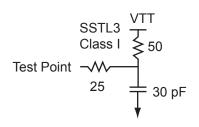

#### Figure 2-132 • AC Loading

#### Table 2-163 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.5                  | 1.5             | 1.485          | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-164 • SSTL3 Class I

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.5 V

| Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.31            | 0.04             | 1.25            | 0.43              | 2.35            | 1.84            |                 |                 | 4.59             | 4.07             | ns    |

| -1             | 0.56              | 1.96            | 0.04             | 1.06            | 0.36              | 2.00            | 1.56            |                 |                 | 3.90             | 3.46             | ns    |

| -2             | 0.49              | 1.72            | 0.03             | 0.93            | 0.32              | 1.75            | 1.37            |                 |                 | 3.42             | 3.04             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

# **IEEE 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/Os" section on page 2-132 for more details.

## **Timing Characteristics**

## Table 2-186 • JTAG 1532

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | -2    | -1    | Std.  | Units |

|----------------------|-----------------------------|-------|-------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 0.50  | 0.57  | 0.67  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 1.00  | 1.13  | 1.33  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 0.50  | 0.57  | 0.67  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 1.00  | 1.13  | 1.33  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 6.00  | 6.80  | 8.00  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 20.00 | 22.67 | 26.67 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 25.00 | 22.00 | 19.00 | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.20  | 0.23  | 0.27  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | TBD   | TBD   | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.