Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | -                                                               |

| Total RAM Bits                 | 110592                                                          |

| Number of I/O                  | 95                                                              |

| Number of Gates                | 600000                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                                 |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                 |

| Package / Case                 | 208-BFQFP                                                       |

| Supplier Device Package        | 208-PQFP (28x28)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs600-2pqg208 |

|                                |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

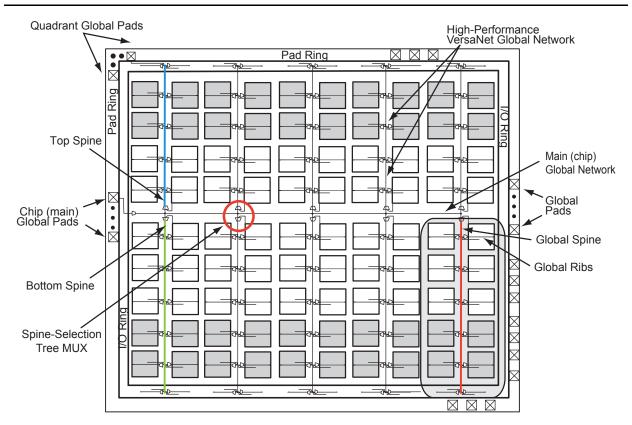

## **Global Resources (VersaNets)**

Fusion devices offer powerful and flexible control of circuit timing through the use of analog circuitry. Each chip has six CCCs. The west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and the east CCCs each contain a PLL. The PLLs include delay lines, a phase shifter (0°, 90°, 180°, 270°), and clock multipliers/dividers. Each CCC has all the circuitry needed for the selection and interconnection of inputs to the VersaNet global network. The east and west CCCs each have access to three VersaNet global lines on each side of the chip (six lines total). The CCCs at the four corners each have access to three quadrant global lines on each quadrant of the chip.

#### Advantages of the VersaNet Approach

One of the architectural benefits of Fusion is the set of powerful and low-delay VersaNet global networks. Fusion offers six chip (main) global networks that are distributed from the center of the FPGA array (Figure 2-11). In addition, Fusion devices have three regional globals (quadrant globals) in each of the four chip quadrants. Each core VersaTile has access to nine global networks on the device. Each of these networks contains spines and ribs that reach all VersaTiles in all quadrants (Figure 2-12 on page 2-12). This flexible VersaNet global network architecture allows users to map up to 180 different internal/external clocks in a Fusion device. Details on the VersaNet networks are given in Table 2-4 on page 2-12. The flexibility of the Fusion VersaNet global network allows the designer to address several design requirements. User applications that are clock-resource-intensive can easily route external or gated internal clocks using VersaNet global routing networks. Designers can also drastically reduce delay penalties and minimize resource usage by mapping critical, high-fanout nets to the VersaNet global network.

Figure 2-11 • Overview of Fusion VersaNet Global Network

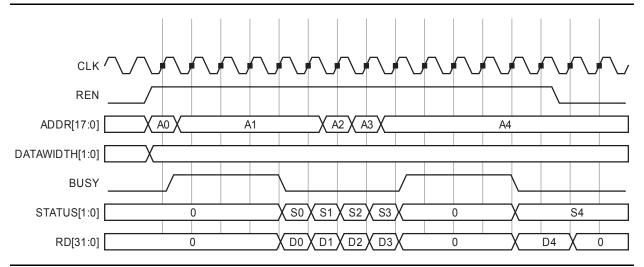

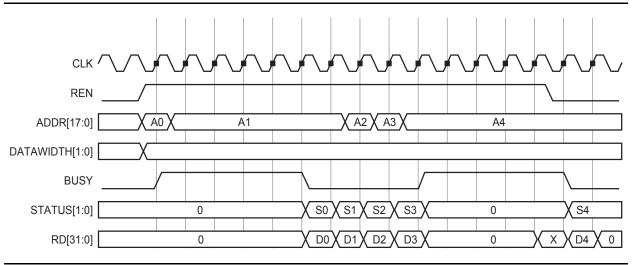

#### **Read Operation**

Read operations are designed to read data from the FB Array, Page Buffer, Block Buffer, or status registers. Read operations support a normal read and a read-ahead mode (done by asserting READNEXT). Also, the timing for Read operations is dependent on the setting of PIPE.

The following diagrams illustrate representative timing for Non-Pipe Mode (Figure 2-38) and Pipe Mode (Figure 2-39) reads of the flash memory block interface.

Figure 2-38 • Read Waveform (Non-Pipe Mode, 32-bit access)

Figure 2-39 • Read Waveform (Pipe Mode, 32-bit access)

The following signals are used to configure the RAM4K9 memory element.

#### WIDTHA and WIDTHB

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 2-27).

| WIDTHA1, WIDTHA0                                                               | WIDTHB1, WIDTHB0 | D×W   |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|------------------|-------|--|--|--|--|--|--|

| 00                                                                             | 00               | 4k×1  |  |  |  |  |  |  |

| 01                                                                             | 01               | 2k×2  |  |  |  |  |  |  |

| 10                                                                             | 10               | 1k×4  |  |  |  |  |  |  |

| 11                                                                             | 11               | 512×9 |  |  |  |  |  |  |

| Note: The aspect ratio settings are constant and cannot be changed on the fly. |                  |       |  |  |  |  |  |  |

#### BLKA and BLKB

These signals are active low and will enable the respective ports when asserted. When a BLKx signal is deasserted, the corresponding port's outputs hold the previous value.

#### WENA and WENB

These signals switch the RAM between read and write mode for the respective ports. A Low on these signals indicates a write operation, and a High indicates a read.

#### CLKA and CLKB

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A Low on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A High indicates a pipelined, read and data appears on the corresponding output in the next clock cycle.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A Low on these signals makes the output retain data from the previous read. A High indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

#### RESET

This active low signal resets the output to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory.

#### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 2-28).

#### Table 2-28 • Address Pins Unused/Used for Various Supported Bus Widths

| D×W   | ADDRx   |        |  |  |  |  |  |

|-------|---------|--------|--|--|--|--|--|

|       | Unused  | Used   |  |  |  |  |  |

| 4k×1  | None    | [11:0] |  |  |  |  |  |

| 2k×2  | [11]    | [10:0] |  |  |  |  |  |

| 1k×4  | [11:10] | [9:0]  |  |  |  |  |  |

| 512×9 | [11:9]  | [8:0]  |  |  |  |  |  |

Note: The "x" in ADDRx implies A or B.

Device Architecture

#### Table 2-36 • Analog Block Pin Description (continued)

| Signal Name                                         | Number<br>of Bits | Direction | Function                                                  | Location of<br>Details |

|-----------------------------------------------------|-------------------|-----------|-----------------------------------------------------------|------------------------|

| GDON0 to GDON9                                      | 10                | Input     | Control to power MOS – 1 per quad                         | Analog Quad            |

| TMSTB0 to TMSTB9                                    | 10                | Input     | Temperature monitor strobe – 1 per quad; active high      | Analog Quad            |

| DAVOUT0, DACOUT0, DATOUT0<br>to                     | 30                | Output    | Digital outputs – 3 per quad                              | Analog Quad            |

| DAVOUT9, DACOUT9, DATOUT9                           |                   |           |                                                           |                        |

| DENAV0, DENAC0, DENAT0 to<br>DENAV9, DENAC9, DENAT9 | 30                | Input     | Digital input enables – 3 per quad                        | Analog Quad            |

| AV0                                                 | 1                 | Input     | Analog Quad 0                                             | Analog Quad            |

| AC0                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG0                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT0                                                 | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN01                                          | 1                 | Input     | Temperature monitor return shared by Analog Quads 0 and 1 | Analog Quad            |

| AV1                                                 | 1                 | Input     | Analog Quad 1                                             | Analog Quad            |

| AC1                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG1                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT1                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AV2                                                 | 1                 | Input     | Analog Quad 2                                             | Analog Quad            |

| AC2                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG2                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT2                                                 | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN23                                          | 1                 | Input     | Temperature monitor return shared by Analog Quads 2 and 3 | Analog Quad            |

| AV3                                                 | 1                 | Input     | Analog Quad 3                                             | Analog Quad            |

| AC3                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG3                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT3                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AV4                                                 | 1                 | Input     | Analog Quad 4                                             | Analog Quad            |

| AC4                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG4                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT4                                                 | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN45                                          | 1                 | Input     | Temperature monitor return shared by Analog Quads 4 and 5 | Analog Quad            |

| AV5                                                 | 1                 | Input     | Analog Quad 5                                             | Analog Quad            |

| AC5                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG5                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT5                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AV6                                                 | 1                 | Input     | Analog Quad 6                                             | Analog Quad            |

| AC6                                                 | 1                 | Input     | 1                                                         | Analog Quad            |

## Analog-to-Digital Converter Block

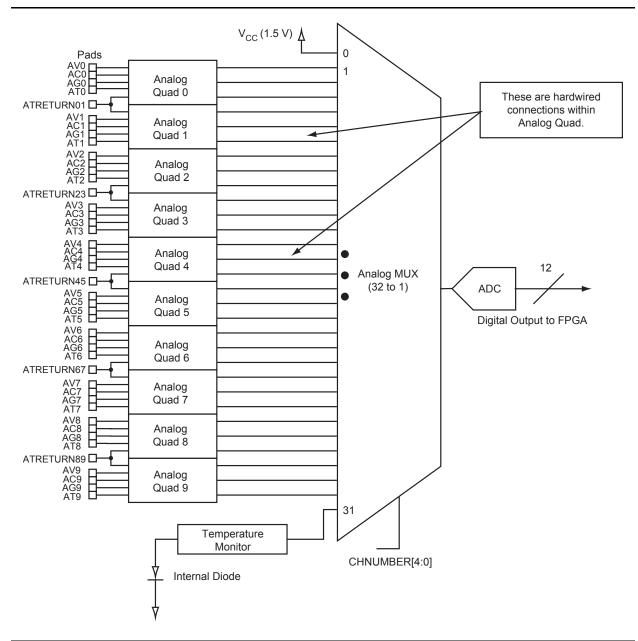

At the heart of the Fusion analog system is a programmable Successive Approximation Register (SAR) ADC. The ADC can support 8-, 10-, or 12-bit modes of operation. In 12-bit mode, the ADC can resolve 500 ksps. All results are MSB-justified in the ADC. The input to the ADC is a large 32:1 analog input multiplexer. A simplified block diagram of the Analog Quads, analog input multiplexer, and ADC is shown in Figure 2-79. The ADC offers multiple self-calibrating modes to ensure consistent high performance both at power-up and during runtime.

Figure 2-79 • ADC Block Diagram

## **Typical Performance Characteristics**

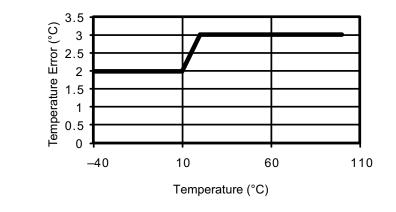

Temperature Errror vs. Die Temperature

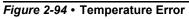

Figure 2-95 • Effect of External Sensor Capacitance

|               | Total Channel<br>Error (LSB) |              |      | -            |            | el Inpu<br>rror (LS | t Offset<br>SB) | Channel Input Offset<br>Error (mV) |      |              | Channel Gain Error<br>(%FSR) |      |      |

|---------------|------------------------------|--------------|------|--------------|------------|---------------------|-----------------|------------------------------------|------|--------------|------------------------------|------|------|

| Analog<br>Pad | Prescaler<br>Range (V)       | Neg.<br>Max. | Med. | Pos.<br>Max. | Neg<br>Max | Med.                | Pos.<br>Max.    | Neg.<br>Max.                       | Med. | Pos.<br>Max. | Min.                         | Тур. | Max. |

| Positi        | ve Range                     |              |      |              |            |                     | ADC in          | 10-Bit N                           | lode |              |                              |      |      |

| AV, AC        | 16                           | -22          | -2   | 12           | -11        | -2                  | 14              | -169                               | -32  | 224          | 3                            | 0    | -3   |

|               | 8                            | -40          | -5   | 17           | -11        | -5                  | 21              | -87                                | -40  | 166          | 2                            | 0    | -4   |

|               | 4                            | -45          | -9   | 24           | -16        | -11                 | 36              | -63                                | -43  | 144          | 2                            | 0    | -4   |

|               | 2                            | -70          | -19  | 33           | -33        | -20                 | 66              | -66                                | -39  | 131          | 2                            | 0    | -4   |

|               | 1                            | -25          | -7   | 5            | -11        | -3                  | 26              | -11                                | -3   | 26           | 3                            | –1   | -3   |

|               | 0.5                          | -41          | -12  | 8            | -12        | -7                  | 38              | -6                                 | -4   | 19           | 3                            | -1   | -3   |

|               | 0.25                         | -53          | -14  | 19           | -20        | -14                 | 40              | -5                                 | -3   | 10           | 5                            | 0    | -4   |

|               | 0.125                        | -89          | -29  | 24           | -40        | -28                 | 88              | -5                                 | -4   | 11           | 7                            | 0    | -5   |

| AT            | 16                           | -3           | 9    | 15           | -4         | 0                   | 4               | -64                                | 5    | 64           | 1                            | 0    | -1   |

|               | 4                            | -10          | 2    | 15           | -11        | -2                  | 11              | -44                                | -8   | 44           | 1                            | 0    | -1   |

| Negati        | ve Range                     |              |      |              |            |                     | ADC in          | 10-Bit Mode                        |      |              |                              |      |      |

| AV, AC        | 16                           | -35          | -10  | 9            | -24        | -6                  | 9               | -383                               | -96  | 148          | 5                            | -1   | -6   |

|               | 8                            | -65          | -19  | 12           | -34        | -12                 | 9               | -268                               | -99  | 75           | 5                            | -1   | -5   |

|               | 4                            | -86          | -28  | 21           | -64        | -24                 | 19              | -254                               | -96  | 76           | 5                            | –1   | -6   |

|               | 2                            | -136         | -53  | 37           | -115       | -42                 | 39              | -230                               | -83  | 78           | 6                            | -2   | -7   |

|               | 1                            | -98          | -35  | 8            | -39        | -8                  | 15              | -39                                | -8   | 15           | 10                           | -3   | -10  |

|               | 0.5                          | -121         | -46  | 7            | -54        | -14                 | 18              | -27                                | -7   | 9            | 10                           | -4   | -11  |

|               | 0.25                         | -149         | -49  | 19           | -72        | -16                 | 40              | -18                                | -4   | 10           | 14                           | -4   | -12  |

|               | 0.125                        | -188         | -67  | 38           | -112       | -27                 | 56              | -14                                | -3   | 7            | 16                           | -5   | -14  |

# Table 2-51 • Uncalibrated Analog Channel Accuracy\*Worst-Case Industrial Conditions, TJ = 85°C

*Note:* \*Channel Accuracy includes prescaler and ADC accuracies. For 12-bit mode, multiply the LSB count by 4. For 8-bit mode, divide the LSB count by 4. Gain remains the same.

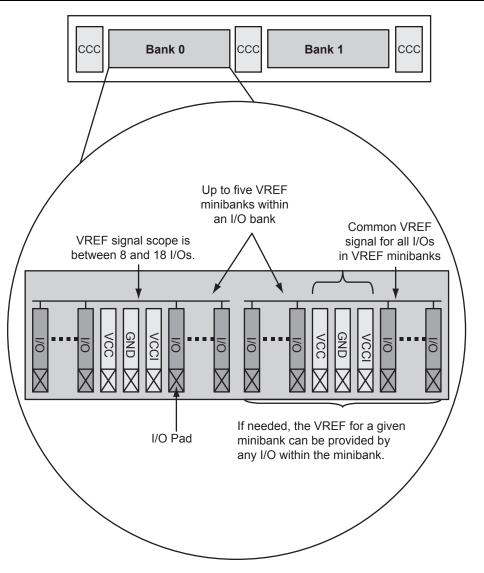

Figure 2-99 • Fusion Pro I/O Bank Detail Showing VREF Minibanks (north side of AFS600 and AFS1500)

| I/O Bank     | Single-Ended I/O Standards                                                                        | Differential I/O<br>Standards | Voltage-Referenced                                                                                          | Hot-<br>Swap |

|--------------|---------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------|--------------|

| Standard I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V                          | _                             | -                                                                                                           | Yes          |

| Advanced I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | -                                                                                                           | -            |

| Pro I/O      | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | GTL+2.5 V / 3.3 V, GTL 2.5 V / 3.3 V,<br>HSTL Class I and II, SSTL2 Class I<br>and II, SSTL3 Class I and II | Yes          |

### Summary of I/O Timing Characteristics – Default I/O Software Settings

# Table 2-90 • Summary of AC Measuring Points Applicable to All I/O Bank Types

| Standard                   | Input Reference Voltage<br>(VREF_TYP) | Board Termination Voltage<br>(VTT_REF) | Measuring Trip Point<br>(Vtrip)         |

|----------------------------|---------------------------------------|----------------------------------------|-----------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | -                                     | _                                      | 1.4 V                                   |

| 2.5 V LVCMOS               | _                                     | -                                      | 1.2 V                                   |

| 1.8 V LVCMOS               | _                                     | -                                      | 0.90 V                                  |

| 1.5 V LVCMOS               | _                                     | -                                      | 0.75 V                                  |

| 3.3 V PCI                  | -                                     | -                                      | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)) |

| 3.3 V PCI-X                | -                                     | -                                      | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)  |

| 3.3 V GTL                  | 0.8 V                                 | 1.2 V                                  | VREF                                    |

| 2.5 V GTL                  | 0.8 V                                 | 1.2 V                                  | VREF                                    |

| 3.3 V GTL+                 | 1.0 V                                 | 1.5 V                                  | VREF                                    |

| 2.5 V GTL+                 | 1.0 V                                 | 1.5 V                                  | VREF                                    |

| HSTL (I)                   | 0.75 V                                | 0.75 V                                 | VREF                                    |

| HSTL (II)                  | 0.75 V                                | 0.75 V                                 | VREF                                    |

| SSTL2 (I)                  | 1.25 V                                | 1.25 V                                 | VREF                                    |

| SSTL2 (II)                 | 1.25 V                                | 1.25 V                                 | VREF                                    |

| SSTL3 (I)                  | 1.5 V                                 | 1.485 V                                | VREF                                    |

| SSTL3 (II)                 | 1.5 V                                 | 1.485 V                                | VREF                                    |

| LVDS                       | _                                     | -                                      | Cross point                             |

| LVPECL                     | _                                     | -                                      | Cross point                             |

#### Table 2-91 • I/O AC Parameter Definitions

| Parameter         | Definition                                                                  |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer with Schmitt trigger disabled    |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>PYS</sub>  | Pad to Data delay through the Input Buffer with Schmitt trigger enabled     |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

# Table 2-132 • 1.5 V LVCMOS Low Slew<br/>Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCI = 1.4 V<br/>Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 12.33           | 0.04             | 1.42            | 0.43              | 11.79           | 12.33           | 2.45            | 2.32            | ns    |

|                   | -1             | 0.56              | 10.49           | 0.04             | 1.21            | 0.36              | 10.03           | 10.49           | 2.08            | 1.98            | ns    |

|                   | -2             | 0.49              | 9.21            | 0.03             | 1.06            | 0.32              | 8.81            | 9.21            | 1.83            | 1.73            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-133 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 7.65            | 0.04             | 1.42            | 0.43              | 6.31            | 7.65            | 2.45            | 2.45            | ns    |

|                   | -1             | 0.56              | 6.50            | 0.04             | 1.21            | 0.36              | 5.37            | 6.50            | 2.08            | 2.08            | ns    |

|                   | -2             | 0.49              | 5.71            | 0.03             | 1.06            | 0.32              | 4.71            | 5.71            | 1.83            | 1.83            | ns    |

Device Architecture

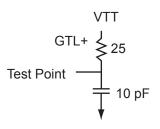

#### 3.3 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-144 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL+        |           | VIL        | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 35 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | -         | 35  | 35 | 181                     | 268                     | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

#### Figure 2-126 • AC Loading

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                  | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-146 • 3.3 V GTL+

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.06            | 0.04             | 1.59            | 0.43              | 2.09            | 2.06            |                 |                 | 4.33             | 4.29             | ns    |

| -1             | 0.56              | 1.75            | 0.04             | 1.35            | 0.36              | 1.78            | 1.75            |                 |                 | 3.68             | 3.65             | ns    |

| -2             | 0.49              | 1.53            | 0.03             | 1.19            | 0.32              | 1.56            | 1.53            |                 |                 | 3.23             | 3.20             | ns    |

Device Architecture

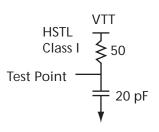

#### **HSTL Class I**

High-Speed Transceiver Logic is a general-purpose high-speed 1.5 V bus standard (EIA/JESD8-6). Fusion devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

| HSTL<br>Class I   | VIL       |            | VIH        |           | VOL       | VOH        | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 8 mA              | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.4       | VCCI – 0.4 | 8   | 8  | 39                      | 32                      | 10               | 10               |

Table 2-150 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

#### Figure 2-128 • AC Loading

#### Table 2-151 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 0.75                 | 0.75            | 0.75           | 20                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-152 • HSTL Class I

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V, VREF = 0.75 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 3.18            | 0.04             | 2.12            | 0.43              | 3.24            | 3.14            |                 |                 | 5.47             | 5.38             | ns    |

| -1             | 0.56              | 2.70            | 0.04             | 1.81            | 0.36              | 2.75            | 2.67            |                 |                 | 4.66             | 4.58             | ns    |

| -2             | 0.49              | 2.37            | 0.03             | 1.59            | 0.32              | 2.42            | 2.35            |                 |                 | 4.09             | 4.02             | ns    |

#### Input Register

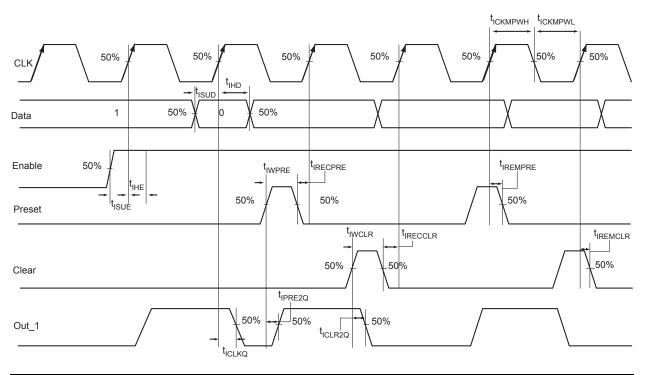

#### Figure 2-139 • Input Register Timing Diagram

#### Timing Characteristics

# Table 2-176 • Input Data Register Propagation DelaysCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.24 | 0.27 | 0.32 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.26 | 0.30 | 0.35 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.37 | 0.42 | 0.50 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.32 | 0.37 | 0.43 | ns    |

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

#### TRST Boundary Scan Reset Pin

The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the TAP is held in reset mode. The resistor values must be chosen from Table 2-183 and must satisfy the parallel resistance value requirement. The values in Table 2-183 correspond to the resistor recommended when a single device is used and to the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entering an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin. Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

#### **Special Function Pins**

#### NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC Don't Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

#### NCAP Negative Capacitor

Negative Capacitor is where the negative terminal of the charge pump capacitor is connected. A capacitor, with a 2.2  $\mu$ F recommended value, is required to connect between PCAP and NCAP.

#### PCAP Positive Capacitor

*Positive Capacitor* is where the positive terminal of the charge pump capacitor is connected. A capacitor, with a 2.2  $\mu$ F recommended value, is required to connect between PCAP and NCAP.

#### PUB Push Button

*Push button* is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.

#### PTBASE Pass Transistor Base

*Pass Transistor Base* is the control signal of the voltage regulator. This pin should be connected to the base of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

#### PTEM Pass Transistor Emitter

Pass Transistor Emitter is the feedback input of the voltage regulator.

This pin should be connected to the emitter of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

#### XTAL1 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

$P_{S-CELL} = 0 W$  $P_{C-CELL} = 0 W$  $P_{NET} = 0 W$  $P_{LOGIC} = 0 W$

#### I/O Input and Output Buffer Contribution—P<sub>I/O</sub>

This example uses LVTTL 3.3 V I/O cells. The output buffers are 12 mA–capable, configured with high output slew and driving a 35 pF output load.

$F_{CLK} = 50 \text{ MHz}$ Number of input pins used: N<sub>INPUTS</sub> = 30 Number of output pins used: N<sub>OUTPUTS</sub> = 40 Estimated I/O buffer toggle rate:  $\alpha_2$  = 0.1 (10%) Estimated IO buffer enable rate:  $\beta_1$  = 1 (100%)

#### **Operating Mode**

$$\begin{split} \mathsf{P}_{\mathsf{INPUTS}} &= \mathsf{N}_{\mathsf{INPUTS}} * (\alpha_2 \,/\, 2) * \mathsf{PAC9} * \mathsf{F}_{\mathsf{CLK}} \\ \mathsf{P}_{\mathsf{INPUTS}} &= 30 * (0.1 \,/\, 2) * 0.01739 * 50 \\ \mathsf{P}_{\mathsf{INPUTS}} &= 1.30 \text{ mW} \end{split}$$

$$\begin{split} \mathsf{P}_{\text{OUTPUTS}} &= \mathsf{N}_{\text{OUTPUTS}} * (\alpha_2 / 2) * \beta_1 * \mathsf{PAC10} * \mathsf{F}_{\text{CLK}} \\ \mathsf{P}_{\text{OUTPUTS}} &= 40 * (0.1 / 2) * 1 * 0.4747 * 50 \\ \mathsf{P}_{\text{OUTPUTS}} &= 47.47 \text{ mW} \end{split}$$

$P_{I/O} = P_{INPUTS} + P_{OUTPUTS}$  $P_{I/O} = 1.30 \text{ mW} + 47.47 \text{ mW}$

P<sub>I/O</sub> = 48.77 mW

#### Standby Mode and Sleep Mode

$P_{INPUTS} = 0 W$

$P_{OUTPUTS} = 0 W$  $P_{I/O} = 0 W$

#### RAM Contribution—P<sub>MEMORY</sub>

Frequency of Read Clock:  $F_{READ-CLOCK} = 10 \text{ MHz}$ Frequency of Write Clock:  $F_{WRITE-CLOCK} = 10 \text{ MHz}$ Number of RAM blocks:  $N_{BLOCKS} = 20$ Estimated RAM Read Enable Rate:  $\beta_2 = 0.125 (12.5\%)$ Estimated RAM Write Enable Rate:  $\beta_3 = 0.125 (12.5\%)$

#### **Operating Mode**

$$\begin{split} \mathsf{P}_{\mathsf{MEMORY}} &= (\mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{PAC11} * \beta_2 * \mathsf{F}_{\mathsf{READ-CLOCK}}) + (\mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{PAC12} * \beta_3 * \mathsf{F}_{\mathsf{WRITE-CLOCK}}) \\ \mathsf{P}_{\mathsf{MEMORY}} &= (20 * 0.025 * 0.125 * 10) + (20 * 0.030 * 0.125 * 10) \\ \mathsf{P}_{\mathsf{MEMORY}} &= 1.38 \text{ mW} \end{split}$$

#### Standby Mode and Sleep Mode

P<sub>MEMORY</sub> = 0 W

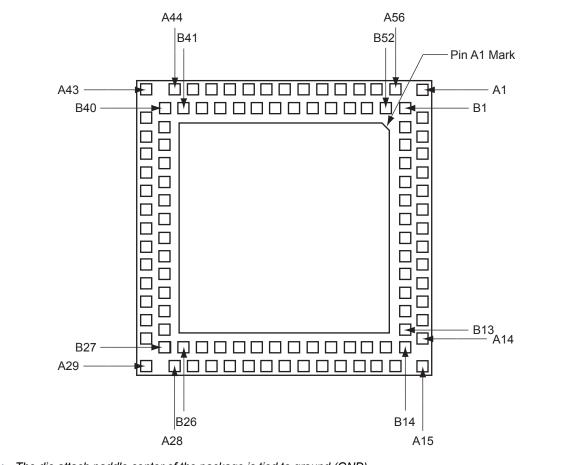

# 4 – Package Pin Assignments

# QN108

Note: The die attach paddle center of the package is tied to ground (GND).

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

## **Microsemi**

Package Pin Assignments

|            | QN108           |            | QN108           |            | QN108           |

|------------|-----------------|------------|-----------------|------------|-----------------|

| Pin Number | AFS090 Function | Pin Number | AFS090 Function | Pin Number | AFS090 Function |

| A1         | NC              | A39        | GND             | B21        | AC2             |

| A2         | GNDQ            | A40        | GCB1/IO35PDB1V0 | B22        | ATRTN1          |

| A3         | GAA2/IO52PDB3V0 | A41        | GCB2/IO33PDB1V0 | B23        | AG3             |

| A4         | GND             | A42        | GBA2/IO31PDB1V0 | B24        | AV3             |

| A5         | GFA1/IO47PDB3V0 | A43        | NC              | B25        | VCC33A          |

| A6         | GEB1/IO45PDB3V0 | A44        | GBA1/IO30RSB0V0 | B26        | VAREF           |

| A7         | VCCOSC          | A45        | GBB1/IO28RSB0V0 | B27        | PUB             |

| A8         | XTAL2           | A46        | GND             | B28        | VCC33A          |

| A9         | GEA1/IO44PPB3V0 | A47        | VCC             | B29        | PTBASE          |

| A10        | GEA0/IO44NPB3V0 | A48        | GBC1/IO26RSB0V0 | B30        | VCCNVM          |

| A11        | GEB2/IO42PDB3V0 | A49        | IO21RSB0V0      | B31        | VCC             |

| A12        | VCCNVM          | A50        | IO19RSB0V0      | B32        | TDI             |

| A13        | VCC15A          | A51        | IO09RSB0V0      | B33        | TDO             |

| A14        | PCAP            | A52        | GAC0/IO04RSB0V0 | B34        | VJTAG           |

| A15        | NC              | A53        | VCCIB0          | B35        | GDC0/IO38NDB1V  |

| A16        | GNDA            | A54        | GND             |            | 0               |

| A17        | AV0             | A55        | GAB0/IO02RSB0V0 | B36        | VCCIB1          |

| A18        | AG0             | A56        | GAA0/IO00RSB0V0 | B37        | GCB0/IO35NDB1V0 |

| A19        | ATRTN0          | B1         | VCOMPLA         | B38        | GCC2/IO33NDB1V  |

| A20        | AT1             | B2         | VCCIB3          | D20        |                 |

| A21        | AC1             | B3         | GAB2/IO52NDB3V0 | B39        | GBB2/IO31NDB1V0 |

| A22        | AV2             | B4         | VCCIB3          | B40        | VCCIB1          |

| A23        | AG2             | B5         | GFA0/IO47NDB3V0 | B41        | GNDQ            |

| A24        | AT2             | B6         | GEB0/IO45NDB3V0 | B42        | GBA0/IO29RSB0V0 |

| A25        | AT3             | B7         | XTAL1           | B43        | VCCIB0          |

| A26        | AC3             | B8         | GNDOSC          | B44        | GBB0/IO27RSB0V0 |

| A27        | GNDAQ           | B9         | GEC2/IO43PSB3V0 | B45        | GBC0/IO25RSB0V0 |

| A28        | ADCGNDREF       | B10        | GEA2/IO42NDB3V0 | B46        | IO20RSB0V0      |

| A29        | NC              | B11        | VCC             | B47        | IO10RSB0V0      |

| A30        | GNDA            | B12        | GNDNVM          | B48        | GAC1/IO05RSB0V0 |

| A31        | PTEM            | B13        | NCAP            | B49        | GAB1/IO03RSB0V0 |

| A32        | GNDNVM          | B14        | VCC33PMP        | B50        | VCC             |

| A33        | VPUMP           | B15        | VCC33N          | B51        | GAA1/IO01RSB0V0 |

| A34        | ТСК             | B16        | GNDAQ           | B52        | VCCPLA          |

| A35        | TMS             | B17        | AC0             |            |                 |

| A36        | TRST            | B18        | AT0             |            |                 |

| A37        | GDB1/IO39PSB1V0 | B19        | AG1             |            |                 |

| A38        | GDC1/IO38PDB1V0 | B20        | AV1             |            |                 |

|               | FG484           |                  |               | FG484           |                  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |

| B5            | IO05NDB0V0      | IO04NDB0V0       | C18           | VCCIB1          | VCCIB1           |

| B6            | IO05PDB0V0      | IO04PDB0V0       | C19           | VCOMPLB         | VCOMPLB          |

| B7            | GND             | GND              | C20           | GBA2/IO30PDB2V0 | GBA2/IO44PDB2V0  |

| B8            | IO10NDB0V1      | IO09NDB0V1       | C21           | NC              | IO48PSB2V0       |

| B9            | IO13PDB0V1      | IO11PDB0V1       | C22           | GBB2/IO31PDB2V0 | GBB2/IO45PDB2V0  |

| B10           | GND             | GND              | D1            | IO82NDB4V0      | IO121NDB4V0      |

| B11           | IO17NDB1V0      | IO24NDB1V0       | D2            | GND             | GND              |

| B12           | IO18NDB1V0      | IO26NDB1V0       | D3            | IO83NDB4V0      | IO123NDB4V0      |

| B13           | GND             | GND              | D4            | GAC2/IO83PDB4V0 | GAC2/IO123PDB4V0 |

| B14           | IO21NDB1V0      | IO31NDB1V1       | D5            | GAA2/IO85PDB4V0 | GAA2/IO125PDB4V0 |

| B15           | IO21PDB1V0      | IO31PDB1V1       | D6            | GAC0/IO03NDB0V0 | GAC0/IO03NDB0V0  |

| B16           | GND             | GND              | D7            | GAC1/IO03PDB0V0 | GAC1/IO03PDB0V0  |

| B17           | GBC1/IO26PDB1V1 | GBC1/IO40PDB1V2  | D8            | IO09NDB0V1      | IO10NDB0V1       |

| B18           | GBA1/IO28PDB1V1 | GBA1/IO42PDB1V2  | D9            | IO09PDB0V1      | IO10PDB0V1       |

| B19           | GND             | GND              | D10           | IO11NDB0V1      | IO14NDB0V2       |

| B20           | VCCPLB          | VCCPLB           | D11           | IO16NDB1V0      | IO23NDB1V0       |

| B21           | GND             | GND              | D12           | IO16PDB1V0      | IO23PDB1V0       |

| B22           | VCC             | NC               | D13           | NC              | IO32NPB1V1       |

| C1            | IO82PDB4V0      | IO121PDB4V0      | D14           | IO23NDB1V1      | IO34NDB1V1       |

| C2            | NC              | IO122PSB4V0      | D15           | IO23PDB1V1      | IO34PDB1V1       |

| C3            | IO00NDB0V0      | IO00NDB0V0       | D16           | IO25PDB1V1      | IO37PDB1V2       |

| C4            | IO00PDB0V0      | IO00PDB0V0       | D17           | GBB1/IO27PDB1V1 | GBB1/IO41PDB1V2  |

| C5            | VCCIB0          | VCCIB0           | D18           | VCCIB2          | VCCIB2           |

| C6            | IO06NDB0V0      | IO05NDB0V1       | D19           | NC              | IO47PPB2V0       |

| C7            | IO06PDB0V0      | IO05PDB0V1       | D20           | IO30NDB2V0      | IO44NDB2V0       |

| C8            | VCCIB0          | VCCIB0           | D21           | GND             | GND              |

| C9            | IO13NDB0V1      | IO11NDB0V1       | D22           | IO31NDB2V0      | IO45NDB2V0       |

| C10           | IO11PDB0V1      | IO14PDB0V2       | E1            | IO81NDB4V0      | IO120NDB4V0      |

| C11           | VCCIB0          | VCCIB0           | E2            | IO81PDB4V0      | IO120PDB4V0      |

| C12           | VCCIB1          | VCCIB1           | E3            | VCCIB4          | VCCIB4           |

| C13           | IO20NDB1V0      | IO29NDB1V1       | E4            | GAB2/IO84PDB4V0 | GAB2/IO124PDB4V0 |

| C14           | IO20PDB1V0      | IO29PDB1V1       | E5            | IO85NDB4V0      | IO125NDB4V0      |

| C15           | VCCIB1          | VCCIB1           | E6            | GND             | GND              |

| C16           | IO25NDB1V1      | IO37NDB1V2       | E7            | VCCIB0          | VCCIB0           |

| C17           | GBB0/IO27NDB1V1 | GBB0/IO41NDB1V2  | E8            | NC              | IO08NDB0V1       |

Fusion Family of Mixed Signal FPGAs

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                                                     | Page  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance 1.0<br>(continued) | In Table 2-47 • ADC Characteristics in Direct Input Mode, the commercial conditions were updated and note 2 is new.                                                                                                                                                                                                                                                                         | 2-121 |

|                            | The $V_{\text{CC33ACAP}}$ signal name was changed to "XTAL1 Crystal Oscillator Circuit Input".                                                                                                                                                                                                                                                                                              | 2-228 |

|                            | Table 2-48 • Uncalibrated Analog Channel Accuracy* is new.                                                                                                                                                                                                                                                                                                                                  | 2-123 |

|                            | Table 2-49 • Calibrated Analog Channel Accuracy <sup>1,2,3</sup> is new.                                                                                                                                                                                                                                                                                                                    | 2-124 |

|                            | Table 2-50 • Analog Channel Accuracy: Monitoring Standard Positive Voltages is new.                                                                                                                                                                                                                                                                                                         | 2-125 |

|                            | In Table 2-57 • Voltage Polarity Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)*, the following I/O Bank names were changed:<br>Hot-Swap changed to Standard<br>LVDS changed to Advanced                                                                                                                                                                                        | 2-131 |

|                            | In Table 2-58 • Prescaler Op Amp Power-Down Truth Table—AV (x = 0), AC (x = 1),<br>and AT (x = 3), the following I/O Bank names were changed:<br>Hot-Swap changed to Standard<br>LVDS changed to Advanced                                                                                                                                                                                   | 2-132 |

|                            | In the title of Table 2-64 • I/O Standards Supported by Bank Type, LVDS I/O was changed to Advanced I/O.                                                                                                                                                                                                                                                                                    | 2-134 |

|                            | The title was changed from "Fusion Standard, LVDS, and Standard plus Hot-Swap I/O" to Table 2-68 • Fusion Standard and Advanced I/O Features. In addition, the table headings were all updated. The heading used to be Standard and LVDS I/O and was changed to Advanced I/O. Standard Hot-Swap was changed to just Standard.                                                               | 2-136 |

|                            | <ul> <li>This sentence was deleted from the "Slew Rate Control and Drive Strength" section:<br/>The Standard hot-swap I/Os do not support slew rate control. In addition, these references were changed:</li> <li>From: Fusion hot-swap I/O (Table 2-69 on page 2-122) To: Fusion Standard I/O</li> <li>From: Fusion LVDS I/O (Table 2-70 on page 2-122) To: Fusion Advanced I/O</li> </ul> | 2-152 |

|                            | The "Cold-Sparing Support" section was significantly updated.                                                                                                                                                                                                                                                                                                                               | 2-143 |

|                            | In the title of Table 2-75 • Fusion Standard I/O Standards—OUT_DRIVE Settings, Hot-Swap was changed to Standard.                                                                                                                                                                                                                                                                            | 2-153 |

|                            | In the title of Table 2-76 • Fusion Advanced I/O Standards—SLEW and OUT_DRIVE Settings, LVDS was changed to Advanced.                                                                                                                                                                                                                                                                       | 2-153 |

|                            | In the title of Table 2-81 • Fusion Standard and Advanced I/O Attributes vs. I/O Standard Applications, LVDS was changed to Advanced.                                                                                                                                                                                                                                                       | 2-157 |

|                            | In Figure 2-111 • Naming Conventions of Fusion Devices with Three Digital I/O<br>Banks and Figure 2-112 • Naming Conventions of Fusion Devices with Four I/O<br>Banks the following names were changed:                                                                                                                                                                                     | 2-160 |

|                            | Hot-Swap changed to Standard<br>LVDS changed to Advanced                                                                                                                                                                                                                                                                                                                                    |       |

|                            | The Figure 2-113 • Timing Model was updated.                                                                                                                                                                                                                                                                                                                                                | 2-161 |

|                            | In the notes for Table 2-86 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions, $T_J$ was changed to $T_A$ .                                                                                                                                                                                                                               | 2-101 |

Fusion Family of Mixed Signal FPGAs

| Revision     | Changes                                                                                                                                          | Page  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|

| Advance v0.3 | The "Temperature Monitor" section was updated.                                                                                                   | 2-96  |  |  |  |

| (continued)  | EQ 2 is new.                                                                                                                                     | 2-103 |  |  |  |

|              | The "ADC Description" section was updated.                                                                                                       | 2-102 |  |  |  |

|              | Figure 2-16 • Fusion Clocking Options was updated.                                                                                               | 2-20  |  |  |  |

|              | Table 2-46 · Analog Channel Specifications was updated.                                                                                          | 2-118 |  |  |  |

|              | The notes in Table 2-72 • Fusion Standard and Advanced I/O – Hot-Swap and 5 V Input Tolerance Capabilities were updated.                         | 2-144 |  |  |  |

|              | The "Simultaneously Switching Outputs and PCB Layout" section is new.                                                                            | 2-149 |  |  |  |

|              | LVPECL and LVDS were updated in Table 2-81 • Fusion Standard and Advanced I/O Attributes vs. I/O Standard Applications.                          | 2-157 |  |  |  |

|              | LVPECL and LVDS were updated in Table 2-82 • Fusion Pro I/O Attributes vs. I/O Standard Applications.                                            | 2-158 |  |  |  |

|              | The "Timing Model" was updated.                                                                                                                  | 2-161 |  |  |  |

|              | All voltage-referenced Minimum and Maximum DC Input and Output Level tables were updated.                                                        |       |  |  |  |

|              | All Timing Characteristic tables were updated                                                                                                    | N/A   |  |  |  |

|              | Table 2-83 • Summary of Maximum and Minimum DC Input and Output LevelsApplicable to Commercial and Industrial Conditions was updated.            |       |  |  |  |

|              | Table 2-79 • Summary of I/O Timing Characteristics – Software Default Settings was updated.                                                      |       |  |  |  |

|              | Table 2-93 • I/O Output Buffer Maximum Resistances <sup>1</sup> was updated.                                                                     | 2-171 |  |  |  |

|              | The "BLVDS/M-LVDS" section is new. BLVDS and M-LVDS are two new I/O standards included in the datasheet.                                         | 2-211 |  |  |  |

|              | The "CoreMP7 and Cortex-M1 Software Tools" section is new.                                                                                       | 2-257 |  |  |  |

|              | Table 2-83 • Summary of Maximum and Minimum DC Input and Output Levels           Applicable to Commercial and Industrial Conditions was updated. | 2-165 |  |  |  |

|              | Table 2-79 • Summary of I/O Timing Characteristics – Software Default Settings was updated.                                                      | 2-134 |  |  |  |

|              | Table 2-93 • I/O Output Buffer Maximum Resistances <sup>1</sup> was updated.                                                                     | 2-171 |  |  |  |

|              | The "BLVDS/M-LVDS" section is new. BLVDS and M-LVDS are two new I/O standards included in the datasheet.                                         | 2-211 |  |  |  |

|              | The "108-Pin QFN" table for the AFS090 device is new.                                                                                            | 3-2   |  |  |  |

|              | The "180-Pin QFN" table for the AFS090 device is new.                                                                                            | 3-4   |  |  |  |

|              | The "208-Pin PQFP" table for the AFS090 device is new.                                                                                           | 3-8   |  |  |  |

|              | The "256-Pin FBGA" table for the AFS090 device is new.                                                                                           | 3-12  |  |  |  |

|              | The "256-Pin FBGA" table for the AFS250 device is new.                                                                                           | 3-12  |  |  |  |