Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells |                                                               |

| Total RAM Bits                 | 110592                                                        |

| Number of I/O                  | 95                                                            |

| Number of Gates                | 600000                                                        |

| Voltage - Supply               | 1.425V ~ 1.575V                                               |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                               |

| Package / Case                 | 208-BFQFP                                                     |

| Supplier Device Package        | 208-PQFP (28x28)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/m1afs600-pq208 |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The on-chip crystal and RC oscillators work in conjunction with the integrated phase-locked loops (PLLs) to provide clocking support to the FPGA array and on-chip resources. In addition to supporting typical RTC uses such as watchdog timer, the Fusion RTC can control the on-chip voltage regulator to power down the device (FPGA fabric, flash memory block, and ADC), enabling a low power standby mode.

The Fusion family offers revolutionary features, never before available in an FPGA. The nonvolatile flash technology gives the Fusion solution the advantage of being a highly secure, low power, single-chip solution that is Instant On. Fusion is reprogrammable and offers time-to-market benefits at an ASIC-level unit cost. These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

# **Flash Advantages**

## Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, high performance, and ease of use. Flashbased Fusion devices are Instant On and do not need to be loaded from an external boot PROM.

On-board security mechanisms prevent access to the programming information and enable remote updates of the FPGA logic that are protected with high level security. Designers can perform remote insystem reprogramming to support future design iterations and field upgrades, with confidence that valuable IP is highly unlikely to be compromised or copied. ISP can be performed using the

industry-standard AES algorithm with MAC data authentication on the device. The Fusion family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the Fusion family a cost-effective ASIC replacement solution for applications in the consumer, networking and communications, computing, and avionics markets.

## Security

As the nonvolatile, flash-based Fusion family requires no boot PROM, there is no vulnerable external bitstream. Fusion devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

Fusion devices utilize a 128-bit flash-based key lock and a separate AES key to provide the highest level of protection in the FPGA industry for programmed IP and configuration data. The FlashROM data in Fusion devices can also be encrypted prior to loading. Additionally, the flash memory blocks can be programmed during runtime using the industry-leading AES-128 block cipher encryption standard (FIPS Publication 192). The AES standard was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the DES standard, which was adopted in 1977. Fusion devices have a

built-in AES decryption engine and a flash-based AES key that make Fusion devices the most comprehensive programmable logic device security solution available today. Fusion devices with

AES-based security provide a high level of protection for remote field updates over public networks, such as the Internet, and are designed to ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves. As an additional security measure, the FPGA configuration data of a programmed Fusion device cannot be read back, although secure design verification is possible. During design, the user controls and defines both internal and external access to the flash memory blocks.

Security, built into the FPGA fabric, is an inherent component of the Fusion family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. Fusion with FlashLock and AES security is unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with

industry-standard security, making remote ISP possible. A Fusion device provides the best available security for programmable logic designs.

# Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based Fusion FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

### VersaTile Characteristics

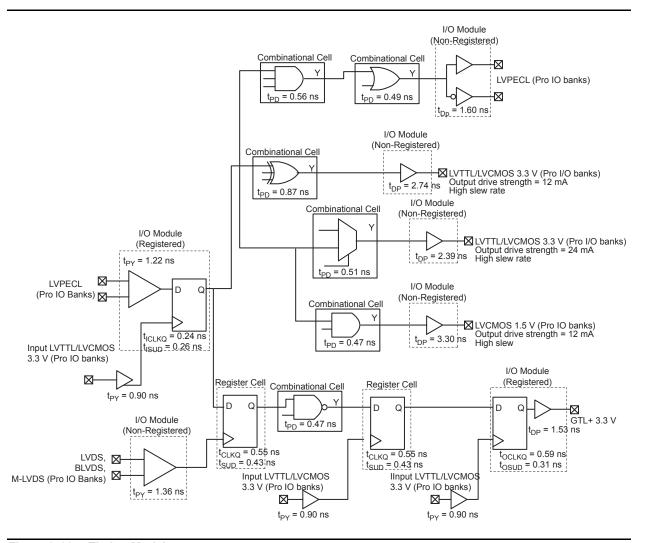

#### Sample VersaTile Specifications—Combinatorial Module

The Fusion library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library (Figure 2-3). For more details, refer to the *IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide*.

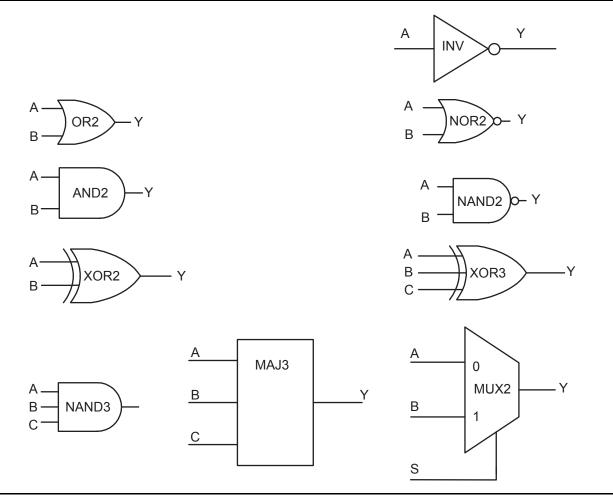

Figure 2-3 • Sample of Combinatorial Cells

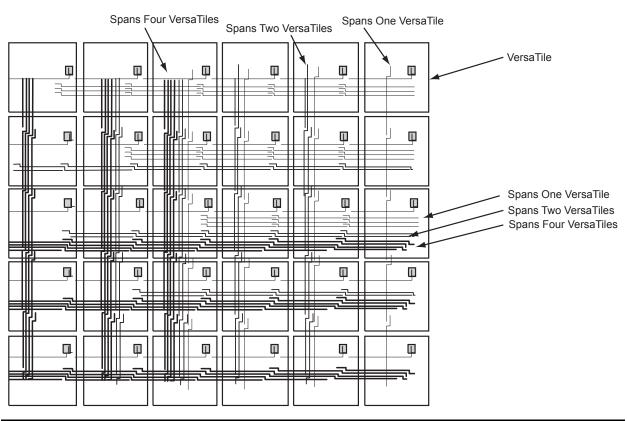

Figure 2-9 • Efficient Long-Line Resources

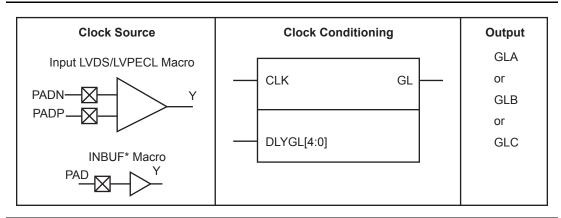

Figure 2-21 • Fusion CCC Options: Global Buffers with Programmable Delay

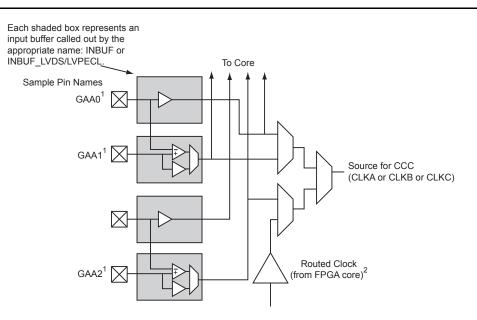

# **Global Input Selections**

Each global buffer, as well as the PLL reference clock, can be driven from one of the following (Figure 2-22):

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

- The FPGA core

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

#### Notes:

- 1. Represents the global input pins. Globals have direct access to the clock conditioning block and are not routed via the FPGA fabric. Refer to the "User I/O Naming Convention" section on page 2-158 for more information.

- 2. Instantiate the routed clock source input as follows:

- a) Connect the output of a logic element to the clock input of the PLL, CLKDLY, or CLKINT macro. b) Do not place a clock source I/O (INBUF or INBUF\_LVPECL/LVDS) in a relevant global pin location.

- 3. LVDS-based clock sources are available in the east and west banks on all Fusion devices.

#### Figure 2-22 • Clock Input Sources Including CLKBUF, CLKBUF\_LVDS/LVPECL, and CLKINT

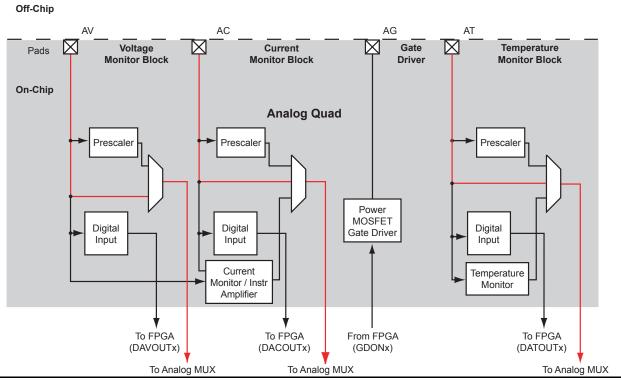

# Voltage Monitor

The Fusion Analog Quad offers a robust set of voltage-monitoring capabilities unique in the FPGA industry. The Analog Quad comprises three analog input pads— Analog Voltage (AV), Analog Current (AC), and Analog Temperature (AT)—and a single gate driver output pad, Analog Gate (AG). There are many common characteristics among the analog input pads. Each analog input can be configured to connect directly to the input MUX of the ADC. When configured in this manner (Figure 2-66), there will be no prescaling of the input signal. Care must be taken in this mode not to drive the ADC into saturation by applying an input voltage greater than the reference voltage. The internal reference voltage of the ADC is 2.56 V. Optionally, an external reference can be supplied by the user. The external reference can be a maximum of 3.3 V DC.

Figure 2-66 • Analog Quad Direct Connect

The Analog Quad offers a wide variety of prescaling options to enable the ADC to resolve the input signals. Figure 2-67 shows the path through the Analog Quad for a signal that is to be prescaled prior to conversion. The ADC internal reference voltage and the prescaler factors were selected to make both prescaling and postscaling of the signals easy binary calculations (refer to Table 2-57 on page 2-130 for details). When an analog input pad is configured with a prescaler, there will be a 1 M $\Omega$  resistor to ground. This occurs even when the device is in power-down mode. In low power standby or sleep mode (VCC is OFF, VCC33A is ON, VCCI is ON) or when the resource is not used, analog inputs are pulled down to ground through a 1 M $\Omega$  resistor. The gate driver output is floating (or tristated), and there is no extra current on VCC33A.

These scaling factors hold true whether the particular pad is configured to accept a positive or negative voltage. Note that whereas the AV and AC pads support the same prescaling factors, the AT pad supports a reduced set of prescaling factors and supports positive voltages only.

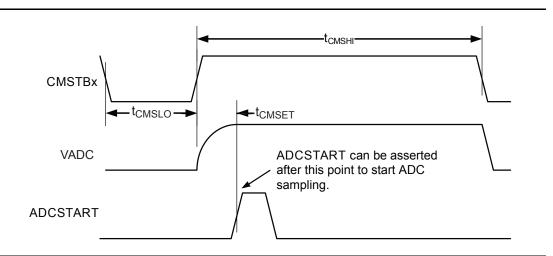

To initiate a current measurement, the appropriate Current Monitor Strobe (CMSTB) signal on the AB macro must be asserted low for at least  $t_{CMSLO}$  in order to discharge the previous measurement. Then CMSTB must be asserted high for at least  $t_{CMSET}$  prior to asserting the ADCSTART signal. The CMSTB must remain high until after the SAMPLE signal is de-asserted by the AB macro. Note that the minimum sample time cannot be less than  $t_{CMSHI}$ . Figure 2-71 shows the timing diagram of CMSTB in relationship with the ADC control signals.

Figure 2-71 • Timing Diagram for Current Monitor Strobe

Figure 2-72 illustrates positive current monitor operation. The differential voltage between AV and AC goes into the 10× amplifier and is then converted by the ADC. For example, a current of 1.5 A is drawn from a 10 V supply and is measured by the voltage drop across a 0.050  $\Omega$  sense resistor, The voltage drop is amplified by ten times by the amplifier and then measured by the ADC. The 1.5 A current creates a differential voltage across the sense resistor of 75 mV. This becomes 750 mV after amplification. Thus, the ADC measures a current of 1.5 A as 750 mV. Using an ADC with 8-bit resolution and VAREF of 2.56 V, the ADC result is decimal 75. EQ 3 shows how to compute the current from the ADC result.

$$||| = (ADC \times V_{AREF}) / (10 \times 2^{N} \times R_{sense})$$

EQ 3

where

I is the current flowing through the sense resistor

ADC is the result from the ADC

VAREF is the Reference voltage

N is the number of bits

Rsense is the resistance of the sense resistor

|                                   |                        |              | al Char<br>ror (LS | -            |            | el Inpu<br>rror (LS | t Offset<br>SB) |              | nel Input<br>Error (m\ |              | Chan | nel Gaiı<br>(%FSR |      |

|-----------------------------------|------------------------|--------------|--------------------|--------------|------------|---------------------|-----------------|--------------|------------------------|--------------|------|-------------------|------|

| Analog<br>Pad                     | Prescaler<br>Range (V) | Neg.<br>Max. | Med.               | Pos.<br>Max. | Neg<br>Max | Med.                | Pos.<br>Max.    | Neg.<br>Max. | Med.                   | Pos.<br>Max. | Min. | Тур.              | Max. |

| Positive Range ADC in 10-Bit Mode |                        |              |                    |              |            |                     |                 |              |                        |              |      |                   |      |

| AV, AC                            | 16                     | -22          | -2                 | 12           | -11        | -2                  | 14              | -169         | -32                    | 224          | 3    | 0                 | -3   |

|                                   | 8                      | -40          | -5                 | 17           | -11        | -5                  | 21              | -87          | -40                    | 166          | 2    | 0                 | -4   |

|                                   | 4                      | -45          | -9                 | 24           | -16        | -11                 | 36              | -63          | -43                    | 144          | 2    | 0                 | -4   |

|                                   | 2                      | -70          | -19                | 33           | -33        | -20                 | 66              | -66          | -39                    | 131          | 2    | 0                 | -4   |

|                                   | 1                      | -25          | -7                 | 5            | -11        | -3                  | 26              | -11          | -3                     | 26           | 3    | –1                | -3   |

|                                   | 0.5                    | -41          | -12                | 8            | -12        | -7                  | 38              | -6           | -4                     | 19           | 3    | -1                | -3   |

|                                   | 0.25                   | -53          | -14                | 19           | -20        | -14                 | 40              | -5           | -3                     | 10           | 5    | 0                 | -4   |

|                                   | 0.125                  | -89          | -29                | 24           | -40        | -28                 | 88              | -5           | -4                     | 11           | 7    | 0                 | -5   |

| AT                                | 16                     | -3           | 9                  | 15           | -4         | 0                   | 4               | -64          | 5                      | 64           | 1    | 0                 | -1   |

|                                   | 4                      | -10          | 2                  | 15           | -11        | -2                  | 11              | -44          | -8                     | 44           | 1    | 0                 | -1   |

| Negati                            | ve Range               |              |                    |              |            |                     | ADC in          | 10-Bit N     | lode                   |              |      |                   |      |

| AV, AC                            | 16                     | -35          | -10                | 9            | -24        | -6                  | 9               | -383         | -96                    | 148          | 5    | -1                | -6   |

|                                   | 8                      | -65          | -19                | 12           | -34        | -12                 | 9               | -268         | -99                    | 75           | 5    | -1                | -5   |

|                                   | 4                      | -86          | -28                | 21           | -64        | -24                 | 19              | -254         | -96                    | 76           | 5    | –1                | -6   |

|                                   | 2                      | -136         | -53                | 37           | -115       | -42                 | 39              | -230         | -83                    | 78           | 6    | -2                | -7   |

|                                   | 1                      | -98          | -35                | 8            | -39        | -8                  | 15              | -39          | -8                     | 15           | 10   | -3                | -10  |

|                                   | 0.5                    | -121         | -46                | 7            | -54        | -14                 | 18              | -27          | -7                     | 9            | 10   | -4                | -11  |

|                                   | 0.25                   | -149         | -49                | 19           | -72        | -16                 | 40              | -18          | -4                     | 10           | 14   | -4                | -12  |

|                                   | 0.125                  | -188         | -67                | 38           | -112       | -27                 | 56              | -14          | -3                     | 7            | 16   | -5                | -14  |

# Table 2-51 • Uncalibrated Analog Channel Accuracy\*Worst-Case Industrial Conditions, TJ = 85°C

*Note:* \*Channel Accuracy includes prescaler and ADC accuracies. For 12-bit mode, multiply the LSB count by 4. For 8-bit mode, divide the LSB count by 4. Gain remains the same.

Device Architecture

Similarly,

Min. Output Voltage = (Max. Negative input offset) + (Input Voltage x Max. Negative Channel Gain) =  $(-88 \text{ mV}) + (5 \text{ V} \times 0.96) = 4.712 \text{ V}$

#### Calculating Accuracy for a Calibrated Analog Channel

#### Formula

For a given prescaler range, EQ 31 gives the output voltage.

Output Voltage = Channel Error in V + Input Voltage

EQ 31

where

Channel Error in V = Total Channel Error in LSBs x Equivalent voltage per LSB

#### Example

Input Voltage = 5 VChosen Prescaler range = 8 V range Refer to Table 2-52 on page 2-123.

Max. Output Voltage = Max. Positive Channel Error in V + Input Voltage Max. Positive Channel Error in V = (6 LSB) × (8 mV per LSB in 10-bit mode) = 48 mV Max. Output Voltage = 48 mV + 5 V = **5.048 V**

Similarly,

Min. Output Voltage = Max. Negative Channel Error in V + Input Voltage = (-48 mV) + 5 V = 4.952 V

#### Calculating LSBs from a Given Error Budget

#### Formula

For a given prescaler range, LSB count = ± (Input Voltage × Required % error) / (Equivalent voltage per LSB)

#### Example

Input Voltage =  $3.3 \vee$ Required error margin= 1% Refer to Table 2-52 on page 2-123. Equivalent voltage per LSB = 16 mV for a 16V prescaler, with ADC in 10-bit mode LSB Count =  $\pm (5.0 \vee \times 1\%) / (0.016)$ LSB Count =  $\pm 3.125$ Equivalent voltage per LSB = 8 mV for an  $8 \vee$  prescaler, with ADC in 10-bit mode LSB Count =  $\pm (5.0 \vee \times 1\%) / (0.008)$ LSB Count =  $\pm (5.0 \vee \times 1\%) / (0.008)$ LSB Count =  $\pm 6.25$ The  $8 \vee$  prescaler satisfies the calculated LSB count accuracy requirement (see Table 2-52 on page 2-123).

Device Architecture

#### Table 2-77 • Comparison Table for 5 V–Compliant Receiver Scheme

| Scheme | Board Components                                                                                                                                                           | Speed                    | Current Limitations                                                                                                                                                                                                                                                                                                                          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Two resistors                                                                                                                                                              | Low to high <sup>1</sup> | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                      |

| 2      | Resistor and Zener 3.3 V                                                                                                                                                   | Medium                   | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                      |

| 3      | Bus switch                                                                                                                                                                 | High                     | N/A                                                                                                                                                                                                                                                                                                                                          |

| 4      | Minimum resistor value <sup>2</sup><br>R = 47 $\Omega$ at T <sub>J</sub> = 70°C<br>R = 150 $\Omega$ at T <sub>J</sub> = 85°C<br>R = 420 $\Omega$ at T <sub>J</sub> = 100°C | Medium                   | Maximum diode current at 100% duty cycle, signal constantly at<br>'1'<br>52.7 mA at $T_J = 70^{\circ}C / 10$ -year lifetime<br>16.5 mA at $T_J = 85^{\circ}C / 10$ -year lifetime<br>5.9 mA at $T_J = 100^{\circ}C / 10$ -year lifetime<br>For duty cycles other than 100%, the currents can be increased<br>by a factor = 1 / (duty cycle). |

|        |                                                                                                                                                                            |                          | Example: 20% duty cycle at 70°C<br>Maximum current = (1 / 0.2) * 52.7 mA = 5 * 52.7 mA = 263.5 mA                                                                                                                                                                                                                                            |

Notes:

1. Speed and current consumption increase as the board resistance values decrease.

2. Resistor values ensure I/O diode long-term reliability.

# **User I/O Characteristics**

# Timing Model

| Figure 2-115 • Timing Model                                                           |  |

|---------------------------------------------------------------------------------------|--|

| Operating Conditions: -2 Speed, Commercial Temperature Range (T <sub>J</sub> = 70°C), |  |

| Worst-Case VCC = 1.425 V                                                              |  |

#### Table 2-106 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Applicab | le to Advar | iced I/Os |

|----------|-------------|-----------|

|          |             |           |

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 10.26           | 0.04             | 1.20            | 0.43              | 10.45           | 8.90            | 2.64            | 2.46            | 12.68            | 11.13            | ns    |

|                   | -1             | 0.56              | 8.72            | 0.04             | 1.02            | 0.36              | 8.89            | 7.57            | 2.25            | 2.09            | 10.79            | 9.47             | ns    |

|                   | -2             | 0.49              | 7.66            | 0.03             | 0.90            | 0.32              | 7.80            | 6.64            | 1.98            | 1.83            | 9.47             | 8.31             | ns    |

| 8 mA              | Std.           | 0.66              | 7.27            | 0.04             | 1.20            | 0.43              | 7.41            | 6.28            | 2.98            | 3.04            | 9.65             | 8.52             | ns    |

|                   | -1             | 0.56              | 6.19            | 0.04             | 1.02            | 0.36              | 6.30            | 5.35            | 2.54            | 2.59            | 8.20             | 7.25             | ns    |

|                   | -2             | 0.49              | 5.43            | 0.03             | 0.90            | 0.32              | 5.53            | 4.69            | 2.23            | 2.27            | 7.20             | 6.36             | ns    |

| 12 mA             | Std.           | 0.66              | 5.58            | 0.04             | 1.20            | 0.43              | 5.68            | 4.87            | 3.21            | 3.42            | 7.92             | 7.11             | ns    |

|                   | -1             | 0.56              | 4.75            | 0.04             | 1.02            | 0.36              | 4.84            | 4.14            | 2.73            | 2.91            | 6.74             | 6.05             | ns    |

|                   | -2             | 0.49              | 4.17            | 0.03             | 0.90            | 0.32              | 4.24            | 3.64            | 2.39            | 2.55            | 5.91             | 5.31             | ns    |

| 16 mA             | Std.           | 0.66              | 5.21            | 0.04             | 1.20            | 0.43              | 5.30            | 4.56            | 3.26            | 3.51            | 7.54             | 6.80             | ns    |

|                   | -1             | 0.56              | 4.43            | 0.04             | 1.02            | 0.36              | 4.51            | 3.88            | 2.77            | 2.99            | 6.41             | 5.79             | ns    |

|                   | -2             | 0.49              | 3.89            | 0.03             | 0.90            | 0.32              | 3.96            | 3.41            | 2.43            | 2.62            | 5.63             | 5.08             | ns    |

| 24 mA             | Std.           | 0.66              | 4.85            | 0.04             | 1.20            | 0.43              | 4.94            | 4.54            | 3.32            | 3.88            | 7.18             | 6.78             | ns    |

|                   | -1             | 0.56              | 4.13            | 0.04             | 1.02            | 0.36              | 4.20            | 3.87            | 2.82            | 3.30            | 6.10             | 5.77             | ns    |

|                   | -2             | 0.49              | 3.62            | 0.03             | 0.90            | 0.32              | 3.69            | 3.39            | 2.48            | 2.90            | 5.36             | 5.06             | ns    |

#### Timing Characteristics

#### Table 2-112 • 2.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os

| Drive    | Speed |                   |                 |                  |                 |                  |                   |                 |                 |                 |                 |                  |                  |       |

|----------|-------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Strength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 4 mA     | Std.  | 0.60              | 12.00           | 0.04             | 1.51            | 1.66             | 0.43              | 12.23           | 11.61           | 2.72            | 2.20            | 14.46            | 13.85            | ns    |

|          | -1    | 0.51              | 10.21           | 0.04             | 1.29            | 1.41             | 0.36              | 10.40           | 9.88            | 2.31            | 1.87            | 12.30            | 11.78            | ns    |

|          | -2    | 0.45              | 8.96            | 0.03             | 1.13            | 1.24             | 0.32              | 9.13            | 8.67            | 2.03            | 1.64            | 10.80            | 10.34            | ns    |

| 8 mA     | Std.  | 0.60              | 8.73            | 0.04             | 1.51            | 1.66             | 0.43              | 8.89            | 8.01            | 3.10            | 2.93            | 11.13            | 10.25            | ns    |

|          | -1    | 0.51              | 7.43            | 0.04             | 1.29            | 1.41             | 0.36              | 7.57            | 6.82            | 2.64            | 2.49            | 9.47             | 8.72             | ns    |

|          | -2    | 0.45              | 6.52            | 0.03             | 1.13            | 1.24             | 0.32              | 6.64            | 5.98            | 2.32            | 2.19            | 8.31             | 7.65             | ns    |

| 12 mA    | Std.  | 0.66              | 6.77            | 0.04             | 1.51            | 1.66             | 0.43              | 6.90            | 6.11            | 3.37            | 3.39            | 9.14             | 8.34             | ns    |

|          | -1    | 0.56              | 5.76            | 0.04             | 1.29            | 1.41             | 0.36              | 5.87            | 5.20            | 2.86            | 2.89            | 7.77             | 7.10             | ns    |

|          | -2    | 0.49              | 5.06            | 0.03             | 1.13            | 1.24             | 0.32              | 5.15            | 4.56            | 2.51            | 2.53            | 6.82             | 6.23             | ns    |

| 16 mA    | Std.  | 0.66              | 6.31            | 0.04             | 1.51            | 1.66             | 0.43              | 6.42            | 5.73            | 3.42            | 3.52            | 8.66             | 7.96             | ns    |

|          | -1    | 0.56              | 5.37            | 0.04             | 1.29            | 1.41             | 0.36              | 5.46            | 4.87            | 2.91            | 3.00            | 7.37             | 6.77             | ns    |

|          | -2    | 0.49              | 4.71            | 0.03             | 1.13            | 1.24             | 0.32              | 4.80            | 4.28            | 2.56            | 2.63            | 6.47             | 5.95             | ns    |

| 24 mA    | Std.  | 0.66              | 5.93            | 0.04             | 1.51            | 1.66             | 0.43              | 6.04            | 5.70            | 3.49            | 4.00            | 8.28             | 7.94             | ns    |

|          | -1    | 0.56              | 5.05            | 0.04             | 1.29            | 1.41             | 0.36              | 5.14            | 4.85            | 2.97            | 3.40            | 7.04             | 6.75             | ns    |

|          | -2    | 0.49              | 4.43            | 0.03             | 1.13            | 1.24             | 0.32              | 4.51            | 4.26            | 2.61            | 2.99            | 6.18             | 5.93             | ns    |

# **Microsemi**

Device Architecture

#### Table 2-123 • 1.8 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 11.86           | 0.04             | 1.22            | 0.43              | 9.14            | 11.86           | 2.77            | 1.66            | 11.37            | 14.10            | ns    |

|                   | -1             | 0.56              | 10.09           | 0.04             | 1.04            | 0.36              | 7.77            | 10.09           | 2.36            | 1.41            | 9.67             | 11.99            | ns    |

|                   | -2             | 0.49              | 8.86            | 0.03             | 0.91            | 0.32              | 6.82            | 8.86            | 2.07            | 1.24            | 8.49             | 10.53            | ns    |

| 4 mA              | Std.           | 0.66              | 6.91            | 0.04             | 1.22            | 0.43              | 5.86            | 6.91            | 3.22            | 2.84            | 8.10             | 9.15             | ns    |

|                   | -1             | 0.56              | 5.88            | 0.04             | 1.04            | 0.36              | 4.99            | 5.88            | 2.74            | 2.41            | 6.89             | 7.78             | ns    |

|                   | -2             | 0.49              | 5.16            | 0.03             | 0.91            | 0.32              | 4.38            | 5.16            | 2.41            | 2.12            | 6.05             | 6.83             | ns    |

| 8 mA              | Std.           | 0.66              | 4.45            | 0.04             | 1.22            | 0.43              | 4.18            | 4.45            | 3.53            | 3.38            | 6.42             | 6.68             | ns    |

|                   | -1             | 0.56              | 3.78            | 0.04             | 1.04            | 0.36              | 3.56            | 3.78            | 3.00            | 2.88            | 5.46             | 5.69             | ns    |

|                   | -2             | 0.49              | 3.32            | 0.03             | 0.91            | 0.32              | 3.12            | 3.32            | 2.64            | 2.53            | 4.79             | 4.99             | ns    |

| 12 mA             | Std.           | 0.66              | 3.92            | 0.04             | 1.22            | 0.43              | 3.93            | 3.92            | 3.60            | 3.52            | 6.16             | 6.16             | ns    |

|                   | -1             | 0.56              | 3.34            | 0.04             | 1.04            | 0.36              | 3.34            | 3.34            | 3.06            | 3.00            | 5.24             | 5.24             | ns    |

|                   | -2             | 0.49              | 2.93            | 0.03             | 0.91            | 0.32              | 2.93            | 2.93            | 2.69            | 2.63            | 4.60             | 4.60             | ns    |

| 16 mA             | Std.           | 0.66              | 3.53            | 0.04             | 1.22            | 0.43              | 3.60            | 3.04            | 3.70            | 4.08            | 5.84             | 5.28             | ns    |

|                   | -1             | 0.56              | 3.01            | 0.04             | 1.04            | 0.36              | 3.06            | 2.59            | 3.15            | 3.47            | 4.96             | 4.49             | ns    |

|                   | -2             | 0.49              | 2.64            | 0.03             | 0.91            | 0.32              | 2.69            | 2.27            | 2.76            | 3.05            | 4.36             | 3.94             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Table 2-124 • 1.8 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 15.01           | 0.04             | 1.20            | 0.43              | 13.15           | 15.01           | 1.99            | 1.99            | ns    |

|                   | -1             | 0.56              | 12.77           | 0.04             | 1.02            | 0.36              | 11.19           | 12.77           | 1.70            | 1.70            | ns    |

|                   | -2             | 0.49              | 11.21           | 0.03             | 0.90            | 0.32              | 9.82            | 11.21           | 1.49            | 1.49            | ns    |

| 4 mA              | Std.           | 0.66              | 10.10           | 0.04             | 1.20            | 0.43              | 9.55            | 10.10           | 2.41            | 2.37            | ns    |

|                   | -1             | 0.56              | 8.59            | 0.04             | 1.02            | 0.36              | 8.13            | 8.59            | 2.05            | 2.02            | ns    |

|                   | -2             | 0.49              | 7.54            | 0.03             | 0.90            | 0.32              | 7.13            | 7.54            | 1.80            | 1.77            | ns    |

#### Timing Characteristics

Table 2-128 • 1.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 14.11           | 0.04             | 1.70            | 2.14             | 0.43              | 14.37           | 13.14           | 3.40            | 2.68            | 16.61            | 15.37            | ns    |

|                   | –1             | 0.56              | 12.00           | 0.04             | 1.44            | 1.82             | 0.36              | 12.22           | 11.17           | 2.90            | 2.28            | 14.13            | 13.08            | ns    |

|                   | -2             | 0.49              | 10.54           | 0.03             | 1.27            | 1.60             | 0.32              | 10.73           | 9.81            | 2.54            | 2.00            | 12.40            | 11.48            | ns    |

| 4 mA              | Std.           | 0.66              | 11.23           | 0.04             | 1.70            | 2.14             | 0.43              | 11.44           | 9.87            | 3.77            | 3.36            | 13.68            | 12.10            | ns    |

|                   | –1             | 0.56              | 9.55            | 0.04             | 1.44            | 1.82             | 0.36              | 9.73            | 8.39            | 3.21            | 2.86            | 11.63            | 10.29            | ns    |

|                   | -2             | 0.49              | 8.39            | 0.03             | 1.27            | 1.60             | 0.32              | 8.54            | 7.37            | 2.81            | 2.51            | 10.21            | 9.04             | ns    |

| 8 mA              | Std.           | 0.66              | 10.45           | 0.04             | 1.70            | 2.14             | 0.43              | 10.65           | 9.24            | 3.84            | 3.55            | 12.88            | 11.48            | ns    |

|                   | –1             | 0.56              | 8.89            | 0.04             | 1.44            | 1.82             | 0.36              | 9.06            | 7.86            | 3.27            | 3.02            | 10.96            | 9.76             | ns    |

|                   | -2             | 0.49              | 7.81            | 0.03             | 1.27            | 1.60             | 0.32              | 7.95            | 6.90            | 2.87            | 2.65            | 9.62             | 8.57             | ns    |

| 12 mA             | Std.           | 0.66              | 10.02           | 0.04             | 1.70            | 2.14             | 0.43              | 10.20           | 9.23            | 3.97            | 4.22            | 12.44            | 11.47            | ns    |

|                   | –1             | 0.56              | 8.52            | 0.04             | 1.44            | 1.82             | 0.36              | 8.68            | 7.85            | 3.38            | 3.59            | 10.58            | 9.75             | ns    |

|                   | -2             | 0.49              | 7.48            | 0.03             | 1.27            | 1.60             | 0.32              | 7.62            | 6.89            | 2.97            | 3.15            | 9.29             | 8.56             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Table 2-129 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOU</sub><br>т | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-----------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 8.53            | 0.04             | 1.70            | 2.14             | 0.43                  | 7.26            | 8.53            | 3.39            | 2.79            | 9.50             | 10.77            | ns    |

|                   | -1             | 0.56              | 7.26            | 0.04             | 1.44            | 1.82             | 0.36                  | 6.18            | 7.26            | 2.89            | 2.37            | 8.08             | 9.16             | ns    |

|                   | -2             | 0.49              | 6.37            | 0.03             | 1.27            | 1.60             | 0.32                  | 5.42            | 6.37            | 2.53            | 2.08            | 7.09             | 8.04             | ns    |

| 4 mA              | Std.           | 0.66              | 5.41            | 0.04             | 1.70            | 2.14             | 0.43                  | 5.22            | 5.41            | 3.75            | 3.48            | 7.45             | 7.65             | ns    |

|                   | -1             | 0.56              | 4.60            | 0.04             | 1.44            | 1.82             | 0.36                  | 4.44            | 4.60            | 3.19            | 2.96            | 6.34             | 6.50             | ns    |

|                   | -2             | 0.49              | 4.04            | 0.03             | 1.27            | 1.60             | 0.32                  | 3.89            | 4.04            | 2.80            | 2.60            | 5.56             | 5.71             | ns    |

| 8 mA              | Std.           | 0.66              | 4.80            | 0.04             | 1.70            | 2.14             | 0.43                  | 4.89            | 4.75            | 3.83            | 3.67            | 7.13             | 6.98             | ns    |

|                   | -1             | 0.56              | 4.09            | 0.04             | 1.44            | 1.82             | 0.36                  | 4.16            | 4.04            | 3.26            | 3.12            | 6.06             | 5.94             | ns    |

|                   | -2             | 0.49              | 3.59            | 0.03             | 1.27            | 1.60             | 0.32                  | 3.65            | 3.54            | 2.86            | 2.74            | 5.32             | 5.21             | ns    |

| 12 mA             | Std.           | 0.66              | 4.42            | 0.04             | 1.70            | 2.14             | 0.43                  | 4.50            | 3.62            | 3.96            | 4.37            | 6.74             | 5.86             | ns    |

|                   | -1             | 0.56              | 3.76            | 0.04             | 1.44            | 1.82             | 0.36                  | 3.83            | 3.08            | 3.37            | 3.72            | 5.73             | 4.98             | ns    |

|                   | -2             | 0.49              | 3.30            | 0.03             | 1.27            | 1.60             | 0.32                  | 3.36            | 2.70            | 2.96            | 3.27            | 5.03             | 4.37             | ns    |

#### Table 2-174 • Parameter Definitions and Measuring Nodes

| Parameter<br>Name     | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>OCLKQ</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L,DOUT                         |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                 | К, Н                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | К, Н                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

*Note:* \*See Figure 2-137 on page 2-212 for more information.

#### Table 3-12 • Summary of I/O Input Buffer Power (per pin)—Default I/O Software Settings (continued)

|                                  | VCCI (V) | Static Power<br>PDC7 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (µW/MHz) <sup>2</sup> |

|----------------------------------|----------|----------------------------------------|---------------------------------------------|

| Applicable to Advanced I/O Banks |          |                                        |                                             |

| Single-Ended                     |          |                                        |                                             |

| 3.3 V LVTTL/LVCMOS               | 3.3      | _                                      | 16.69                                       |

| 2.5 V LVCMOS                     | 2.5      | _                                      | 5.12                                        |

| 1.8 V LVCMOS                     | 1.8      | _                                      | 2.13                                        |

| 1.5 V LVCMOS (JESD8-11)          | 1.5      | _                                      | 1.45                                        |

| 3.3 V PCI                        | 3.3      | _                                      | 18.11                                       |

| 3.3 V PCI-X                      | 3.3      | _                                      | 18.11                                       |

| Differential                     |          |                                        |                                             |

| LVDS                             | 2.5      | 2.26                                   | 1.20                                        |

| LVPECL                           | 3.3      | 5.72                                   | 1.87                                        |

| Applicable to Standard I/O Banks | · ·      |                                        | •                                           |

| 3.3 V LVTTL/LVCMOS               | 3.3      | _                                      | 16.79                                       |

| 2.5 V LVCMOS                     | 2.5      | _                                      | 5.19                                        |

| 1.8 V LVCMOS                     | 1.8      | _                                      | 2.18                                        |

| 1.5 V LVCMOS (JESD8-11)          | 1.5      | _                                      | 1.52                                        |

Notes:

1. PDC7 is the static power (where applicable) measured on VCCI.

2. PAC9 is the total dynamic power measured on VCC and VCCI.

### Methodology

#### Total Power Consumption—PTOTAL

#### Operating Mode, Standby Mode, and Sleep Mode

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—P<sub>STAT</sub>

#### **Operating Mode**

$\label{eq:pstat} \begin{array}{l} \mathsf{P}_{\mathsf{STAT}} = \mathsf{PDC1} + (\mathsf{N}_{\mathsf{NVM-BLOCKS}} * \mathsf{PDC4}) + \mathsf{PDC5} + (\mathsf{N}_{\mathsf{QUADS}} * \mathsf{PDC6}) + (\mathsf{N}_{\mathsf{INPUTS}} * \mathsf{PDC7}) + (\mathsf{N}_{\mathsf{OUTPUTS}} * \mathsf{PDC8}) + (\mathsf{N}_{\mathsf{PLLS}} * \mathsf{PDC9}) \end{array}$

$N_{\ensuremath{\mathsf{NVM}}\xspace-BLOCKS}$  is the number of NVM blocks available in the device.

N<sub>QUADS</sub> is the number of Analog Quads used in the design.

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

N<sub>PLLS</sub> is the number of PLLs available in the device.

#### Standby Mode

P<sub>STAT</sub> = PDC2

#### Sleep Mode

P<sub>STAT</sub> = PDC3

#### Total Dynamic Power Consumption—P<sub>DYN</sub>

#### **Operating Mode**

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub> + P<sub>NVM</sub>+ P<sub>XTL-OSC</sub> + P<sub>RC-OSC</sub> + P<sub>AB</sub>

#### Standby Mode

$P_{DYN} = P_{XTL-OSC}$

Sleep Mode

$P_{DYN} = 0 W$

#### Global Clock Dynamic Contribution—P<sub>CLOCK</sub>

#### **Operating Mode**

$P_{CLOCK} = (PAC1 + N_{SPINE} * PAC2 + N_{ROW} * PAC3 + N_{S-CELL} * PAC4) * F_{CLK}$

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *Fusion and Extended Temperature Fusion FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *Fusion and Extended Temperature Fusion FPGA Fabric User's Guide*.

$\mathsf{F}_{\mathsf{CLK}}$  is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

#### Standby Mode and Sleep Mode

$P_{CLOCK} = 0 W$

#### Sequential Cells Dynamic Contribution—P<sub>S-CELL</sub>

#### **Operating Mode**

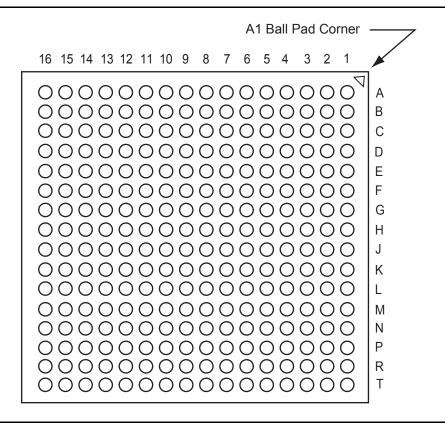

# FG256

# Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

# **Datasheet Categories**

#### Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "Fusion Device Status" table, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

#### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

#### Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

#### Production

This version contains information that is considered to be final.

# **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.