#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

|                            |                                                                       |

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                       |

| Number of I/O              | 28                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 14x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl04z32vlc4r |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.4 Voltage and current operating ratings

Table 4. Voltage and current operating ratings

| Symbol           | Description                                                               | Min.                  | Max.                  | Unit |

|------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| $V_{DD}$         | Digital supply voltage                                                    | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>  | Digital supply current                                                    | —                     | 120                   | mA   |

| V <sub>IO</sub>  | IO pin input voltage                                                      | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| Ι <sub>D</sub>   | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub> | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

# 2 General

## 2.1 AC electrical characteristics

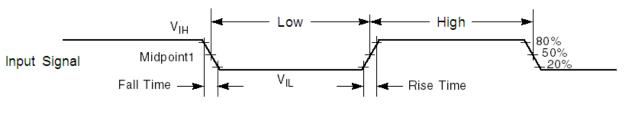

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL}$  +  $(V_{IH} - V_{IL})/2$ .

#### Figure 1. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume the output pins have the following characteristics.

- $C_L=30 \text{ pF loads}$

- Slew rate disabled

- Normal drive strength

## 2.2 Nonswitching electrical specifications

# 2.2.1 Voltage and current operating requirements

Table 5. Voltage and current operating requirements

| Symbol              | Description                                                                                                                                                                                                                     | Min.                 | Max.                 | Unit | Notes |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DD</sub>     | Supply voltage                                                                                                                                                                                                                  | 1.71                 | 3.6                  | V    |       |

| V <sub>DDA</sub>    | Analog supply voltage                                                                                                                                                                                                           | 1.71                 | 3.6                  | V    | _     |

| $V_{DD} - V_{DDA}$  | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                                                                                                                                       | -0.1                 | 0.1                  | V    | _     |

| $V_{SS} - V_{SSA}$  | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                                                                                                                                                       | -0.1                 | 0.1                  | V    | —     |

| V <sub>IH</sub>     | Input high voltage                                                                                                                                                                                                              |                      |                      |      | _     |

|                     | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                                                                                                                     | $0.7 \times V_{DD}$  | _                    | V    |       |

|                     | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                                                                                    | $0.75 \times V_{DD}$ | _                    | V    |       |

| V <sub>IL</sub>     | Input low voltage                                                                                                                                                                                                               |                      |                      |      | _     |

|                     | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                                                                                                                     | _                    | $0.35 \times V_{DD}$ | V    |       |

|                     | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                                                                                                                                                    | _                    | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>    | Input hysteresis                                                                                                                                                                                                                | $0.06 \times V_{DD}$ |                      | V    |       |

| I <sub>ICIO</sub>   | <ul> <li>IO pin negative DC injection current—single pin</li> <li>V<sub>IN</sub> &lt; V<sub>SS</sub>-0.3V (negative current injection)</li> <li>V<sub>IN</sub> &lt; V<sub>SS</sub>-0.3V (positive current injection)</li> </ul> | _3<br>               |                      | mA   | 1     |

| I <sub>ICcont</sub> | Contiguous pin DC injection current —regional limit,<br>includes sum of negative injection currents or sum of<br>positive injection currents of 16 contiguous pins                                                              |                      |                      |      | _     |

|                     | Negative current injection                                                                                                                                                                                                      | -25                  | —                    | mA   |       |

|                     | Positive current injection                                                                                                                                                                                                      | _                    | +25                  |      |       |

| V <sub>ODPU</sub>   | Open drain pullup voltage level                                                                                                                                                                                                 | V <sub>DD</sub>      | V <sub>DD</sub>      | V    | 2     |

| V <sub>RAM</sub>    | V <sub>DD</sub> voltage required to retain RAM                                                                                                                                                                                  | 1.2                  | —                    | V    | _     |

All IO pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> through ESD protection diodes. If V<sub>IN</sub> is greater than V<sub>IO\_MIN</sub> (=V<sub>SS</sub>-0.3V) and V<sub>IN</sub> is less than V<sub>IO\_MAX</sub>(=V<sub>DD</sub>+0.3V) is observed, then there is no need to provide current limiting resistors at the pads. If these limits cannot be observed then a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>IO\_MIN</sub>-V<sub>IN</sub>)/II<sub>CIO</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>IO\_MIN</sub>-V<sub>IN</sub>)/II<sub>CIO</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>IN</sub>-V<sub>IO\_MAX</sub>)/II<sub>CIO</sub>I. Select the larger of these two calculated resistances.

2. Open drain outputs must be pulled to  $V_{DD}$ .

# 2.2.2 LVD and POR operating requirements

#### Table 6. V<sub>DD</sub> supply LVD and POR operating requirements

| Symbol            | Description                                                   | Min. | Тур. | Max. | Unit | Notes |

|-------------------|---------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>  | Falling V <sub>DD</sub> POR detect voltage                    | 0.8  | 1.1  | 1.5  | V    | —     |

| V <sub>LVDH</sub> | Falling low-voltage detect threshold — high range (LVDV = 01) | 2.48 | 2.56 | 2.64 | V    | —     |

|                   | Low-voltage warning thresholds — high range                   |      |      |      |      | 1     |

| Symbol                 | Description                                                                                                                                                                | Min. | Тур.  | Max. <sup>1</sup> | Unit | Notes |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------|------|-------|

| I <sub>DD_WAIT</sub>   | Wait mode current - core disabled / 24 MHz<br>system / 24 MHz bus / flash disabled (flash<br>doze enabled), all peripheral clocks disabled<br>• at 3.0 V                   | _    | 2.2   | 2.3               | mA   | 3     |

| I <sub>DD_PSTOP2</sub> | Stop mode current with partial stop 2 clocking<br>option - core and system disabled / 10.5 MHz<br>bus / flash disabled (flash doze enabled)<br>• at 3.0 V                  | _    | 1.5   | 1.7               | mA   | 3     |

| I <sub>DD_VLPRCO</sub> | Very-low-power run mode current in compute<br>operation - 4 MHz core / 0.8 MHz flash / bus<br>clock disabled, code executing from flash<br>• at 3.0 V                      | _    | 182   | 253               | μA   | 5     |

| I <sub>DD_VLPR</sub>   | Very low power run mode current - 4 MHz<br>core / 0.8 MHz bus and flash, all peripheral<br>clocks disabled, code executing from flash<br>• at 3.0 V                        | _    | 213   | 284               | μA   | 5     |

| I <sub>DD_VLPR</sub>   | Very low power run mode current - 4 MHz<br>core / 0.8 MHz bus and flash, all peripheral<br>clocks enabled, code executing from flash<br>• at 3.0 V                         | _    | 243   | 313               | μA   | 4, 5  |

| I <sub>DD_VLPW</sub>   | Very low power wait mode current - core<br>disabled / 4 MHz system / 0.8 MHz bus / flash<br>disabled (flash doze enabled), all peripheral<br>clocks disabled<br>• at 3.0 V | _    | 111   | 170               | μA   | 5     |

| I <sub>DD_STOP</sub>   | Stop mode current<br>• at 3.0 V                                                                                                                                            |      |       |                   |      |       |

|                        | • at 25 °C                                                                                                                                                                 | -    | 257   | 277               | μA   |       |

|                        | • at 50 °C                                                                                                                                                                 | -    | 265   | 285               |      |       |

|                        | • at 70 °C                                                                                                                                                                 | -    | 278   | 303               |      |       |

|                        | • at 85 °C                                                                                                                                                                 | -    | 295   | 326               |      |       |

|                        | • at 105 °C                                                                                                                                                                | -    | 353   | 412               |      |       |

| I <sub>DD_VLPS</sub>   | Very-low-power stop mode current<br>• at 3.0 V                                                                                                                             |      |       |                   |      |       |

|                        | • at 25 °C                                                                                                                                                                 | -    | 2.25  | 5.76              | μΑ   |       |

|                        | • at 50 °C                                                                                                                                                                 | -    | 4.08  | 8.27              |      |       |

|                        | • at 70 °C                                                                                                                                                                 | -    | 8.10  | 14.52             |      |       |

|                        | • at 85 °C                                                                                                                                                                 | -    | 14.18 | 23.78             |      |       |

|                        | • at 105 °C                                                                                                                                                                | -    | 37.07 | 58.58             |      |       |

| I <sub>DD_LLS</sub>    | Low-leakage stop mode current<br>• at 3.0 V                                                                                                                                |      |       |                   |      |       |

#### Table 9. Power consumption operating behaviors (continued)

- 2. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

- 3. MCG configured for FEI mode.

- 4. Incremental current consumption from peripheral activity is not included.

- 5. MCG configured for BLPI mode.

- 6. No brownout

#### Table 10. Low power mode peripheral adders — typical value

| Symbol                     | Description                                                                                                                                                                                                                                                  |     | -   | Tempera | ature (°C | ;)  |     | Unit |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-----------|-----|-----|------|

|                            |                                                                                                                                                                                                                                                              |     | 25  | 50      | 70        | 85  | 105 |      |

| I <sub>IREFSTEN4MHz</sub>  | 4 MHz internal reference clock (IRC)<br>adder. Measured by entering STOP or<br>VLPS mode with 4 MHz IRC enabled.                                                                                                                                             | 56  | 56  | 56      | 56        | 56  | 56  | μA   |

| I <sub>IREFSTEN32KHz</sub> | 32 kHz internal reference clock (IRC)<br>adder. Measured by entering STOP<br>mode with the 32 kHz IRC enabled.                                                                                                                                               | 52  | 52  | 52      | 52        | 52  | 52  | μA   |

| I <sub>EREFSTEN4MHz</sub>  | External 4 MHz crystal clock adder.<br>Measured by entering STOP or VLPS<br>mode with the crystal enabled.                                                                                                                                                   | 206 | 228 | 237     | 245       | 251 | 258 | uA   |

| I <sub>EREFSTEN32KHz</sub> | External 32 kHz crystal clock adder by<br>means of the OSC0_CR[EREFSTEN<br>and EREFSTEN] bits. Measured by                                                                                                                                                   | 440 | 490 | 540     | 560       | 570 | 580 |      |

|                            | entering all modes with the crystal<br>enabled.                                                                                                                                                                                                              | 440 | 490 | 540     | 560       | 570 | 580 | nA   |

|                            | VLLS1                                                                                                                                                                                                                                                        | 490 | 490 | 540     | 560       | 570 | 680 |      |

|                            | • VLLS3                                                                                                                                                                                                                                                      | 510 | 560 | 560     | 560       | 610 | 680 |      |

|                            | <ul><li>LLS</li><li>VLPS</li><li>STOP</li></ul>                                                                                                                                                                                                              | 510 | 560 | 560     | 560       | 610 | 680 |      |

| I <sub>CMP</sub>           | CMP peripheral adder measured by<br>placing the device in VLLS1 mode with<br>CMP enabled using the 6-bit DAC and a<br>single external input for compare.<br>Includes 6-bit DAC power consumption.                                                            | 22  | 22  | 22      | 22        | 22  | 22  | μA   |

| I <sub>RTC</sub>           | RTC peripheral adder measured by<br>placing the device in VLLS1 mode with<br>external 32 kHz crystal enabled by<br>means of the RTC_CR[OSCE] bit and<br>the RTC ALARM set for 1 minute.<br>Includes ERCLK32K (32 kHz external<br>crystal) power consumption. | 432 | 357 | 388     | 475       | 532 | 810 | nA   |

| I <sub>UART</sub>          | UART peripheral adder measured by<br>placing the device in STOP or VLPS<br>mode with selected clock source waiting<br>for RX data at 115200 baud rate.                                                                                                       | 66  | 66  | 66      | 66        | 66  | 66  | μA   |

|                            | <ul> <li>Includes selected clock source power consumption.</li> <li>MCGIRCLK (4 MHz internal reference clock)</li> <li>OSCERCLK (4 MHz external crystal)</li> </ul>                                                                                          | 214 | 237 | 246     | 254       | 260 | 268 |      |

| Symbol           | Description                                                                                                                                                                                                                                                                                               |     | -   | Tempera | ature (°C | ;)  |     | Unit |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-----------|-----|-----|------|

|                  |                                                                                                                                                                                                                                                                                                           | -40 | 25  | 50      | 70        | 85  | 105 |      |

| I <sub>TPM</sub> | TPM peripheral adder measured by<br>placing the device in STOP or VLPS<br>mode with selected clock source<br>configured for output compare                                                                                                                                                                | 86  | 86  | 86      | 86        | 86  | 86  | μA   |

|                  | <ul> <li>generating 100 Hz clock signal. No load</li> <li>is placed on the I/O generating the</li> <li>clock signal. Includes selected clock</li> <li>source and I/O switching currents.</li> <li>MCGIRCLK (4 MHz internal<br/>reference clock)</li> <li>OSCERCLK (4 MHz external<br/>crystal)</li> </ul> | 235 | 256 | 265     | 274       | 280 | 287 |      |

| I <sub>BG</sub>  | Bandgap adder when BGEN bit is set<br>and device is placed in VLPx, LLS, or<br>VLLSx mode.                                                                                                                                                                                                                | 45  | 45  | 45      | 45        | 45  | 45  | μA   |

| I <sub>ADC</sub> | ADC peripheral adder combining the measured values at $V_{DD}$ and $V_{DDA}$ by placing the device in STOP or VLPS mode. ADC is configured for low power mode using the internal clock and continuous conversions.                                                                                        | 366 | 366 | 366     | 366       | 366 | 366 | μΑ   |

Table 10.

Low power mode peripheral adders — typical value (continued)

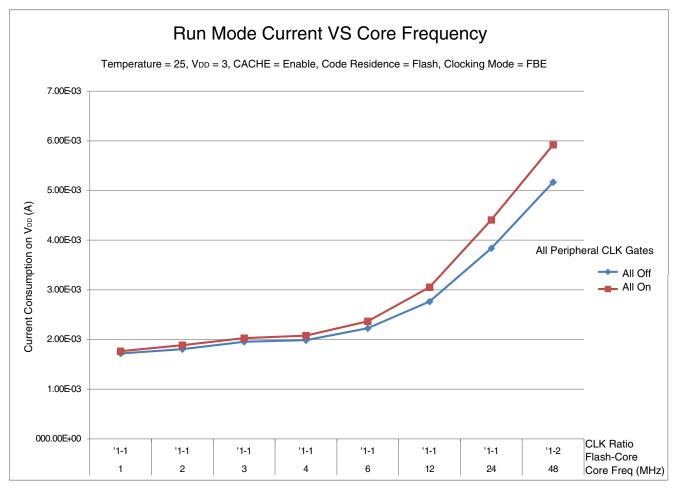

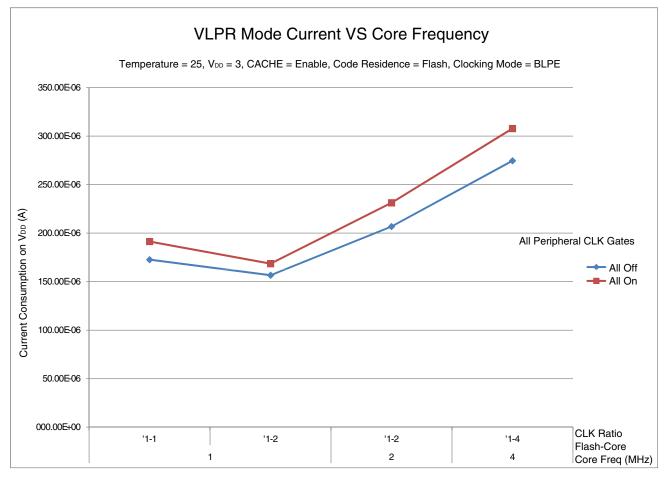

#### 2.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE for run mode, and BLPE for VLPR mode

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

Figure 2. Run mode supply current vs. core frequency

Figure 3. VLPR mode current vs. core frequency

#### 2.2.6 EMC performance

Electromagnetic compatibility (EMC) performance is highly dependent on the environment in which the MCU resides. Board design and layout, circuit topology choices, location and characteristics of external components as well as MCU software operation play a significant role in EMC performance. The system designer must consult the following Freescale applications notes, available on **freescale.com** for advice and guidance specifically targeted at optimizing EMC performance.

- AN2321: Designing for Board Level Electromagnetic Compatibility

- AN1050: Designing for Electromagnetic Compatibility (EMC) with HCMOS Microcontrollers

- AN1263: Designing for Electromagnetic Compatibility with Single-Chip Microcontrollers

### 2.3.2 General switching specifications

These general-purpose specifications apply to all signals configured for GPIO and UART signals.

Table 13. General switching specifications

| Description                                                                           | Min. | Max. | Unit                | Notes |

|---------------------------------------------------------------------------------------|------|------|---------------------|-------|

| GPIO pin interrupt pulse width (digital glitch filter disabled)<br>— Synchronous path | 1.5  | —    | Bus clock<br>cycles | 1     |

| External RESET and NMI pin interrupt pulse width — Asynchronous path                  | 100  |      | ns                  | 2     |

| GPIO pin interrupt pulse width — Asynchronous path                                    | 16   | _    | ns                  | 2     |

| Port rise and fall time                                                               | —    | 36   | ns                  | 3     |

1. The greater synchronous and asynchronous timing must be met.

2. This is the shortest pulse that is guaranteed to be recognized.

3. 75 pF load

## 2.4 Thermal specifications

#### 2.4.1 Thermal operating requirements

#### Table 14. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| TJ             | Die junction temperature | -40  | 125  | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   |

### 2.4.2 Thermal attributes

Table 15. Thermal attributes

| Board type        | Symbol           | Description                                                        | 48<br>LQFP | 32<br>LQFP | 32 QFN | 24 QFN | Unit | Notes |

|-------------------|------------------|--------------------------------------------------------------------|------------|------------|--------|--------|------|-------|

| Single-layer (1S) | R <sub>θJA</sub> | Thermal resistance, junction<br>to ambient (natural<br>convection) | 82         | 88         | 97     | 110    | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJA</sub> | Thermal resistance, junction<br>to ambient (natural<br>convection) | 58         | 59         | 34     | 42     | °C/W |       |

Peripheral operating requirements and behaviors

## 3.2 System modules

There are no specifications necessary for the device's system modules.

## 3.3 Clock modules

## 3.3.1 MCG specifications

| Symbol                  | Description                             |                                                                                                 | Min.                            | Тур.      | Max.    | Unit                  | Notes |

|-------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------|-----------|---------|-----------------------|-------|

| f <sub>ints_ft</sub>    |                                         | frequency (slow clock) —<br>nominal V <sub>DD</sub> and 25 °C                                   | _                               | 32.768    | —       | kHz                   |       |

| f <sub>ints_t</sub>     | Internal reference<br>user trimmed      | frequency (slow clock) —                                                                        | 31.25                           | _         | 39.0625 | kHz                   |       |

| $\Delta_{fdco\_res\_t}$ | frequency at fixed                      | ned average DCO output<br>voltage and temperature —<br>] and C4[SCFTRIM]                        | _                               | ± 0.3     | ± 0.6   | %f <sub>dco</sub>     | 1     |

| $\Delta f_{dco\_t}$     |                                         | trimmed average DCO output<br>Itage and temperature                                             |                                 | +0.5/-0.7 | ± 3     | %f <sub>dco</sub>     | 1, 2  |

| $\Delta f_{dco_t}$      |                                         | trimmed average DCO output<br>ed voltage and temperature                                        | _                               | ± 0.4     | ± 1.5   | %f <sub>dco</sub>     | 1, 2  |

| f <sub>intf_ft</sub>    |                                         | frequency (fast clock) —<br>nominal V <sub>DD</sub> and 25 °C                                   | _                               | 4         | —       | MHz                   |       |

| ∆f <sub>intf_ft</sub>   | (fast clock) over te                    | on of internal reference clock<br>emperature and voltage —<br>nominal V <sub>DD</sub> and 25 °C | —                               | +1/-2     | ± 3     | %f <sub>intf_ft</sub> | 2     |

| f <sub>intf_t</sub>     | Internal reference<br>trimmed at nomina | frequency (fast clock) — user<br>al V <sub>DD</sub> and 25 °C                                   | 3                               | _         | 5       | MHz                   |       |

| f <sub>loc_low</sub>    | Loss of external cl<br>RANGE = 00       | ock minimum frequency —                                                                         | (3/5) x<br>f <sub>ints_t</sub>  | _         | —       | kHz                   |       |

| f <sub>loc_high</sub>   | Loss of external cl                     | ock minimum frequency —                                                                         | (16/5) x<br>f <sub>ints_t</sub> | _         | —       | kHz                   |       |

|                         | •                                       | FI                                                                                              | L                               |           |         |                       |       |

| f <sub>fll_ref</sub>    | FLL reference free                      | luency range                                                                                    | 31.25                           | —         | 39.0625 | kHz                   |       |

| f <sub>dco</sub>        | DCO output                              | Low range (DRS = 00)                                                                            | 20                              | 20.97     | 25      | MHz                   | 3, 4  |

|                         | frequency range                         | $640 \times f_{fll\_ref}$                                                                       |                                 |           |         |                       |       |

|                         |                                         | Mid range (DRS = 01)                                                                            | 40                              | 41.94     | 48      | MHz                   |       |

|                         |                                         | 1280 × f <sub>fll_ref</sub>                                                                     |                                 |           |         |                       |       |

| f <sub>dco_t_DMX3</sub> | DCO output                              | Low range (DRS = 00)                                                                            | —                               | 23.99     | —       | MHz                   | 5, 6  |

| 2                       | frequency                               | $732 \times f_{fll\_ref}$                                                                       |                                 |           |         |                       |       |

|                         |                                         | Mid range (DRS = 01)                                                                            | _                               | 47.97     |         | MHz                   |       |

#### Table 17. MCG specifications

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

|                              | <ul><li> 24 MHz</li><li> 32 MHz</li></ul>                                                              |      |                 |      |      |       |

| C <sub>x</sub>               | EXTAL load capacitance                                                                                 | _    | _               |      |      | 2, 3  |

| Cy                           | XTAL load capacitance                                                                                  | _    | —               | —    |      | 2, 3  |

| R <sub>F</sub>               | Feedback resistor — low-frequency, low-power mode (HGO=0)                                              | _    | _               | —    | MΩ   | 2, 4  |

|                              | Feedback resistor — low-frequency, high-gain mode (HGO=1)                                              | —    | 10              | —    | MΩ   |       |

|                              | Feedback resistor — high-frequency, low-<br>power mode (HGO=0)                                         | _    | _               | -    | MΩ   |       |

|                              | Feedback resistor — high-frequency, high-gain mode (HGO=1)                                             | _    | 1               | -    | MΩ   |       |

| R <sub>S</sub>               | Series resistor — low-frequency, low-power mode (HGO=0)                                                | _    | —               | —    | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                                | _    | 200             | _    | kΩ   |       |

|                              | Series resistor — high-frequency, low-power mode (HGO=0)                                               | —    | _               | _    | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | —    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | -    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | -    | V    |       |

Table 18. Oscillator DC electrical specifications (continued)

1. V<sub>DD</sub>=3.3 V, Temperature =25 °C

2. See crystal or resonator manufacturer's recommendation

3.  $C_x, C_y$  can be provided by using the integrated capacitors when the low frequency oscillator (RANGE = 00) is used. For all other cases external capacitors must be used.

- 4. When low power mode is selected, R<sub>F</sub> is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other devices.

#### Peripheral operating requirements and behaviors

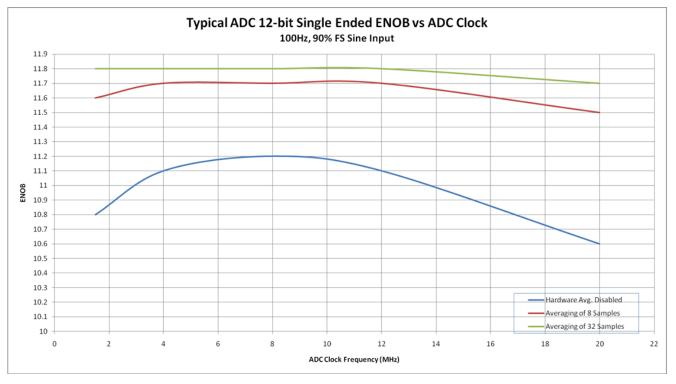

- The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{\text{REFH}} V_{\text{REFL}})/2^{N}$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. ADC conversion clock < 3 MHz

Figure 7. Typical ENOB vs. ADC\_CLK for 12-bit single-ended mode

#### 3.6.2 CMP and 6-bit DAC electrical specifications Table 26. Comparator and 6-bit DAC electrical specifications

| Symbol            | Description                                         | Min.            | Тур. | Max.            | Unit |

|-------------------|-----------------------------------------------------|-----------------|------|-----------------|------|

| V <sub>DD</sub>   | Supply voltage                                      | 1.71            | —    | 3.6             | V    |

| I <sub>DDHS</sub> | Supply current, high-speed mode (EN = 1, PMODE = 1) | —               | _    | 200             | μA   |

| I <sub>DDLS</sub> | Supply current, low-speed mode (EN = 1, PMODE = 0)  | —               | _    | 20              | μA   |

| V <sub>AIN</sub>  | Analog input voltage                                | V <sub>SS</sub> | —    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>  | Analog input offset voltage                         | _               | _    | 20              | mV   |

| V <sub>H</sub>    | Analog comparator hysteresis <sup>1</sup>           |                 |      |                 |      |

|                   | • CR0[HYSTCTR] = 00                                 | _               | 5    | _               | mV   |

|                   | <ul> <li>CR0[HYSTCTR] = 01</li> </ul>               | _               | 10   | _               | mV   |

| Symbol             | Description                                               | Min.                  | Тур. | Max. | Unit             |

|--------------------|-----------------------------------------------------------|-----------------------|------|------|------------------|

|                    | CR0[HYSTCTR] = 10                                         |                       | 20   |      | mV               |

|                    | <ul> <li>CR0[HYSTCTR] = 11</li> </ul>                     | —                     | 30   | —    | mV               |

| V <sub>CMPOh</sub> | Output high                                               | V <sub>DD</sub> – 0.5 | _    |      | V                |

| V <sub>CMPOI</sub> | Output low                                                | _                     | _    | 0.5  | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN = 1,<br>PMODE = 1) | 20                    | 50   | 200  | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN = 1, PMODE = 0)     | 80                    | 250  | 600  | ns               |

|                    | Analog comparator initialization delay <sup>2</sup>       | _                     | _    | 40   | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                         | _                     | 7    | —    | μA               |

| INL                | 6-bit DAC integral non-linearity                          | -0.5                  | —    | 0.5  | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                      | -0.3                  | —    | 0.3  | LSB              |

Table 26. Comparator and 6-bit DAC electrical specifications (continued)

1. Typical hysteresis is measured with input voltage range limited to 0.7 to  $V_{DD} - 0.7 V$ .

2. Comparator initialization delay is defined as the time between software writes to change control inputs (writes to

DACEN, VRSEL, PSEL, MSEL, VOSEL) and the comparator output settling to a stable level.

3. 1 LSB =  $V_{reference}/64$

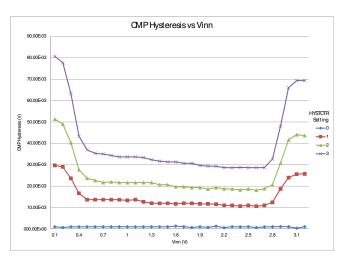

Figure 8. Typical hysteresis vs. Vin level ( $V_{DD}$  = 3.3 V, PMODE = 0)

Peripheral operating requirements and behaviors

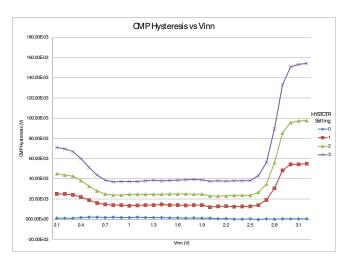

Figure 9. Typical hysteresis vs. Vin level ( $V_{DD}$  = 3.3 V, PMODE = 1)

## 3.7 Timers

See General switching specifications.

## 3.8 Communication interfaces

### 3.8.1 SPI switching specifications

The Serial Peripheral Interface (SPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The following tables provide timing characteristics for classic SPI timing modes. See the SPI chapter of the chip's Reference Manual for information about the modified transfer formats used for communicating with slower peripheral devices.

All timing is shown with respect to 20%  $V_{DD}$  and 80%  $V_{DD}$  thresholds, unless noted, as well as input signal transitions of 3 ns and a 30 pF maximum load on all SPI pins.

| Num. | Symbol             | Description            | Min.                      | Max.                          | Unit               | Note |

|------|--------------------|------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>    | Frequency of operation | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub> | SPSCK period           | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>  | Enable lead time       | 1/2                       |                               | t <sub>SPSCK</sub> |      |

| 4    | t <sub>Lag</sub>   | Enable lag time        | 1/2                       |                               | t <sub>SPSCK</sub> | —    |

Table 27. SPI master mode timing on slew rate disabled pads

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|------|------|

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> – 30 | 1024 x                   | ns   | —    |

|      |                     |                                |                          | t <sub>periph</sub>      |      |      |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 16                       | _                        | ns   | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                        | _                        | ns   | —    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 10                       | ns   | —    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | —                        | ns   | —    |

| 10   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> – 25 | ns   | —    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |      |      |

| 11   | t <sub>RO</sub>     | Rise time output               | —                        | 25                       | ns   | —    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |      |      |

Table 27. SPI master mode timing on slew rate disabled pads (continued)

1. For SPI0,  $f_{periph}$  is the bus clock ( $f_{BUS}$ ).

2.  $t_{periph} = 1/f_{periph}$

Table 28. SPI master mode timing on slew rate enabled pads

| Num. | Symbol              | Description                    | Min.                      | Max.                          | Unit               | Note |

|------|---------------------|--------------------------------|---------------------------|-------------------------------|--------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | f <sub>periph</sub> /2048 | f <sub>periph</sub> /2        | Hz                 | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 2 x t <sub>periph</sub>   | 2048 x<br>t <sub>periph</sub> | ns                 | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1/2                       | —                             | t <sub>SPSCK</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1/2                       | —                             | t <sub>SPSCK</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> – 30  | 1024 x<br>t <sub>periph</sub> | ns                 | _    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 96                        | —                             | ns                 | _    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 0                         | —                             | ns                 | —    |

| 8    | t <sub>v</sub>      | Data valid (after SPSCK edge)  |                           | 52                            | ns                 | _    |

| 9    | t <sub>HO</sub>     | Data hold time (outputs)       | 0                         | —                             | ns                 | _    |

| 10   | t <sub>RI</sub>     | Rise time input                | _                         | t <sub>periph</sub> – 25      | ns                 | —    |

|      | t <sub>FI</sub>     | Fall time input                |                           |                               |                    |      |

| 11   | t <sub>RO</sub>     | Rise time output               | —                         | 36                            | ns                 | _    |

|      | t <sub>FO</sub>     | Fall time output               |                           |                               |                    |      |

1. For SPI0,  $f_{periph}$  is the bus clock ( $f_{BUS}$ ).

2.  $t_{periph} = 1/f_{periph}$

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | _                        | t <sub>periph</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> – 30 | _                        | ns                  | —    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2                        | _                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 7                        | _                        | ns                  | —    |

| 8    | ta                  | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | -                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 22                       | ns                  | —    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> – 25 | ns                  | —    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 25                       | ns                  | —    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

Table 29. SPI slave mode timing on slew rate disabled pads (continued)

For SPI0, f<sub>periph</sub> is the bus clock (f<sub>BUS</sub>).

t<sub>periph</sub> = 1/f<sub>periph</sub>

Time to data active from high-impedance state

4. Hold time to high-impedance state

#### Table 30. SPI slave mode timing on slew rate enabled pads

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  |                          | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | _                        | t <sub>periph</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | _                        | t <sub>periph</sub> | _    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> – 30 | —                        | ns                  | —    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2                        | _                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 7                        | —                        | ns                  | _    |

| 8    | t <sub>a</sub>      | Slave access time              | _                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | _                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | _                        | 122                      | ns                  | _    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | —                        | ns                  | _    |

| 12   | t <sub>RI</sub>     | Rise time input                | _                        | t <sub>periph</sub> – 25 | ns                  | _    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               |                          | 36                       | ns                  | _    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

1. For SPI0,  $f_{periph}$  is the bus clock ( $f_{BUS}$ ).

- 2.  $t_{periph} = 1/f_{periph}$ 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

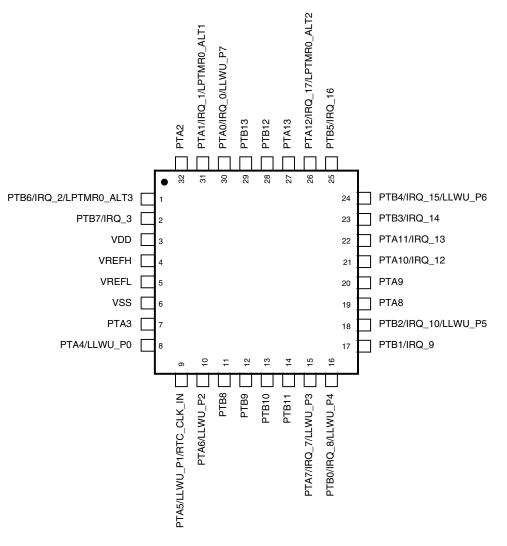

Figure 16. KL04 32-pin LQFP pinout diagram

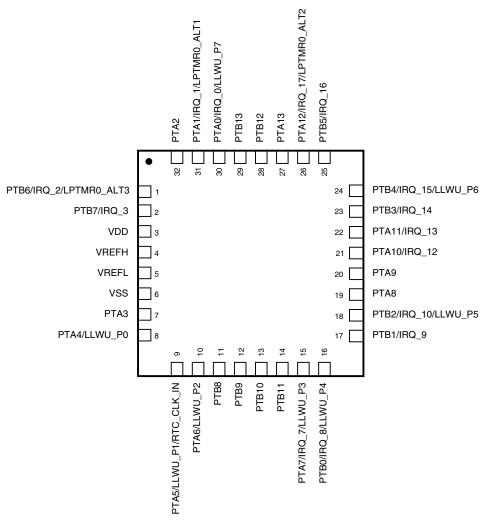

Figure 17. KL04 32-pin QFN pinout diagram

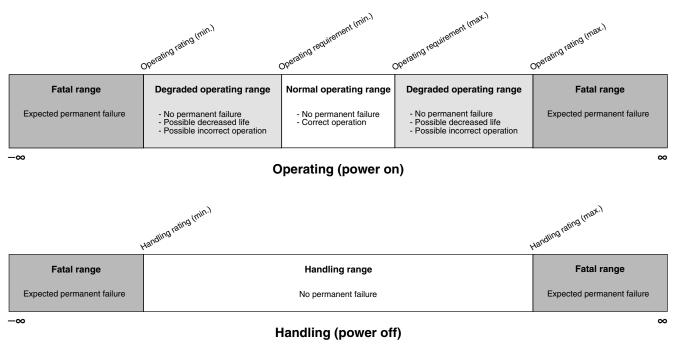

# 8.6 Relationship between ratings and operating requirements

# 8.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 8.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

#### 8.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

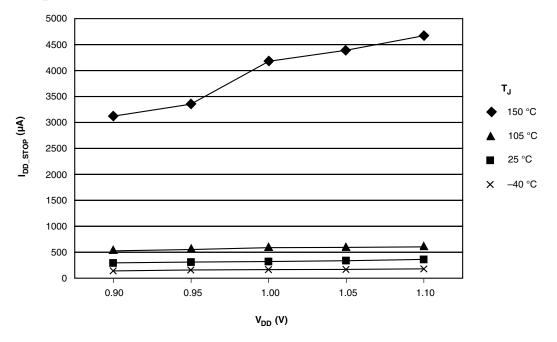

#### 8.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

## 8.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. Freescale reserves the right to make changes without further notice to any products herein.

Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, Energy Efficient Solutions logo, and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM and Cortex-M0+ are the registered trademarks of ARM Limited.

© 2012-2014 Freescale Semiconductor, Inc.

Document Number KL04P48M48SF1 Revision 4 03/2014