Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | C1665V2                                                                            |

| Core Size                  | 16/32-Bit                                                                          |

| Speed                      | 100MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                               |

| Number of I/O              | 150                                                                                |

| Program Memory Size        | 1.6MB (1.6M x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 138K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 30x10b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 176-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-176-12                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2298h200f100labkxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

## 16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC229[89]H (XC2000 Family)

# 1 Summary of Features

For a quick overview and easy reference, the features of the XC229[89]H are summarized here.

- · High-performance CPU with five-stage pipeline and MPU

- 10 ns instruction cycle @ 100 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Mbytes total linear address space for code and data

- 1,024 Bytes on-chip special function register area (C166 Family compatible)

Integrated Memory Protection Unit (MPU)

- Interrupt system with 16 priority levels providing 112 interrupt nodes

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 10 ns

- Eight-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- 24 Kbytes on-chip data SRAM (DSRAM)

- Up to 112 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 1,600 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

## XC2298H, XC2299H XC2000 Family / High Line

#### **General Device Information**

| Table | Table 6         Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |  |

|-------|--------------------------------------------------------|------------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.      | Туре | Function                                       |  |  |  |

| 100   | P12.6                                                  | O0 / I     | St/B | Bit 6 of Port 12, General Purpose Input/Output |  |  |  |

|       | CC1_CC6                                                | O1 / I     | St/B | CAPCOM1 CC6IO Capture Inp./ Compare Out.       |  |  |  |

|       | U4C0_MCLK<br>OUT                                       | O2         | St/B | USIC4 Channel 0 Master Clock Output            |  |  |  |

|       | U3C1_SELO<br>2                                         | O3         | St/B | USIC3 Channel 1 Select/Control 2 Output        |  |  |  |

|       | RxDC3F                                                 | I          | St/B | CAN Node 3 Receive Data Input                  |  |  |  |

|       | CCU63_CCP<br>OS1B                                      | I          | St/B | CCU63 Position Input 1                         |  |  |  |

| 101   | P0.2                                                   | O0 / I     | St/B | Bit 2 of Port 0, General Purpose Input/Output  |  |  |  |

|       | U1C0_SCLK<br>OUT                                       | O1         | St/B | USIC1 Channel 0 Shift Clock Output             |  |  |  |

|       | TxDC0                                                  | 02         | St/B | CAN Node 0 Transmit Data Output                |  |  |  |

|       | CCU61_CC6<br>2                                         | O3         | St/B | CCU61 Channel 2 Output                         |  |  |  |

|       | A2                                                     | ОН         | St/B | External Bus Interface Address Line 2          |  |  |  |

|       | U1C0_DX1B                                              | Ι          | St/B | USIC1 Channel 0 Shift Clock Input              |  |  |  |

|       | CCU61_CC6<br>2INA                                      | I          | St/B | CCU61 Channel 2 Input                          |  |  |  |

| 102   | P10.0                                                  | O0 / I     | St/B | Bit 0 of Port 10, General Purpose Input/Output |  |  |  |

|       | U0C1_DOUT                                              | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |

|       | CCU60_CC6<br>0                                         | O2         | St/B | CCU60 Channel 0 Output                         |  |  |  |

|       | AD0                                                    | OH /<br>IH | St/B | External Bus Interface Address/Data Line 0     |  |  |  |

|       | CCU60_CC6<br>0INA                                      | 1          | St/B | CCU60 Channel 0 Input                          |  |  |  |

|       | ESR1_2                                                 | Ι          | St/B | ESR1 Trigger Input 2                           |  |  |  |

|       | U0C0_DX0A                                              | Ι          | St/B | USIC0 Channel 0 Shift Data Input               |  |  |  |

|       | U0C1_DX0A                                              | Ι          | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |

## XC2298H, XC2299H XC2000 Family / High Line

## **General Device Information**

| Table | Table 6Pin Definitions and Functions (cont'd) |            |      |                                                |  |  |  |

|-------|-----------------------------------------------|------------|------|------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.      | Туре | Function                                       |  |  |  |

| 115   | P2.10                                         | O0 / I     | St/B | Bit 10 of Port 2, General Purpose Input/Output |  |  |  |

|       | U0C1_DOUT                                     | 01         | St/B | USIC0 Channel 1 Shift Data Output              |  |  |  |

|       | U0C0_SELO<br>3                                | O2         | St/B | USIC0 Channel 0 Select/Control 3 Output        |  |  |  |

|       | CC2_CC23                                      | O3 / I     | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |  |  |  |

|       | A23                                           | ОН         | St/B | External Bus Interface Address Line 23         |  |  |  |

|       | U0C1_DX0E                                     | I          | St/B | USIC0 Channel 1 Shift Data Input               |  |  |  |

|       | CAPINA                                        | I          | St/B | GPT12E Register CAPREL Capture Input           |  |  |  |

|       | U3C1_DX0A                                     | I          | St/B | USIC3 Channel 1 Shift Data Input               |  |  |  |

| 116   | P10.3                                         | O0 / I     | St/B | Bit 3 of Port 10, General Purpose Input/Output |  |  |  |

|       | CCU60_COU<br>T60                              | O2         | St/B | CCU60 Channel 0 Output                         |  |  |  |

|       | AD3                                           | OH /<br>IH | St/B | External Bus Interface Address/Data Line 3     |  |  |  |

|       | U0C0_DX2A                                     | I          | St/B | USIC0 Channel 0 Shift Control Input            |  |  |  |

|       | U0C1_DX2A                                     | I          | St/B | USIC0 Channel 1 Shift Control Input            |  |  |  |

|       | U3C0_DX0A                                     | I          | St/B | USIC3 Channel 0 Shift Data Input               |  |  |  |

| 117   | P0.5                                          | O0 / I     | St/B | Bit 5 of Port 0, General Purpose Input/Output  |  |  |  |

|       | U1C1_SCLK<br>OUT                              | 01         | St/B | USIC1 Channel 1 Shift Clock Output             |  |  |  |

|       | U1C0_SELO<br>2                                | 02         | St/B | USIC1 Channel 0 Select/Control 2 Output        |  |  |  |

|       | CCU61_COU<br>T62                              | O3         | St/B | CCU61 Channel 2 Output                         |  |  |  |

|       | A5                                            | ОН         | St/B | External Bus Interface Address Line 5          |  |  |  |

|       | U1C1_DX1A                                     | I          | St/B | USIC1 Channel 1 Shift Clock Input              |  |  |  |

|       | U1C0_DX1C                                     | I          | St/B | USIC1 Channel 0 Shift Clock Input              |  |  |  |

|       | RXDC3E                                        | I          | St/B | CAN Node 3 Receive Data Input                  |  |  |  |

| 118   | P12.2                                         | O0 / I     | St/B | Bit 2 of Port 12, General Purpose Input/Output |  |  |  |

|       | CC1_CC2                                       | O1 / I     | St/B | CAPCOM1 CC2IO Capture Inp./ Compare Out.       |  |  |  |

|       | U4C0_DX1B                                     | I          | St/B | USIC4 Channel 0 Shift Clock Input              |  |  |  |

#### **General Device Information**

## 2.2 Identification Registers

The identification registers describe the current version of the XC229[89]H and of its modules.

| Table 7 X | C229[89]H | Identification | Registers |

|-----------|-----------|----------------|-----------|

|-----------|-----------|----------------|-----------|

| Short Name  | Value                  | Address              | Notes                      |

|-------------|------------------------|----------------------|----------------------------|

| SCU_IDMANUF | 1820 <sub>H</sub>      | 00'F07E <sub>H</sub> |                            |

| SCU_IDCHIP  | 4001 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking EES-AA or ES-AA    |

|             | 4002 <sub>H</sub>      | 00'F07C <sub>H</sub> | marking ES+AA, ES-AB or AB |

| SCU_IDMEM   | 318F <sub>H</sub>      | 00'F07A <sub>H</sub> |                            |

| SCU_IDPROG  | 1313 <sub>H</sub>      | 00'F078 <sub>H</sub> |                            |

| JTAG_ID     | 0018'A083 <sub>H</sub> |                      | marking EES-AA or ES-AA    |

|             | 1018'A083 <sub>H</sub> |                      | marking ES+AA              |

|             | 2018'A083 <sub>H</sub> |                      | marking ES-AB or AB        |

# 3 Functional Description

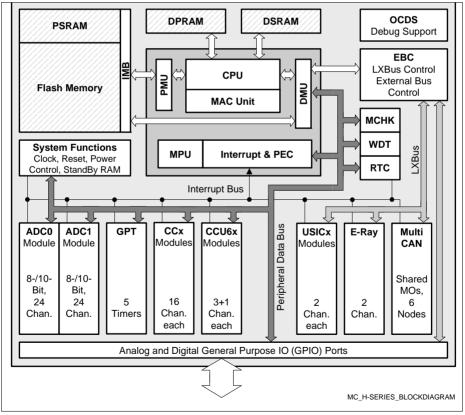

The architecture of the XC229[89]H combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources. This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC229[89]H.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC229[89]H.

Figure 4 Block Diagram

## 3.4 Memory Protection Unit (MPU)

The XC229[89]H's Memory Protection Unit (MPU) protects user-specified memory areas from unauthorized read, write, or instruction fetch accesses. The MPU can protect the whole address space including the peripheral area. This completes established mechanisms such as the register security mechanism or stack overrun/underrun detection.

Four Protection Levels support flexible system programming where operating system, low level drivers, and applications run on separate levels. Each protection level permits different access restrictions for instructions and/or data.

Every access is checked (if the MPU is enabled) and an access violating the permission rules will be marked as invalid and leads to a protection trap.

A set of protection registers for each protection level specifies the address ranges and the access permissions. Applications requiring more than 4 protection levels can dynamically re-program the protection registers.

## 3.5 Memory Checker Module (MCHK)

The XC229[89]H's Memory Checker Module calculates a checksum (fractional polynomial division) on a block of data, often called Cyclic Redundancy Code (CRC). It is based on a 32-bit linear feedback shift register and may, therefore, also be used to generate pseudo-random numbers.

The Memory Checker Module is a 16-bit parallel input signature compression circuitry which enables error detection within a block of data stored in memory, registers, or communicated e.g. via serial communication lines. It reduces the probability of error masking due to repeated error patterns by calculating the signature of blocks of data.

The polynomial used for operation is configurable, so most of the commonly used polynomials may be used. Also, the block size for generating a CRC result is configurable via a local counter. An interrupt may be generated if testing the current data block reveals an error.

An autonomous CRC compare circuitry is included to enable redundant error detection, e.g. to enable higher safety integrity levels.

The Memory Checker Module provides enhanced fault detection (beyond parity or ECC) for data and instructions in volatile and non volatile memories. This is especially important for the safety and reliability of embedded systems.

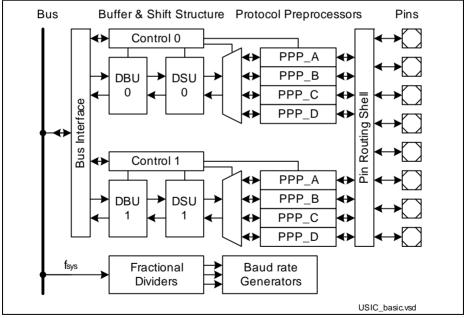

## 3.13 Universal Serial Interface Channel Modules (USIC)

The XC229[89]H features the USIC modules USIC0, USIC1, USIC2, USIC3, USIC4. Each module provides two serial communication channels.

The Universal Serial Interface Channel (USIC) module is based on a generic data shift and data storage structure which is identical for all supported serial communication protocols. Each channel supports complete full-duplex operation with a basic data buffer structure (one transmit buffer and two receive buffer stages). In addition, the data handling software can use FIFOs.

The protocol part (generation of shift clock/data/control signals) is independent of the general part and is handled by protocol-specific preprocessors (PPPs).

The USIC's input/output lines are connected to pins by a pin routing unit. The inputs and outputs of each USIC channel can be assigned to different interface pins, providing great flexibility to the application software. All assignments can be made during runtime.

### Figure 11 General Structure of a USIC Module

The regular structure of the USIC module brings the following advantages:

- Higher flexibility through configuration with same look-and-feel for data management

- Reduced complexity for low-level drivers serving different protocols

- Wide range of protocols with improved performances (baud rate, buffer handling)

## 3.16 System Timer

The System Timer consists of a programmable prescaler and two concatenated timers (10 bits and 6 bits). Both timers can generate interrupt requests. The clock source can be selected and the timers can also run during power reduction modes.

Therefore, the System Timer enables the software to maintain the current time for scheduling functions or for the implementation of a clock.

## 3.17 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz).

Time intervals between 2.56  $\mu$ s and 10.71 s can be monitored (@ 100 MHz).

The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

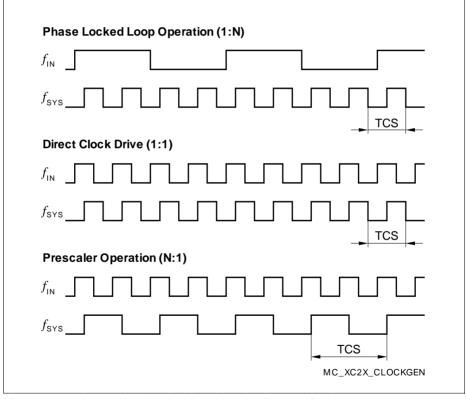

## 3.18 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XC229[89]H from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.7.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

## 4.3.3 Power Consumption

The power consumed by the XC229[89]H depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current I<sub>LK</sub> depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Standby mode:

Voltage domain DMP\_1 switched off completely, power supply control switched off. DMP\_M domain is supplied by ultra low power electronic voltage regulator (ULPEVR). The alternate regulator EVR\_M is switched off.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{DDIM}$  and  $V_{DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

#### Table 18Switching Power Consumption

| Parameter                                                                                  | Symbol                     | Values |                           |                              | Unit | Note /                                                              |

|--------------------------------------------------------------------------------------------|----------------------------|--------|---------------------------|------------------------------|------|---------------------------------------------------------------------|

|                                                                                            |                            | Min.   | Тур.                      | Max.                         |      | Test Condition                                                      |

| Power supply current<br>(active) with all peripherals<br>active and EVVRs on <sup>1)</sup> | I <sub>SACT_FR</sub><br>CC | _      | $40 + 0.9 x f_{SYS}^{2)}$ | 40 + 1.4 x<br>$f_{SYS}^{2)}$ | mA   | power_mode=<br>active ;<br>voltage_range=<br>both <sup>3)4)5)</sup> |

| Power supply current in standby mode                                                       | I <sub>SSB</sub> CC        | -      | 95                        | 200                          | μΑ   | power_mode=<br>standby ;<br>voltage_range=<br>lower <sup>6)</sup>   |

|                                                                                            |                            | -      | 120                       | 330                          | μΑ   | power_mode=<br>standby ;<br>voltage_range=<br>upper <sup>6)</sup>   |

| Power supply current in stopover mode, EVVRs on                                            | I <sub>SSO</sub> CC        | -      | 1.4                       | 4.0                          | mA   | power_mode=<br>stopover ;<br>voltage_range=<br>both <sup>4)</sup>   |

If the FlexRay module clock (running @ 80 MHz) is turned off (KSCFG.MODEN=0) the value is reduced by 15 mA.

2)  $f_{SYS}$  in MHz

- 3) The pad supply voltage pins (V<sub>DDPB</sub>) provide the input current for the on-chip EVVRs and the current consumed by the pin output drivers. A small current is consumed because the drivers input stages are switched. In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to 3 + 0.6 x f<sub>SYS</sub>.

- 4) Please consider the additional conditions described in section "Active Mode Power Supply Current".

- 5) The pad supply voltage has only a minor influence on this parameter.

- 6) These values are valid if the voltage validation circuits for V<sub>DDPB</sub> (SWD) and V<sub>DDIM</sub> (PVC\_M) are off. Leaving SWD and PVC\_M active adds another 90 μA.

#### **Active Mode Power Supply Current**

The actual power supply current in active mode not only depends on the system frequency but also on the configuration of the XC229[89]H's subsystem.

Besides the power consumed by the device logic the power supply pins also provide the current that flows through the pin output drivers.

A small current is consumed because the drivers' input stages are switched.

The IO power domains can be supplied separately. Power domain A ( $V_{\rm DDPA}$ ) supplies the A/D converters and Port 6. Power domain B ( $V_{\rm DDPB}$ ) supplies the on-chip EVVRs and all other ports.

| Parameter                                                 | Symbol                  | Values |      |       | Unit | Note /                         |

|-----------------------------------------------------------|-------------------------|--------|------|-------|------|--------------------------------|

|                                                           |                         | Min.   | Тур. | Max.  |      | Test Condition                 |

| Leakage supply current (DMP_1 off) <sup>1)2)</sup>        | $I_{\rm LK0}  {\rm CC}$ | -      | 20   | 35    | μA   | <i>T</i> <sub>J</sub> = 25 °C  |

|                                                           |                         | -      | 115  | 330   | μA   | <i>T</i> <sub>J</sub> = 85 °C  |

|                                                           |                         | -      | 270  | 880   | μA   | <i>T</i> <sub>J</sub> = 125 °C |

|                                                           |                         | -      | 420  | 1.445 | μA   | <i>T</i> <sub>J</sub> = 150 °C |

| Leakage supply current<br>(DMP_1 powered) <sup>1)2)</sup> | I <sub>LK1</sub> CC     | -      | 0.04 | 0.06  | mA   | <i>T</i> <sub>J</sub> = 25 °C  |

|                                                           |                         | -      | 0.7  | 1.8   | mA   | <i>T</i> <sub>J</sub> = 85 °C  |

|                                                           |                         | -      | 3.1  | 8.6   | mA   | <i>T</i> <sub>J</sub> = 125 °C |

|                                                           |                         | -      | 6.6  | 19.2  | mA   | <i>T</i> <sub>J</sub> = 150 °C |

#### Table 19 Leakage Power Consumption

The supply current caused by leakage depends mainly on the junction temperature and the supply voltage. The temperature difference between the junction temperature T<sub>J</sub> and the ambient temperature T<sub>A</sub> must be taken into account. As this fraction of the supply current does not depend on device activity, it must be added to other power consumption values.

All inputs (including pins configured as inputs) are set at 0 V to 0.1 V or at V<sub>DDP</sub> - 0.1 V to V<sub>DDP</sub> and all outputs (including pins configured as outputs) are disconnected.

Note: A fraction of the leakage current flows through domain DMP\_A (pin  $V_{DDPA}$ ). This current can be calculated as 7,000 ×  $e^{-\alpha}$ , with  $\alpha = 5000 / (273 + 1.3 \times T_J)$ . For  $T_J = 150^{\circ}$ C, this results in a current of 160  $\mu$ A.

The leakage power consumption can be calculated according to the following formulas:  $I_{I K0} = 500,000 \times e^{-\alpha}$  with  $\alpha = 3000 / (273 + B \times T_J)$

Parameter B must be replaced by

- 1.0 for typical values

- 1.6 for maximum values

$I_{LK1} = 600,000 \times e^{-\alpha}$  with  $\alpha = 5000 / (273 + B \times T_{J})$

Parameter B must be replaced by

- 1.1 for typical values

- 1.4 for maximum values

## XC2298H, XC2299H XC2000 Family / High Line

### **Electrical Parameters**

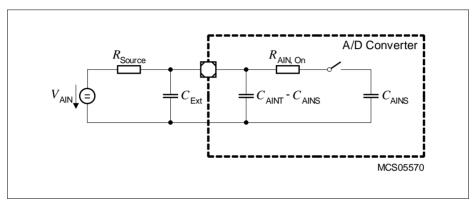

- 4) TUE is tested at V<sub>AREF</sub> = V<sub>DDPA</sub> = 5.0 V, V<sub>AGND</sub> = 0 V. It is verified by design for all other voltages within the defined voltage range. The specified TUE is valid only if the absolute sum of input overload currents on analog port pins (see I<sub>OV</sub> specification) does not exceed 10 mA, and if V<sub>AREF</sub> and V<sub>AGND</sub> remain stable during the measurement time.

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

Figure 17 Equivalent Circuitry for Analog Inputs

Sample time and conversion time of the XC229[89]H's A/D converters are programmable. The timing above can be calculated using Table 21.

The limit values for  $f_{\rm ADCI}$  must not be exceeded when selecting the prescaler value.

| GLOBCTR.5-0<br>(DIVA) | A/D Converter<br>Analog Clock $f_{\text{ADCI}}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup><br>t <sub>s</sub> |

|-----------------------|-------------------------------------------------|---------------------|---------------------------------------------|

| 000000 <sub>B</sub>   | f <sub>SYS</sub>                                | 00 <sub>H</sub>     | $t_{ADCI} \times 2$                         |

| 000001 <sub>B</sub>   | f <sub>SYS</sub> / 2                            | 01 <sub>H</sub>     | $t_{ADCI} \times 3$                         |

| 000010 <sub>B</sub>   | f <sub>SYS</sub> / 3                            | 02 <sub>H</sub>     | $t_{ADCI} \times 4$                         |

| :                     | $f_{\rm SYS}$ / (DIVA+1)                        | :                   | $t_{ADCI} \times (STC+2)$                   |

| 111110 <sub>B</sub>   | f <sub>SYS</sub> / 63                           | FE <sub>H</sub>     | $t_{ADCI} \times 256$                       |

| 111111 <sub>B</sub>   | f <sub>SYS</sub> / 64                           | FF <sub>H</sub>     | $t_{ADCI} 	imes 257$                        |

Table 21

A/D Converter Computation Table

1) The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

#### **Converter Timing Example A:**

| Assumptions:                | $f_{\rm SYS}$           | = 100 MHz (i.e. $t_{SYS}$ = 10 ns), DIVA = 03 <sub>H</sub> , STC = 00 <sub>H</sub>            |  |  |  |  |

|-----------------------------|-------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| Analog clock                | $f_{\rm ADCI}$          | $= f_{SYS} / 4 = 25 \text{ MHz}$ , i.e. $t_{ADCI} = 40 \text{ ns}$                            |  |  |  |  |

| Sample time                 | t <sub>S</sub>          | $= t_{ADCI} \times 2 = 80 \text{ ns}$                                                         |  |  |  |  |

| Conversion 10-              | bit:                    |                                                                                               |  |  |  |  |

|                             | <i>t</i> <sub>C10</sub> | = $13 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 13 × 40 ns + 2 × 10ns = 0.540 µs                     |  |  |  |  |

| Conversion 8-b              | it:                     |                                                                                               |  |  |  |  |

|                             | t <sub>C8</sub>         | = $11 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $11 \times 40$ ns + $2 \times 10$ ns = 0.460 µs |  |  |  |  |

| Converter Timing Example B: |                         |                                                                                               |  |  |  |  |

| Assumptions:          | $f_{\rm SYS}$           | = 40 MHz (i.e. <i>t</i> <sub>SYS</sub> = 25 ns), DIVA = 02 <sub>H</sub> , STC = 03 <sub>H</sub>                    |

|-----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------|

| Analog clock          | $f_{\rm ADCI}$          | $= f_{SYS} / 3 = 13.3 \text{ MHz}$ , i.e. $t_{ADCI} = 75 \text{ ns}$                                               |

| Sample time           | t <sub>S</sub>          | $= t_{ADCI} \times 5 = 375 \text{ ns}$                                                                             |

| <b>Conversion 10-</b> | bit:                    |                                                                                                                    |

|                       | <i>t</i> <sub>C10</sub> | = $16 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $16 \times 75$ ns + $2 \times 25$ ns = $1.25 \ \mu s$                |

| <b>Conversion 8-b</b> | it:                     |                                                                                                                    |

|                       | t <sub>C8</sub>         | = $14 \times t_{ADCI} + 2 \times t_{SYS} = 14 \times 75 \text{ ns} + 2 \times 25 \text{ ns} = 1.10 \ \mu \text{s}$ |

|                       |                         |                                                                                                                    |

|                       |                         |                                                                                                                    |

## 4.7.2 Definition of Internal Timing

The internal operation of the XC229[89]H is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XC229[89]H.

Figure 20 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 20** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

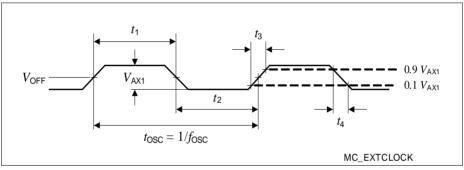

- 1) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

- 2) Overload conditions must not occur on pin XTAL1.

- Note: For crystal or ceramic resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

The manufacturers of crystals and ceramic resonators offer an oscillator evaluation service. This evaluation checks the crystal/resonator specification limits to ensure a reliable oscillator operation.

Figure 22 External Clock Drive XTAL1

## 4.7.5 External Bus Timing

The following parameters specify the behavior of the XC229[89]H bus interface.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

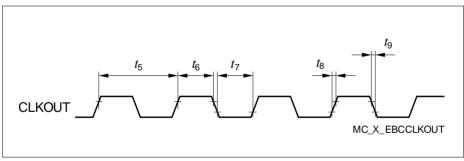

#### Table 31 Parameters

| Parameter                       | Symbol            | Values |                 |      | Unit | Note /         |

|---------------------------------|-------------------|--------|-----------------|------|------|----------------|

|                                 |                   | Min.   | Тур.            | Max. |      | Test Condition |

| CLKOUT Cycle Time <sup>1)</sup> | t <sub>5</sub> CC | -      | $1/f_{\rm SYS}$ | -    | ns   |                |

| CLKOUT high time                | t <sub>6</sub> CC | 2      | -               | -    |      |                |

| CLKOUT low time                 | t <sub>7</sub> CC | 2      | -               | -    |      |                |

| CLKOUT rise time                | t <sub>8</sub> CC | -      | -               | 3    | ns   |                |

| CLKOUT fall time                | t <sub>9</sub> CC | -      | -               | 3    |      |                |

1) The CLKOUT cycle time is influenced by PLL jitter. For longer periods the relative deviation decreases (see PLL deviation formula).

### Figure 23 CLKOUT Signal Timing

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

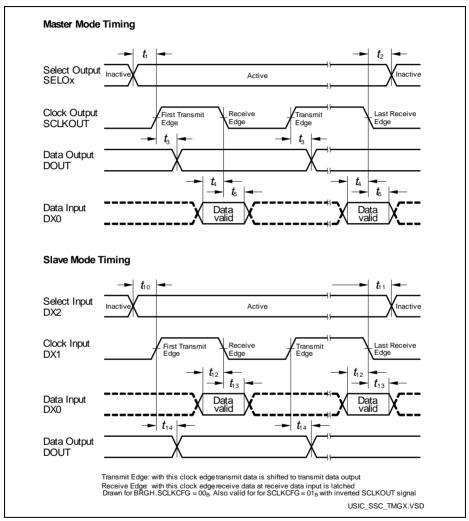

Figure 27 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.

|                                                                          |                           | •      |      | 0    | •    | ,              |

|--------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

| Parameter                                                                | Symbol                    | Values |      |      | Unit | Note /         |

|                                                                          |                           | Min.   | Тур. | Max. |      | Test Condition |

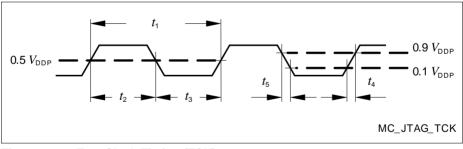

| TCK low time                                                             | t <sub>3</sub> SR         | 16     | -    | -    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR         | -      | _    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -      | _    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6      | -    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6      | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>2)</sup>        | t <sub>8</sub> CC         | -      | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>3)2)</sup> | t <sub>9</sub> CC         | -      | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>2)</sup>   | <i>t</i> <sub>10</sub> CC | -      | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>2)</sup>                            | <i>t</i> <sub>18</sub> CC | 5      | -    | -    | ns   |                |

#### Table 42 JTAG Interface Timing for Upper Voltage Range (cont'd)

1) Under typical conditions, the JTAG interface can operate at transfer rates up to 20 MHz.

2) The falling edge on TCK is used to generate the TDO timing.

3) The setup time for TDO is given implicitly by the TCK cycle time.

**Table 43** is valid under the following conditions:  $C_{L}$  = 20 pF; voltage\_range = lower

| Parameter                        | Symbol            | Values |      |      | Unit | Note /         |

|----------------------------------|-------------------|--------|------|------|------|----------------|

|                                  |                   | Min.   | Тур. | Max. | 1    | Test Condition |

| TCK clock period                 | t <sub>1</sub> SR | 50     | -    | _    | ns   |                |

| TCK high time                    | t <sub>2</sub> SR | 16     | -    | -    | ns   |                |

| TCK low time                     | t <sub>3</sub> SR | 16     | -    | -    | ns   |                |

| TCK clock rise time              | t <sub>4</sub> SR | -      | -    | 8    | ns   |                |

| TCK clock fall time              | t <sub>5</sub> SR | _      | -    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge | t <sub>6</sub> SR | 6      | -    | -    | ns   |                |

Table 43

JTAG Interface Timing for Lower Voltage Range

| <b>Table 43</b> JTAG Interface Timing for Lower Voltage Range (contin | e Timing for Lower Voltage Range (cont'd) |

|-----------------------------------------------------------------------|-------------------------------------------|

|-----------------------------------------------------------------------|-------------------------------------------|

| Parameter                                                                | Symbol                    | Values |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

|                                                                          |                           | Min.   | Тур. | Max. | 1    | Test Condition |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6      | -    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>1)</sup>        | t <sub>8</sub> CC         | -      | 32   | 36   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>2)1)</sup> | t <sub>9</sub> CC         | -      | 32   | 36   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>1)</sup>   | <i>t</i> <sub>10</sub> CC | -      | 32   | 36   | ns   |                |

| TDO hold after TCK falling edge <sup>1)</sup>                            | <i>t</i> <sub>18</sub> CC | 5      | -    | -    | ns   |                |

1) The falling edge on TCK is used to generate the TDO timing.

2) The setup time for TDO is given implicitly by the TCK cycle time.

Figure 32 Test Clock Timing (TCK)