Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                                                |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                            |

| Core Size                  | 16/32-Bit                                                                          |

| Speed                      | 100MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI               |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                               |

| Number of I/O              | 150                                                                                |

| Program Memory Size        | 1.6MB (1.6M × 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 138K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Data Converters            | A/D 30x10b                                                                         |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 176-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-176-12                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2299h200f100labkxuma1 |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **General Device Information**

| Pin | Symbol            | Ctrl.  | Туре | Function                                      |

|-----|-------------------|--------|------|-----------------------------------------------|

| 14  | P8.1              | O0 / I | St/B | Bit 1 of Port 8, General Purpose Input/Output |

|     | CCU60_CC6<br>1    | O1     | St/B | CCU60 Channel 1 Output                        |

|     | CC1_CC1           | 02     | St/B | CC1 Channel 1 Output                          |

|     | U4C1_MCLK<br>OUT  | O3     | St/B | USIC4 Channel 1 Master Clock Output           |

|     | CCU60_CC6<br>1INB | 1      | St/B | CCU60 Channel 1 Input                         |

|     | RxDC1F            | I      | St/B | CAN Node 1 Receive Data Input                 |

| 15  | P8.0              | O0 / I | St/B | Bit 0 of Port 8, General Purpose Input/Output |

|     | CCU60_CC6<br>0    | O1     | St/B | CCU60 Channel 0 Output                        |

|     | CC1_CC0           | 02     | St/B | CC1 Channel 0 Output                          |

|     | U4C1_SELO<br>1    | O3     | St/B | USIC4 Channel 1 Select/Control 1 Output       |

|     | CCU60_CC6<br>0INB | I      | St/B | CCU60 Channel 0 Input                         |

| 18  | P6.0              | O0 / I | DA/A | Bit 0 of Port 6, General Purpose Input/Output |

|     | EMUX0             | 01     | DA/A | External Analog MUX Control Output 0 (ADC0)   |

|     | TxDC2             | O2     | DA/A | CAN Node 2 Transmit Data Output               |

|     | BRKOUT            | O3     | DA/A | OCDS Break Signal Output                      |

|     | ADCx_REQG<br>TyG  | I      | DA/A | External Request Gate Input for ADC0/1        |

|     | U1C1_DX0E         | I      | DA/A | USIC1 Channel 1 Shift Data Input              |

| 19  | P6.1              | O0 / I | DA/A | Bit 1 of Port 6, General Purpose Input/Output |

|     | EMUX1             | 01     | DA/A | External Analog MUX Control Output 1 (ADC0)   |

|     | T3OUT             | 02     | DA/A | GPT12E Timer T3 Toggle Latch Output           |

|     | U1C1_DOUT         | O3     | DA/A | USIC1 Channel 1 Shift Data Output             |

|     | ADCx_REQT<br>RyE  | I      | DA/A | External Request Trigger Input for ADC0/1     |

|     | RxDC2E            | I      | DA/A | CAN Node 2 Receive Data Input                 |

|     | ESR1_6            | Ι      | DA/A | ESR1 Trigger Input 6                          |

| Table 6     Pin Definitions and Functions (cont'd) |                  |       |      |                                                   |  |  |

|----------------------------------------------------|------------------|-------|------|---------------------------------------------------|--|--|

| Pin                                                | Symbol           | Ctrl. | Туре | Function                                          |  |  |

| 42                                                 | P5.2             | 1     | In/A | Bit 2 of Port 5, General Purpose Input            |  |  |

|                                                    | ADC0_CH2         | I     | In/A | Analog Input Channel 2 for ADC0                   |  |  |

|                                                    | TDI_A            | I     | In/A | JTAG Test Data Input                              |  |  |

| 43                                                 | P5.3             | I     | In/A | Bit 3 of Port 5, General Purpose Input            |  |  |

|                                                    | ADC0_CH3         | I     | In/A | Analog Input Channel 3 for ADC0                   |  |  |

|                                                    | T3INA            | I     | In/A | GPT12E Timer T3 Count/Gate Input                  |  |  |

| 47                                                 | P5.4             | 1     | In/A | Bit 4 of Port 5, General Purpose Input            |  |  |

|                                                    | ADC0_CH4         | 1     | In/A | Analog Input Channel 4 for ADC0                   |  |  |

|                                                    | CCU63_T12<br>HRB | I     | In/A | External Run Control Input for T12 of CCU63       |  |  |

|                                                    | T3EUDA           | I     | In/A | GPT12E Timer T3 External Up/Down Control<br>Input |  |  |

|                                                    | TMS_A            | 1     | In/A | JTAG Test Mode Selection Input                    |  |  |

| 48                                                 | P5.5             | I     | In/A | Bit 5 of Port 5, General Purpose Input            |  |  |

|                                                    | ADC0_CH5         | 1     | In/A | Analog Input Channel 5 for ADC0                   |  |  |

|                                                    | CCU60_T12<br>HRB | I     | In/A | External Run Control Input for T12 of CCU60       |  |  |

| 49                                                 | P5.6             | I     | In/A | Bit 6 of Port 5, General Purpose Input            |  |  |

|                                                    | ADC0_CH6         | I     | In/A | Analog Input Channel 6 for ADC0                   |  |  |

| 50                                                 | P5.7             | I     | In/A | Bit 7 of Port 5, General Purpose Input            |  |  |

|                                                    | ADC0_CH7         | I     | In/A | Analog Input Channel 7 for ADC0                   |  |  |

| 51                                                 | P5.8             | I     | In/A | Bit 8 of Port 5, General Purpose Input            |  |  |

|                                                    | ADC0_CH8         | I     | In/A | Analog Input Channel 8 for ADC0                   |  |  |

|                                                    | ADC1_CH8         | I     | In/A | Analog Input Channel 8 for ADC1                   |  |  |

|                                                    | CCU6x_T12H<br>RC | I     | In/A | External Run Control Input for T12 of CCU60/1/2/3 |  |  |

|                                                    | CCU6x_T13H<br>RC | I     | In/A | External Run Control Input for T13 of CCU60/1/2/3 |  |  |

|                                                    | U2C0_DX0F        | I     | In/A | USIC2 Channel 0 Shift Data Input                  |  |  |

| Table 6Pin Definitions and Functions (cont'd) |                   |            |      |                                                 |  |

|-----------------------------------------------|-------------------|------------|------|-------------------------------------------------|--|

| Pin                                           | Symbol            | Ctrl.      | Туре | Function                                        |  |

| 70                                            | P11.4             | O0 / I     | St/B | Bit 4 of Port 11, General Purpose Input/Output  |  |

|                                               | CCU61_CC6<br>2    | O1         | St/B | CCU61 Channel 2 Output                          |  |

|                                               | U3C1_DOUT         | 02         | St/B | USIC3 Channel 1 Shift Data Output               |  |

|                                               | RxDC5B            | I          | St/B | CAN Node 5 Receive Data Input                   |  |

|                                               | CCU61_CC6<br>2INB | 1          | St/B | CCU61 Channel 2 Input                           |  |

|                                               | U3C1_DX0B         | I          | St/B | USIC3 Channel 1 Shift Data Input                |  |

| 71                                            | P12.10            | O0 / I     | St/B | Bit 10 of Port 12, General Purpose Input/Output |  |

|                                               | CC2_CC16          | 01         | St/B | CAPCOM2 Channel 16 Compare Output               |  |

|                                               | CCU63_COU<br>T62  | O2         | St/B | CCU63 Channel 2 Output                          |  |

|                                               | U4C0_DX1C         | I          | St/B | USIC4 Channel 0 Shift Clock Input               |  |

|                                               | U3C1_DX1C         | I          | St/B | USIC3 Channel 1 Shift Clock Input               |  |

| 72                                            | P2.2              | O0 / I     | St/B | Bit 2 of Port 2, General Purpose Input/Output   |  |

|                                               | TxDC1             | 01         | St/B | CAN Node 1 Transmit Data Output                 |  |

|                                               | CCU63_CC6<br>2    | O2         | St/B | CCU63 Channel 2 Output                          |  |

|                                               | AD15              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 15     |  |

|                                               | CCU63_CC6<br>2INB | 1          | St/B | CCU63 Channel 2 Input                           |  |

|                                               | ESR2_5            | I          | St/B | ESR2 Trigger Input 5                            |  |

| 73                                            | P11.3             | O0 / I     | St/B | Bit 3 of Port 11, General Purpose Input/Output  |  |

|                                               | CCU61_COU<br>T63  | O1         | St/B | CCU61 Channel 3 Output                          |  |

|                                               | CCU61_COU<br>T62  | O2         | St/B | CCU61 Channel 2 Output                          |  |

|                                               | TxDC5             | O3         | St/B | CAN Node 5 Transmit Data Input                  |  |

|                                               | CCU61_T13<br>HRF  | 1          | St/B | External Run Control Input for T13 of CCU61     |  |

|                                               | U4C0_DX1A         | I          | St/B | USIC4 Channel 0 Shift Clock Input               |  |

| Table 6Pin Definitions and Functions (cont'd) |                   |        |      |                                                |  |  |

|-----------------------------------------------|-------------------|--------|------|------------------------------------------------|--|--|

| Pin                                           | Symbol            | Ctrl.  | Туре | Function                                       |  |  |

| 81                                            | P12.8             | O0 / I | St/B | Bit 8 of Port 12, General Purpose Input/Output |  |  |

|                                               | CC1_CC8           | 01 / I | St/B | CAPCOM1 CC8IO Capture Inp./ Compare Out.       |  |  |

|                                               | U3C1_DOUT         | O3     | St/B | USIC3 Channel 1 Shift Data Output              |  |  |

|                                               | U4C0_DX0C         | I      | St/B | USIC4 Channel 0 Shift Data Input               |  |  |

| 82                                            | P11.0             | O0 / I | St/B | Bit 0 of Port 11, General Purpose Input/Output |  |  |

|                                               | CCU61_COU<br>T60  | 01     | St/B | CCU61 Channel 0 Output                         |  |  |

|                                               | U3C1_SCLK<br>OUT  | O2     | St/B | USIC3 Channel 1 Shift Clock Output             |  |  |

|                                               | U4C0_SCLK<br>OUT  | O3     | St/B | USIC4 Channel 0 Shift Clock Output             |  |  |

|                                               | U4C0_DX1D         | I      | St/B | USIC4 Channel 0 Shift Clock Input              |  |  |

|                                               | CCU63_CCP<br>OS0A | I      | St/B | CCU63 Position Input 0                         |  |  |

|                                               | RxDC0F            | I      | St/B | CAN Node 0 Receive Data Input                  |  |  |

|                                               | U3C1_DX1A         | I      | St/B | USIC3 Channel 1 Shift Clock Input              |  |  |

|                                               | ESR1_7            | I      | St/B | ESR1 Trigger Input 7                           |  |  |

| 83                                            | P2.5              | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output  |  |  |

|                                               | U0C0_SCLK<br>OUT  | 01     | St/B | USIC0 Channel 0 Shift Clock Output             |  |  |

|                                               | TxDC0             | O2     | St/B | CAN Node 0 Transmit Data Output                |  |  |

|                                               | CC2_CC18          | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.      |  |  |

|                                               | A18               | ОН     | St/B | External Bus Interface Address Line 18         |  |  |

|                                               | U0C0_DX1D         | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |  |

|                                               | ESR1_10           | I      | St/B | ESR1 Trigger Input 10                          |  |  |

|                                               | U3C1_DX0D         | 1      | St/B | USIC3 Channel 1 Shift Data Input               |  |  |

| Table | e 6 Pin De        | finitior | is and | Functions (cont'd)                              |

|-------|-------------------|----------|--------|-------------------------------------------------|

| Pin   | Symbol            | Ctrl.    | Туре   | Function                                        |

| 153   | P9.4              | O0 / I   | St/B   | Bit 4 of Port 9, General Purpose Input/Output   |

|       | CCU63_COU<br>T61  | O1       | St/B   | CCU63 Channel 1 Output                          |

|       | U2C0_DOUT         | 02       | St/B   | USIC2 Channel 0 Shift Data Output               |

|       | CCU62_COU<br>T63  | O3       | St/B   | CCU62 Channel 3 Output                          |

| 154   | P9.5              | O0 / I   | St/B   | Bit 5 of Port 9, General Purpose Input/Output   |

|       | CCU63_COU<br>T62  | O1       | St/B   | CCU63 Channel 2 Output                          |

|       | U2C0_DOUT         | 02       | St/B   | USIC2 Channel 0 Shift Data Output               |

|       | CCU62_COU<br>T62  | O3       | St/B   | CCU62 Channel 2 Output                          |

|       | U2C0_DX0E         | I        | St/B   | USIC2 Channel 0 Shift Data Input                |

|       | CCU60_CCP<br>OS2B | 1        | St/B   | CCU60 Position Input 2                          |

| 156   | P10.14            | O0 / I   | St/B   | Bit 14 of Port 10, General Purpose Input/Output |

|       | U1C0_SELO<br>1    | 01       | St/B   | USIC1 Channel 0 Select/Control 1 Output         |

|       | U0C1_DOUT         | 02       | St/B   | USIC0 Channel 1 Shift Data Output               |

|       | U3C0_SCLK<br>OUT  | O3       | St/B   | USIC3 Channel 0 Shift Clock Output              |

|       | RD                | ОН       | St/B   | External Bus Interface Read Strobe Output       |

|       | ESR2_2            | I        | St/B   | ESR2 Trigger Input 2                            |

|       | U0C1_DX0C         | I        | St/B   | USIC0 Channel 1 Shift Data Input                |

|       | RxDC3C            | I        | St/B   | CAN Node 3 Receive Data Input                   |

|       | U3C0_DX1A         | I        | St/B   | USIC3 Channel 0 Shift Clock Input               |

## **Functional Description**

| Address Area         | Start Loc.           | End Loc.             | Area Size <sup>2)</sup> | Notes |  |  |  |

|----------------------|----------------------|----------------------|-------------------------|-------|--|--|--|

| Dualport RAM (DPRAM) | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                |       |  |  |  |

| Reserved for DPRAM   | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbytes                |       |  |  |  |

| ESFR area            | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbytes              |       |  |  |  |

| XSFR area            | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                |       |  |  |  |

| Data SRAM (DSRAM)    | 00'8000 <sub>H</sub> | 00'DFFF <sub>H</sub> | 24 Kbytes               |       |  |  |  |

| External memory area | 00'000 <sub>H</sub>  | 00'7FFF <sub>H</sub> | 32 Kbytes               |       |  |  |  |

## Table 8XC229[89]H Memory Map (cont'd)1)

Accesses to the shaded areas are reserved. In devices with external bus interface these accesses generate external bus accesses.

2) The areas marked with "<" are slightly smaller than indicated, see column "Notes".

3) The uppermost 4-Kbyte sector of the first Flash segment is reserved for internal use (C0'F000<sub>H</sub> to C0'FFFF<sub>H</sub>).

4) Several pipeline optimizations are not active within the external IO area. This is necessary to control external peripherals properly.

This common memory space consists of 16 Mbytes organized as 256 segments of 64 Kbytes; each segment contains four data pages of 16 Kbytes. The entire memory space can be accessed bytewise or wordwise. Portions of the on-chip DPRAM and the register spaces (ESFR/SFR) additionally are directly bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls access to the program memories such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls access to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected to the high-speed system bus so that they can exchange data. This is required if operands are read from program memory, code or data is written to the PSRAM, code is fetched from external memory, or data is read from or written to external resources. These include peripherals on the LXBus such as USIC or MultiCAN. The system bus allows concurrent two-way communication for maximum transfer performance.

**Up to 112 Kbytes of on-chip Program SRAM (PSRAM)** are provided to store user code or data. The PSRAM is accessed via the PMU and is optimized for code fetches. A section of the PSRAM with programmable size can be write-protected.

Note: The actual size of the PSRAM depends on the quoted device type.

#### **Functional Description**

Up to 24 Kbytes of on-chip Data SRAM (DSRAM) are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**8 Kbytes of on-chip Stand-By SRAM (SBRAM)** provide storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

**1024 bytes (2** × **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XC2000 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

In order to meet the requirements of designs where more memory is required than is available on chip, up to 12 Mbytes (approximately, see **Table 8**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

**The on-chip Flash memory** stores code, constant data, and control data. The 1,600 Kbytes of on-chip Flash memory consist of 1 module of 64 Kbytes (preferably for data storage) and 6 modules of 256 Kbytes. Each module is organized in 4-Kbyte sectors.

The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen device type.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see Section 4.6.

To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

## **Functional Description**

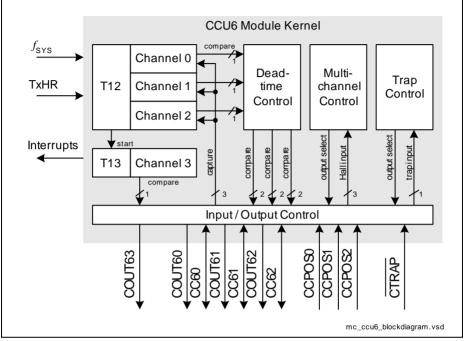

## Figure 7 CCU6 Block Diagram

Timer T12 can work in capture and/or compare mode for its three channels. The modes can also be combined. Timer T13 can work in compare mode only. The multi-channel control unit generates output patterns that can be modulated by timer T12 and/or timer T13. The modulation sources can be selected and combined for signal modulation.

### **Functional Description**

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time-based interrupt, to provide a system time tick independent of CPU frequency and other resources

- 48-bit timer for long-term measurements

- Alarm interrupt at a defined time

### **Functional Description**

### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Independent CAN nodes

- Set of independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- · Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

# **Functional Description**

| Mnemonic     | Description                                                                              | Bytes |  |  |  |

|--------------|------------------------------------------------------------------------------------------|-------|--|--|--|

| ROL/ROR      | Rotate left/right direct word GPR                                                        | 2     |  |  |  |

| ASHR         | Arithmetic (sign bit) shift right direct word GPR                                        | 2     |  |  |  |

| MOV(B)       | Move word (byte) data                                                                    | 2/4   |  |  |  |

| MOVBS/Z      | Move byte operand to word op. with sign/zero extension                                   |       |  |  |  |

| JMPA/I/R     | Jump absolute/indirect/relative if condition is met                                      | 4     |  |  |  |

| JMPS         | Jump absolute to a code segment                                                          | 4     |  |  |  |

| JB(C)        | Jump relative if direct bit is set (and clear bit)                                       | 4     |  |  |  |

| JNB(S)       | Jump relative if direct bit is not set (and set bit)                                     | 4     |  |  |  |

| CALLA/I/R    | Call absolute/indirect/relative subroutine if condition is met                           | 4     |  |  |  |

| CALLS        | Call absolute subroutine in any code segment                                             | 4     |  |  |  |

| PCALL        | Push direct word register onto system stack and call absolute subroutine                 | 4     |  |  |  |

| TRAP         | Call interrupt service routine via immediate trap number                                 | 2     |  |  |  |

| PUSH/POP     | Push/pop direct word register onto/from system stack                                     | 2     |  |  |  |

| SCXT         | Push direct word register onto system stack and update register with word operand        |       |  |  |  |

| RET(P)       | Return from intra-segment subroutine<br>(and pop direct word register from system stack) | 2     |  |  |  |

| RETS         | Return from inter-segment subroutine                                                     | 2     |  |  |  |

| RETI         | Return from interrupt service subroutine                                                 | 2     |  |  |  |

| SBRK         | Software Break                                                                           | 2     |  |  |  |

| SRST         | Software Reset                                                                           | 4     |  |  |  |

| IDLE         | Enter Idle Mode                                                                          | 4     |  |  |  |

| PWRDN        | Unused instruction <sup>1)</sup>                                                         | 4     |  |  |  |

| SRVWDT       | Service Watchdog Timer                                                                   |       |  |  |  |

| DISWDT/ENWDT | Disable/Enable Watchdog Timer                                                            |       |  |  |  |

| EINIT        | End-of-Initialization Register Lock                                                      |       |  |  |  |

| ATOMIC       | Begin ATOMIC sequence                                                                    | 2     |  |  |  |

| EXTR         | Begin EXTended Register sequence                                                         | 2     |  |  |  |

| EXTP(R)      | Begin EXTended Page (and Register) sequence                                              | 2/4   |  |  |  |

| EXTS(R)      | Begin EXTended Segment (and Register) sequence                                           | 2/4   |  |  |  |

## 4.2 Voltage Range definitions

The XC229[89]H timing depends on the supply voltage. If such a dependency exists the timing values are given for 2 voltage areas commonly used. The voltage areas are defined in the following tables.

### Table 14 Upper Voltage Range Definition

| Parameter                                                       | Symbol               |      | Values |      | Unit | Note /         |

|-----------------------------------------------------------------|----------------------|------|--------|------|------|----------------|

|                                                                 |                      | Min. | Тур.   | Max. |      | Test Condition |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$ | 4.5  | 5      | 5.5  | V    |                |

### Table 15 Lower Voltage Range Definition

| Parameter                                                       | Symbol               |      | Values |      | Unit | Note /         |

|-----------------------------------------------------------------|----------------------|------|--------|------|------|----------------|

|                                                                 |                      | Min. | Тур.   | Max. |      | Test Condition |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$ | 3.0  | 3.3    | 4.5  | V    |                |

# 4.2.1 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XC229[89]H and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

**CC** (Controller Characteristics):

The logic of the XC229[89]H provides signals with the specified characteristics.

SR (System Requirement):

The external system must provide signals with the specified characteristics to the XC229[89]H.

# 4.3 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

The XC229[89]H can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XC229[89]H are designed to operate in various driver modes. The DC parameter specifications refer to the pad current limits specified in **Section 4.7.4**.

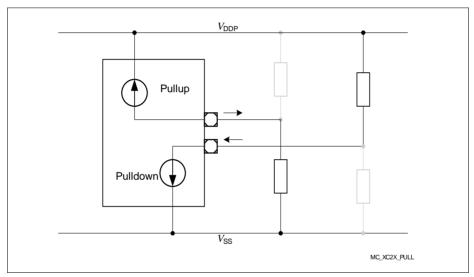

### Pullup/Pulldown Device Behavior

Most pins of the XC229[89]H feature pullup or pulldown devices. For some special pins these are fixed; for the port pins they can be selected by the application.

The specified current values indicate how to load the respective pin depending on the intended signal level. **Figure 14** shows the current paths.

The shaded resistors shown in the figure may be required to compensate system pull currents that do not match the given limit values.

Figure 14 Pullup/Pulldown Current Definition

# 4.3.3 Power Consumption

The power consumed by the XC229[89]H depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current  $I_{\rm S}$  depends on the device activity

- The leakage current  $I_{LK}$  depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Standby mode:

Voltage domain DMP\_1 switched off completely, power supply control switched off. DMP\_M domain is supplied by ultra low power electronic voltage regulator (ULPEVR). The alternate regulator EVR\_M is switched off.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{DDIM}$  and  $V_{DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

| Parameter                                              | Symbol                  |      | Values | i     | Unit | Note /<br>Test Condition       |

|--------------------------------------------------------|-------------------------|------|--------|-------|------|--------------------------------|

|                                                        |                         | Min. | Тур.   | Max.  |      |                                |

| Leakage supply current                                 | $I_{\rm LK0}  {\rm CC}$ | -    | 20     | 35    | μA   | <i>T</i> <sub>J</sub> = 25 °C  |

| (DMP_1 off) <sup>1)2)</sup>                            |                         | -    | 115    | 330   | μA   | <i>T</i> <sub>J</sub> = 85 °C  |

|                                                        |                         | -    | 270    | 880   | μA   | <i>T</i> <sub>J</sub> = 125 °C |

|                                                        |                         | -    | 420    | 1.445 | μA   | <i>T</i> <sub>J</sub> = 150 °C |

| Leakage supply current (DMP_1 powered) <sup>1)2)</sup> | I <sub>LK1</sub> CC     | -    | 0.04   | 0.06  | mA   | <i>T</i> <sub>J</sub> = 25 °C  |

|                                                        |                         | -    | 0.7    | 1.8   | mA   | <i>T</i> <sub>J</sub> = 85 °C  |

|                                                        |                         | -    | 3.1    | 8.6   | mA   | <i>T</i> <sub>J</sub> = 125 °C |

|                                                        |                         | -    | 6.6    | 19.2  | mA   | <i>T</i> <sub>J</sub> = 150 °C |

## Table 19 Leakage Power Consumption

The supply current caused by leakage depends mainly on the junction temperature and the supply voltage. The temperature difference between the junction temperature T<sub>J</sub> and the ambient temperature T<sub>A</sub> must be taken into account. As this fraction of the supply current does not depend on device activity, it must be added to other power consumption values.

All inputs (including pins configured as inputs) are set at 0 V to 0.1 V or at V<sub>DDP</sub> - 0.1 V to V<sub>DDP</sub> and all outputs (including pins configured as outputs) are disconnected.

Note: A fraction of the leakage current flows through domain DMP\_A (pin  $V_{DDPA}$ ). This current can be calculated as 7,000 ×  $e^{-\alpha}$ , with  $\alpha = 5000 / (273 + 1.3 \times T_J)$ . For  $T_J = 150^{\circ}$ C, this results in a current of 160  $\mu$ A.

The leakage power consumption can be calculated according to the following formulas:  $I_{I K0} = 500,000 \times e^{-\alpha}$  with  $\alpha = 3000 / (273 + B \times T_J)$

Parameter B must be replaced by

- 1.0 for typical values

- 1.6 for maximum values

$I_{LK1} = 600,000 \times e^{-\alpha}$  with  $\alpha = 5000 / (273 + B \times T_{J})$

Parameter B must be replaced by

- 1.1 for typical values

- 1.4 for maximum values

## Coding of bit fields LEVxV in SWD and PVC Configuration Registers

| County of bit netus LEVXV |                                                                                                                                                                                                                                                                       |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Default Voltage Level     | Notes <sup>1)</sup>                                                                                                                                                                                                                                                   |

| 2.9 V                     |                                                                                                                                                                                                                                                                       |

| 3.0 V                     | LEV1V: reset request                                                                                                                                                                                                                                                  |

| 3.1 V                     |                                                                                                                                                                                                                                                                       |

| 3.2 V                     |                                                                                                                                                                                                                                                                       |

| 3.3 V                     |                                                                                                                                                                                                                                                                       |

| 3.4 V                     |                                                                                                                                                                                                                                                                       |

| 3.6 V                     |                                                                                                                                                                                                                                                                       |

| 4.0 V                     |                                                                                                                                                                                                                                                                       |

| 4.2 V                     |                                                                                                                                                                                                                                                                       |

| 4.5 V                     | LEV2V: no request                                                                                                                                                                                                                                                     |

| 4.6 V                     |                                                                                                                                                                                                                                                                       |

| 4.7 V                     |                                                                                                                                                                                                                                                                       |

| 4.8 V                     |                                                                                                                                                                                                                                                                       |

| 4.9 V                     |                                                                                                                                                                                                                                                                       |

| 5.0 V                     |                                                                                                                                                                                                                                                                       |

| 5.5 V                     |                                                                                                                                                                                                                                                                       |

|                           | Default Voltage Level           2.9 V           3.0 V           3.1 V           3.2 V           3.3 V           3.4 V           3.6 V           4.0 V           4.2 V           4.5 V           4.6 V           4.7 V           4.8 V           4.9 V           5.0 V |

## Table 23 Coding of bit fields LEVxV in Register SWDCON0

1) The indicated default levels are selected automatically after a power reset.

## Table 24 Coding of bit fields LEVxV in Registers PVCyCONz

| Code             | Default Voltage Level | Notes <sup>1)</sup>                    |

|------------------|-----------------------|----------------------------------------|

| 000 <sub>B</sub> | 0.95 V                |                                        |

| 001 <sub>B</sub> | 1.05 V                |                                        |

| 010 <sub>B</sub> | 1.15 V                |                                        |

| 011 <sub>B</sub> | 1.25 V                |                                        |

| 100 <sub>B</sub> | 1.35 V                | LEV1V: reset request                   |

| 101 <sub>B</sub> | 1.45 V                | LEV2V: interrupt request <sup>2)</sup> |

| 110 <sub>B</sub> | 1.55 V                |                                        |

| 111 <sub>B</sub> | 1.65 V                |                                        |

1) The indicated default levels are selected automatically after a power reset.

2) Due to variations of the tolerance of both the Embedded Voltage Regulators (EVR) and the PVC levels, this interrupt can be triggered inadvertently, even though the core voltage is within the normal range. It is, therefore, recommended not to use this warning level.

| Parameter                          | Symbol             | Values |      |                                          | Unit | Note /                                                                                                                                                                 |

|------------------------------------|--------------------|--------|------|------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                    | Min.   | Тур. | Max.                                     |      | Test Condition                                                                                                                                                         |

| Rise and Fall times (10% -<br>90%) | t <sub>RF</sub> CC | _      | _    | 37 +<br>0.65 x<br>C <sub>L</sub>         | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Medium                                                                               |

|                                    |                    | _      | _    | 24 +<br>0.3 x<br>C <sub>L</sub>          | ns   | $\begin{array}{l} C_{L} \geq 20 \text{ pF};\\ C_{L} \leq 100 \text{ pF};\\ \text{Driver_Strength}\\ = \text{Strong};\\ \text{Driver_Edge}\\ \text{Medium} \end{array}$ |

|                                    |                    | -      | -    | 6.2 +<br>0.24 x<br><i>C</i> <sub>L</sub> | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Sharp                                                     |

|                                    |                    | _      | -    | 34 +<br>0.3 x<br>C <sub>L</sub>          | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Strong;<br>Driver_Edge=<br>Slow                                                      |

|                                    |                    | _      | _    | 500 +<br>2.5 x<br>C <sub>L</sub>         | ns   | $C_{L} \ge 20 \text{ pF};$<br>$C_{L} \le 100 \text{ pF};$<br>Driver_Strength<br>= Weak                                                                                 |

Table 30 Standard Pad Parameters for Lower Voltage Range (cont'd)

An output current above |I<sub>OXnom</sub>| may be drawn from up to three pins at the same time. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

### **Electrical Parameters**

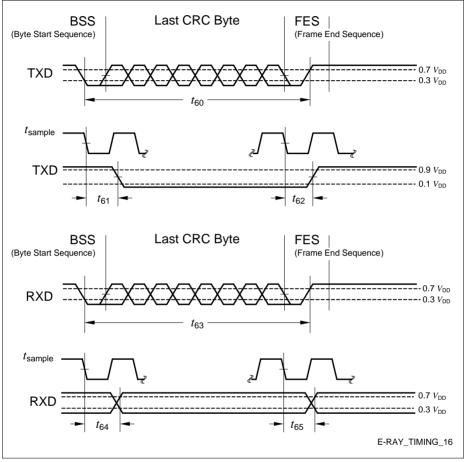

Figure 28 FlexRay Timing