Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 34                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 42-SDIP (0.600", 15.24mm)                                              |

| Supplier Device Package    | 42-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08gt16acbe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Memory

Table 4-2. Direct-Page Register Summary (Sheet 1 of 3)

| Address        | Register Name | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|----------------|---------------|--------|---------|--------|--------|--------|--------|--------|--------|

| 0x00 <b>00</b> | PTAD          | PTAD7  | PTAD6   | PTAD5  | PTAD4  | PTAD3  | PTAD2  | PTAD1  | PTAD0  |

| 0x00 <b>01</b> | PTAPE         | PTAPE7 | PTAPE6  | PTAPE5 | PTAPE4 | PTAPE3 | PTAPE2 | PTAPE1 | PTAPE0 |

| 0x00 <b>02</b> | PTASE         | PTASE7 | PTASE6  | PTASE5 | PTASE4 | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

| 0x00 <b>03</b> | PTADD         | PTADD7 | PTADD6  | PTADD5 | PTADD4 | PTADD3 | PTADD2 | PTADD1 | PTADD0 |

| 0x00 <b>04</b> | PTBD          | PTBD7  | PTBD6   | PTBD5  | PTBD4  | PTBD3  | PTBD2  | PTBD1  | PTBD0  |

| 0x00 <b>05</b> | PTBPE         | PTBPE7 | PTBPE6  | PTBPE5 | PTBPE4 | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x00 <b>06</b> | PTBSE         | PTBSE7 | PTBSE6  | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x00 <b>07</b> | PTBDD         | PTBDD7 | PTBDD6  | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| <b>80</b> 00x0 | PTCD          | PTCD7  | PTCD6   | PTCD5  | PTCD4  | PTCD3  | PTCD2  | PTCD1  | PTCD0  |

| 0x00 <b>09</b> | PTCPE         | PTCPE7 | PTCPE6  | PTCPE5 | PTCPE4 | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

| 0x00 <b>0A</b> | PTCSE         | PTCSE7 | PTCSE6  | PTCSE5 | PTCSE4 | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| 0x00 <b>0B</b> | PTCDD         | PTCDD7 | PTCDD6  | PTCDD5 | PTCDD4 | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| 0x00 <b>0C</b> | PTDD          | 0      | 0       | 0      | PTDD4  | PTDD3  | PTDD2  | PTDD1  | PTDD0  |

| 0x00 <b>0D</b> | PTDPE         | 0      | 0       | 0      | PTDPE4 | PTDPE3 | PTDPE2 | PTDPE1 | PTDPE0 |

| 0x00 <b>0E</b> | PTDSE         | 0      | 0       | 0      | PTDSE4 | PTDSE3 | PTDSE2 | PTDSE1 | PTDSE0 |

| 0x00 <b>0F</b> | PTDDD         | 0      | 0       | 0      | PTDDD4 | PTDDD3 | PTDDD2 | PTDDD1 | PTDDD0 |

| 0x00 <b>10</b> | PTED          | 0      | 0       | PTED5  | PTED4  | PTED3  | PTED2  | PTED1  | PTED0  |

| 0x00 <b>11</b> | PTEPE         | 0      | 0       | PTEPE5 | PTEPE4 | PTEPE3 | PTEPE2 | PTEPE1 | PTEPE0 |

| 0x00 <b>12</b> | PTESE         | 0      | 0       | PTESE5 | PTESE4 | PTESE3 | PTESE2 | PTESE1 | PTESE0 |

| 0x00 <b>13</b> | PTEDD         | 0      | 0       | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 | PTEDD0 |

| 0x00 <b>14</b> | IRQSC         | 0      | 0       | IRQEDG | IRQPE  | IRQF   | IRQACK | IRQIE  | IRQMOD |

| 0x00 <b>15</b> | Reserved      | _      | _       | _      | _      | _      | -      | _      | _      |

| 0x00 <b>16</b> | KBISC         | KBEDG7 | KBEDG6  | KBEDG5 | KBEDG4 | KBF    | KBACK  | KBIE   | KBIMOD |

| 0x00 <b>17</b> | KBIPE         | KBIPE7 | KBIPE6  | KBIPE5 | KBIPE4 | KBIPE3 | KBIPE2 | KBIPE1 | KBIPE0 |

| 0x00 <b>18</b> | SCI1BDH       | 0      | 0       | 0      | SBR12  | SBR11  | SBR10  | SBR9   | SBR8   |

| 0x00 <b>19</b> | SCI1BDL       | SBR7   | SBR6    | SBR5   | SBR4   | SBR3   | SBR2   | SBR1   | SBR0   |

| 0x00 <b>1A</b> | SCI1C1        | LOOPS  | SCISWAI | RSRC   | М      | WAKE   | ILT    | PE     | PT     |

| 0x00 <b>1B</b> | SCI1C2        | TIE    | TCIE    | RIE    | ILIE   | TE     | RE     | RWU    | SBK    |

| 0x00 <b>1C</b> | SCI1S1        | TDRE   | TC      | RDRF   | IDLE   | OR     | NF     | FE     | PF     |

| 0x00 <b>1D</b> | SCI1S2        | 0      | 0       | 0      | 0      | 0      | 0      | 0      | RAF    |

| 0x00 <b>1E</b> | SCI1C3        | R8     | T8      | TXDIR  | 0      | ORIE   | NEIE   | FEIE   | PEIE   |

| 0x00 <b>1F</b> | SCI1D         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>20</b> | SCI2BDH       | 0      | 0       | 0      | SBR12  | SBR11  | SBR10  | SBR9   | SBR8   |

| 0x00 <b>21</b> | SCI2BDL       | SBR7   | SBR6    | SBR5   | SBR4   | SBR3   | SBR2   | SBR1   | SBR0   |

| 0x00 <b>22</b> | SCI2C1        | LOOPS  | SCISWAI | RSRC   | М      | WAKE   | ILT    | PE     | PT     |

| 0x00 <b>23</b> | SCI2C2        | TIE    | TCIE    | RIE    | ILIE   | TE     | RE     | RWU    | SBK    |

| 0x00 <b>24</b> | SCI2S1        | TDRE   | TC      | RDRF   | IDLE   | OR     | NF     | FE     | PF     |

| 0x00 <b>25</b> | SCI2S2        | 0      | 0       | 0      | 0      | 0      | 0      | 0      | RAF    |

| 0x00 <b>26</b> | SCI2C3        | R8     | T8      | TXDIR  | 0      | ORIE   | NEIE   | FEIE   | PEIE   |

| 0x00 <b>27</b> | SCI2D         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

MC9S08GT16A/GT8A Data Sheet, Rev. 1

Table 4-2. Direct-Page Register Summary (Sheet 2 of 3)

| Address                          | Register Name  | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

|----------------------------------|----------------|--------|----------|-------|----------|--------------|-----------|---------|--------|--|

| 0x00 <b>28</b>                   | SPIC1          | SPIE   | SPE      | SPTIE | MSTR     | CPOL         | CPHA      | SSOE    | LSBFE  |  |

| 0x00 <b>29</b>                   | SPIC2          | 0      | 0        | 0     | MODFEN   | BIDIROE      | 0         | SPISWAI | SPC0   |  |

| 0x00 <b>23</b>                   | SPIBR          | 0      | SPPR2    | SPPR1 | SPPR0    | 0            | SPR2      | SPR1    | SPR0   |  |

| 0x00 <b>2B</b>                   | SPIS           | SPRF   | 0        | SPTEF | MODF     | 0            | 0         | 0       | 0      |  |

| 0x002 <b>B</b>                   | Reserved       | 0      | 0        | 0     | 0        | 0            | 0         | 0       | 0      |  |

| 0x00 <b>2D</b>                   | SPID           | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

| 0x00 <b>2E</b>                   | Reserved       | 0      | 0        | 0     | 0        | 0            | 0         | 0       | 0      |  |

| 0x00 <b>2F</b>                   | Reserved       | 0      | 0        | 0     | 0        | 0            | 0         | 0       | 0      |  |

| 0x00 <b>30</b>                   | TPM1SC         | TOF    | TOIE     | CPWMS | CLKSB    | CLKSA        | PS2       | PS1     | PS0    |  |

| 0x00 <b>31</b>                   | TPM1CNTH       | Bit 15 | 14       | 13    | 12       | 11           | 10        | 9       | Bit 8  |  |

| 0x00 <b>32</b>                   | TPM1CNTL       | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

| 0x00 <b>33</b>                   | TPM1MODH       | Bit 15 | 14       | 13    | 12       | 11           | 10        | 9       | Bit 8  |  |

| 0x00 <b>34</b>                   | TPM1MODL       | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

| 0x00 <b>35</b>                   | TPM1C0SC       | CH0F   | CH0IE    | MS0B  | MS0A     | ELS0B        | ELS0A     | 0       | 0      |  |

| 0x00 <b>36</b>                   | TPM1C0VH       | Bit 15 | 14       | 13    | 12       | 11           | 10        | 9       | Bit 8  |  |

| 0x00 <b>37</b>                   | TPM1C0VL       | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

| 0x00 <b>38</b>                   | TPM1C1SC       | CH1F   | CH1IE    | MS1B  | MS1A     | ELS1B        | ELS1A     | 0       | 0      |  |

| 0x00 <b>39</b>                   | TPM1C1VH       | Bit 15 | 14       | 13    | 12       | 11           | 10        | 9       | Bit 8  |  |

| 0x00 <b>3A</b>                   | TPM1C1VL       | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

| 0x00 <b>3B</b>                   | TPM1C2SC       | CH2F   | CH2IE    | MS2B  | MS2A     | ELS2B        | ELS2A     | 0       | 0      |  |

| 0x00 <b>3C</b>                   | TPM1C2VH       | Bit 15 | 14       | 13    | 12       | 11           | 10        | 9       | Bit 8  |  |

| 0x00 <b>3D</b>                   | TPM1C2VL       | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

| 0x00 <b>3E</b> -                 | Reserved       | _      | _        | _     | _        | _            | _         | _       | _      |  |

| 0x00 <b>43</b>                   |                | _      | _        | _     | _        | _            | _         | _       | _      |  |

| 0x00 <b>44</b>                   | PTGD           | 0      | 0        | 0     | 0        | PTGD3        | PTGD2     | PTGD1   | PTGD0  |  |

| 0x00 <b>45</b>                   | PTGPE          | 0      | 0        | 0     | 0        | PTGPE3       | PTGPE2    | PTGPE1  | PTGPE0 |  |

| 0x00 <b>46</b>                   | PTGSE          | 0      | 0        | 0     | 0        | PTGSE3       | PTGSE2    | PTGSE1  | PTGSE0 |  |

| 0x00 <b>47</b>                   | PTGDD          | 0      | 0        | 0     | 0        | PTGDD3       | PTGDD2    | PTGDD1  | PTGDD0 |  |

| 0x00 <b>48</b>                   | ICGC1          | HGO    | RANGE    | REFS  | CL       | .KS          | OSCSTEN   |         | 0      |  |

| 0x00 <b>49</b><br>0x00 <b>4A</b> | ICGC2<br>ICGS1 | LOLRE  | /CT      | MFD   | 1016     | LOCK         | 1,000     | RFD     | ICCIE  |  |

| 0x00 <b>4A</b><br>0x00 <b>4B</b> | ICGS2          |        | KST<br>0 | REFST | LOLS     | LOCK         | LOCS<br>0 | ERCS    | ICGIF  |  |

| 0x00 <b>4B</b>                   | ICGSZ          | 0      | 0        | 0     | 0        | 0            |           | 0       | DCOS   |  |

| 0x00 <b>4C</b>                   | ICGFLTU        | 0      | U        | 0     | -        | <br>LT       | FI        | <u></u> |        |  |

| 0x00 <b>4D</b>                   | ICGTRM         |        |          |       |          | RIM          |           |         |        |  |

| 0x004E                           | Reserved       | 0      | 0        | 0     | 0        | 0            | 0         | 0       | 0      |  |

| 0x00 <b>4F</b>                   | ATDC           | ATDPU  | DJM      | RES8  | SGN      | 0            |           |         | 0      |  |

| 0x00 <b>50</b>                   | ATDSC          | CCF    | ATDIE    | ATDCO | Jain     | PRS<br>ATDCH |           |         |        |  |

| 0x00 <b>51</b>                   | ATDRH          | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

| 0x00 <b>53</b>                   | ATDRL          | Bit 7  | 6        | 5     | 4        | 3            | 2         | 1       | Bit 0  |  |

|                                  | ·              | , ,    |          |       | <u> </u> |              |           |         |        |  |

### MC9S08GT16A/GT8A Data Sheet, Rev. 1

| Address           | Register Name | Bit 7  | 6      | 5      | 4       | 3     | 2      | 1     | Bit 0 |

|-------------------|---------------|--------|--------|--------|---------|-------|--------|-------|-------|

| 0x1811            | DBGCAL        | Bit 7  | 6      | 5      | 4       | 3     | 2      | 1     | Bit 0 |

| 0x1812            | DBGCBH        | Bit 15 | 14     | 13     | 12      | 11    | 10     | 9     | Bit 8 |

| 0x1813            | DBGCBL        | Bit 7  | 6      | 5      | 4       | 3     | 2      | 1     | Bit 0 |

| 0x1814            | DBGFH         | Bit 15 | 14     | 13     | 12      | 11    | 10     | 9     | Bit 8 |

| 0x1815            | DBGFL         | Bit 7  | 6      | 5      | 4       | 3     | 2      | 1     | Bit 0 |

| 0x1816            | DBGC          | DBGEN  | ARM    | TAG    | BRKEN   | RWA   | RWAEN  | RWB   | RWBEN |

| 0x1817            | DBGT          | TRGSEL | BEGIN  | 0      | 0       | TRG3  | TRG2   | TRG1  | TRG0  |

| 0x1818            | DBGS          | AF     | BF     | ARMF   | 0       | CNT3  | CNT2   | CNT1  | CNT0  |

| 0x1819–<br>0x181F | Reserved      | _      | _      | _      | _       | _     | _      | _     | _     |

| 0x1820            | FCDIV         | DIVLD  | PRDIV8 | DIV5   | DIV4    | DIV3  | DIV2   | DIV1  | DIV0  |

| 0x1821            | FOPT          | KEYEN  | FNORED | 0      | 0       | 0     | 0      | SEC01 | SEC00 |

| 0x1822            | Reserved      | _      | _      | _      | _       | _     | _      |       | _     |

| 0x1823            | FCNFG         | 0      | 0      | KEYACC | 0       | 0     | 0      | 0     | 0     |

| 0x1824            | FPROT         | FPS7   | FPS6   | FPS5   | FPS4    | FPS3  | FPS2   | FPS1  | FPDIS |

| 0x1825            | FSTAT         | FCBEF  | FCCF   | FPVIOL | FACCERR | 0     | FBLANK | 0     | 0     |

| 0x1826            | FCMD          | FCMD7  | FCMD6  | FCMD5  | FCMD4   | FCMD3 | FCMD2  | FCMD1 | FCMD0 |

| 0x1827-<br>0x182B | Reserved      | _<br>_ | _      | _<br>_ |         | _     | _      | _     |       |

Nonvolatile FLASH registers, shown in Table 4-4, are located in the FLASH memory. These registers include an 8-byte backdoor key which optionally can be used to gain access to secure memory resources. During reset events, the contents of NVPROT and NVOPT in the nonvolatile register area of the FLASH memory are transferred into corresponding FPROT and FOPT working registers in the high-page registers to control security and block protection options.

**Table 4-4. Nonvolatile Register Summary**

| Address            | Register Name         | Bit 7                 | 6      | 5    | 4    | 3    | 2    | 1     | Bit 0 |  |

|--------------------|-----------------------|-----------------------|--------|------|------|------|------|-------|-------|--|

| 0xFFB0 –<br>0xFFB7 | NVBACKKEY             | 8-Byte Comparison Key |        |      |      |      |      |       |       |  |

| 0xFFB8 –           | Reserved              | _                     | _      | _    | _    | _    | _    | _     | _     |  |

| 0xFFBC             |                       | _                     | _      | _    | _    | _    | _    | _     | _     |  |

| 0xFFBD             | NVPROT                | FPS7                  | FPS6   | FPS5 | FPS4 | FPS3 | FPS2 | FPS1  | FPDIS |  |

| 0xFFBE             | NVICGTRM <sup>1</sup> | NVTRIM                |        |      |      |      |      |       |       |  |

| 0xFFBF             | NVOPT                 | KEYEN                 | FNORED | 0    | 0    | 0    | 0    | SEC01 | SEC00 |  |

<sup>&</sup>lt;sup>1</sup> NVICGTRM is the factory trim value. This value must be copied to ICGTRM in user code.

Provided the key enable (KEYEN) bit is 1, the 8-byte comparison key can be used to temporarily disengage memory security. This key mechanism can be accessed only through user code running in secure memory. (A security key cannot be entered directly through background debug commands.) This security key can be disabled completely by programming the KEYEN bit to 0. If the security key is disabled, the

### MC9S08GT16A/GT8A Data Sheet, Rev. 1

makes the MCU secure. During development, whenever the FLASH is erased, it is good practice to immediately program the SEC00 bit to 0 in NVOPT so SEC01:SEC00 = 1:0. This would allow the MCU to remain unsecured after a subsequent reset.

The on-chip debug module cannot be enabled while the MCU is secure. The separate background debug controller can still be used for background memory access commands, but the MCU cannot enter active background mode except by holding BKGD/MS low at the rising edge of reset.

A user can choose to allow or disallow a security unlocking mechanism through an 8-byte backdoor security key. If the nonvolatile KEYEN bit in NVOPT/FOPT is 0, the backdoor key is disabled and there is no way to disengage security without completely erasing all FLASH locations. If KEYEN is 1, a secure user program can temporarily disengage security by:

- 1. Writing 1 to KEYACC in the FCNFG register. This makes the FLASH module interpret writes to the backdoor comparison key locations (NVBACKKEY through NVBACKKEY+7) as values to be compared against the key rather than as the first step in a FLASH program or erase command.

- 2. Writing the user-entered key values to the NVBACKKEY through NVBACKKEY+7 locations. These writes must be done in order, starting with the value for NVBACKKEY and ending with NVBACKKEY+7. STHX should not be used for these writes because these writes cannot be done on adjacent bus cycles. User software normally would get the key codes from outside the MCU system through a communication interface such as a serial I/O.

- 3. Writing 0 to KEYACC in the FCNFG register. If the 8-byte key that was just written matches the key stored in the FLASH locations, SEC01:SEC00 are automatically changed to 1:0 and security will be disengaged until the next reset.

The security key can be written only from RAM, so it cannot be entered through background commands without the cooperation of a secure user program.

The backdoor comparison key (NVBACKKEY through NVBACKKEY+7) is located in FLASH memory locations in the nonvolatile register space so users can program these locations exactly as they would program any other FLASH memory location. The nonvolatile registers are in the same 512-byte block of FLASH as the reset and interrupt vectors, so block protecting that space also block protects the backdoor comparison key. Block protects cannot be changed from user application programs, so if the vector space is block protected, the backdoor security key mechanism cannot permanently change the block protect, security settings, or the backdoor key.

Security can always be disengaged through the background debug interface by performing these steps:

- 1. Disable any block protections by writing FPROT. FPROT can be written only with background debug commands, not from application software.

- 2. Mass erase FLASH, if necessary.

- 3. Blank check FLASH. Provided FLASH is completely erased, security is disengaged until the next reset.

To avoid returning to secure mode after the next reset, program NVOPT so SEC01:SEC00 = 1:0.

Resets, Interrupts, and System Configuration

# 5.7.2 System Reset Status Register (SRS)

This register includes six read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

| _                  | 7   | 6                                                             | 5        | 4        | 3    | 2        | 1   | 0 |  |  |  |  |

|--------------------|-----|---------------------------------------------------------------|----------|----------|------|----------|-----|---|--|--|--|--|

| R                  | POR | PIN                                                           | COP      | ILOP     | ILAD | ICG      | LVD | 0 |  |  |  |  |

| w                  |     | Writing any value to SIMRS address clears COP watchdog timer. |          |          |      |          |     |   |  |  |  |  |

| Power-on reset:    | 1   | 0                                                             | 0        | 0        | 0    | 0        | 1   | 0 |  |  |  |  |

| Low-voltage reset: | U   | 0                                                             | 0        | 0        | 0    | 0        | 1   | 0 |  |  |  |  |

| Any other reset:   | 0   | Note (1)                                                      | Note (1) | Note (1) | 0    | Note (1) | 0   | 0 |  |  |  |  |

U = Unaffected by reset

Figure 5-3. System Reset Status (SRS)

**Table 5-3. SRS Field Descriptions**

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVD) status bit is also set to indicate that the reset occurred while the internal supply was below the LVD threshold.  O Reset not caused by POR.  1 POR caused reset.                                                                     |

| 6<br>PIN  | External Reset Pin — Reset was caused by an active-low level on the external reset pin.  O Reset not caused by external reset pin.  Reset came from external reset pin.                                                                                                                                                                                                                               |

| 5<br>COP  | Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source may be blocked by COPE = 0.  Reset not caused by COP timeout.  Reset caused by COP timeout.                                                                                                                                                                                     |

| 4<br>ILOP | Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.  O Reset not caused by an illegal opcode.  1 Reset caused by an illegal opcode. |

Any of these reset sources that are active at the time of reset will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset will be cleared.

### Central Processor Unit (S08CPUV2)

Table 8-3. Opcode Map (Sheet 1 of 2)

| Bit-Manipulation                         | Branch                |                       | Rea                    | ad-Modify-W            | /rite                  |                       | Cor                    | itrol                 |                      |                      | Register             | /Memory              |                      |                     |

|------------------------------------------|-----------------------|-----------------------|------------------------|------------------------|------------------------|-----------------------|------------------------|-----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|

| 00 5 10 5<br>BRSET0 BSET0<br>3 DIR 2 DIR | 20 3<br>BRA<br>2 REL  | 30 5<br>NEG<br>2 DIR  | NEGA                   | 50 1<br>NEGX<br>1 INH  | 60 5<br>NEG<br>2 IX1   | 70 4<br>NEG<br>1 IX   | 80 9<br>RTI<br>1 INH   | 90 3<br>BGE<br>2 REL  | SUB                  | SUB<br>2 DIR         | SUB                  | D0 4<br>SUB<br>3 IX2 | E0 3<br>SUB<br>2 IX1 | F0 3<br>SUB<br>1 IX |

| 01 5 11 5<br>BRCLR0 BCLR0<br>3 DIR 2 DIR | 21 3<br>BRN<br>2 REL  | 31 5<br>CBEQ<br>3 DIR | 41 4<br>CBEQA<br>3 IMM | 51 4<br>CBEQX<br>3 IMM | 61 5<br>CBEQ<br>3 IX1+ | 71 5<br>CBEQ<br>2 IX+ | 81 6<br>RTS<br>1 INH   | 91 3<br>BLT<br>2 REL  | A1 2<br>CMP<br>2 IMM | CMP<br>2 DIR         | CMP<br>3 EXT         | D1 4<br>CMP<br>3 IX2 | E1 3<br>CMP<br>2 IX1 | F1 3<br>CMP<br>1 IX |

| 02 5 12 5<br>BRSET1 BSET1<br>3 DIR 2 DIR | 22 3<br>BHI<br>2 REL  | 32 5<br>LDHX<br>3 EXT | 42 5<br>MUL<br>1 INH   | 52 6<br>DIV<br>1 INH   | 62 1<br>NSA<br>1 INH   | 72 1<br>DAA<br>1 INH  | 82 5+<br>BGND<br>1 INH | 92 3<br>BGT<br>2 REL  | A2 2<br>SBC<br>2 IMM | B2 3<br>SBC<br>2 DIR | SBC<br>3 EXT         | D2 4<br>SBC<br>3 IX2 | SBC 2 IX1            | F2 3<br>SBC<br>1 IX |

| 03 5 13 5<br>BRCLR1 BCLR1<br>3 DIR 2 DIR | 23 3<br>BLS<br>2 REL  | 33 5<br>COM<br>2 DIR  | 43 1<br>COMA<br>1 INH  | 53 1<br>COMX<br>1 INH  | 63 5<br>COM<br>2 IX1   | 73 4<br>COM<br>1 IX   | 83 11<br>SWI<br>1 INH  | 93 3<br>BLE<br>2 REL  | A3 2<br>CPX<br>2 IMM | CPX<br>2 DIR         | C3 4<br>CPX<br>3 EXT | D3 4<br>CPX<br>3 IX2 | E3 3<br>CPX<br>2 IX1 | F3 3<br>CPX<br>1 IX |

| 04 5 14 5<br>BRSET2 BSET2<br>3 DIR 2 DIR | 24 3<br>BCC<br>2 REL  | 34 5<br>LSR<br>2 DIR  | 44 1<br>LSRA<br>1 INH  | 54 1<br>LSRX<br>1 INH  | 64 5<br>LSR<br>2 IX1   | LSR<br>1 IX           | 84 1<br>TAP<br>1 INH   | 94 2<br>TXS<br>1 INH  | AND<br>2 IMM         | B4 3<br>AND<br>2 DIR | AND<br>3 EXT         | D4 4<br>AND<br>3 IX2 | E4 3<br>AND<br>2 IX1 | F4 3<br>AND<br>1 IX |

| 05 5 15 5<br>BRCLR2 BCLR2<br>3 DIR 2 DIR | 25 3<br>BCS<br>2 REL  | 35 4<br>STHX<br>2 DIR | 45 3<br>LDHX<br>3 IMM  | 55 4<br>LDHX<br>2 DIR  | 65 3<br>CPHX<br>3 IMM  | 75 5<br>CPHX<br>2 DIR | 85 1<br>TPA<br>1 INH   | 95 2<br>TSX<br>1 INH  | A5 2<br>BIT<br>2 IMM | B5 3<br>BIT<br>2 DIR | C5 4<br>BIT<br>3 EXT | D5 4<br>BIT<br>3 IX2 | E5 3<br>BIT<br>2 IX1 | F5 3<br>BIT<br>1 IX |

| 06 5 16 5<br>BRSET3 BSET3<br>3 DIR 2 DIR | 26 3<br>BNE<br>2 REL  | 36 5<br>ROR<br>2 DIR  | 46 1<br>RORA<br>1 INH  | 56 1<br>RORX<br>1 INH  | 66 5<br>ROR<br>2 IX1   | 76 4<br>ROR<br>1 IX   | 86 3<br>PULA<br>1 INH  | 96 5<br>STHX<br>3 EXT | A6 2<br>LDA<br>2 IMM | LDA<br>2 DIR         | LDA<br>3 EXT         | D6 4<br>LDA<br>3 IX2 | LDA<br>2 IX1         | F6 3<br>LDA<br>1 IX |

| 07 5 17 5<br>BRCLR3 BCLR3<br>3 DIR 2 DIR | 27 3<br>BEQ<br>2 REL  | 37 5<br>ASR<br>2 DIR  | 47 1<br>ASRA<br>1 INH  | 57 1<br>ASRX<br>1 INH  | 67 5<br>ASR<br>2 IX1   | 77 4<br>ASR<br>1 IX   | 87 2<br>PSHA<br>1 INH  | 97 1<br>TAX<br>1 INH  | A7 2<br>AIS<br>2 IMM | B7 3<br>STA<br>2 DIR | C7 4<br>STA<br>3 EXT | D7 4<br>STA<br>3 IX2 | E7 3<br>STA<br>2 IX1 | F7 2<br>STA<br>1 IX |

| 08 5 18 5<br>BRSET4 BSET4<br>3 DIR 2 DIR | 28 3<br>BHCC<br>2 REL | 38 5<br>LSL<br>2 DIR  | 48 1<br>LSLA<br>1 INH  | 58 1<br>LSLX<br>1 INH  | 68 5<br>LSL<br>2 IX1   | 78 4<br>LSL<br>1 IX   | 88 3<br>PULX<br>1 INH  | 98 1<br>CLC<br>1 INH  | A8 2<br>EOR<br>2 IMM | B8 3<br>EOR<br>2 DIR | C8 4<br>EOR<br>3 EXT | D8 4<br>EOR<br>3 IX2 | E8 3<br>EOR<br>2 IX1 | F8 3<br>EOR<br>1 IX |

| 09 5 19 5<br>BRCLR4 BCLR4<br>3 DIR 2 DIR | 29 3<br>BHCS<br>2 REL | 39 5<br>ROL<br>2 DIR  | 49 1<br>ROLA<br>1 INH  | 59 1<br>ROLX<br>1 INH  | 69 5<br>ROL<br>2 IX1   | 79 4<br>ROL<br>1 IX   | 89 2<br>PSHX<br>1 INH  | 99 1<br>SEC<br>1 INH  | A9 2<br>ADC<br>2 IMM | B9 3<br>ADC<br>2 DIR | C9 4<br>ADC<br>3 EXT | D9 4<br>ADC<br>3 IX2 | E9 3<br>ADC<br>2 IX1 | F9 3<br>ADC<br>1 IX |

| 0A 5 1A 5<br>BRSET5 BSET5<br>3 DIR 2 DIR | 2A 3<br>BPL<br>2 REL  | 3A 5<br>DEC<br>2 DIR  | 4A 1<br>DECA<br>1 INH  | 5A 1<br>DECX<br>1 INH  | 6A 5<br>DEC<br>2 IX1   | 7A 4<br>DEC<br>1 IX   | 8A 3<br>PULH<br>1 INH  | 9A 1<br>CLI<br>1 INH  |                      | BA 3<br>ORA<br>2 DIR | CA 4<br>ORA<br>3 EXT | DA 4<br>ORA<br>3 IX2 | EA 3<br>ORA<br>2 IX1 | FA 3<br>ORA<br>1 IX |

| 0B 5 1B 5 BCLR5 3 DIR 2 DIR              | 2B 3<br>BMI<br>2 REL  | 3B 7<br>DBNZ<br>3 DIR | 4B 4<br>DBNZA<br>2 INH | 5B 4<br>DBNZX<br>2 INH | 6B 7<br>DBNZ<br>3 IX1  | 7B 6<br>DBNZ<br>2 IX  | 8B 2<br>PSHH<br>1 INH  | 9B 1<br>SEI<br>1 INH  | ADD                  | BB 3<br>ADD<br>2 DIR | CB 4<br>ADD<br>3 EXT | DB 4<br>ADD<br>3 IX2 | EB 3<br>ADD<br>2 IX1 | FB 3<br>ADD<br>1 IX |

| 0C 5 1C 5<br>BRSET6 BSET6<br>3 DIR 2 DIR | 2C 3<br>BMC<br>2 REL  | 3C 5<br>INC<br>2 DIR  | 4C 1<br>INCA<br>1 INH  | 5C 1<br>INCX<br>1 INH  | 6C 5<br>INC<br>2 IX1   | 7C 4<br>INC<br>1 IX   | 8C 1<br>CLRH<br>1 INH  | 9C 1<br>RSP<br>1 INH  |                      | BC 3<br>JMP<br>2 DIR | CC 4<br>JMP<br>3 EXT | DC 4<br>JMP<br>3 IX2 | EC 3<br>JMP<br>2 IX1 | FC 3<br>JMP<br>1 IX |

| 0D 5 1D 5<br>BRCLR6 BCLR6<br>3 DIR 2 DIR | 2D 3<br>BMS<br>2 REL  | 3D 4<br>TST<br>2 DIR  | 4D 1<br>TSTA<br>1 INH  | 5D 1<br>TSTX<br>1 INH  | 6D 4<br>TST<br>2 IX1   | 7D 3<br>TST<br>1 IX   |                        | 9D 1<br>NOP<br>1 INH  | BSR<br>2 REL         | BD 5<br>JSR<br>2 DIR | CD 6<br>JSR<br>3 EXT | DD 6<br>JSR<br>3 IX2 | ED 5<br>JSR<br>2 IX1 | FD 5<br>JSR<br>1 IX |

| 0E 5 1E 5<br>BRSET7 BSET7<br>3 DIR 2 DIR | 2E 3<br>BIL<br>2 REL  | 3E 6<br>CPHX<br>3 EXT | 4E 5<br>MOV<br>3 DD    | 5E 5<br>MOV<br>2 DIX+  | 6E 4<br>MOV<br>3 IMD   | 7E 5<br>MOV<br>2 IX+D | 8E 2+<br>STOP<br>1 INH | 9E<br>Page 2          | AE 2<br>LDX<br>2 IMM | BE 3<br>LDX<br>2 DIR | CE 4<br>LDX<br>3 EXT | DE 4<br>LDX<br>3 IX2 | EE 3<br>LDX<br>2 IX1 | FE 3<br>LDX<br>1 IX |

| 0F 5 1F 5<br>BRCLR7 BCLR7<br>3 DIR 2 DIR | 2F 3<br>BIH<br>2 REL  | 3F 5<br>CLR<br>2 DIR  | 4F 1<br>CLRA<br>1 INH  | 5F 1<br>CLRX<br>1 INH  | 6F 5<br>CLR<br>2 IX1   | 7F 4<br>CLR<br>1 IX   | 8F 2+<br>WAIT<br>1 INH | 9F 1<br>TXA<br>1 INH  | AF 2<br>AIX<br>2 IMM | BF 3<br>STX<br>2 DIR | CF 4<br>STX<br>3 EXT | DF 4<br>STX<br>3 IX2 | EF 3<br>STX<br>2 IX1 | FF 2<br>STX<br>1 IX |

INH IMM DIR EXT DD IX+D Inherent Immediate Direct Extended DIR to DIR IX+ to DIR REL IX IX1 IX2 IMD DIX+ Relative Indexed, No Offset Indexed, 8-Bit Offset Indexed, 16-Bit Offset IMM to DIR DIR to IX+

Stack Pointer, 8-Bit Offset Stack Pointer, 16-Bit Offset Indexed, No Offset with Post Increment Indexed, 1-Byte Offset with Post Increment SP1 SP2 IX+ IX1+

Opcode in Hexadecimal SUB Instruction Mnemonic Addressing Mode

### Central Processor Unit (S08CPUV2)

Table 8-3. Opcode Map (Sheet 2 of 2)

| Bit-Manipulation | Branch | Read-Modify-Write |  |                                   |  |  | Control Register/Memory |                        |                         |                         |                                         |                        |                         |

|------------------|--------|-------------------|--|-----------------------------------|--|--|-------------------------|------------------------|-------------------------|-------------------------|-----------------------------------------|------------------------|-------------------------|

|                  |        |                   |  | 9E60 6<br>NEG<br>3 SP1            |  |  |                         |                        |                         |                         | 9ED0 5<br>SUB<br>4 SP2                  | 9EE0 4<br>SUB<br>3 SP1 |                         |

|                  |        |                   |  | 9E61 6<br>CBEQ<br>4 SP1           |  |  |                         |                        |                         |                         | 9ED1 5<br>CMP<br>4 SP2                  | 9EE1 4<br>CMP<br>3 SP1 |                         |

|                  |        |                   |  |                                   |  |  |                         |                        |                         |                         | 9ED2 5<br>SBC<br>4 SP2                  | 3 SP1                  |                         |

|                  |        |                   |  | 9E63 6<br>COM<br>3 SP1            |  |  |                         |                        |                         |                         | 9ED3 5<br>CPX<br>4 SP2<br>9ED4 5<br>AND | 9EE3 4<br>CPX<br>3 SP1 | 9EF3 6<br>CPHX<br>3 SP1 |

|                  |        |                   |  | 9E64 6<br>LSR<br>3 SP1            |  |  |                         |                        |                         |                         | 4 SP2                                   | 3 SP1                  |                         |

|                  |        |                   |  |                                   |  |  |                         |                        |                         |                         | 9ED5 5<br>BIT<br>4 SP2                  | BIT<br>3 SP1           |                         |

|                  |        |                   |  | 9E66 6<br>ROR<br>3 SP1            |  |  |                         |                        |                         |                         | 9ED6 5<br>LDA<br>4 SP2                  | LDA<br>3 SP1           |                         |

|                  |        |                   |  | 9E67 6<br>ASR<br>3 SP1<br>9E68 6  |  |  |                         |                        |                         |                         | 9ED7 5<br>STA<br>4 SP2                  | SΤΔ                    |                         |

|                  |        |                   |  | LSL<br>3 SP1                      |  |  |                         |                        |                         |                         | 4 SP2<br>9ED8 5<br>EOR<br>4 SP2         | 9EE8 4<br>EOR<br>3 SP1 |                         |

|                  |        |                   |  | 9E69 6<br>ROL<br>3 SP1            |  |  |                         |                        |                         |                         | 9ED9 5<br>ADC<br>4 SP2                  | 9EE9 4<br>ADC<br>3 SP1 |                         |

|                  |        |                   |  | 9E6A 6<br>DEC<br>3 SP1            |  |  |                         |                        |                         |                         | 9EDA 5<br>ORA<br>4 SP2                  | ORA<br>3 SP1           |                         |

|                  |        |                   |  | 9E6B 8<br>DBNZ<br>4 SP1<br>9E6C 6 |  |  |                         |                        |                         |                         | 9EDB 5<br>ADD<br>4 SP2                  | ADD                    |                         |

|                  |        |                   |  | INC<br>3 SP1                      |  |  |                         |                        |                         |                         |                                         |                        |                         |

|                  |        |                   |  | 9E6D 5<br>TST<br>3 SP1            |  |  |                         |                        |                         |                         |                                         |                        |                         |

|                  |        |                   |  |                                   |  |  |                         | 9EAE 5<br>LDHX<br>2 IX | 9EBE 6<br>LDHX<br>4 IX2 | 9ECE 5<br>LDHX<br>3 IX1 | 9EDE 5<br>LDX<br>4 SP2<br>9EDF 5        | 9EEE 4<br>LDX<br>3 SP1 | 9EFE 5<br>LDHX<br>3 SP1 |

|                  |        |                   |  | 9E6F 6<br>CLR<br>3 SP1            |  |  |                         |                        |                         |                         | 9EDF 5<br>STX<br>4 SP2                  | STX                    | I STHX I                |

| INH       | Inherent               | REL        | Relative                             | SP1  | Stack Pointer, 8-Bit Offset                  |

|-----------|------------------------|------------|--------------------------------------|------|----------------------------------------------|

| IMM       | Immediate              | IX         | Indexed, No Offset                   | SP2  | Stack Pointer, 16-Bit Offset                 |

| DIR       | Direct                 | IX1        | Indexed, 8-Bit Offset                | IX+  | Indexed, No Offset with                      |

| EXT       | Extended               | IX2        | Indexed, 16-Bit Offset               |      | Post Increment                               |

| DD        | DIR to DIR             | IMD        | IMM to DIR                           | IX1+ | Indexed, 1-Byte Offset with                  |

| IX+D      | IX+ to DIR             | DIX+       | DIR to IX+                           |      | Post Increment                               |

| EXT<br>DD | Extended<br>DIR to DIR | IX2<br>IMD | Indexed, 16-Bit Offset<br>IMM to DIR |      | Post Increment<br>Indexed, 1-Byte Offset wit |

Note: All Sheet 2 Opcodes are Preceded by the Page 2 Prebyte (9E)

| Prebyte (9E) and Opcode in |      |   | _                    |

|----------------------------|------|---|----------------------|

| Hexadecimal                | 9E60 | 6 | HCS08 Cycles         |

|                            | NEG  |   | Instruction Mnemonic |

| Number of Bytes            | 3 SF | 1 | Addressing Mode      |

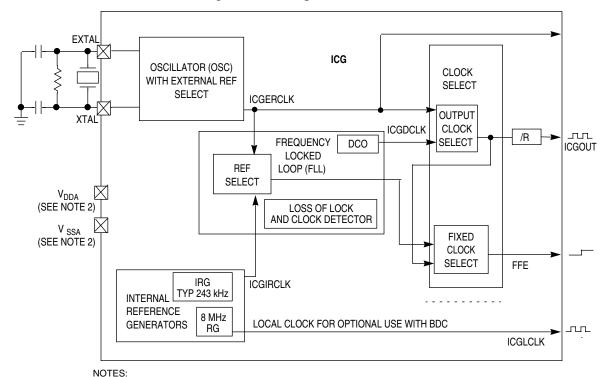

The ICG provides multiple options for clock sources. This offers a user great flexibility when making choices between cost, precision, current draw, and performance. The ICG consists of four functional blocks. Each of these is briefly described here and then in more detail in a later section.

- Oscillator block The oscillator block provides means for connecting an external crystal or

resonator. Two frequency ranges are software selectable to allow optimal startup and stability.

Alternatively, the oscillator block can be used to route an external square wave to the system clock.

External sources can provide a very precise clock source. The oscillator is capable of being

configured for low power mode or high amplitude mode as selected by HGO.

- Internal reference generator The internal reference generator consists of two controlled clock sources. One is designed to be approximately 8 MHz and can be selected as a local clock for the background debug controller. The other internal reference clock source is typically 243 kHz and can be trimmed for finer accuracy via software when a precise timed event is input to the MCU. This provides a highly reliable, low-cost clock source.

- Frequency-locked loop A frequency-locked loop (FLL) stage takes either the internal or external clock source and multiplies it to a higher frequency. Status bits provide information when the circuit has achieved lock and when it falls out of lock. Additionally, this block can monitor the external reference clock and signals whether the clock is valid or not.

- Clock select block The clock select block provides several switch options for connecting different clock sources to the system clock tree. ICGDCLK is the multiplied clock frequency out of the FLL, ICGERCLK is the reference clock frequency from the crystal or external clock source, and FFE (fixed frequency enable) is a control signal used to control the system fixed frequency clock (XCLK). ICGLCLK is the clock source for the background debug controller (BDC).

### 9.1.1 Features

The module is intended to be very user friendly with many of the features occurring automatically without user intervention. To quickly configure the module, go to Section 9.5, "Initialization/Application Information" and pick an example that best suits the application needs.

Features of the ICG and clock distribution system:

- Several options for the primary clock source allow a wide range of cost, frequency, and precision choices:

- 32 kHz–100 kHz crystal or resonator

- 1 MHz–16 MHz crystal or resonator

- External clock

- Internal reference generator

- Defaults to self-clocked mode to minimize startup delays

- Frequency-locked loop (FLL) generates 8 MHz to 40 MHz (for bus rates up to 20 MHz)

- Uses external or internal clock as reference frequency

- Automatic lockout of non-running clock sources

- Reset or interrupt on loss of clock or loss of FLL lock

### 9.1.3 Block Diagram

Figure 9-3 is a top-level diagram that shows the functional organization of the internal clock generation (ICG) module. This section includes a general description and a feature list.

See chip level clock routing diagram for specific use of ICGOUT, FFE, ICGLCLK, ICGERCLK

Not all HCS08 microcontrollers have unique supply pins for the ICG. See the device pin assignments.

Figure 9-3. ICG Block Diagram

# 9.2 External Signal Description

The oscillator pins are used to provide an external clock source for the MCU. The oscillator pins are gain controlled in low-power mode (default). Oscillator amplitudes in low-power mode are limited to approximately 1 V, peak-to-peak.

# 9.2.1 EXTAL — External Reference Clock / Oscillator Input

If upon the first write to ICGC1, either the FEE mode or FBE mode is selected, this pin functions as either the external clock input or the input of the oscillator circuit as determined by REFS. If upon the first write to ICGC1, either the FEI mode or SCM mode is selected, this pin is not used by the ICG.

# 9.2.2 XTAL — Oscillator Output

If upon the first write to ICGC1, either the FEE mode or FBE mode is selected, this pin functions as the output of the oscillator circuit. If upon the first write to ICGC1, either the FEI mode or SCM mode is

MC9S08GT16A/GT8A Data Sheet, Rev. 1

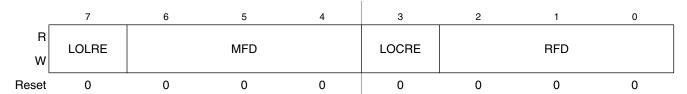

# 9.3.2 ICG Control Register 2 (ICGC2)

Figure 9-7. ICG Control Register 2 (ICGC2)

**Table 9-2. ICGC2 Register Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOLRE | Loss of Lock Reset Enable — The LOLRE bit determines what type of request is made by the ICG following a loss of lock indication. The LOLRE bit only has an effect when LOLS is set.  O Generate an interrupt request on loss of lock.  1 Generate a reset request on loss of lock.                                                                                                                                                                                                                                                                                                                                                              |

| 6:4<br>MFD | Multiplication Factor — The MFD bits control the programmable multiplication factor in the FLL loop. The value specified by the MFD bits establishes the multiplication factor (N) applied to the reference frequency. Writes to the MFD bits will not take effect if a previous write is not complete. Select a low enough value for N such that f <sub>ICGDCLK</sub> does not exceed its maximum specified value.  000 Multiplication factor = 4  001 Multiplication factor = 6  010 Multiplication factor = 8  011 Multiplication factor = 10  100 Multiplication factor = 12  101 Multiplication factor = 14  110 Multiplication factor = 18 |

| 3<br>LOCRE | Loss of Clock Reset Enable — The LOCRE bit determines how the system manages a loss of clock condition.  O Generate an interrupt request on loss of clock.  Generate a reset request on loss of clock.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2:0<br>RFD | Reduced Frequency Divider — The RFD bits control the value of the divider following the clock select circuitry. The value specified by the RFD bits establishes the division factor (R) applied to the selected output clock source. Writes to the RFD bits will not take effect if a previous write is not complete.  000 Division factor = 1 001 Division factor = 2 010 Division factor = 4 011 Division factor = 8 100 Division factor = 16 101 Division factor = 32 110 Division factor = 64 111 Division factor = 128                                                                                                                      |

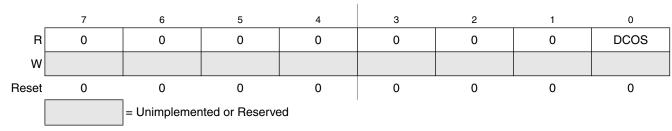

# 9.3.4 ICG Status Register 2 (ICGS2)

Figure 9-9. ICG Status Register 2 (ICGS2)

**Table 9-4. ICGS2 Register Field Descriptions**

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>DCOS | DCO Clock Stable — The DCOS bit is set when the DCO clock (ICG2DCLK) is stable, meaning the count error has not changed by more than n <sub>unlock</sub> for two consecutive samples and the DCO clock is not static. This bit is used when exiting off state if CLKS = X1 to determine when to switch to the requested clock mode. It is also used in self-clocked mode to determine when to start monitoring the DCO clock. This bit is cleared upon entering the off state.  0 DCO clock is unstable.  1 DCO clock is stable. |

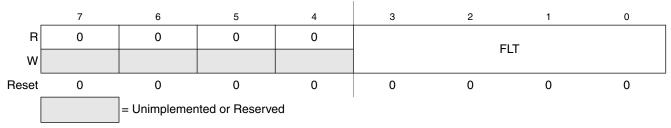

# 9.3.5 ICG Filter Registers (ICGFLTU, ICGFLTL)

Figure 9-10. ICG Upper Filter Register (ICGFLTU)

**Table 9-5. ICGFLTU Register Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3:0<br>FLT | <b>Filter Value</b> — The FLT bits indicate the current filter value, which controls the DCO frequency. The FLT bits are read only except when the CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. |  |  |  |

Internal Clock Generator (S08ICGV4)

### 9.4.7.1 FLL Engaged External Unlocked

FEE unlocked is entered when FEE is entered and the count error ( $\Delta n$ ) output from the subtractor is greater than the maximum  $n_{unlock}$  or less than the minimum  $n_{unlock}$ , as required by the lock detector to detect the unlock condition.

The ICG will remain in this state while the count error ( $\Delta n$ ) is greater than the maximum  $n_{lock}$  or less than the minimum  $n_{lock}$ , as required by the lock detector to detect the lock condition.

In this state, the pulse counter, subtractor, digital loop filter, and DCO form a closed loop and attempt to lock it according to their operational descriptions later in this section. Upon entering this state and until the FLL becomes locked, the output clock signal ICGOUT frequency is given by  $f_{ICGDCLK}$  / (2×R) This extra divide by two prevents frequency overshoots during the initial locking process from exceeding chip-level maximum frequency specifications. After the FLL has locked, if an unexpected loss of lock causes it to re-enter the unlocked state while the ICG remains in FEE mode, the output clock signal ICGOUT frequency is given by  $f_{ICGDCLK}$  / R.

### 9.4.7.2 FLL Engaged External Locked

FEE locked is entered from FEE unlocked when the count error ( $\Delta n$ ) is less than  $n_{lock}$  (max) and greater than  $n_{lock}$  (min) for a given number of samples, as required by the lock detector to detect the lock condition. The output clock signal ICGOUT frequency is given by  $f_{ICGDCLK}/R$ . In FLL engaged external locked, the filter value is updated only once every four comparison cycles. The update made is an average of the error measurements taken in the four previous comparisons.

### 9.4.8 FLL Lock and Loss-of-Lock Detection

To determine the FLL locked and loss-of-lock conditions, the pulse counter counts the pulses of the DCO for one comparison cycle (see Table 9-9 for explanation of a comparison cycle) and passes this number to the subtractor. The subtractor compares this value to the value in MFD and produces a count error,  $\Delta n$ . To achieve locked status,  $\Delta n$  must be between  $n_{lock}$  (min) and  $n_{lock}$  (max). After the FLL has locked,  $\Delta n$  must stay between  $n_{unlock}$  (min) and  $n_{unlock}$  (max) to remain locked. If  $\Delta n$  goes outside this range unexpectedly, the LOLS status bit is set and remains set until cleared by software or until the MCU is reset. LOLS is cleared by reading ICGS1 then writing 1 to ICGIF (LOLRE = 0), or by a loss-of-lock induced reset (LOLRE = 1), or by any MCU reset.

If the ICG enters the off state due to stop mode when ENBDM = OSCSTEN = 0, the FLL loses locked status (LOCK is cleared), but LOLS remains unchanged because this is not an unexpected loss-of-lock condition. Though it would be unusual, if ENBDM is cleared to 0 while the MCU is in stop, the ICG enters the off state. Because this is an unexpected stopping of clocks, LOLS will be set when the MCU wakes up from stop.

Expected loss of lock occurs when the MFD or CLKS bits are changed or in FEI mode only, when the TRIM bits are changed. In these cases, the LOCK bit will be cleared until the FLL regains lock, but the LOLS will not be set.

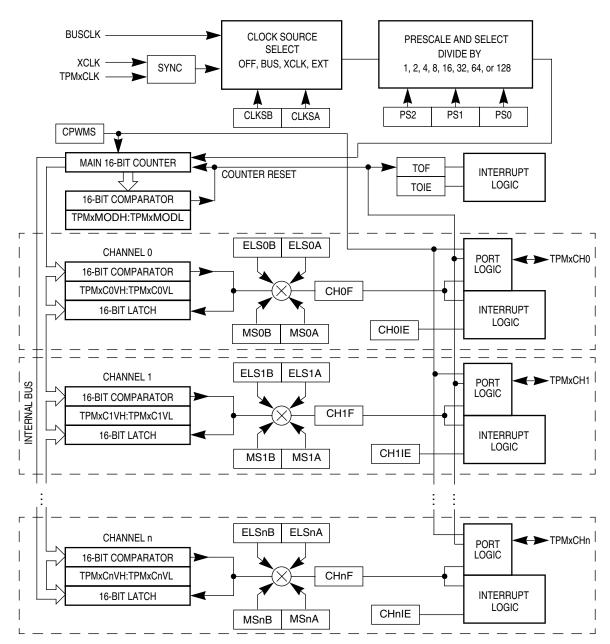

#### Timer/Pulse-Width Modulator (S08TPMV2)

Figure 10-2. TPM Block Diagram

The central component of the TPM is the 16-bit counter that can operate as a free-running counter, a modulo counter, or an up-/down-counter when the TPM is configured for center-aligned PWM. The TPM counter (when operating in normal up-counting mode) provides the timing reference for the input capture, output compare, and edge-aligned PWM functions. The timer counter modulo registers, TPMxMODH:TPMxMODL, control the modulo value of the counter. (The values 0x0000 or 0xFFFF

TPMxMODH:TPMxMODL, control the modulo value of the counter. (The values 0x0000 or 0xFFFF effectively make the counter free running.) Software can read the counter value at any time without affecting the counting sequence. Any write to either byte of the TPMxCNT counter resets the counter regardless of the data value written.

MC9S08GT16A/GT8A Data Sheet, Rev. 1

has one full character time after RDRF is set before the data in the receive data buffer must be read to avoid a receiver overrun.

When a program detects that the receive data register is full (RDRF = 1), it gets the data from the receive data register by reading SCIxD. The RDRF flag is cleared automatically by a 2-step sequence which is normally satisfied in the course of the user's program that handles receive data. Refer to Section 11.3.4, "Interrupts and Status Flags," for more details about flag clearing.

### 11.3.3.1 Data Sampling Technique

The SCI receiver uses a 16× baud rate clock for sampling. The receiver starts by taking logic level samples at 16 times the baud rate to search for a falling edge on the RxD1 serial data input pin. A falling edge is defined as a logic 0 sample after three consecutive logic 1 samples. The 16× baud rate clock is used to divide the bit time into 16 segments labeled RT1 through RT16. When a falling edge is located, three more samples are taken at RT3, RT5, and RT7 to make sure this was a real start bit and not merely noise. If at least two of these three samples are 0, the receiver assumes it is synchronized to a receive character.

The receiver then samples each bit time, including the start and stop bits, at RT8, RT9, and RT10 to determine the logic level for that bit. The logic level is interpreted to be that of the majority of the samples taken during the bit time. In the case of the start bit, the bit is assumed to be 0 if at least two of the samples at RT3, RT5, and RT7 are 0 even if one or all of the samples taken at RT8, RT9, and RT10 are 1s. If any sample in any bit time (including the start and stop bits) in a character frame fails to agree with the logic level for that bit, the noise flag (NF) will be set when the received character is transferred to the receive data buffer.

The falling edge detection logic continuously looks for falling edges, and if an edge is detected, the sample clock is resynchronized to bit times. This improves the reliability of the receiver in the presence of noise or mismatched baud rates. It does not improve worst case analysis because some characters do not have any extra falling edges anywhere in the character frame.

In the case of a framing error, provided the received character was not a break character, the sampling logic that searches for a falling edge is filled with three logic 1 samples so that a new start bit can be detected almost immediately.

In the case of a framing error, the receiver is inhibited from receiving any new characters until the framing error flag is cleared. The receive shift register continues to function, but a complete character cannot transfer to the receive data buffer if FE is still set.

# 11.3.3.2 Receiver Wakeup Operation

Receiver wakeup is a hardware mechanism that allows an SCI receiver to ignore the characters in a message that is intended for a different SCI receiver. In such a system, all receivers evaluate the first character(s) of each message, and as soon as they determine the message is intended for a different receiver, they write logic 1 to the receiver wake up (RWU) control bit in SCIxC2. When RWU = 1, it inhibits setting of the status flags associated with the receiver, thus eliminating the software overhead for handling the unimportant message characters. At the end of a message, or at the beginning of the next message, all receivers automatically force RWU to 0 so all receivers wake up in time to look at the first character(s) of the next message.

Inter-Integrated Circuit (S08IICV1)

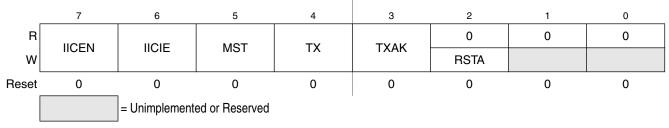

# 13.3.3 IIC Control Register (IICC)

Figure 13-5. IIC Control Register (IICC)

**Table 13-4. IICC Register Field Descriptions**

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7<br>IICEN | IIC Enable — The IICEN bit determines whether the IIC module is enabled.  0 IIC is not enabled.  1 IIC is enabled.                                                                                                                                                                                                                                                           |  |  |  |

| 6<br>IICIE | IIC Interrupt Enable — The IICIE bit determines whether an IIC interrupt is requested.  0 IIC interrupt request not enabled.  1 IIC interrupt request enabled.                                                                                                                                                                                                               |  |  |  |

| 5<br>MST   | Master Mode Select — The MST bit is changed from a 0 to a 1 when a START signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a STOP signal is generated and the mode of operation changes from master to slave.  0 Slave Mode.  1 Master Mode.                                                                                 |  |  |  |

| 4<br>TX    | Transmit Mode Select — The TX bit selects the direction of master and slave transfers. In master mode this bit should be set according to the type of transfer required. Therefore, for address cycles, this bit will always be high. When addressed as a slave this bit should be set by software according to the SRW bit in the status register.  O Receive.  1 Transmit. |  |  |  |

| 3<br>TXAK  | Transmit Acknowledge Enable — This bit specifies the value driven onto the SDA during data acknowledge cycles for both master and slave receivers.  O An acknowledge signal will be sent out to the bus after receiving one data byte.  1 No acknowledge signal response is sent.                                                                                            |  |  |  |

| 2<br>RSTA  | <b>Repeat START</b> — Writing a one to this bit will generate a repeated START condition provided it is the current master. This bit will always be read as a low. Attempting a repeat at the wrong time will result in loss of arbitration.                                                                                                                                 |  |  |  |

### 14.5 Resets

The ATD module is reset on system reset. If the system reset signal is activated, the ATD registers are initialized back to their reset state and the ATD module is powered down. This occurs as a function of the register file initialization; the reset definition of the ATDPU bit (power down bit) is zero or disabled.

The MCU places the module back into an initialized state. If the module is performing a conversion, the current conversion is terminated, the conversion complete flag is cleared, and the SAR register bits are cleared. Any pending interrupts are also cancelled. Note that the control, test, and status registers are initialized on reset; the initialized register state is defined in the register description section of this specification.

Enabling the module (using the ATDPU bit) does not cause the module to reset since the register file is not initialized. Finally, writing to control register ATDC does not cause the module to reset; the current conversion will be terminated.

# 14.6 Interrupts

The ATD module originates interrupt requests and the MCU handles or services these requests. Details on how the ATD interrupt requests are handled can be found in the resets and interrupts chapter of this data sheet.

The ATD interrupt function is enabled by setting the ATDIE bit in the ATDSC register. When the ATDIE bit is set, an interrupt is generated at the end of an ATD conversion and the ATD result registers (ATDRH and ATDRL) contain the result data generated by the conversion. If the interrupt function is disabled (ATDIE = 0), then the CCF flag must be polled to determine when a conversion is complete.

The interrupt will remain pending as long as the CCF flag is set. The CCF bit is cleared whenever the ATD status and control (ATDSC) register is written. The CCF bit is also cleared whenever the ATD result registers (ATDRH or ATDRL) are read.

Interrupt

Local Enable

Description

CCF

ATDIE

Conversion complete

**Table 14-8. Interrupt Summary**

|       | _     |            |        |            |

|-------|-------|------------|--------|------------|

| Tabla | V _ 2 | Thormal    | Chara  | cteristics |

| Iable | A-0.  | HILEHIIIAI | Cilaia | CIGHOUS    |

| Rating                                 | Symbol                          | Value                                          | Unit |

|----------------------------------------|---------------------------------|------------------------------------------------|------|

| Operating temperature range (packaged) | T <sub>A</sub>                  | T <sub>L</sub> to T <sub>H</sub><br>-40 to 125 | °C   |

| Thermal resistance 1s board type       |                                 |                                                |      |

| 48-pin QFN                             |                                 | 84                                             |      |

| 44-pin QFP                             | θ <sub>JA</sub> <sup>1, 2</sup> | 72                                             | °C/W |

| 42-pin SDIP                            |                                 | 62                                             |      |

| 32-pin QFN                             |                                 | 99                                             |      |

| Thermal resistance 2s2p board type     |                                 |                                                |      |

| 48-pin QFN                             |                                 | 26                                             |      |

| 44-pin QFP                             | $\theta_{JA}^{1,2}$             | 54                                             | °C/W |

| 42-pin SDIP                            |                                 | 51                                             |      |

| 32-pin QFN                             |                                 | 33                                             |      |

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

The average chip-junction temperature (T<sub>J</sub>) in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. A-1

where:

$T_A = Ambient temperature, °C$

$\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W

$$P_D = P_{int} + P_{I/O}$$

$P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

$P_{I/O}$  = Power dissipation on input and output pins — user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_D = K \div (T_J + 273^{\circ}C)$$

Eqn. A-2

Solving equations 1 and 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2$$

Eqn. A-3

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

#### MC9S08GT16A/GT8A Data Sheet, Rev. 1

Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal. Single layer board is designed per JEDEC JESD51-3.

### NOTES:

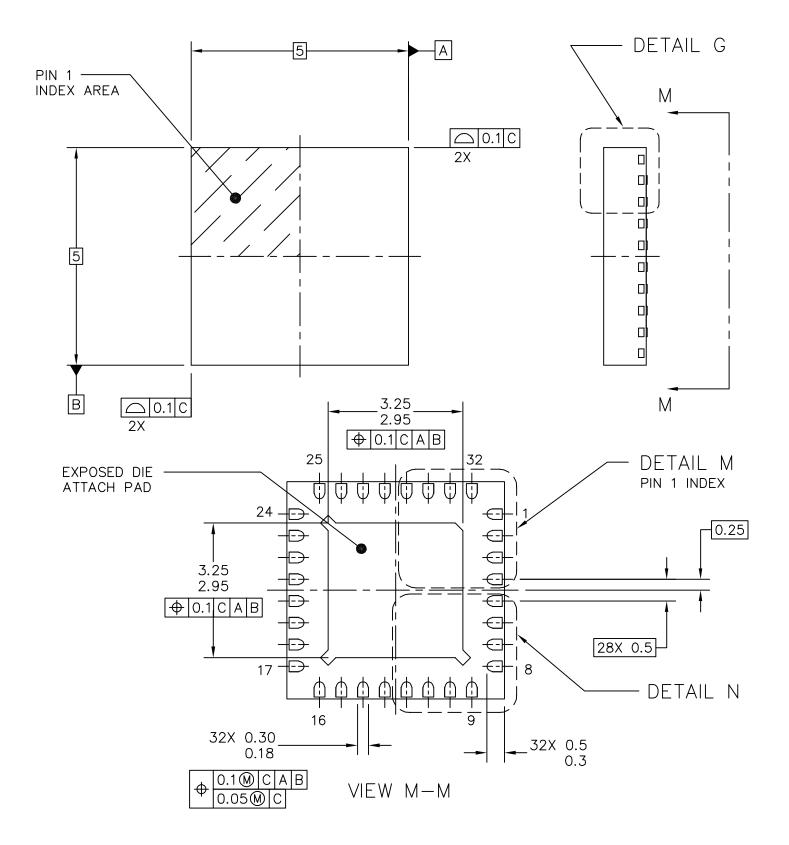

- 1. DIMENSIONS AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DATUMPLANE —H— IS LOCATED AT BOTTOM OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE BOTTOM OF THE PARTING LINE.

- 4. DATUMS A-B AND -D- TO BE DETERMINED AT DATUM PLANE -H-.

THIS DIMENSION DO NOT INCLUDE MOLD PROTRUSION, ALLOWABLE PROTRUSION IS 0.25 PER SIDE, DIMENSIONS A AND B DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE —H—.

THIS DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSTION, ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | CHANICAL OUTLINE | PRINT VERSION NO | OT TO SCALE |

|------------------------------------------------------|------------------|------------------|-------------|

| TITLE:                                               | DOCUMENT NO      | O: 98ASB42839B   | REV: B      |

| 44LD QFP,<br>10X10X2.0 PKG, 0.8 PITCH                | CASE NUMBER      | R: 824A-01       | 06 APR 2005 |

| 10/10//2: 0 11/0, 0: 0 11/                           | STANDARD: NO     | ON-JEDEC         |             |

| FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                              | MECHANICA | AL OUTLINE   | PRINT VERSION NO  | T TO SCALE  |

|-----------------------------------------------------------------------------------------------------------------|-----------|--------------|-------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD  FLAT NON-LEADED PACKAGE (QFN)  32 TERMINAL, 0.5 PITCH (5 X 5 X 1)  CASE OUTLINE |           | DOCUMENT NO  | ): 98ARH99035A    | REV: J      |

|                                                                                                                 |           | CASE NUMBER  | 2: 1311–06        | 17 MAR 2006 |

|                                                                                                                 |           | STANDARD: JE | DEC-MO-220 VHHD-2 | 2           |