Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S08                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 16KB (16K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-QFP                                                                  |

| Supplier Device Package    | 44-QFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08gt16acfbe |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

**Section Number**

Page

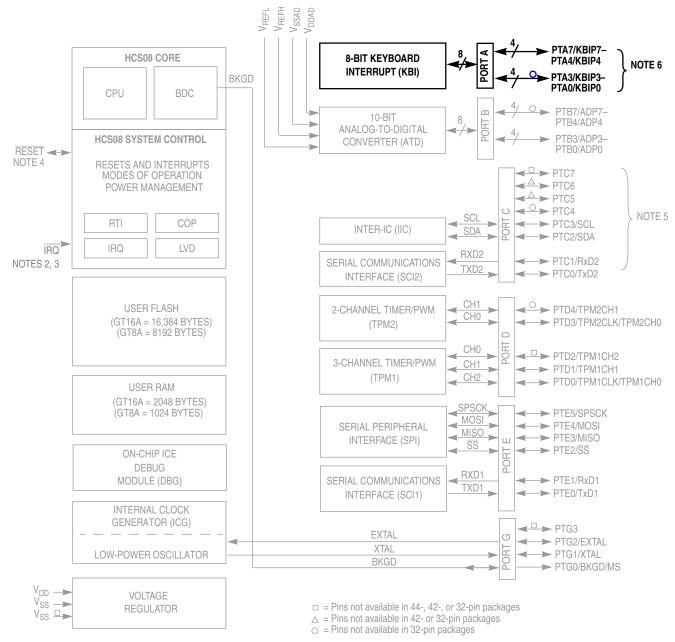

## Chapter 1 Device Overview

| 1.1 | Introdu | ction                                  | 19 |

|-----|---------|----------------------------------------|----|

|     | 1.1.1   | Devices in the MC9S08GT16A/GT8A Series | 19 |

|     | 1.1.2   | MCU Block Diagram                      | 19 |

| 1.2 | System  | Clock Distribution                     | 21 |

### Chapter 2 Pins and Connections

| 2.1 | Introdu | ction                                                                                                                                            | 23 |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Device  | Pin Assignment                                                                                                                                   | 23 |

| 2.3 | Recom   | nended System Connections                                                                                                                        | 27 |

|     | 2.3.1   | V <sub>DD</sub> , V <sub>SS</sub> , V <sub>DDAD</sub> , V <sub>SSAD</sub> , V <sub>REFH</sub> , V <sub>REFL</sub> — Power and Voltage References | 28 |

|     |         | PTG1/XTAL, PTG2/EXTAL — Oscillator                                                                                                               |    |

|     | 2.3.3   | RESET — External Reset Pin                                                                                                                       | 29 |

|     | 2.3.4   | PTG0/BKGD/MS — Background / Mode Select                                                                                                          | 29 |

|     | 2.3.5   | IRQ — External Interrupt Request Pin                                                                                                             | 30 |

|     | 2.3.6   | General-Purpose I/O and Peripheral Ports                                                                                                         | 30 |

|     | 2.3.7   | Signal Properties Summary                                                                                                                        | 31 |

|     |         |                                                                                                                                                  |    |

# Chapter 3 Modes of Operation

| 3.1 | Introdu  | ction                                    |    |

|-----|----------|------------------------------------------|----|

|     | 3.1.1    | Features                                 |    |

| 3.2 | Run Mo   | ode                                      |    |

| 3.3 | Active 1 | Background Mode                          |    |

| 3.4 | Wait M   | ode                                      | 34 |

| 3.5 | Stop M   | odes                                     | 35 |

|     | 3.5.1    | Stop1 Mode                               | 35 |

|     | 3.5.2    | Stop2 Mode                               | 35 |

|     | 3.5.3    | Stop3 Mode                               |    |

|     | 3.5.4    | Active BDM Enabled in Stop Mode          |    |

|     | 3.5.5    | LVD Enabled in Stop Mode                 |    |

|     | 3.5.6    | On-Chip Peripheral Modules in Stop Modes |    |

|     |          |                                          |    |

MC9S08GT16A/GT8A Data Sheet, Rev. 1

## **Section Number**

### Title

### Page

| 15.4.3.2 | Debug Comparator A Low Register (DBGCAL)  |  |

|----------|-------------------------------------------|--|

| 15.4.3.3 | Debug Comparator B High Register (DBGCBH) |  |

| 15.4.3.4 | Debug Comparator B Low Register (DBGCBL)  |  |

| 15.4.3.5 | Debug FIFO High Register (DBGFH)          |  |

| 15.4.3.6 | Debug FIFO Low Register (DBGFL)           |  |

| 15.4.3.7 | Debug Control Register (DBGC)             |  |

|          | Debug Trigger Register (DBGT)             |  |

| 15.4.3.9 | Debug Status Register (DBGS)              |  |

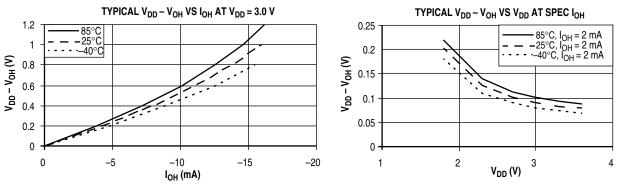

## Appendix A Electrical Characteristics

| Introduction                                             |                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter Classification                                 |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Absolute Maximum Ratings                                 |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Thermal Characteristics                                  |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Electrostatic Discharge (ESD) Protection Characteristics |                                                                                                                                                                                                                                                                                                                                                                                                      |

| DC Characteristics                                       |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Supply Current Characteristics                           |                                                                                                                                                                                                                                                                                                                                                                                                      |

| ATD Characteristics                                      |                                                                                                                                                                                                                                                                                                                                                                                                      |

| Internal Clock Generation Module Characteristics         |                                                                                                                                                                                                                                                                                                                                                                                                      |

| A.9.1 ICG Frequency Specifications                       |                                                                                                                                                                                                                                                                                                                                                                                                      |

| AC Characteristics                                       |                                                                                                                                                                                                                                                                                                                                                                                                      |

| A.10.1 Control Timing                                    |                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                          |                                                                                                                                                                                                                                                                                                                                                                                                      |

| A.10.3 SPI Timing                                        |                                                                                                                                                                                                                                                                                                                                                                                                      |

| FLASH Specifications                                     |                                                                                                                                                                                                                                                                                                                                                                                                      |

| )                                                        | Absolute Maximum Ratings<br>Thermal Characteristics<br>Electrostatic Discharge (ESD) Protection Characteristics<br>DC Characteristics<br>Supply Current Characteristics<br>ATD Characteristics<br>Internal Clock Generation Module Characteristics<br>A.9.1 ICG Frequency Specifications<br>AC Characteristics<br>A.10.1 Control Timing<br>A.10.2 Timer/PWM (TPM) Module Timing<br>A.10.3 SPI Timing |

# Appendix B

# **Ordering Information and Mechanical Drawings**

| <b>B</b> .1 | Ordering Information          | 285 |

|-------------|-------------------------------|-----|

|             | B.1.1 Device Numbering Scheme | 285 |

| <b>B</b> .2 | Mechanical Drawings           |     |

Memory

## 4.1.1 Reset and Interrupt Vector Assignments

Table 4-1 shows address assignments for reset and interrupt vectors. The vector names shown in this table are the labels used in the Freescale-provided equate file for the MC9S08GT16A/GT8A. For more details about resets, interrupts, interrupt priority, and local interrupt mask controls, refer to Chapter 5, "Resets, Interrupts, and System Configuration."

| Address<br>(High/Low) | Vector                                              | Vector Name |

|-----------------------|-----------------------------------------------------|-------------|

| 0xFFC0:FFC1           |                                                     |             |

| \$                    | Unused Vector Space<br>(available for user program) |             |

| 0xFFCA:FFCB           |                                                     |             |

| 0xFFCC:FFCD           | RTI                                                 | Vrti        |

| 0xFFCE:FFCF           | IIC                                                 | Viic        |

| 0xFFD0:FFD1           | ATD Conversion                                      | Vatd        |

| 0xFFD2:FFD3           | Keyboard                                            | Vkeyboard   |

| 0xFFD4:FFD5           | SCI2 Transmit                                       | Vsci2tx     |

| 0xFFD6:FFD7           | SCI2 Receive                                        | Vsci2rx     |

| 0xFFD8:FFD9           | SCI2 Error                                          | Vsci2err    |

| 0xFFDA:FFDB           | SCI1 Transmit                                       | Vsci1tx     |

| 0xFFDC:FFDD           | SCI1 Receive                                        | Vsci1rx     |

| 0xFFDE:FFDF           | SCI1 Error                                          | Vsci1err    |

| 0xFFE0:FFE1           | SPI                                                 | Vspi        |

| 0xFFE2:FFE3           | TPM2 Overflow                                       | Vtpm2ovf    |

| 0xFFE4:FFE9           | Unused Vector Space (available for user program)    |             |

| 0xFFEA:FFEB           | TPM2 Channel 1                                      | Vtpm2ch1    |

| 0xFFEC:FFED           | TPM2 Channel 0                                      | Vtpm2ch0    |

| 0xFFEE:FFEF           | TPM1 Overflow                                       | Vtpm1ovf    |

| 0xFFF0:FFF1           | TPM1 Channel 2                                      | Vtpm1ch2    |

| 0xFFF2:FFF3           | TPM1 Channel 1                                      | Vtpm1ch1    |

| 0xFFF4:FFF5           | TPM1 Channel 0                                      | Vtpm1ch0    |

| 0xFFF6:FFF7           | ICG                                                 | Vicg        |

| 0xFFF8:FFF9           | Low Voltage Detect                                  | Vlvd        |

| 0xFFFA:FFFB           | IRQ                                                 | Virq        |

| 0xFFFC:FFFD           | SWI                                                 | Vswi        |

| 0xFFFE:FFFF           | Reset                                               | Vreset      |

### Table 4-1. Reset and Interrupt Vectors

NVPROT) must be programmed to logic 0 to enable block protection. Therefore the value 0xDE must be programmed into NVPROT to protect addresses 0xE000 through 0xFFFF.

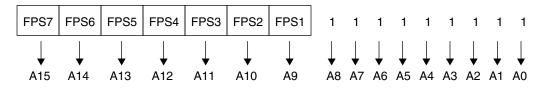

### Figure 4-4. Block Protection Mechanism

One use for block protection is to block protect an area of FLASH memory for a bootloader program. This bootloader program then can be used to erase the rest of the FLASH memory and reprogram it. Because the bootloader is protected, it remains intact even if MCU power is lost in the middle of an erase and reprogram operation.

## 4.4.7 Vector Redirection

Whenever any block protection is enabled, the reset and interrupt vectors will be protected. Vector redirection allows users to modify interrupt vector information without unprotecting bootloader and reset vector space. Vector redirection is enabled by programming the FNORED bit in the NVOPT register located at address 0xFFBF to zero. For redirection to occur, at least some portion but not all of the FLASH memory must be block protected by programming the NVPROT register located at address 0xFFBD. All of the interrupt vectors (memory locations 0xFFC0–0xFFFD) are redirected, while the reset vector (0xFFFE:FFFF) is not.

For example, if 512 bytes of FLASH are protected, the protected address region is from 0xFE00 through 0xFFFF. The interrupt vectors (0xFFC0–0xFFFD) are redirected to the locations 0xFDC0–0xFDFD. Now, if an SPI interrupt is taken for instance, the values in the locations 0xFDE0:FDE1 are used for the vector instead of the values in the locations 0xFFE0:FFE1. This allows the user to reprogram the unprotected portion of the FLASH with new program code including new interrupt vector values while leaving the protected area, which includes the default vector locations, unchanged.

# 4.5 Security

The MC9S08GT16A/GT8A includes circuitry to prevent unauthorized access to the contents of FLASH and RAM memory. When security is engaged, FLASH and RAM are considered secure resources. Direct-page registers, high-page registers, and the background debug controller are considered unsecured resources. Programs executing within secure memory have normal access to any MCU memory locations and resources. Attempts to access a secure memory location with a program executing from an unsecured memory space or through the background debug interface are blocked (writes are ignored and reads return all 0s).

Security is engaged or disengaged based on the state of two nonvolatile register bits (SEC01:SEC00) in the FOPT register. During reset, the contents of the nonvolatile location NVOPT are copied from FLASH into the working FOPT register in high-page register space. A user engages security by programming the NVOPT location which can be done at the same time the FLASH memory is programmed. The 1:0 state disengages security while the other three combinations engage security. Notice the erased state (1:1)

#### Resets, Interrupts, and System Configuration

- Computer operating properly (COP) watchdog timer

- Illegal opcode detect

- Illegal address detect

- Background debug forced reset

- The reset pin ( $\overline{\text{RESET}}$ )

- Clock generator loss of lock and loss of clock reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the internal clock generator (ICG) module switches to self-clocked mode with the frequency of  $f_{Self\_reset}$  selected. The reset pin is driven low for 34 internal bus cycles where the internal bus frequency is half the ICG frequency. After the 34 cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.3 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP timer periodically. If the application program gets lost and fails to reset the COP before it times out, a system reset is generated to force the system back to a known starting point. The COP watchdog is enabled by the COPE bit in SOPT (see Section 5.7.4, "System Options Register (SOPT)" for additional information). The COP timer is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP timer.

After any reset, the COP timer is enabled. This provides a reliable way to detect code that is not executing as intended. If the COP watchdog is not used in an application, it can be disabled by clearing the COPE bit in the write-once SOPT register. Also, the COPT bit can be used to choose one of two timeout periods (2<sup>18</sup> or 2<sup>13</sup> cycles of the bus rate clock). Even if the application will use the reset default settings in COPE and COPT, the user should still write to write-once SOPT during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost.

The write to SRS that services (clears) the COP timer should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

When the MCU is in active background mode, the COP timer is temporarily disabled.

# 5.4 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

| Vector<br>Priority                      | Vector<br>Number    | Address<br>(High/Low)                 | Vector Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Module            | Source                                    | Enable                  | Description                                                            |               |

|-----------------------------------------|---------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------|-------------------------|------------------------------------------------------------------------|---------------|

| Lower                                   | 26<br>through<br>31 | 0xFFC0/FFC1<br>through<br>0xFFCA/FFCB |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                           |                         |                                                                        |               |

| <b>≜</b>                                | 25                  | 0xFFCC/FFCD                           | Vrti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | System<br>control | RTIF                                      | RTIE                    | Real-time interrupt                                                    |               |

|                                         | 24                  | 0xFFCE/FFCF                           | Viic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IIC               | licis                                     | IICIE                   | IIC control                                                            |               |

|                                         | 23                  | 0xFFD0/FFD1                           | Vatd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ATD               | COCO                                      | AIEN                    | AD conversion<br>complete                                              |               |

|                                         | 22                  | 0xFFD2/FFD3                           | DescriptionConstrainedUnused Vector Space<br>(available for user program)2DVrtiSystem<br>controlRTIFRTIE2DVrtiSystem<br>controlRTIFRTIE2FViicIICIICISIICIE2FViicIICIICISIICIE2FViicIICIICISIICIE2FViicIICIICISIICIE2FViicIICIICISIICIE2FViicIICIICISIICIE2FVsci2txSCI2TDRETIE2FVsci2txSCI2IDLEIILIE2FVsci2rxSCI2ORORIE2FVsci2errSCI2ORORIE2FVsci1txSCI1TDRETIE2FVsci1txSCI1IDLEIILIE2FVsci1rxSCI1IDLEIILIE2FVsci1errSCI1ORORIE2FVsci1errSCI1ORORIE2FVspiSPISPIFSPIE3Vtpm2ovfTPM2TOFTOIE3Vtpm2ch1TPM2CH1FCH1IE2FVtpm1ovfTPM1TOFTOIE1Vtpm1ch2TPM1CH2FCH2IE3Vtpm1ch1TPM1CH1FCH1IE |                   | Vkeyboard KBI KBF KBIE                    |                         |                                                                        | Keyboard pins |

|                                         | 21                  | 0xFFD4/FFD5                           | Vsci2tx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SCI2              |                                           |                         | SCI2 transmit                                                          |               |

|                                         | 20                  | 0xFFD6/FFD7                           | Vsci2rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SCI2              |                                           |                         | SCI2 receive                                                           |               |

| 190xFFD8/FFD9180xFFDA/FFDB170xFFDC/FFDD |                     | 0xFFD8/FFD9                           | Vsci2err                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SCI2              | NF<br>FE                                  | NFIE<br>FEIE            | SCI2 error                                                             |               |

|                                         |                     | Vsci1tx                               | SCI1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |                                           | SCI1 transmit           |                                                                        |               |

|                                         | 17                  | 0xFFDC/FFDD                           | Vsci1rx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SCI1              |                                           |                         | SCI1 receive                                                           |               |

|                                         | 16                  | 0xFFDE/FFDF                           | Vsci1err                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SCI1              | NF<br>FE                                  | NFIE<br>FEIE            | SCI1 error                                                             |               |

|                                         | 15                  | 0xFFE0/FFE1                           | Vspi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SPI               | MODF                                      | SPIE<br>SPIE            | SPI                                                                    |               |

|                                         | 14                  | 0xFFE2/FFE3                           | Vtpm2ovf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TPM2              | TOF                                       | TOIE                    | TPM2 overflow                                                          |               |

|                                         | 11<br>through<br>13 | 0xFFEC/FFED<br>through<br>0xFFE4/FFE5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                           |                         |                                                                        |               |

|                                         | 10                  | 0xFFEA/FFEB                           | Vtpm2ch1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TPM2              | CH1F                                      | CH1IE                   | TPM2 channel 1                                                         |               |

|                                         | 9                   | 0xFFEC/FFED                           | Vtpm2ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TPM2              | CH0F                                      | CH0IE                   | TPM2 channel 0                                                         |               |

|                                         | 8                   | 0xFFEE/FFEF                           | Vtpm1ovf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TPM1              | TOF                                       | TOIE                    | TPM1 overflow                                                          |               |

|                                         | 7                   | 0xFFF0/FFF1                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TPM1              | CH2F                                      | CH2IE                   | TPM1 channel 2                                                         |               |

|                                         | 6                   | 0xFFF2/FFF3                           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |                                           |                         | TPM1 channel 1                                                         |               |

|                                         | 5                   | 0xFFF4/FFF5                           | Vtpm1ch0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TPM1              | CH0F                                      | CH0IE                   | TPM1 channel 0                                                         |               |

|                                         | 4                   | 0xFFF6/FFF7                           | Vicg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ICG               | ICGIF<br>(LOLS/LOCS)                      | LOLRE/LOCRE             | ICG                                                                    |               |

|                                         | 3                   | 0xFFF8/FFF9                           | Vlvd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | System<br>control | LVDF                                      | LVDIE                   | Low-voltage detect                                                     |               |

|                                         | 2                   | 0xFFFA/FFFB                           | Virq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IRQ               | IRQF                                      | IRQIE                   | IRQ pin                                                                |               |

|                                         | 1                   | 0xFFFC/FFFD                           | Vswi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Core              | SWI<br>Instruction                        |                         | Software interrupt                                                     |               |

| <b>∀</b><br>Higher                      | 0                   | 0xFFFE/FFFF                           | Vreset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | System<br>control | COP<br>LVD<br>RESET pin<br>Illegal opcode | COPE<br>LVDRE<br>—<br>— | Watchdog timer<br>Low-voltage detect<br>External pin<br>Illegal opcode |               |

### Table 5-1. Vector Summary

MC9S08GT16A/GT8A Data Sheet, Rev. 1

1

Resets, Interrupts, and System Configuration

## 5.7.8 System Power Management Status and Control 2 Register (SPMSC2)

This register is used to report the status of the low voltage warning function, and to configure the stop mode behavior of the MCU.

|                     | 7                        | 6            | 5               | 4    | 3             | 2          | 1   | 0    |

|---------------------|--------------------------|--------------|-----------------|------|---------------|------------|-----|------|

| R                   | LVWF                     | 0            |                 | LVWV | PPDF          | 0          | PDC | PPDC |

| W                   |                          | LVWACK       | LVDV            |      |               | PPDACK     | FDC | FFDC |

| Power-on reset:     | 0<br>Note <sup>(1)</sup> | 0            | 0               | 0    | 0             | 0          | 0   | 0    |

| LVD reset:          | 0<br>Note <sup>(1)</sup> | 0            | U               | U    | 0             | 0          | 0   | 0    |

| Any other<br>reset: | 0<br>Note <sup>(1)</sup> | 0            | U               | U    | 0             | 0          | 0   | 0    |

|                     |                          | = Unimplemer | nted or Reserve | ed   | U = Unaffecte | d by reset |     |      |

LVWF will be set in the case when V<sub>Supply</sub> transitions below the trip point or after reset and V<sub>Supply</sub> is already below V<sub>LVW</sub>.

### Figure 5-10. System Power Management Status and Control 2 Register (SPMSC2)

| Field       | Description                                                                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVWF   | <ul> <li>Low-Voltage Warning Flag — The LVWF bit indicates the low voltage warning status.</li> <li>0 Low voltage warning not present.</li> <li>1 Low voltage warning is present or was present.</li> </ul>                                                                    |

| 6<br>LVWACK | <b>Low-Voltage Warning Acknowledge</b> — The LVWACK bit is the low-voltage warning acknowledge. Writing a 1 to LVWACK clears LVWF to 0 if a low voltage warning is not present.                                                                                                |

| 5<br>LVDV   | Low-Voltage Detect Voltage Select — The LVDV bit selects the LVD trip point voltage (V <sub>LVD</sub> ).         0 Low trip point selected (V <sub>LVD</sub> = V <sub>LVDL</sub> ).         1 High trip point selected (V <sub>LVD</sub> = V <sub>LVDH</sub> ).                |

| 4<br>LVWV   | <ul> <li>Low-Voltage Warning Voltage Select — The LVWV bit selects the LVW trip point voltage (V<sub>LVW</sub>).</li> <li>0 Low trip point selected (V<sub>LVW</sub> = V<sub>LVWL</sub>).</li> <li>1 High trip point selected (V<sub>LVW</sub> = V<sub>LVWH</sub>).</li> </ul> |

| 3<br>PPDF   | <ul> <li>Partial Power Down Flag — The PPDF bit indicates that the MCU has exited the stop2 mode.</li> <li>0 Not stop2 mode recovery.</li> <li>1 Stop2 mode recovery.</li> </ul>                                                                                               |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit.                                                                                                                                                                                                    |

| 1<br>PDC    | <ul> <li>Power Down Control — The write-once PDC bit controls entry into the power down (stop2 and stop1) modes.</li> <li>0 Power down modes are disabled.</li> <li>1 Power down modes are enabled.</li> </ul>                                                                 |

| 0<br>PPDC   | <ul> <li>Partial Power Down Control — The write-once PPDC bit controls which power down mode, stop1 or stop2, is selected.</li> <li>0 Stop1, full power down, mode enabled if PDC set.</li> <li>1 Stop2, partial power down, mode enabled if PDC set.</li> </ul>               |

### Table 5-11. SPMSC2 Field Descriptions

#### Parallel Input/Output

- Eight port B pins shared with ATD

- Eight high-current port C pins shared with SCI2 and IIC

- Five port D pins shared with TPM1 and TPM2

- Six port E pins shared with SCI1 and SPI

- Four port G pins shared with EXTAL, XTAL, and BKGD/MS

Keyboard Interrupt (S08KBIV1)

#### NOTES:

1. Port pins are software configurable with pullup device if input port.

- 2. Pin contains pullup/pulldown device if IRQ enabled (IRQPE = 1).

- 3. IRQ does not have a clamp diode to VDD. IRQ should not be driven above VDD.

- 4. Pin contains integrated pullup device.

5. High current drive

6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBIPn = 1).

#### Figure 7-2. Block Diagram Highlighting the KBI Module

MC9S08GT16A/GT8A Data Sheet, Rev. 1

- 0 = Bit forced to 0

- 1 = Bit forced to 1

- = Bit set or cleared according to results of operation

- U = Undefined after the operation

### Machine coding notation

- dd = Low-order 8 bits of a direct address 0x0000-0x00FF (high byte assumed to be 0x00)

- ee = Upper 8 bits of 16-bit offset

- ff = Lower 8 bits of 16-bit offset or 8-bit offset

- ii = One byte of immediate data

- jj = High-order byte of a 16-bit immediate data value

- kk = Low-order byte of a 16-bit immediate data value

- hh = High-order byte of 16-bit extended address

- II = Low-order byte of 16-bit extended address

- rr = Relative offset

### Source form

Everything in the source forms columns, *except expressions in italic characters*, is literal information that must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic is always a literal expression. All commas, pound signs (#), parentheses, and plus signs (+) are literal characters.

- n Any label or expression that evaluates to a single integer in the range 0–7

- opr8i Any label or expression that evaluates to an 8-bit immediate value

- opr16i Any label or expression that evaluates to a 16-bit immediate value

- *opr8a* Any label or expression that evaluates to an 8-bit value. The instruction treats this 8-bit value as the low order 8 bits of an address in the direct page of the 64-Kbyte address space (0x00xx).

- *opr16a* Any label or expression that evaluates to a 16-bit value. The instruction treats this value as an address in the 64-Kbyte address space.

- *oprx8* Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing

- *oprx16* Any label or expression that evaluates to a 16-bit value. Because the HCS08 has a 16-bit address bus, this can be either a signed or an unsigned value.

- rel Any label or expression that refers to an address that is within -128 to +127 locations from the next address after the last byte of object code for the current instruction. The assembler will calculate the 8-bit signed offset and include it in the object code for this instruction.

### Address modes

- INH = Inherent (no operands)

- IMM = 8-bit or 16-bit immediate

- DIR = 8-bit direct

- EXT = 16-bit extended

Central Processor Unit (S08CPUV2)

| Source                                                                                                           |                                             |                                                                                                                                                                                                                                                                                                     |    |   |   | ieci<br>CC |    |    | ess                                                                                                      | ep                                           | pue                                                                           | cles <sup>1</sup>               |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|---|------------|----|----|----------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------|---------------------------------|

| Form                                                                                                             | Operation                                   | Description                                                                                                                                                                                                                                                                                         | v  | н | I | N          | z  | с  | Address<br>Mode                                                                                          | Opcode                                       | Operand                                                                       | Bus Cycles <sup>1</sup>         |

| BRCLR n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory<br>Clear   | Branch if (Mn) = 0                                                                                                                                                                                                                                                                                  | _  | _ | _ | _          | _  | \$ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 03<br>05<br>07<br>09<br>0B<br>0D             | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr | 55555555555                     |

| BRN <i>rel</i>                                                                                                   | Branch Never                                | Uses 3 Bus Cycles                                                                                                                                                                                                                                                                                   | -  | - | - | -          | -  | -  | REL                                                                                                      | 21                                           |                                                                               | 3                               |

| BRSET n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory<br>Set     | Branch if (Mn) = 1                                                                                                                                                                                                                                                                                  | -  | _ | _ | -          | _  | \$ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 02<br>04<br>06<br>08<br>0A<br>0C             | dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr<br>dd rr          | 55555555                        |

| BSET <i>n,opr8a</i>                                                                                              | Set Bit <i>n</i> in Memory                  | Mn ← 1                                                                                                                                                                                                                                                                                              | _  | _ | _ | _          | _  | _  | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7)             | 10<br>12<br>14<br>16<br>18<br>1A<br>1C<br>1E | dd<br>dd<br>dd<br>dd<br>dd<br>dd                                              | 555555555555                    |

| BSR rel                                                                                                          | Branch to Subroutine                        | $\begin{array}{l} PC \leftarrow (PC) + 0x0002\\ push\ (PCL); SP \leftarrow (SP) - 0x0001\\ push\ (PCH); SP \leftarrow (SP) - 0x0001\\ PC \leftarrow (PC) + \mathit{rel} \end{array}$                                                                                                                | -  | - | - | -          | _  | _  | REL                                                                                                      | AD                                           | rr                                                                            | 5                               |

| CBEQ opr8a,rel<br>CBEQA #opr8i,rel<br>CBEQX #opr8i,rel<br>CBEQ oprx8,X+,rel<br>CBEQ ,X+,rel<br>CBEQ oprx8,SP,rel | Compare and Branch if<br>Equal              | Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(X) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$                                                                                                                                                  | _  | _ | _ | _          | _  | _  | DIR<br>IMM<br>IX1+<br>IX+<br>SP1                                                                         | 41<br>51<br>61                               | ii rr<br>ff rr<br>rr                                                          | 544556                          |

| CLC                                                                                                              | Clear Carry Bit                             | $C \leftarrow 0$                                                                                                                                                                                                                                                                                    | -  | - | - | -          | -  | 0  | INH                                                                                                      | 98                                           |                                                                               | 1                               |

| CLI                                                                                                              | Clear Interrupt Mask Bit                    | I ← 0                                                                                                                                                                                                                                                                                               | -  | - | 0 | -          | -  | -  | INH                                                                                                      | 9A                                           |                                                                               | 1                               |

| CLR opr8a<br>CLRA<br>CLRX<br>CLRH<br>CLR oprx8,X<br>CLR ,X<br>CLR oprx8,SP                                       | Clear                                       | $\begin{array}{l} M \leftarrow 0x00\\ A \leftarrow 0x00\\ X 0x00\\ H \leftarrow 0x00\\ H \leftarrow 0x00\\ M \leftarrow 0x00\\ M \leftarrow 0x00\\ M \leftarrow 0x00 \end{array}$                                                                                                                   | 0  | _ | - | 0          | 1  | _  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 3F<br>4F<br>5F<br>8C<br>6F<br>7F<br>9E6F     | ff                                                                            | 5<br>1<br>1<br>5<br>4<br>6      |

| CMP #opr8i<br>CMP opr8a<br>CMP opr16a<br>CMP oprx16,X<br>CMP oprx8,X<br>CMP ,X<br>CMP oprx16,SP<br>CMP oprx8,SP  | Compare Accumulator<br>with Memory          | (A) – (M)<br>(CCR Updated But Operands Not<br>Changed)                                                                                                                                                                                                                                              | \$ | _ | _ | \$         | \$ | \$ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1                                                      | D1                                           | dd<br>hh II<br>ee ff<br>ff<br>ee ff                                           | 2<br>3<br>4<br>3<br>3<br>5<br>4 |

| COM opr8a<br>COMA<br>COMX<br>COM oprx8,X<br>COM ,X<br>COM oprx8,SP                                               | Complement<br>(One's Complement)            | $\begin{array}{l} M \leftarrow (\overline{M}) = 0xFF - (M) \\ A \leftarrow (\overline{A}) = 0xFF - (A) \\ X \leftarrow (\overline{X}) = 0xFF - (X) \\ M \leftarrow (\overline{M}) = 0xFF - (M) \\ M \leftarrow (\overline{M}) = 0xFF - (M) \\ M \leftarrow (\overline{M}) = 0xFF - (M) \end{array}$ | 0  | _ | _ | \$         | \$ | 1  | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 43<br>53<br>63<br>73<br>9E63                 | ff                                                                            | 5<br>1<br>1<br>5<br>4<br>6      |

| CPHX opr16a<br>CPHX #opr16i<br>CPHX opr8a<br>CPHX oprx8,SP                                                       | Compare Index Register<br>(H:X) with Memory | (H:X) – (M:M + 0x0001)<br>(CCR Updated But Operands Not<br>Changed)                                                                                                                                                                                                                                 | \$ | _ | _ | \$         | \$ | \$ | EXT<br>IMM<br>DIR<br>SP1                                                                                 | 3E<br>65<br>75<br>9EF3                       | dd                                                                            | 6<br>3<br>5<br>6                |

| Table 8-2. HCS | 08 Instruction | Set Summary | (Sheet 3 of 7) |

|----------------|----------------|-------------|----------------|

|----------------|----------------|-------------|----------------|

#### Timer/Pulse-Width Modulator (S08TPMV2)

When center-aligned PWM operation is specified, the counter counts upward from 0x0000 through its terminal count and then counts downward to 0x0000 where it returns to up-counting. Both 0x0000 and the terminal count value (value in TPMxMODH:TPMxMODL) are normal length counts (one timer clock period long).

An interrupt flag and enable are associated with the main 16-bit counter. The timer overflow flag (TOF) is a software-accessible indication that the timer counter has overflowed. The enable signal selects between software polling (TOIE = 0) where no hardware interrupt is generated, or interrupt-driven operation (TOIE = 1) where a static hardware interrupt is automatically generated whenever the TOF flag is 1.

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the main 16-bit counter counts from 0x0000 through 0xFFFF and overflows to 0x0000 on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the main 16-bit counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction at the transition from the value set in the modulus register and the next lower count value. This corresponds to the end of a PWM period. (The 0x0000 count value corresponds to the center of a period.)

Because the HCS08 MCU is an 8-bit architecture, a coherency mechanism is built into the timer counter for read operations. Whenever either byte of the counter is read (TPMxCNTH or TPMxCNTL), both bytes are captured into a buffer so when the other byte is read, the value will represent the other byte of the count at the time the first byte was read. The counter continues to count normally, but no new value can be read from either byte until both bytes of the old count have been read.

The main timer counter can be reset manually at any time by writing any value to either byte of the timer count TPMxCNTH or TPMxCNTL. Resetting the counter in this manner also resets the coherency mechanism in case only one byte of the counter was read before resetting the count.

### 10.4.2 Channel Mode Selection

Provided CPWMS = 0 (center-aligned PWM operation is not specified), the MSnB and MSnA control bits in the channel n status and control registers determine the basic mode of operation for the corresponding channel. Choices include input capture, output compare, and buffered edge-aligned PWM.

### 10.4.2.1 Input Capture Mode

With the input capture function, the TPM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TPM latches the contents of the TPM counter into the channel value registers (TPMxCnVH:TPMxCnVL). Rising edges, falling edges, or any edge may be chosen as the active edge that triggers an input capture.

When either byte of the 16-bit capture register is read, both bytes are latched into a buffer to support coherent 16-bit accesses regardless of order. The coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An input capture event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

MC9S08GT16A/GT8A Data Sheet, Rev. 1

### 10.4.2.2 Output Compare Mode

With the output compare function, the TPM can generate timed pulses with programmable position, polarity, duration, and frequency. When the counter reaches the value in the channel value registers of an output compare channel, the TPM can set, clear, or toggle the channel pin.

In output compare mode, values are transferred to the corresponding timer channel value registers only after both 8-bit bytes of a 16-bit register have been written. This coherency sequence can be manually reset by writing to the channel status/control register (TPMxCnSC).

An output compare event sets a flag bit (CHnF) that can optionally generate a CPU interrupt request.

### 10.4.2.3 Edge-Aligned PWM Mode

This type of PWM output uses the normal up-counting mode of the timer counter (CPWMS = 0) and can be used when other channels in the same TPM are configured for input capture or output compare functions. The period of this PWM signal is determined by the setting in the modulus register (TPMxMODH:TPMxMODL). The duty cycle is determined by the setting in the timer channel value register (TPMxCnVH:TPMxCnVL). The polarity of this PWM signal is determined by the setting in the ELSnA control bit. Duty cycle cases of 0 percent and 100 percent are possible.

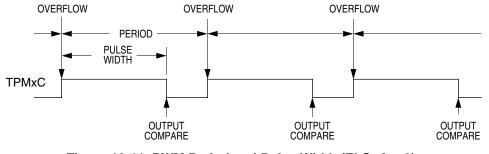

As Figure 10-11 shows, the output compare value in the TPM channel registers determines the pulse width (duty cycle) of the PWM signal. The time between the modulus overflow and the output compare is the pulse width. If ELSnA = 0, the counter overflow forces the PWM signal high and the output compare forces the PWM signal low. If ELSnA = 1, the counter overflow forces the PWM signal low and the output compare forces the PWM signal high.

Figure 10-11. PWM Period and Pulse Width (ELSnA = 0)

When the channel value register is set to 0x0000, the duty cycle is 0 percent. By setting the timer channel value register (TPMxCnVH:TPMxCnVL) to a value greater than the modulus setting, 100% duty cycle can be achieved. This implies that the modulus setting must be less than 0xFFFF to get 100% duty cycle.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to either register, TPMxCnVH or TPMxCnVL, write to buffer registers. In edge-PWM mode, values are transferred to the corresponding timer channel registers only after both 8-bit bytes of a 16-bit register have been written and the value in the TPMxCNTH:TPMxCNTL counter is 0x0000. (The new duty cycle does not take effect until the next full period.)

Timer/Pulse-Width Modulator (S08TPMV2)

## 10.5.3 Channel Event Interrupt Description

The meaning of channel interrupts depends on the current mode of the channel (input capture, output compare, edge-aligned PWM, or center-aligned PWM).

When a channel is configured as an input capture channel, the ELSnB:ELSnA control bits select rising edges, falling edges, any edge, or no edge (off) as the edge that triggers an input capture event. When the selected edge is detected, the interrupt flag is set. The flag is cleared by the 2-step sequence described in Section 10.5.1, "Clearing Timer Interrupt Flags."

When a channel is configured as an output compare channel, the interrupt flag is set each time the main timer counter matches the 16-bit value in the channel value register. The flag is cleared by the 2-step sequence described in Section 10.5.1, "Clearing Timer Interrupt Flags."

## 10.5.4 PWM End-of-Duty-Cycle Events

For channels that are configured for PWM operation, there are two possibilities:

- When the channel is configured for edge-aligned PWM, the channel flag is set when the timer counter matches the channel value register that marks the end of the active duty cycle period.

- When the channel is configured for center-aligned PWM, the timer count matches the channel value register twice during each PWM cycle. In this CPWM case, the channel flag is set at the start and at the end of the active duty cycle, which are the times when the timer counter matches the channel value register.

The flag is cleared by the 2-step sequence described in Section 10.5.1, "Clearing Timer Interrupt Flags."

# 12.3 Modes of Operation

### 12.3.1 SPI in Stop Modes

The SPI is disabled in all stop modes, regardless of the settings before executing the STOP instruction. During either stop1 or stop2 mode, the SPI module will be fully powered down. Upon wake-up from stop1 or stop2 mode, the SPI module will be in the reset state. During stop3 mode, clocks to the SPI module are halted. No registers are affected. If stop3 is exited with a reset, the SPI will be put into its reset state. If stop3 is exited with an interrupt, the SPI continues from the state it was in when stop3 was entered.

# 12.4 Register Definition

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

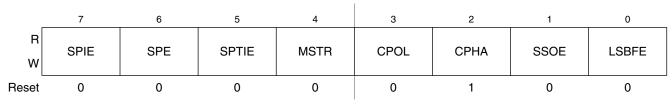

# 12.4.1 SPI Control Register 1 (SPIC1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 12-6. SPI Control Register 1 (SPIC1)

| Field      | Description                                                                                                                                                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable (for SPRF and MODF) — This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.</li> <li>Interrupts from SPRF and MODF inhibited (use polling)</li> <li>When SPRF or MODF is 1, request a hardware interrupt</li> </ul>  |

| 6<br>SPE   | <ul> <li>SPI System Enable — Disabling the SPI halts any transfer that is in progress and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.</li> <li>O SPI system inactive</li> <li>1 SPI system enabled</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).</li> <li>Interrupts from SPTEF inhibited (use polling)</li> <li>When SPTEF is 1, hardware interrupt requested</li> </ul>                                                  |

# Chapter 14 Analog-to-Digital Converter (S08ATDV3)

The MC9S08GT16A/GT8A provides one 8-channel analog-to-digital (ATD) module. The eight ATD channels share port B. Each channel individually can be configured for general-purpose I/O or for ATD functionality. All features of the ATD module as described in this section are available on the MC9S08GT16A/GT8A. Electrical parametric information for the ATD may be found in Appendix A, "Electrical Characteristics."

of how straight the line is (how far it deviates from a straight line). The adjusted ideal transition voltage is:

Adjusted Ideal Trans. V =

$$\frac{(\text{Current Code - 1/2})}{2^{N}} * ((V_{\text{REFH}} + E_{\text{FS}}) - (V_{\text{REFL}} + E_{\text{ZS}}))$$

• Zero scale error  $(E_{ZS})$  — This is the difference between the transition voltage to the first valid code and the ideal transition to that code. Normally, it is defined as the difference between the actual and ideal transition to code \$001, but in some cases the first transition may be to a higher code. The ideal transition to any code is:

#### Eqn. 14-7

Ideal Transition V =

$$\frac{(\text{Current Code - 1/2})}{2^{\text{N}}} * (\text{V}_{\text{REFH}} - \text{V}_{\text{REFL}})$$