Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | S08                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 40MHz                                                        |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                   |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 39                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 2K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 48-VFQFN Exposed Pad                                         |

| Supplier Device Package    | 48-QFN-EP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08gt16amfde |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

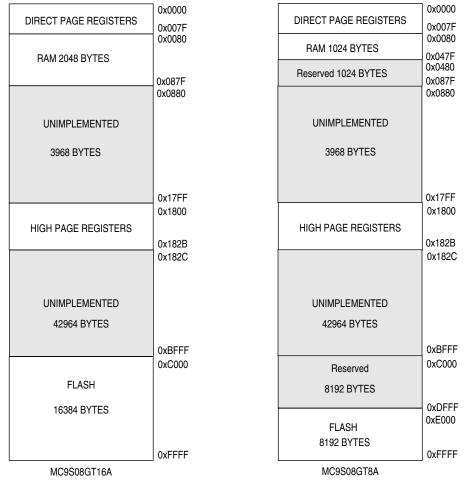

# Chapter 4 Memory

# 4.1 MC9S08GT16A/GT8A Memory Map

As shown in Figure 4-1, on-chip memory in the MC9S08GT16A/GT8A series of MCUs consists of RAM, FLASH program memory for nonvolatile data storage, plus I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (0x0000 through 0x007F)

- High-page registers (0x1800 through 0x182B)

- Nonvolatile registers (0xFFB0 through 0xFFBF)

Memory

| Address                            | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|------------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x00 <b>54</b>                     | ATDPE         | ATDPE7 | ATDPE6 | ATDPE5 | ATDPE4 | ATDPE3 | ATDPE2 | ATDPE1 | ATDPE0 |

| 0x00 <b>55</b> –<br>0x00 <b>57</b> | Reserved      | _      |        | _      | _      | —      | _      |        | _      |

| 0x00 <b>58</b>                     | IICA          |        |        |        | ADDR   |        |        |        | 0      |

| 0x00 <b>59</b>                     | licf          | MU     | JLT    |        |        | IC     | R      |        |        |

| 0x00 <b>5A</b>                     | IICC          | IICEN  | IICIE  | MST    | ΤX     | TXAK   | RSTA   | 0      | 0      |

| 0x00 <b>5B</b>                     | IICS          | TCF    | IAAS   | BUSY   | ARBL   | 0      | SRW    | IICIF  | RXAK   |

| 0x00 <b>5C</b>                     | licd          |        |        |        | DA     | TA     |        |        |        |

| 0x00 <b>5D</b> –<br>0x00 <b>5F</b> | Reserved      | _      | _      | _      | _      | _      | _      | _      | _      |

| 0x00 <b>60</b>                     | TPM2SC        | TOF    | TOIE   | CPWMS  | CLKSB  | CLKSA  | PS2    | PS1    | PS0    |

| 0x00 <b>61</b>                     | TPM2CNTH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>62</b>                     | TPM2CNTL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>63</b>                     | TPM2MODH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>64</b>                     | TPM2MODL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>65</b>                     | TPM2C0SC      | CH0F   | CH0IE  | MS0B   | MS0A   | ELS0B  | ELS0A  | 0      | 0      |

| 0x00 <b>66</b>                     | TPM2C0VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>67</b>                     | TPM2C0VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>68</b>                     | TPM2C1SC      | CH1F   | CH1IE  | MS1B   | MS1A   | ELS1B  | ELS1A  | 0      | 0      |

| 0x00 <b>69</b>                     | TPM2C1VH      | Bit 15 | 14     | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>6A</b>                     | TPM2C1VL      | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>6B</b> –<br>0x00 <b>7F</b> | Reserved      | —      | —      | —      |        | —      | —      | —      | —      |

Table 4-2. Direct-Page Register Summary (Sheet 3 of 3)

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

### Table 4-3. High-Page Register Summary

| Address            | Register Name | Bit 7  | 6      | 5       | 4     | 3     | 2      | 1      | Bit 0 |

|--------------------|---------------|--------|--------|---------|-------|-------|--------|--------|-------|

| 0x1800             | SRS           | POR    | PIN    | COP     | ILOP  | ILAD  | ICG    | LVD    | 0     |

| 0x1801             | SBDFR         | 0      | 0      | 0       | 0     | 0     | 0      | 0      | BDFR  |

| 0x1802             | SOPT          | COPE   | COPT   | STOPE   | —     | 0     | 0      | BKGDPE | _     |

| 0x1803 —<br>0x1805 | Reserved      | _      | _      | _       | _     | _     | _      | _      | _     |

| 0x1806             | SDIDH         |        |        |         |       | ID11  | ID10   | ID9    | ID8   |

| 0x1807             | SDIDL         | ID7    | ID6    | ID5     | ID4   | ID3   | ID2    | ID1    | ID0   |

| 0x1808             | SRTISC        | RTIF   | RTIACK | RTICLKS | RTIE  | 0     | RTIS2  | RTIS1  | RTIS0 |

| 0x1809             | SPMSC1        | LVDF   | LVDACK | LVDIE   | LVDRE | LVDSE | LVDE   | 0      | 0     |

| 0x180A             | SPMSC2        | LVWF   | LVWACK | LVDV    | LVWV  | PPDF  | PPDACK | PDC    | PPDC  |

| 0x180B–<br>0x180F  | Reserved      | _      | _      | _       | _     | _     | _      | _      | _     |

| 0x1810             | DBGCAH        | Bit 15 | 14     | 13      | 12    | 11    | 10     | 9      | Bit 8 |

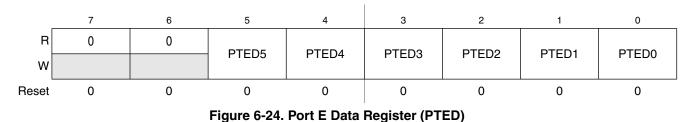

## 6.5.5 Port E Registers (PTED, PTEPE, PTESE, and PTEDD)

Port E includes six general-purpose I/O pins that share with the SCI1 and SPI modules. Port E pins used as general-purpose I/O pins are controlled by the port E data (PTED), data direction (PTEDD), pullup enable (PTEPE), and slew rate control (PTESE) registers.

If the SCI1 takes control of a port E pin, the corresponding PTEDD bit is ignored. PTESE can be used to provide slew rate on the SCI1 transmit pin, TxD1. PTEPE can be used, provided the corresponding PTEDD bit is 0, to provide a pullup device on the SCI1 receive pin, RxD1.

If the SPI takes control of a port E pin, the corresponding PTEDD bit is ignored. PTESE can be used to provide slew rate on the SPI serial output pin (MOSI or MISO) and serial clock pin (SPSCK) depending on the SPI operational mode. PTEPE can be used, provided the corresponding PTEDD bit is 0, to provide a pullup device on the SPI serial input pins (MOSI or MISO) and slave select pin ( $\overline{SS}$ ) depending on the SPI operational mode.

Reads of PTED will return the logic value of the corresponding pin, provided PTEDD is 0.

## Table 6-17. PTED Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:0<br>PTED[5:0] | Port E Data Register Bits — For port E pins that are inputs, reads return the logic level on the pin. For port E pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits in this register. For port E pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTED to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

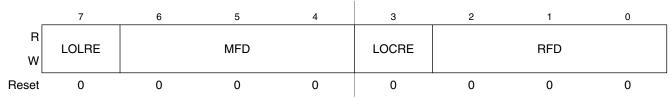

## 9.3.2 ICG Control Register 2 (ICGC2)

Figure 9-7. ICG Control Register 2 (ICGC2)

### Table 9-2. ICGC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOLRE | Loss of Lock Reset Enable — The LOLRE bit determines what type of request is made by the ICG following aloss of lock indication. The LOLRE bit only has an effect when LOLS is set.00Generate an interrupt request on loss of lock.11Generate a reset request on loss of lock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6:4<br>MFD | Multiplication Factor — The MFD bits control the programmable multiplication factor in the FLL loop. The value specified by the MFD bits establishes the multiplication factor (N) applied to the reference frequency. Writes to the MFD bits will not take effect if a previous write is not complete. Select a low enough value for N such that f <sub>ICGDCLK</sub> does not exceed its maximum specified value.         000       Multiplication factor = 4         001       Multiplication factor = 6         010       Multiplication factor = 8         011       Multiplication factor = 10         100       Multiplication factor = 12         101       Multiplication factor = 14         110       Multiplication factor = 16         111       Multiplication factor = 18 |

| 3<br>LOCRE | <ul> <li>Loss of Clock Reset Enable — The LOCRE bit determines how the system manages a loss of clock condition.</li> <li>Generate an interrupt request on loss of clock.</li> <li>Generate a reset request on loss of clock.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2:0<br>RFD | Reduced Frequency Divider — The RFD bits control the value of the divider following the clock select circuitry.         The value specified by the RFD bits establishes the division factor (R) applied to the selected output clock source.         Writes to the RFD bits will not take effect if a previous write is not complete.         000       Division factor = 1         001       Division factor = 2         010       Division factor = 4         011       Division factor = 8         100       Division factor = 32         110       Division factor = 64         111       Division factor = 128                                                                                                                                                                      |

## 9.4.10 Clock Mode Requirements

A clock mode is requested by writing to CLKS1:CLKS0 and the actual clock mode is indicated by CLKST1:CLKST0. Provided minimum conditions are met, the status shown in CLKST1:CLKST0 should be the same as the requested mode in CLKS1:CLKS0. Table 9-9 shows the relationship between CLKS, CLKST, and ICGOUT. It also shows the conditions for CLKS = CLKST or the reason CLKS  $\neq$  CLKST.

## NOTE

If a crystal will be used before the next reset, then be sure to set REFS = 1 and CLKS = 1x on the first write to the ICGC1 register. Failure to do so will result in "locking" REFS = 0 which will prevent the oscillator amplifier from being enabled until the next reset occurs.

| Actual<br>Mode<br>(CLKST) | Desired<br>Mode<br>(CLKS) | Range | Reference     Comparison       Frequency     Cycle Time       (f <sub>REFERENCE</sub> )     Cycle Time |                           | ICGOUT                   | Conditions <sup>1</sup> for<br>CLKS = CLKST | Reason<br>CLKS1 ≠<br>CLKST |

|---------------------------|---------------------------|-------|--------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|---------------------------------------------|----------------------------|

| Off                       | Off<br>(XX)               | х     | 0                                                                                                      | _                         | 0                        | _                                           | _                          |

| (XX)                      | FBE<br>(10)               | х     | 0                                                                                                      | _                         | 0                        | _                                           | ERCS = 0                   |

|                           | SCM<br>(00)               | x     | ficgirclk/7 <sup>2</sup>                                                                               | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | Not switching<br>from FBE to<br>SCM         | _                          |

| SCM<br>(00)               | FEI<br>(01)               | 0     | f <sub>ICGIRCLK</sub> /7 <sup>(1)</sup>                                                                | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | DCOS = 0                   |

| (00)                      | FBE<br>(10)               | x     | ficgirclk/7 <sup>(1)</sup>                                                                             | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | ERCS = 0                   |

|                           | FEE<br>(11)               | х     | ficgirclk/7 <sup>(1)</sup>                                                                             | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | _                                           | DCOS = 0 or<br>ERCS = 0    |

| FEI                       | FEI<br>(01)               | 0     | f <sub>ICGIRCLK</sub> /7                                                                               | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                | DCOS = 1                                    | —                          |

| (01)                      | FEE<br>(11)               | x     | f <sub>ICGIRCLK</sub> /7                                                                               | 8/f <sub>ICGIRCLK</sub>   | ICGDCLK/R                |                                             | ERCS = 0                   |

| FBE                       | FBE<br>(10)               | x     | 0                                                                                                      | _                         | ICGERCLK/R               | ERCS = 1                                    | —                          |

| (10)                      | FEE<br>(11)               | x     | 0                                                                                                      | _                         | ICGERCLK/R               | _                                           | LOCS = 1 &<br>ERCS = 1     |

| FEE                       |                           | 0     | ficgerclk                                                                                              | 2/f <sub>ICGERCLK</sub>   | ICGDCLK/R <sup>3</sup>   | ERCS = 1 and<br>DCOS = 1                    | _                          |

| (11)                      | (11)                      | 1     | ficgerclk                                                                                              | 128/f <sub>ICGERCLK</sub> | ICGDCLK/R <sup>(2)</sup> | ERCS = 1 and<br>DCOS = 1                    | _                          |

### Table 9-9. ICG State Table

<sup>1</sup> CLKST will not update immediately after a write to CLKS. Several bus cycles are required before CLKST updates to the new value.

<sup>2</sup> The reference frequency has no effect on ICGOUT in SCM, but the reference frequency is still used in making the comparisons that determine the DCOS bit

<sup>3</sup> After initial LOCK; will be ICGDCLK/2R during initial locking process and while FLL is re-locking after the MFD bits are changed.

#### Table 9-12. MFD and RFD Decode Table

| 101 | 14 | 101 | ÷32  |

|-----|----|-----|------|

| 110 | 16 | 110 | ÷64  |

| 111 | 18 | 111 | ÷128 |

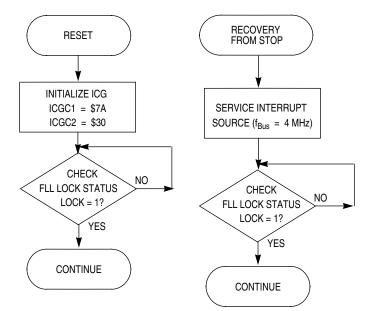

## 9.5.2 Example #1: External Crystal = 32 kHz, Bus Frequency = 4.19 MHz

In this example, the FLL will be used (in FEE mode) to multiply the external 32 kHz oscillator up to 8.38 MHz to achieve 4.19 MHz bus frequency.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately 8 MHz on ICGOUT, which corresponds to a 4 MHz bus frequency ( $f_{Bus}$ ).

The clock scheme will be FLL engaged, external (FEE). So

Solving for N / R gives:

| N / R = 8.38 MHz /(32 kHz * 64) = 4 ; we can choose N = 4 and R =1 | Eqn. 9-2 |

|--------------------------------------------------------------------|----------|

|--------------------------------------------------------------------|----------|

The values needed in each register to set up the desired operation are:

### ICGC1 = \$38 (%00111000)

| Bit 7    | HGO     | 0  | Configures oscillator for low power                                      |

|----------|---------|----|--------------------------------------------------------------------------|

| Bit 6    | RANGE   | 0  | Configures oscillator for low-frequency range; FLL prescale factor is 64 |

| Bit 5    | REFS    | 1  | Oscillator using crystal or resonator is requested                       |

| Bits 4:3 | CLKS    | 11 | FLL engaged, external reference clock mode                               |

| Bit 2    | OSCSTEN | 0  | Oscillator disabled                                                      |

| Bit 1    | LOCD    | 0  | Loss-of-clock detection enabled                                          |

| Bit 0    |         | 0  | Unimplemented or reserved, always reads zero                             |

### ICGC2 = \$00 (%0000000)

| Bit 7    | LOLRE | 0   | Generates an interrupt request on loss of lock  |

|----------|-------|-----|-------------------------------------------------|

| Bits 6:4 | MFD   | 000 | Sets the MFD multiplication factor to 4         |

| Bit 3    | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bits 2:0 | RFD   | 000 | Sets the RFD division factor to ÷1              |

### ICGS1 = \$xx

This is read only except for clearing interrupt flag

### ICGS2 = \$xx

This is read only; should read DCOS = 1 before performing any time critical tasks

### ICGFLTLU/L =\$xx

Only needed in self-clocked mode; FLT will be adjusted by loop to give 8.38 MHz DCO clock Bits 15:12 unused 0000

Figure 9-15. ICG Initialization and Stop Recovery for Example #2

## 10.1.2 Features

The TPM has the following features:

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock sources independently selectable per TPM (multiple TPMs device)

- Selectable clock sources (device dependent): bus clock, fixed system clock, external pin

- Clock prescaler taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus a terminal count interrupt for each TPM module (multiple TPMs device)

- Channel features:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

## 10.1.3 Block Diagram

Figure 10-2 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

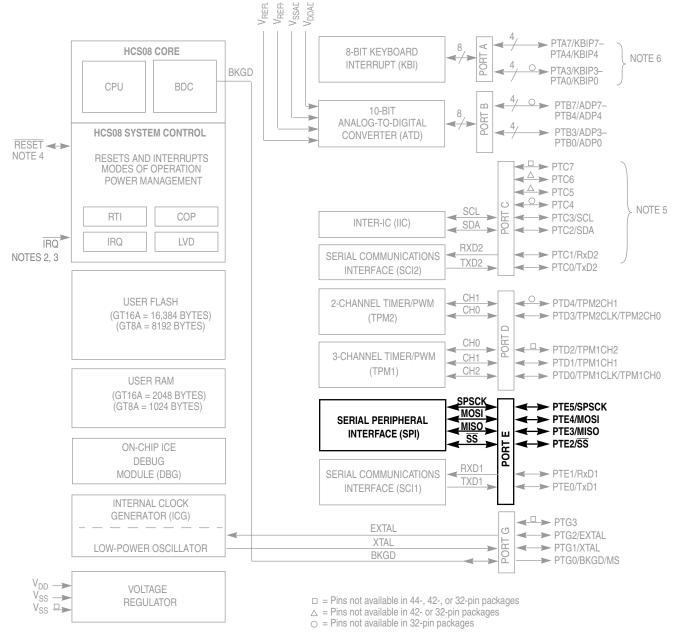

Serial Peripheral Interface (S08SPIV3)

### NOTES:

#### 1. Port pins are software configurable with pullup device if input port.

- 2. Pin contains pullup/pulldown device if IRQ enabled (IRQPE = 1).

- 3. IRQ does not have a clamp diode to VDD. IRQ should not be driven above VDD.

- 4. Pin contains integrated pullup device.

- 5. High current drive

- 6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBIPn = 1).

### Figure 12-1. Block Diagram Highlighting the SPI Module

## 13.1.1 Features

The IIC includes these distinctive features:

- Compatible with IIC bus standard

- Multi-master operation

- Software programmable for one of 64 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- START and STOP signal generation/detection

- Repeated START signal generation

- Acknowledge bit generation/detection

- Bus busy detection

## 13.1.2 Modes of Operation

The IIC functions the same in normal and monitor modes. A brief description of the IIC in the various MCU modes is given here.

- Run mode This is the basic mode of operation. To conserve power in this mode, disable the module.

- Wait mode The module will continue to operate while the MCU is in wait mode and can provide a wake-up interrupt.

- Stop mode The IIC is inactive in stop3 mode for reduced power consumption. The STOP instruction does not affect IIC register states. Stop1 and stop2 will reset the register contents.

Inter-Integrated Circuit (S08IICV1)

## 13.4.1.1 START Signal

When the bus is free; i.e., no master device is engaging the bus (both SCL and SDA lines are at logical high), a master may initiate communication by sending a START signal. As shown in Figure 13-8, a START signal is defined as a high-to-low transition of SDA while SCL is high. This signal denotes the beginning of a new data transfer (each data transfer may contain several bytes of data) and brings all slaves out of their idle states.

## 13.4.1.2 Slave Address Transmission

The first byte of data transferred immediately after the START signal is the slave address transmitted by the master. This is a seven-bit calling address followed by a R/W bit. The R/W bit tells the slave the desired direction of data transfer.

- 1 =Read transfer, the slave transmits data to the master.

- 0 = Write transfer, the master transmits data to the slave.

Only the slave with a calling address that matches the one transmitted by the master will respond by sending back an acknowledge bit. This is done by pulling the SDA low at the 9th clock (see Figure 13-8).

No two slaves in the system may have the same address. If the IIC module is the master, it must not transmit an address that is equal to its own slave address. The IIC cannot be master and slave at the same time. However, if arbitration is lost during an address cycle, the IIC will revert to slave mode and operate correctly even if it is being addressed by another master.

## 13.4.1.3 Data Transfer

Before successful slave addressing is achieved, the data transfer can proceed byte-by-byte in a direction specified by the R/W bit sent by the calling master.

All transfers that come after an address cycle are referred to as data transfers, even if they carry sub-address information for the slave device

Each data byte is 8 bits long. Data may be changed only while SCL is low and must be held stable while SCL is high as shown in Figure 13-8. There is one clock pulse on SCL for each data bit, the MSB being transferred first. Each data byte is followed by a 9th (acknowledge) bit, which is signalled from the receiving device. An acknowledge is signalled by pulling the SDA low at the ninth clock. In summary, one complete data transfer needs nine clock pulses.

If the slave receiver does not acknowledge the master in the 9th bit time, the SDA line must be left high by the slave. The master interprets the failed acknowledge as an unsuccessful data transfer.

If the master receiver does not acknowledge the slave transmitter after a data byte transmission, the slave interprets this as an end of data transfer and releases the SDA line.

In either case, the data transfer is aborted and the master does one of two things:

- Relinquishes the bus by generating a STOP signal.

- Commences a new calling by generating a repeated START signal.

Analog-to-Digital Converter (S08ATDV3)

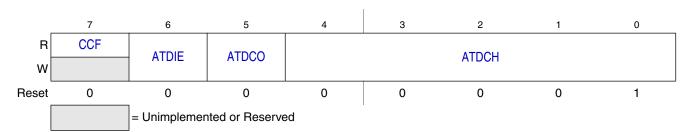

## 14.3.2 ATD Status and Control (ATDSC)

Writes to the ATD status and control register clears the CCF flag, cancels any pending interrupts, and initiates a new conversion.

### Figure 14-6. ATD Status and Control Register (ATDSC)

### Table 14-5. ATDSC Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCF     | <ul> <li>Conversion Complete Flag — The CCF is a read-only bit which is set each time a conversion is complete. The CCF bit is cleared whenever the ATDSC register is written. It is also cleared whenever the result registers, ATDRH or ATDRL, are read.</li> <li>0 Current conversion is not complete.</li> <li>1 Current conversion is complete.</li> </ul>                                                                                                                                                                                   |

| 6<br>ATDIE   | <ul> <li>ATD Interrupt Enabled — When this bit is set, an interrupt is generated upon completion of an ATD conversion. At this time, the result registers contain the result data generated by the conversion. The interrupt will remain pending as long as the conversion complete flag CCF is set. If the ATDIE bit is cleared, then the CCF bit must be polled to determine when the conversion is complete. Note that system reset clears pending interrupts.</li> <li>0 ATD interrupt disabled.</li> <li>1 ATD interrupt enabled.</li> </ul> |

| 5<br>ATDCO   | <ul> <li>ATD Continuous Conversion — When this bit is set, the ATD will convert samples continuously and update the result registers at the end of each conversion. When this bit is cleared, only one conversion is completed between writes to the ATDSC register.</li> <li>0 Single conversion mode.</li> <li>1 Continuous conversion mode.</li> </ul>                                                                                                                                                                                         |

| 4:0<br>ATDCH | Analog Input Channel Select — This field of bits selects the analog input channel whose signal is sampled and converted to digital codes. Table 14-6 lists the coding used to select the various analog input channels.                                                                                                                                                                                                                                                                                                                           |

### Table 14-6. Analog Input Channel Select Coding

| ATDCH | Analog Input Channel                     |

|-------|------------------------------------------|

| 00    | AD0                                      |

| 01    | AD1                                      |

| 02    | AD2                                      |

| 03    | AD3                                      |

| 04    | AD4                                      |

| 05    | AD5                                      |

| 06    | AD6                                      |

| 07    | AD7                                      |

| 08–1D | Reserved (default to V <sub>REFL</sub> ) |

| 1E    | V <sub>REFH</sub>                        |

| 1F    | V <sub>REFL</sub>                        |

# Chapter 15 Development Support

## 15.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip FLASH and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

The alternate BDC clock source for MC9S08GT16A/GT8A is the ICGLCLK. See the Chapter 9, "Internal Clock Generator (S08ICGV4)," for more information about ICGCLK and how to select clock sources.

Development Support

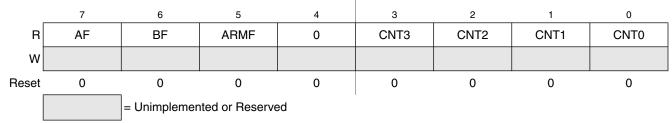

## 15.4.3.9 Debug Status Register (DBGS)

This is a read-only status register.

### Figure 15-9. Debug Status Register (DBGS)

### Table 15-6. DBGS Register Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>AF         | <ul> <li>Trigger Match A Flag — AF is cleared at the start of a debug run and indicates whether a trigger match A condition was met since arming.</li> <li>0 Comparator A has not matched</li> <li>1 Comparator A match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 6<br>BF         | <ul> <li>Trigger Match B Flag — BF is cleared at the start of a debug run and indicates whether a trigger match B condition was met since arming.</li> <li>0 Comparator B has not matched</li> <li>1 Comparator B match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 5<br>ARMF       | Arm Flag — While DBGEN = 1, this status bit is a read-only image of ARM in DBGC. This bit is set by writing 1 to the ARM control bit in DBGC (while DBGEN = 1) and is automatically cleared at the end of a debug run. A debug run is completed when the FIFO is full (begin trace) or when a trigger event is detected (end trace). A debug run can also be ended manually by writing 0 to ARM or DBGEN in DBGC.<br>0 Debugger not armed<br>1 Debugger armed                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 3:0<br>CNT[3:0] | FIFO Valid Count — These bits are cleared at the start of a debug run and indicate the number of words of valid data in the FIFO at the end of a debug run. The value in CNT does not decrement as data is read out of the FIFO. The external debug host is responsible for keeping track of the count as information is read out of the FIFO.         0000 Number of valid words in FIFO = No valid data         0001 Number of valid words in FIFO = 1         0010 Number of valid words in FIFO = 2         0011 Number of valid words in FIFO = 3         0100 Number of valid words in FIFO = 4         0101 Number of valid words in FIFO = 5         0110 Number of valid words in FIFO = 6         0111 Number of valid words in FIFO = 7         1000 Number of valid words in FIFO = 8 |  |  |  |  |  |  |

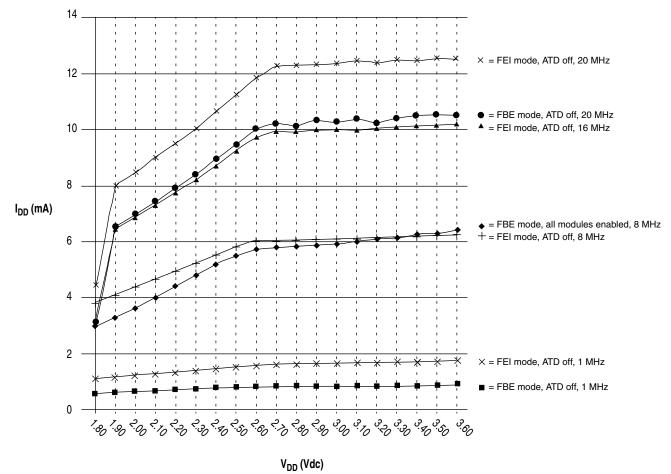

**Electrical Characteristics**

Figure A-6. Typical Run  $I_{DD}$  for FBE and FEE Modes,  $I_{DD}$  vs  $V_{DD}$

Electrical Characteristics

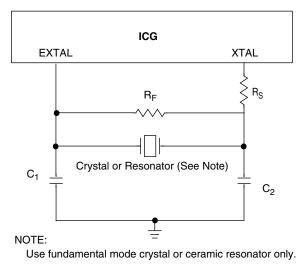

## A.9 Internal Clock Generation Module Characteristics

### Table A-10. ICG DC Electrical Specifications (Temperature Range = -40 to 125°C Ambient)

| Characteristic                                                                                                                                                         | Symbol                           | Min                   | Typ <sup>1</sup>          | Max | Unit     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|---------------------------|-----|----------|

| Load capacitors                                                                                                                                                        | C <sub>1</sub><br>C <sub>2</sub> | See Note <sup>2</sup> |                           |     |          |

| Feedback resistor<br>Low range (32k to 100 kHz)<br>High range (1M – 16 MHz)                                                                                            | R <sub>F</sub>                   |                       | 10<br>1                   |     | ΜΩ<br>ΜΩ |

| Series resistor<br>Low range<br>Low Gain (HGO = 0)<br>High Gain (HGO = 1)<br>High range<br>Low Gain (HGO = 0)<br>High Gain (HGO = 1)<br>$\geq 8$ MHz<br>4 MHz<br>1 MHz | R <sub>S</sub>                   | <br>                  | 0<br>100<br>0<br>10<br>20 |     | kΩ       |

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25°C or is typical recommended value.

<sup>2</sup> See crystal or resonator manufacturer's recommendation.

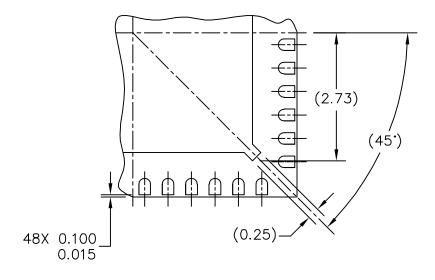

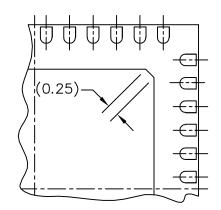

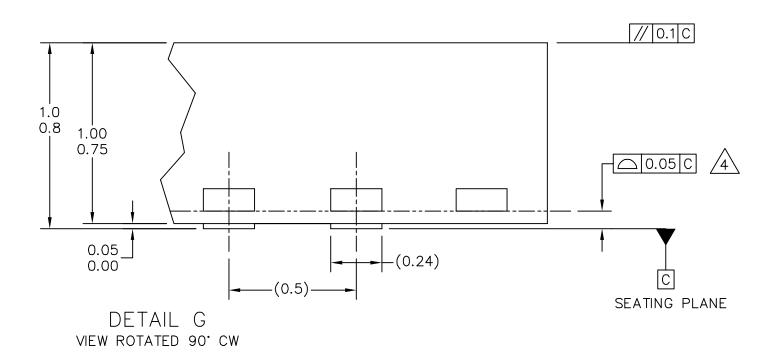

DETAIL M PREFERED PIN 1 BACKSIDE IDENTIFIER

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA   | LOUTLINE       | PRINT VERSION NO  | T TO SCALE |

|---------------------------------------------------------|-------------|----------------|-------------------|------------|

| TITLE: THERMALLY ENHANCED                               | DOCUMENT NO | ): 98ARH99048A | REV: F            |            |

| FLAT NON-LEADED PACKA                                   | CASE NUMBER | 2: 1314–05     | 05 DEC 2005       |            |

| 48 TERMINAL, 0.5 PITCH (7                               | ′ X / X 1)  | STANDARD: JE   | DEC-MO-220 VKKD-2 | 2          |

4.

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS IN MILLIMETERS.

DIMENSION DOES NOT INCLUDE MOLD FLASH. MAXIMUM MOLD FLASH 0.25.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICA           | LOUTLINE    | PRINT VERSION NO | DT TO SCALE |

|---------------------------------------------------------|---------------------|-------------|------------------|-------------|

| TITLE:                                                  |                     | DOCUMENT NO | ): 98ASB42767B   | REV: A      |

| 42 LD PDIP                                              | CASE NUMBER: 858-01 |             | 24 OCT 2005      |             |

|                                                         | STANDARD: NON JEDEC |             |                  |             |

### How to Reach Us:

#### USA/Europe/Locations not listed:

Freescale Semiconductor Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

#### Japan:

Freescale Semiconductor Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku Tokyo 106-8573, Japan 81-3-3440-3569

#### Asia/Pacific:

Freescale Semiconductor H.K. Ltd. 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong 852-26668334

#### Learn More: For more information about Freescale Semiconductor products, please visit http://www.freescale.com

MC9S08GT16A Rev. 1 7/2006 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2004. All rights reserved.