Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                  |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 24                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                |                                                             |

| RAM Size                   | 1K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                 |

| Data Converters            | A/D 4x10b                                                   |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-VFQFN Exposed Pad                                        |

| Supplier Device Package    | 32-HVQFN (5x5)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s08gt8acfce |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section Number

# Title

| 12.6.1 SPI Modu | le Initialization Example |  |

|-----------------|---------------------------|--|

|                 | Initialization Sequence   |  |

| 12.6.1.2        | Pseudo—Code Example       |  |

### Chapter 13 Inter-Integrated Circuit (S08IICV1)

| 13.1 | Introduction                                 | 205 |

|------|----------------------------------------------|-----|

|      | 13.1.1 Features                              | 207 |

|      | 13.1.2 Modes of Operation                    | 207 |

|      | 13.1.3 Block Diagram                         | 208 |

| 13.2 | External Signal Description                  | 208 |

|      | 13.2.1 SCL — Serial Clock Line               | 208 |

|      | 13.2.2 SDA — Serial Data Line                | 208 |

| 13.3 | Register Definition                          |     |

|      | 13.3.1 IIC Address Register (IICA)           | 209 |

|      | 13.3.2 IIC Frequency Divider Register (IICF) | 209 |

|      | 13.3.3 IIC Control Register (IICC)           | 212 |

|      | 13.3.4 IIC Status Register (IICS)            | 213 |

|      | 13.3.5 IIC Data I/O Register (IICD)          | 214 |

| 13.4 | Functional Description                       | 215 |

|      | 13.4.1 IIC Protocol                          |     |

|      | 13.4.1.1 START Signal                        |     |

|      | 13.4.1.2 Slave Address Transmission          |     |

|      | 13.4.1.3 Data Transfer                       | 216 |

|      | 13.4.1.4 STOP Signal                         |     |

|      | 13.4.1.5 Repeated START Signal               |     |

|      | 13.4.1.6 Arbitration Procedure               | 217 |

|      | 13.4.1.7 Clock Synchronization               | 217 |

|      | 13.4.1.8 Handshaking                         | 218 |

|      | 13.4.1.9 Clock Stretching                    | 218 |

| 13.5 | Resets                                       | 218 |

| 13.6 | Interrupts                                   |     |

|      | 13.6.1 Byte Transfer Interrupt               | 219 |

|      | 13.6.2 Address Detect Interrupt              | 219 |

|      | 13.6.3 Arbitration Lost Interrupt            | 219 |

# Chapter 14 Analog-to-Digital Converter (S08ATDV3)

| 14.1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 223 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | 14.1.1 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 223 |

|      | 14.1.2 Modes of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | 14.1.2.1 Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|      | This is the first of the first |     |

# Chapter 3 Modes of Operation

# 3.1 Introduction

The operating modes of the MC9S08GT16A/GT8A are described in this section. Entry into each mode, exit from each mode, and functionality while in each of the modes are described.

### 3.1.1 Features

- Active background mode for code development

- Wait mode:

- CPU shuts down to conserve power

- System clocks running

- Full voltage regulation maintained

- Stop modes:

- Stop1 Full power down of internal circuits for maximum power savings

- Stop2 Partial power down of internal circuits, RAM contents retained

- Stop3 All internal circuits powered for fast recovery

# 3.2 Run Mode

This is the normal operating mode for the MC9S08GT16A/GT8A. This mode is selected when the BKGD/MS pin is high at the rising edge of reset. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at 0xFFFE:0xFFFF after reset.

# 3.3 Active Background Mode

The active background mode functions are managed through the background debug controller (BDC) in the HCS08 core. The BDC, together with the on-chip ICE debug module (DBG), provide the means for analyzing MCU operation during software development.

Active background mode is entered in any of five ways:

- When the BKGD/MS pin is low at the rising edge of reset

- When a BACKGROUND command is received through the BKGD pin

- When a BGND instruction is executed

- When encountering a BDC breakpoint

- When encountering a DBG breakpoint

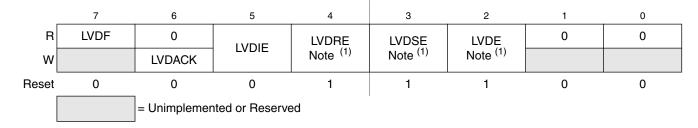

# 5.7.7 System Power Management Status and Control 1 Register (SPMSC1)

<sup>1</sup> This bit can be written only one time after reset. Additional writes are ignored.

### Figure 5-9. System Power Management Status and Control 1 Register (SPMSC1)

| Field       | Description                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF   | Low-Voltage Detect Flag — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                                                                                                                                                           |

| 6<br>LVDACK | <b>Low-Voltage Detect Acknowledge</b> — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0.                                                                                                                                        |

| 5<br>LVDIE  | <ul> <li>Low-Voltage Detect Interrupt Enable — This read/write bit enables hardware interrupt requests for LVDF.</li> <li>0 Hardware interrupt disabled (use polling).</li> <li>1 Request a hardware interrupt when LVDF = 1.</li> </ul>                                                               |

| 4<br>LVDRE  | <ul> <li>Low-Voltage Detect Reset Enable — This read/write bit enables LVDF events to generate a hardware reset (provided LVDE = 1).</li> <li>0 LVDF does not generate hardware resets.</li> <li>1 Force an MCU reset when LVDF = 1.</li> </ul>                                                        |

| 3<br>LVDSE  | <ul> <li>Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.</li> <li>0 Low-voltage detect disabled during stop mode.</li> <li>1 Low-voltage detect enabled during stop mode.</li> </ul> |

| 2<br>LVDE   | <ul> <li>Low-Voltage Detect Enable — This read/write bit enables low-voltage detect logic and qualifies the operation of other bits in this register.</li> <li>0 LVD logic disabled.</li> <li>1 LVD logic enabled.</li> </ul>                                                                          |

### Table 5-10. SPMSC1 Field Descriptions

Parallel Input/Output

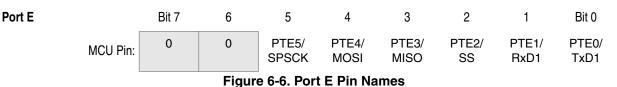

# 6.2.5 Port E, SCI1, and SPI

Port E is an 6-bit port shared with the SCI1 module, SPI1 module, and general-purpose I/O. When the SCI or SPI modules are enabled, the pin direction will be controlled by the module function.

Port E pins are available as general-purpose I/O pins controlled by the port E data (PTED), data direction (PTEDD), pullup enable (PTEPE), and slew rate control (PTESE) registers. Refer to Section 6.3, "Parallel I/O Controls" for more information about general-purpose I/O control.

When the SCI1 module is enabled, PTE0 serves as the SCI1 module's transmit pin (TxD1) and PTE1 serves as the receive pin (RxD1). Refer to Chapter 11, "Serial Communications Interface (S08SCIV1)" for more information about using PTE0 and PTE1 as SCI pins.

When the SPI module is enabled, PTE2 serves as the SPI module's slave select pin ( $\overline{SS1}$ ), PTE3 serves as the master-in slave-out pin (MISO1), PTE4 serves as the master-out slave-in pin (MOS11), and PTE5 serves as the SPI clock pin (SPSCK1). Refer to Chapter 12, "Serial Peripheral Interface (S08SPIV3) for more information about using PTE5–PTE2 as SPI pins.

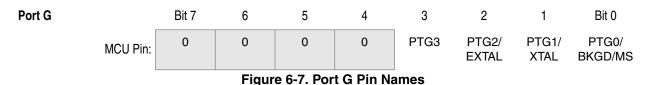

# 6.2.6 Port G, BKGD/MS, and Oscillator

Port G is an 4-bit port which is shared among the background/mode select function, oscillator, and general-purpose I/O. When the background/mode select function or oscillator is enabled, the pin direction will be controlled by the module function.

Port G pins are available as general-purpose I/O pins controlled by the port G data (PTGD), data direction (PTGDD), pullup enable (PTGPE), and slew rate control (PTGSE) registers. Refer to Section 6.3, "Parallel I/O Controls," for more information about general-purpose I/O control.

The internal pullup for PTG0 is enabled when the background/mode select function is enabled, regardless of the state of PTGPE0. During reset, the BKGD/MS pin functions as a mode select pin. After the MCU exits reset, the BKGD/MS pin becomes the background communications input/output pin. The PTG0 can be configured to be a general-purpose output pin. Refer to Section 5.7.4, "System Options Register (SOPT)," for selecting BKGD or PTG0. Refer to Chapter 3, "Modes of Operation,", Chapter 5, "Resets, Interrupts, and System Configuration," and Chapter 15, "Development Support," for more information about using this pin.

The ICG module can be configured to use PTG2–PTG1 ports as crystal oscillator or external clock pins.

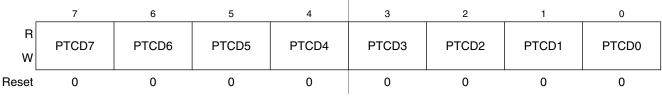

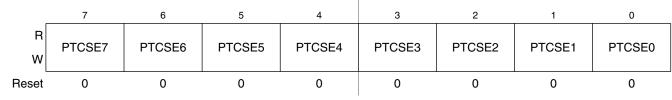

# 6.5.3 Port C Registers (PTCD, PTCPE, PTCSE, and PTCDD)

Port C includes eight general-purpose I/O pins that share with the SCI2 and IIC modules. Port C pins used as general-purpose I/O pins are controlled by the port C data (PTCD), data direction (PTCDD), pullup enable (PTCPE), and slew rate control (PTCSE) registers.

If the SCI2 takes control of a port C pin, the corresponding PTCDD bit is ignored. PTCSE can be used to provide slew rate on the SCI2 transmit pin, TxD2. PTCPE can be used, provided the corresponding PTCDD bit is 0, to provide a pullup device on the SCI2 receive pin, RxD2.

If the IIC takes control of a port C pin, the corresponding PTCDD bit is ignored. PTCSE can be used to provide slew rate on the IIC serial data pin (SDA), when in output mode and the IIC clock pin (SCL). PTCPE can be used, provided the corresponding PTCDD bit is 0, to provide a pullup device on the IIC serial data pin, when in receive mode.

Reads of PTCD will return the logic value of the corresponding pin, provided PTCDD is 0.

Figure 6-16. Port C Data Register (PTCD)

### Table 6-9. PTCD Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCD[7:0] | <b>Port C Data Register Bits</b> — For port C pins that are inputs, reads return the logic level on the pin. For port C pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port C pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTCD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled. |

#### Parallel Input/Output

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      | _ |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---|

| R<br>W | PTCPE7 | PTCPE6 | PTCPE5 | PTCPE4 | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |   |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | - |

### Figure 6-17. Pullup Enable for Port C (PTCPE)

### Table 6-10. PTCPE Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                           |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Pullup Enable for Port C Bits — For port C pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled. For port C pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled.</li> <li>1 Internal pullup device enabled.</li> </ul> |

### Figure 6-18. Slew Rate Control Enable for Port C (PTCSE)

### Table 6-11. PTCSE Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                        |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCSE[7:0] | <ul> <li>Slew Rate Control Enable for Port C Bits — For port C pins that are outputs, these read/write control bits determine whether the slew rate controlled outputs are enabled. For port B pins that are configured as inputs, these bits are ignored.</li> <li>O Slew rate control disabled.</li> <li>1 Slew rate control enabled.</li> </ul> |

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTCDD7 | PTCDD6 | PTCDD5 | PTCDD4 | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| Reset  | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### Figure 6-19. Data Direction for Port C (PTCDD)

### Table 6-12. PTCDD Field Descriptions

| Field             | Description                                                                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTCDD[7:0] | <b>Data Direction for Port C Bits</b> — These read/write bits control the direction of port C pins and what is read for PTCD reads.                                             |

|                   | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port C bit n and PTCD reads return the contents of PTCDn.</li> </ol> |

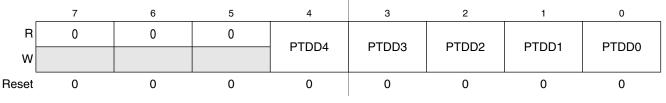

# 6.5.4 Port D Registers (PTDD, PTDPE, PTDSE, and PTDDD)

Port D includes five pins shared between general-purpose I/O, TPM1, and TPM2. Port D pins used as general-purpose I/O pins are controlled by the port D data (PTDD), data direction (PTDDD), pullup enable (PTDPE), and slew rate control (PTDSE) registers.

If a TPM takes control of a port D pin, the corresponding PTDDD bit is ignored. When the TPM is in output compare mode, the corresponding PTDSE can be used to provide slew rate on the pin. When the TPM is in input capture mode, the corresponding PTDPE can be used, provided the corresponding PTDDD bit is 0, to provide a pullup device on the pin.

Reads of PTDD will return the logic value of the corresponding pin, provided PTDDD is 0.

### Figure 6-20. Port D Data Register (PTDD)

### Table 6-13. PTDD Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0<br>PTDD[4:0] | <ul> <li>Port D Data Register Bits — For port D pins that are inputs, reads return the logic level on the pin. For port D pins that are configured as outputs, reads return the last value written to this register.</li> <li>Writes are latched into all bits of this register. For port D pins that are configured as outputs, the logic level is driven out the corresponding MCU pin.</li> <li>Reset forces PTDD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pullups disabled.</li> </ul> |

| _     | 7 | 6 | 5 | 4      | 3      | 2      | 1      | 0      |

|-------|---|---|---|--------|--------|--------|--------|--------|

| R     | 0 | 0 | 0 | PTDPE4 | PTDPE3 | PTDPE2 | PTDPE1 | PTDPE0 |

| w     |   |   |   | FIDFE4 | FIDEES | FIDEEZ | FIDELI | FIDEEU |

| Reset | 0 | 0 | 0 | 0      | 0      | 0      | 0      | 0      |

Figure 6-21. Pullup Enable for Port D (PTDPE)

### Table 6-14. PTDPE Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4:0<br>PTDPE[4:0] | <ul> <li>Pullup Enable for Port D Bits — For port D pins that are inputs, these read/write control bits determine whether internal pullup devices are enabled. For port D pins that are configured as outputs, these bits are ignored and the internal pullup devices are disabled.</li> <li>0 Internal pullup device disabled.</li> <li>1 Internal pullup device enabled.</li> </ul> |  |  |

# Chapter 8 Central Processor Unit (S08CPUV2)

# 8.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

## 8.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

# Chapter 9 Internal Clock Generator (S08ICGV4)

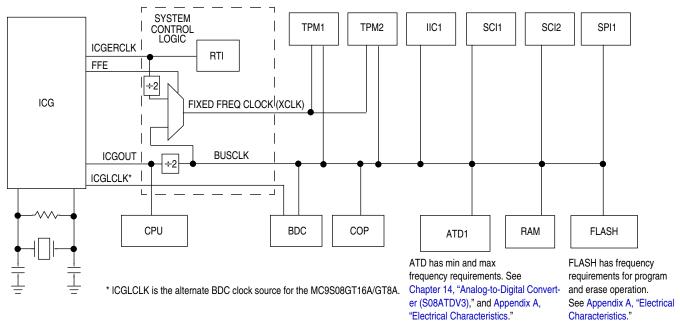

# 9.1 Introduction

The MC9S08GT16A/GT8A microcontroller provides one internal clock generation (ICG) module to create the system bus frequency. All functions described in this section are available on the MC9S08GT16A/GT8A microcontroller. The EXTAL and XTAL pins share port G bits 2 and 1, respectively. Analog supply lines V<sub>DDA</sub> and V<sub>SSA</sub> are internally derived from the MCU's V<sub>DD</sub> and V<sub>SS</sub> pins. Electrical parametric data for the ICG may be found in Appendix A, "Electrical Characteristics."

### NOTE

Freescale Semiconductor programs a factory trim value for ICGTRM into the FLASH location \$FFBE (NVICGTRM). Leaving this address for the ICGTRM value also allows debugger and programmer vendors to perform a manual trim operation and store the resultant ICGTRM value into NVICGTRM for users to access at a later time. The value in NVICGTRM is not automatically loaded and therefore must be copied into ICGTTRM by user code.

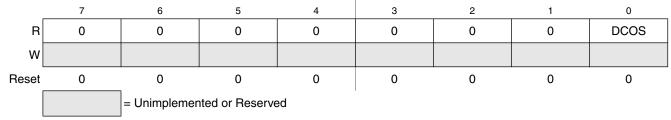

# 9.3.4 ICG Status Register 2 (ICGS2)

### Figure 9-9. ICG Status Register 2 (ICGS2)

### Table 9-4. ICGS2 Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>DCOS | <ul> <li>DCO Clock Stable — The DCOS bit is set when the DCO clock (ICG2DCLK) is stable, meaning the count error has not changed by more than n<sub>unlock</sub> for two consecutive samples and the DCO clock is not static. This bit is used when exiting off state if CLKS = X1 to determine when to switch to the requested clock mode. It is also used in self-clocked mode to determine when to start monitoring the DCO clock. This bit is cleared upon entering the off state.</li> <li>0 DCO clock is unstable.</li> <li>1 DCO clock is stable.</li> </ul> |

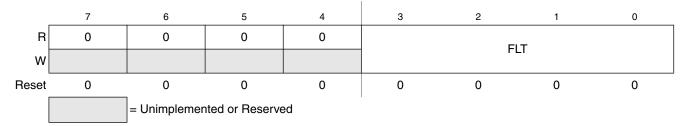

# 9.3.5 ICG Filter Registers (ICGFLTU, ICGFLTL)

### Figure 9-10. ICG Upper Filter Register (ICGFLTU)

### Table 9-5. ICGFLTU Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>FLT | <b>Filter Value</b> — The FLT bits indicate the current filter value, which controls the DCO frequency. The FLT bits are read only except when the CLKS bits are programmed to self-clocked mode (CLKS = 00). In self-clocked mode, any write to ICGFLTU updates the current 12-bit filter value. Writes to the ICGFLTU register will not affect FLT if a previous latch sequence is not complete. |

# 9.4.9 FLL Loss-of-Clock Detection

The reference clock and the DCO clock are monitored under different conditions (see Table 9-8). Provided the reference frequency is being monitored, ERCS = 1 indicates that the reference clock meets minimum frequency requirements. When the reference and/or DCO clock(s) are being monitored, if either one falls below a certain frequency,  $f_{LOR}$  and  $f_{LOD}$ , respectively, the LOCS status bit will be set to indicate the error. LOCS will remain set until it is acknowledged or until the MCU is reset. LOCS is cleared by reading ICGS1 then writing 1 to ICGIF (LOCRE = 0), or by a loss-of-clock induced reset (LOCRE = 1), or by any MCU reset.

If the ICG is in FEE, a loss of reference clock causes the ICG to enter SCM, and a loss of DCO clock causes the ICG to enter FBE mode. If the ICG is in FBE mode, a loss of reference clock will cause the ICG to enter SCM. In each case, the CLKST and CLKS bits will be automatically changed to reflect the new state.

If the ICG is in FEE mode when a loss of clock occurs and the ERCS is still set to 1, then the CLKST bits are set to 10 and the ICG reverts to FBE mode.

A loss of clock will also cause a loss of lock when in FEE or FEI modes. Because the method of clearing the LOCS and LOLS bits is the same, this would only be an issue in the unlikely case that LOLRE = 1 and LOCRE = 0. In this case, the interrupt would be overridden by the reset for the loss of lock.

| Mode                | CLKS     | REFST        | ERCS                   | External Reference<br>Clock<br>Monitored? | DCO Clock<br>Monitored? |

|---------------------|----------|--------------|------------------------|-------------------------------------------|-------------------------|

| Off                 | 0X or 11 | Х            | Forced Low             | No                                        | No                      |

|                     | 10       | 0            | Forced Low             | No                                        | No                      |

|                     | 10       | 1            | Real-Time <sup>1</sup> | Yes <sup>(1)</sup>                        | No                      |

| SCM                 | 0X       | Х            | Forced Low             | No                                        | Yes <sup>2</sup>        |

| (CLKST = 00)        | 10       | 0            | Forced High            | No                                        | Yes <sup>(2)</sup>      |

|                     | 10       | 1            | Real-Time              | Yes                                       | Yes <sup>(2)</sup>      |

|                     | 11       | Х            | Real-Time              | Yes                                       | Yes <sup>(2)</sup>      |

| FEI                 | 0X       | X Forced Low |                        | No                                        | Yes                     |

| (CLKST = 01)        | 11       | Х            | Real-Time              | Yes                                       | Yes                     |

| FBE                 | 10       | 0            | Forced High            | No                                        | No                      |

| (CLKST = 10)        | 10       | 1            | Real-Time              | Yes                                       | No                      |

| FEE<br>(CLKST = 11) | 11       | Х            | Real-Time              | Yes                                       | Yes                     |

Table 9-8. Clock Monitoring (When LOCD = 0)

<sup>1</sup> If ENABLE is high (waiting for external crystal start-up after exiting stop).

<sup>2</sup> DCO clock will not be monitored until DCOS = 1 upon entering SCM from off or FLL bypassed external mode.

## 9.4.11 Fixed Frequency Clock

The ICG provides a fixed frequency clock output, XCLK, for use by on-chip peripherals. This output is equal to the internal bus clock, BUSCLK, in all modes except FEE. In FEE mode, XCLK is equal to ICGERCLK ÷ 2 when the following conditions are met:

- (P × N) ÷ R ≥ 4 where P is determined by RANGE (see Table 9-11), N and R are determined by MFD and RFD respectively (see Table 9-12).

- LOCK = 1.

If the above conditions are not true, then XCLK is equal to BUSCLK.

When the ICG is in either FEI or SCM mode, XCLK is turned off. Any peripherals which can use XCLK as a clock source must not do so when the ICG is in FEI or SCM mode.

## 9.4.12 High Gain Oscillator

The oscillator has the option of running in a high gain oscillator (HGO) mode, which improves the oscillator's resistance to EMC noise when running in FBE or FEE modes. This option is selected by writing a 1 to the HGO bit in the ICGC1 register. HGO is used with both the high and low range oscillators but is only valid when REFS = 1 in the ICGC1 register. When HGO = 0, the standard low-power oscillator is selected. This bit is writable only once after any reset.

# 9.5 Initialization/Application Information

### 9.5.1 Introduction

The section is intended to give some basic direction on which configuration a user would want to select when initializing the ICG. For some applications, the serial communication link may dictate the accuracy of the clock reference. For other applications, lowest power consumption may be the chief clock consideration. Still others may have lowest cost as the primary goal. The ICG allows great flexibility in choosing which is best for any application.

# 11.3 Functional Description

The SCI allows full-duplex, asynchronous, NRZ serial communication among the MCU and remote devices, including other MCUs. The SCI comprises a baud rate generator, transmitter, and receiver block. The transmitter and receiver operate independently, although they use the same baud rate generator. During normal operation, the MCU monitors the status of the SCI, writes the data to be transmitted, and processes received data. The following describes each of the blocks of the SCI.

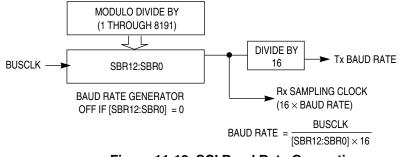

# 11.3.1 Baud Rate Generation

As shown in Figure 11-12, the clock source for the SCI baud rate generator is the bus-rate clock.

Figure 11-12. SCI Baud Rate Generation

SCI communications require the transmitter and receiver (which typically derive baud rates from independent clock sources) to use the same baud rate. Allowed tolerance on this baud frequency depends on the details of how the receiver synchronizes to the leading edge of the start bit and how bit sampling is performed.

The MCU resynchronizes to bit boundaries on every high-to-low transition, but in the worst case, there are no such transitions in the full 10- or 11-bit time character frame so any mismatch in baud rate is accumulated for the whole character time. For a Freescale Semiconductor SCI system whose bus frequency is driven by a crystal, the allowed baud rate mismatch is about  $\pm 4.5$  percent for 8-bit data format and about  $\pm 4$  percent for 9-bit data format. Although baud rate modulo divider settings do not always produce baud rates that exactly match standard rates, it is normally possible to get within a few percent, which is acceptable for reliable communications.

# 11.3.2 Transmitter Functional Description

This section describes the overall block diagram for the SCI transmitter (Figure 11-2), as well as specialized functions for sending break and idle characters.

The transmitter is enabled by setting the TE bit in SCIxC2. This queues a preamble character that is one full character frame of the idle state. The transmitter then remains idle until data is available in the transmit data buffer. Programs store data into the transmit data buffer by writing to the SCI data register (SCIxD).

The central element of the SCI transmitter is the transmit shift register that is either 10 or 11 bits long depending on the setting in the M control bit. For the remainder of this section, we will assume M = 0, selecting the normal 8-bit data mode. In 8-bit data mode, the shift register holds a start bit, eight data bits, and a stop bit. When the transmit shift register is available for a new SCI character, the value waiting in

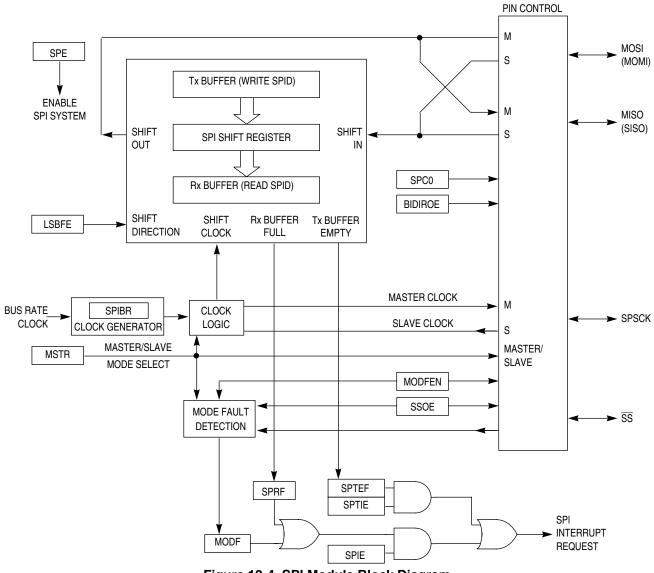

When the SPI is configured as a master, the clock output is routed to the SPSCK pin, the shifter output is routed to MOSI, and the shifter input is routed from the MISO pin.

When the SPI is configured as a slave, the SPSCK pin is routed to the clock input of the SPI, the shifter output is routed to MISO, and the shifter input is routed from the MOSI pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

Figure 12-4. SPI Module Block Diagram

# 12.1.3 SPI Baud Rate Generation

As shown in Figure 12-5, the clock source for the SPI baud rate generator is the bus clock. The three prescale bits (SPPR2:SPPR1:SPPR0) choose a prescale divisor of 1, 2, 3, 4, 5, 6, 7, or 8. The three rate select bits (SPR2:SPR1:SPR0) divide the output of the prescaler stage by 2, 4, 8, 16, 32, 64, 128, or 256 to get the internal SPI master mode bit-rate clock.

Inter-Integrated Circuit (S08IICV1)

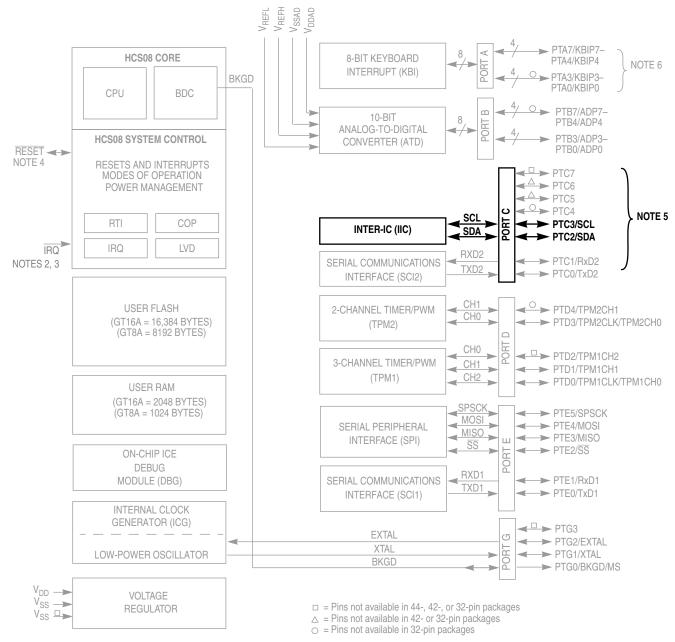

#### NOTES:

1. Port pins are software configurable with pullup device if input port.

- 2. Pin contains pullup/pulldown device if IRQ enabled (IRQPE = 1).

- 3. IRQ does not have a clamp diode to VDD. IRQ should not be driven above VDD.

- 4. Pin contains integrated pullup device.

5. High current drive

6. Pins PTA[7:4] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBIPn = 1).

#### Figure 13-1. Block Diagram Highlighting the IIC Module

| ICR<br>(hex) | SCL Divider | SDA Hold<br>Value |

|--------------|-------------|-------------------|

| 00           | 20          | 7                 |

| 01           | 22          | 7                 |

| 02           | 24          | 8                 |

| 03           | 26          | 8                 |

| 04           | 28          | 9                 |

| 05           | 30          | 9                 |

| 06           | 34          | 10                |

| 07           | 40          | 10                |

| 08           | 28          | 7                 |

| 09           | 32          | 7                 |

| 0A           | 36          | 9                 |

| 0B           | 40          | 9                 |

| 0C           | 44          | 11                |

| 0D           | 48          | 11                |

| 0E           | 56          | 13                |

| 0F           | 68          | 13                |

| 10           | 48          | 9                 |

| 11           | 56          | 9                 |

| 12           | 64          | 13                |

| 13           | 72          | 13                |

| 14           | 80          | 17                |

| 15           | 88          | 17                |

| 16           | 104         | 21                |

| 17           | 128         | 21                |

| 18           | 80          | 9                 |

| 19           | 96          | 9                 |

| 1A           | 112         | 17                |

| 1B           | 128         | 17                |

| 1C           | 144         | 25                |

| 1D           | 160         | 25                |

| 1E           | 192         | 33                |

| 1F           | 240         | 33                |

| Table 13-3. IIC Divider and Hold Values |  |

|-----------------------------------------|--|

|-----------------------------------------|--|

| ICR<br>(hex) | SCL Divider | SDA Hold<br>Value |

|--------------|-------------|-------------------|

| 20           | 160         | 17                |

| 21           | 192         | 17                |

| 22           | 224         | 33                |

| 23           | 256         | 33                |

| 24           | 288         | 49                |

| 25           | 320         | 49                |

| 26           | 384         | 65                |

| 27           | 480         | 65                |

| 28           | 320         | 33                |

| 29           | 384         | 33                |

| 2A           | 448         | 65                |

| 2B           | 512         | 65                |

| 2C           | 576         | 97                |

| 2D           | 640         | 97                |

| 2E           | 768         | 129               |

| 2F           | 960         | 129               |

| 30           | 640         | 65                |

| 31           | 768         | 65                |

| 32           | 896         | 129               |

| 33           | 1024        | 129               |

| 34           | 1152        | 193               |

| 35           | 1280        | 193               |

| 36           | 1536        | 257               |

| 37           | 1920        | 257               |

| 38           | 1280        | 129               |

| 39           | 1536        | 129               |

| 3A           | 1792        | 257               |

| 3B           | 2048        | 257               |

| 3C           | 2304        | 385               |

| 3D           | 2560        | 385               |

| 3E           | 3072        | 513               |

| 3F           | 3840        | 513               |

|              |             |                   |

Inter-Integrated Circuit (S08IICV1)

# 13.3.5 IIC Data I/O Register (IICD)

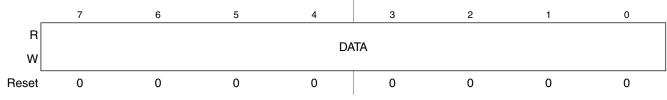

Figure 13-7. IIC Data I/O Register (IICD)

### Table 13-6. IICD Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data</b> — In master transmit mode, when data is written to the IICD, a data transfer is initiated. The most significant bit is sent first. In master receive mode, reading this register initiates receiving of the next byte of data. |

### NOTE

When transmitting out of master receive mode, the IIC mode should be switched before reading the IICD register to prevent an inadvertent initiation of a master receive data transfer.

In slave mode, the same functions are available after an address match has occurred.

Note that the TX bit in IICC must correctly reflect the desired direction of transfer in master and slave modes for the transmission to begin. For instance, if the IIC is configured for master transmit but a master receive is desired, then reading the IICD will not initiate the receive.

Reading the IICD will return the last byte received while the IIC is configured in either master receive or slave receive modes. The IICD does not reflect every byte that is transmitted on the IIC bus, nor can software verify that a byte has been written to the IICD correctly by reading it back.

In master transmit mode, the first byte of data written to IICD following assertion of MST is used for the address transfer and should comprise of the calling address (in bit 7–bit 1) concatenated with the required R/W bit (in position bit 0).

**Electrical Characteristics**

| Rating                                                                                                                  | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                                          | V <sub>DD</sub>  | -0.3 to +3.8                  | V    |

| Maximum current into V <sub>DD</sub>                                                                                    | I <sub>DD</sub>  | 120                           | mA   |

| Digital input voltage                                                                                                   | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1</sup> , <sup>2</sup> , <sup>3</sup> | Ι <sub>D</sub>   | ± 25                          | mA   |

| Storage temperature range                                                                                               | T <sub>stg</sub> | -55 to 150                    | °C   |

| Maximum junction temperature                                                                                            | TJ               | 150                           | °C   |

### Table A-2. Absolute Maximum Ratings

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2\,$  All functional non-supply pins are internally clamped to V\_{SS} and V\_{DD}

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

# A.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.