#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HCS08                                                                  |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI, UART/USART                                 |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 39                                                                     |

| Program Memory Size        | 8KB (8K × 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 8x10b SAR                                                          |

| Oscillator Type            | External, Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-MAPQFN-EP (7x7)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s08gt8acfde |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 2 Pins and Connections

# 2.1 Introduction

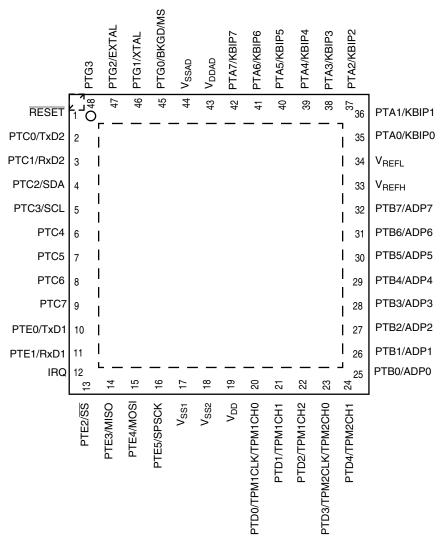

This section describes signals that connect to package pins. It includes a pinout diagram, a table of signal properties, and detailed discussion of signals.

# 2.2 Device Pin Assignment

Figure 2-1. MC9S08GT16A/GT8A in 48-Pin QFN Package

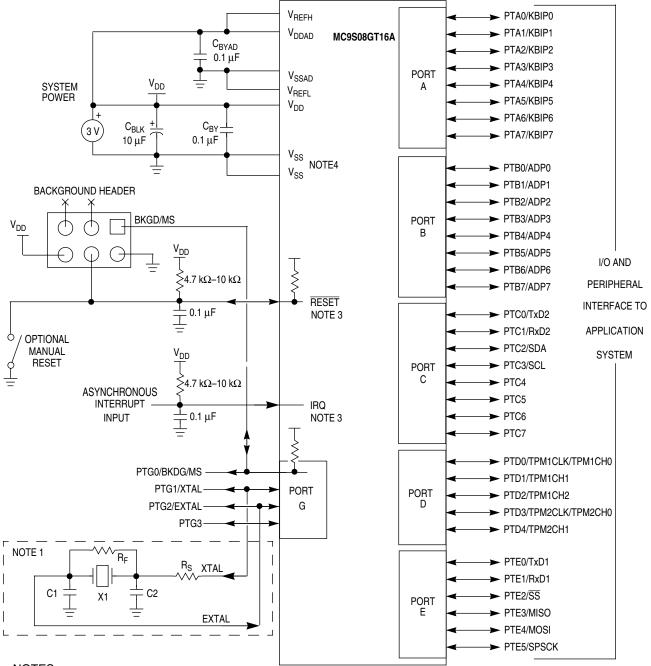

### 2.3 Recommended System Connections

Figure 2-5 shows pin connections that are common to almost all MC9S08GT16A application systems. A more detailed discussion of system connections follows.

#### NOTES:

- 1. Not required if using the internal oscillator option.

- 2. The 48-pin QFN has 2 V<sub>SS</sub> pins (V<sub>SS1</sub> and V<sub>SS2</sub>), both of which must be connected to GND.

- 3. RC filters on RESET and IRQ are recommended for EMC-sensitive applications and systems.

Figure 2-5. Basic System Connections

#### Resets, Interrupts, and System Configuration

- Computer operating properly (COP) watchdog timer

- Illegal opcode detect

- Illegal address detect

- Background debug forced reset

- The reset pin ( $\overline{\text{RESET}}$ )

- Clock generator loss of lock and loss of clock reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register. Whenever the MCU enters reset, the internal clock generator (ICG) module switches to self-clocked mode with the frequency of  $f_{Self\_reset}$  selected. The reset pin is driven low for 34 internal bus cycles where the internal bus frequency is half the ICG frequency. After the 34 cycles are completed, the pin is released and will be pulled up by the internal pullup resistor, unless it is held low externally. After the pin is released, it is sampled after another 38 cycles to determine whether the reset pin is the cause of the MCU reset.

# 5.3 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP timer periodically. If the application program gets lost and fails to reset the COP before it times out, a system reset is generated to force the system back to a known starting point. The COP watchdog is enabled by the COPE bit in SOPT (see Section 5.7.4, "System Options Register (SOPT)" for additional information). The COP timer is reset by writing any value to the address of SRS. This write does not affect the data in the read-only SRS. Instead, the act of writing to this address is decoded and sends a reset signal to the COP timer.

After any reset, the COP timer is enabled. This provides a reliable way to detect code that is not executing as intended. If the COP watchdog is not used in an application, it can be disabled by clearing the COPE bit in the write-once SOPT register. Also, the COPT bit can be used to choose one of two timeout periods (2<sup>18</sup> or 2<sup>13</sup> cycles of the bus rate clock). Even if the application will use the reset default settings in COPE and COPT, the user should still write to write-once SOPT during reset initialization to lock in the settings. That way, they cannot be changed accidentally if the application program gets lost.

The write to SRS that services (clears) the COP timer should not be placed in an interrupt service routine (ISR) because the ISR could continue to be executed periodically even if the main application program fails.

When the MCU is in active background mode, the COP timer is temporarily disabled.

# 5.4 Interrupts

Interrupts provide a way to save the current CPU status and registers, execute an interrupt service routine (ISR), and then restore the CPU status so processing resumes where it left off before the interrupt. Other than the software interrupt (SWI), which is a program instruction, interrupts are caused by hardware events such as an edge on the IRQ pin or a timer-overflow event. The debug module can also generate an SWI under certain circumstances.

# 6.4 Stop Modes

Depending on the stop mode, I/O functions differently as the result of executing a STOP instruction. An explanation of I/O behavior for the various stop modes follows:

- When the MCU enters stop1 mode, all internal registers including general-purpose I/O control and data registers are powered down. All of the general-purpose I/O pins assume their reset state: output buffers and pullups turned off. Upon exit from stop1, all I/O must be initialized as if the MCU had been reset.

- When the MCU enters stop2 mode, the internal registers are powered down as in stop1 but the I/O pin states are latched and held. For example, a port pin that is an output driving low continues to function as an output driving low even though its associated data direction and output data registers are powered down internally. Upon exit from stop2, the pins continue to hold their states until a 1 is written to the PPDACK bit. To avoid discontinuity in the pin state following exit from stop2, the user must restore the port control and data registers to the values they held before entering stop2. These values can be stored in RAM before entering stop2 because the RAM is maintained during stop2.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

# 6.5 Register Definition

This section provides information about all registers and control bits associated with the parallel I/O ports.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

# 6.5.1 Port A Registers (PTAD, PTAPE, PTASE, and PTADD)

Port A includes eight pins shared between general-purpose I/O and the KBI module. Port A pins used as general-purpose I/O pins are controlled by the port A data (PTAD), data direction (PTADD), pullup enable (PTAPE), and slew rate control (PTASE) registers.

If the KBI takes control of a port A pin, the corresponding PTASE bit is ignored since the pin functions as an input. As long as PTADD is 0, the PTAPE controls the pullup enable for the KBI function. Reads of PTAD will return the logic value of the corresponding pin, provided PTADD is 0.

Internal Clock Generator (S08ICGV4)

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2<br>OSCSTEN | <ul> <li>Enable Oscillator in Off Mode — The OSCSTEN bit controls whether or not the oscillator circuit remains enabled when the ICG enters off mode. This bit has no effect if HGO = 1 and RANGE = 1.</li> <li>Oscillator disabled when ICG is in off mode unless ENABLE is high, CLKS = 10, and REFST = 1.</li> <li>Oscillator enabled when ICG is in off mode, CLKS = 1X and REFST = 1.</li> </ul> |  |  |  |

| 1<br>LOCD    | Loss of Clock Disable         0       Loss of clock detection enabled.         1       Loss of clock detection disabled.                                                                                                                                                                                                                                                                              |  |  |  |

#### Table 9-1. ICGC1 Register Field Descriptions (continued)

Internal Clock Generator (S08ICGV4)

### 9.4.7.1 FLL Engaged External Unlocked

FEE unlocked is entered when FEE is entered and the count error ( $\Delta n$ ) output from the subtractor is greater than the maximum  $n_{unlock}$  or less than the minimum  $n_{unlock}$ , as required by the lock detector to detect the unlock condition.

The ICG will remain in this state while the count error  $(\Delta n)$  is greater than the maximum  $n_{lock}$  or less than the minimum  $n_{lock}$ , as required by the lock detector to detect the lock condition.

In this state, the pulse counter, subtractor, digital loop filter, and DCO form a closed loop and attempt to lock it according to their operational descriptions later in this section. Upon entering this state and until the FLL becomes locked, the output clock signal ICGOUT frequency is given by  $f_{ICGDCLK} / (2 \times R)$  This extra divide by two prevents frequency overshoots during the initial locking process from exceeding chip-level maximum frequency specifications. After the FLL has locked, if an unexpected loss of lock causes it to re-enter the unlocked state while the ICG remains in FEE mode, the output clock signal ICGOUT frequency is given by  $f_{ICGDCLK} / R$ .

### 9.4.7.2 FLL Engaged External Locked

FEE locked is entered from FEE unlocked when the count error ( $\Delta n$ ) is less than  $n_{lock}$  (max) and greater than  $n_{lock}$  (min) for a given number of samples, as required by the lock detector to detect the lock condition. The output clock signal ICGOUT frequency is given by  $f_{ICGDCLK}/R$ . In FLL engaged external locked, the filter value is updated only once every four comparison cycles. The update made is an average of the error measurements taken in the four previous comparisons.

### 9.4.8 FLL Lock and Loss-of-Lock Detection

To determine the FLL locked and loss-of-lock conditions, the pulse counter counts the pulses of the DCO for one comparison cycle (see Table 9-9 for explanation of a comparison cycle) and passes this number to the subtractor. The subtractor compares this value to the value in MFD and produces a count error,  $\Delta n$ . To achieve locked status,  $\Delta n$  must be between  $n_{lock}$  (min) and  $n_{lock}$  (max). After the FLL has locked,  $\Delta n$  must stay between  $n_{unlock}$  (min) and  $n_{unlock}$  (max) to remain locked. If  $\Delta n$  goes outside this range unexpectedly, the LOLS status bit is set and remains set until cleared by software or until the MCU is reset. LOLS is cleared by reading ICGS1 then writing 1 to ICGIF (LOLRE = 0), or by a loss-of-lock induced reset (LOLRE = 1), or by any MCU reset.

If the ICG enters the off state due to stop mode when ENBDM = OSCSTEN = 0, the FLL loses locked status (LOCK is cleared), but LOLS remains unchanged because this is not an unexpected loss-of-lock condition. Though it would be unusual, if ENBDM is cleared to 0 while the MCU is in stop, the ICG enters the off state. Because this is an unexpected stopping of clocks, LOLS will be set when the MCU wakes up from stop.

Expected loss of lock occurs when the MFD or CLKS bits are changed or in FEI mode only, when the TRIM bits are changed. In these cases, the LOCK bit will be cleared until the FLL regains lock, but the LOLS will not be set.

### 9.4.11 Fixed Frequency Clock

The ICG provides a fixed frequency clock output, XCLK, for use by on-chip peripherals. This output is equal to the internal bus clock, BUSCLK, in all modes except FEE. In FEE mode, XCLK is equal to ICGERCLK ÷ 2 when the following conditions are met:

- (P × N) ÷ R ≥ 4 where P is determined by RANGE (see Table 9-11), N and R are determined by MFD and RFD respectively (see Table 9-12).

- LOCK = 1.

If the above conditions are not true, then XCLK is equal to BUSCLK.

When the ICG is in either FEI or SCM mode, XCLK is turned off. Any peripherals which can use XCLK as a clock source must not do so when the ICG is in FEI or SCM mode.

### 9.4.12 High Gain Oscillator

The oscillator has the option of running in a high gain oscillator (HGO) mode, which improves the oscillator's resistance to EMC noise when running in FBE or FEE modes. This option is selected by writing a 1 to the HGO bit in the ICGC1 register. HGO is used with both the high and low range oscillators but is only valid when REFS = 1 in the ICGC1 register. When HGO = 0, the standard low-power oscillator is selected. This bit is writable only once after any reset.

### 9.5 Initialization/Application Information

#### 9.5.1 Introduction

The section is intended to give some basic direction on which configuration a user would want to select when initializing the ICG. For some applications, the serial communication link may dictate the accuracy of the clock reference. For other applications, lowest power consumption may be the chief clock consideration. Still others may have lowest cost as the primary goal. The ICG allows great flexibility in choosing which is best for any application.

#### 9.5.4 Example #3: No External Crystal Connection, 5.4 MHz Bus Frequency

In this example, the FLL will be used (in FEI mode) to multiply the internal 243 kHz (approximate) reference clock up to 10.8 MHz to achieve 5.4 MHz bus frequency. This system will also use the trim function to fine tune the frequency based on an external reference signal.

After the MCU is released from reset, the ICG is in self-clocked mode (SCM) and supplies approximately 8 MHz on ICGOUT which corresponds to a 4 MHz bus frequency (f<sub>Bus</sub>).

The clock scheme will be FLL engaged, internal (FEI). So

$$f_{ICGOUT} = (f_{IRG} / 7) * P * N / R ; P = 64, f_{IRG} = 243 \text{ kHz}$$

Eqn. 9-5

Solving for N / R gives:

A trim procedure will be required to hone the frequency to exactly 5.4 MHz. An example of the trim procedure is shown in example #4.

The values needed in each register to set up the desired operation are:

#### ICGC1 = \$28 (%00101000)

| Bit 7    | HGO     | 0  | Configures oscillator for low power                                          |

|----------|---------|----|------------------------------------------------------------------------------|

| Bit 6    | RANGE   | 0  | Configures oscillator for low-frequency range; FLL prescale factor is 64     |

| Bit 5    | REFS    | 1  | Oscillator using crystal or resonator requested (bit is really a don't care) |

| Bits 4:3 | CLKS    | 01 | FLL engaged, internal reference clock mode                                   |

| Bit 2    | OSCSTEN | 0  | Disables the oscillator                                                      |

| Bit 1    | LOCD    | 0  | Loss-of-clock enabled                                                        |

| Bit 0    |         | 0  | Unimplemented or reserved, always reads zero                                 |

ICGC2 = \$31 (%00110001)

| Bit 7   | LOLRE | 0   | Generates an interrupt request on loss of lock  |

|---------|-------|-----|-------------------------------------------------|

| Bit 6:4 | MFD   | 011 | Sets the MFD multiplication factor to 10        |

| Bit 3   | LOCRE | 0   | Generates an interrupt request on loss of clock |

| Bit 2:0 | RFD   | 001 | Sets the RFD division factor to $\div 2$        |

#### ICGS1 = \$xx

This is read only except for clearing interrupt flag

#### ICGS2 = \$xx

This is read only; good idea to read this before performing time critical operations

#### ICGFLTLU/L =\$xx

Not used in this example

#### Timer/Pulse-Width Modulator (S08TPMV2)

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some MCU systems have more than one TPM, so register names include placeholder characters to identify which TPM and which channel is being referenced. For example, TPMxCnSC refers to timer (TPM) x, channel n and TPM1C2SC is the status and control register for timer 1, channel 2.

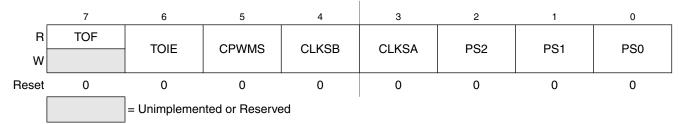

# 10.3.1 Timer x Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits that are used to configure the interrupt enable, TPM configuration, clock source, and prescale divisor. These controls relate to all channels within this timer module.

#### Figure 10-3. Timer x Status and Control Register (TPMxSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | <b>Timer Overflow Flag</b> — This flag is set when the TPM counter changes to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. When the TPM is configured for CPWM, TOF is set after the counter has reached the value in the modulo register, at the transition to the next lower count value. Clear TOF by reading the TPM status and control register when TOF is set and then writing a 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. Reset clears TOF. Writing a 1 to TOF has no effect. 0 TPM counter has not reached modulo value or overflow 1 TPM counter has overflowed |

| 6<br>TOIE        | Timer Overflow Interrupt Enable — This read/write bit enables TPM overflow interrupts. If TOIE is set, aninterrupt is generated when TOF equals 1. Reset clears TOIE.0 TOF interrupts inhibited (use software polling)1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>CPWMS       | <ul> <li>Center-Aligned PWM Select — This read/write bit selects CPWM operating mode. Reset clears this bit so the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up-/down-counting mode for CPWM functions. Reset clears CPWMS.</li> <li>All TPMx channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register</li> <li>All TPMx channels operate in center-aligned PWM mode</li> </ul>                                                                                                                                                                  |

| 4:3<br>CLKS[B:A] | <b>Clock Source Select</b> — As shown in Table 10-2, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The external source and the XCLK are synchronized to the bus clock by an on-chip synchronization circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2:0<br>PS[2:0]   | <b>Prescale Divisor Select</b> — This 3-bit field selects one of eight divisors for the TPM clock input as shown in Table 10-3. This prescaler is located after any clock source synchronization or clock source selection, so it affects whatever clock source is selected to drive the TPM system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 10-1. TPMxSC Register Field Descriptions

In output compare or PWM modes, writing to either byte (TPMxCnVH or TPMxCnVL) latches the value into a buffer. When both bytes have been written, they are transferred as a coherent 16-bit value into the timer channel value registers. This latching mechanism may be manually reset by writing to the TPMxCnSC register.

This latching mechanism allows coherent 16-bit writes in either order, which is friendly to various compiler implementations.

# **10.4 Functional Description**

All TPM functions are associated with a main 16-bit counter that allows flexible selection of the clock source and prescale divisor. A 16-bit modulo register also is associated with the main 16-bit counter in the TPM. Each TPM channel is optionally associated with an MCU pin and a maskable interrupt function.

The TPM has center-aligned PWM capabilities controlled by the CPWMS control bit in TPMxSC. When CPWMS is set to 1, timer counter TPMxCNT changes to an up-/down-counter and all channels in the associated TPM act as center-aligned PWM channels. When CPWMS = 0, each channel can independently be configured to operate in input capture, output compare, or buffered edge-aligned PWM mode.

The following sections describe the main 16-bit counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend on the operating mode, these topics are covered in the associated mode sections.

### 10.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, up-counting vs. up-/down-counting, end-of-count overflow, and manual counter reset.

After any MCU reset, CLKSB:CLKSA = 0:0 so no clock source is selected and the TPM is inactive. Normally, CLKSB:CLKSA would be set to 0:1 so the bus clock drives the timer counter. The clock source for each of the TPM can be independently selected to be off, the bus clock (BUSCLK), the fixed system clock (XCLK), or an external input. The maximum frequency allowed for the external clock option is one-fourth the bus rate. Refer to Section 10.3.1, "Timer x Status and Control Register (TPMxSC)" and Table 10-2 for more information about clock source selection.

When the microcontroller is in active background mode, the TPM temporarily suspends all counting until the microcontroller returns to normal user operating mode. During stop mode, all TPM clocks are stopped; therefore, the TPM is effectively disabled until clocks resume. During wait mode, the TPM continues to operate normally.

The main 16-bit counter has two counting modes. When center-aligned PWM is selected (CPWMS = 1), the counter operates in up-/down-counting mode. Otherwise, the counter operates as a simple up-counter. As an up-counter, the main 16-bit counter counts from 0x0000 through its terminal count and then continues with 0x0000. The terminal count is 0xFFFF or a modulus value in TPMxMODH:TPMxMODL.

Inter-Integrated Circuit (S08IICV1)

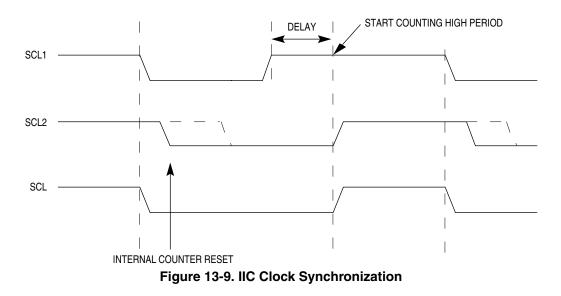

#### 13.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

#### 13.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

### 13.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

### 13.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 13-7 occur provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a one to it in the interrupt routine. The user can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | IICIF | IICIE        |

| Match of received calling address | IAAS   | IICIF | IICIE        |

| Arbitration Lost                  | ARBL   | IICIF | IICIE        |

| Table 13-7. | Interrupt | Summary |

|-------------|-----------|---------|

|-------------|-----------|---------|

| Name                                                     | Function                                |  |  |

|----------------------------------------------------------|-----------------------------------------|--|--|

| AD7–AD0                                                  | Channel input pins                      |  |  |

| V <sub>REFH</sub> High reference voltage for ATD convert |                                         |  |  |

| V <sub>REFL</sub>                                        | Low reference voltage for ATD converter |  |  |

| V <sub>DDAD</sub>                                        | ATD power supply voltage                |  |  |

| V <sub>SSAD</sub>                                        | ATD ground supply voltage               |  |  |

Table 14-1. Signal Properties

#### 14.2.1 ADP7–ADP0 — Channel Input Pins

The channel pins are used as the analog input pins of the ATD. Each pin is connected to an analog switch which serves as the signal gate into the sample submodule.

### 14.2.2 V<sub>REFH</sub>, V<sub>REFL</sub> — ATD Reference Pins

These pins serve as the source for the high and low reference potentials for the converter. Separation from the power supply pins accommodates the filtering necessary to achieve the accuracy of which the system is capable.

# 14.2.3 V<sub>DDAD</sub>, V<sub>SSAD</sub> — ATD Supply Pins

These two pins are used to supply power and ground to the analog section of the ATD. Dedicated power is required to isolate the sensitive analog circuitry from the normal levels of noise present on digital power supplies.

#### NOTE

$V_{DDAD1}$  and  $V_{DD}$  must be at the same potential. Likewise,  $V_{SSAD1}$  and  $V_{SS}$  must be at the same potential.

# 14.3 Register Definition

The ATD has seven registers that control ATD functions.

Refer to the direct-page register summary in the memory chapter of this data sheet for the absolute address assignments for all ATD registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

# 14.3.1 ATD Control (ATDC)

Writes to the ATD control register will abort the current conversion, but will not start a new conversion.

**Electrical Characteristics**

#### Unit С Symbol Typical<sup>1</sup> Parameter Min Max Output low voltage ( $V_{DD} \ge 1.8 \text{ V}$ ) D $I_{OI} = 2.0 \text{ mA}$ (ports A, B, D, E, and G) 0.5 V D Output low voltage (port C) VOL $I_{OL} = 10.0 \text{ mA} (V_{DD} \ge 2.7 \text{ V})$ 0.5 $I_{OL} = 6 \text{ mA} (V_{DD} \ge 2.3 \text{ V})$ 0.5 $I_{OL} = 3 \text{ mA} (V_{DD} \ge 1.8 \text{ V})$ 0.5 Maximum total IOL for all port pins D mΑ IOLT 60 dc injection current $^{\rm 4,\ 5,\ 6,\ 7}$ DC Injection Current A, B, C, D Single pin limit $V_{IN} > V_{DD}$ 0 2 mΑ ll<sub>IC</sub> $V_{IN} < V_{SS}$ 0 -0.2 mΑ Total MCU limit, includes sum of all stressed pins $V_{IN} > V_{DD}$ 0 25 mΑ $V_{IN} < V_{SS}$ 0 -5 mΑ Input capacitance (all non-supply pins)<sup>(2)</sup> С CIn 7 pF

Table A-6. DC Characteristics (Sheet 2 of 2) (Temperature Range = -40 to 125°C Ambient)

<sup>1</sup> Typicals are measured at 25°C.

<sup>2</sup> This parameter is characterized and not tested on each device.

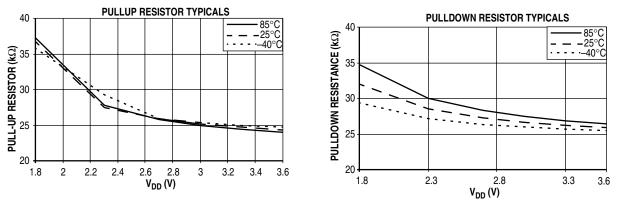

<sup>3</sup> Measurement condition for pull resistors:  $V_{In} = V_{SS}$  for pullup and  $V_{In} = V_{DD}$  for pulldown.

<sup>4</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low which (would reduce overall power consumption).

$^{5}$  All functional non-supply pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub>.

<sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

$^7$  IRQ does not have a clamp diode to V<sub>DD</sub>. Do not drive IRQ above V<sub>DD</sub>.

Figure A-1. Pullup and Pulldown Typical Resistor Values ( $V_{DD} = 3.0 \text{ V}$ )

| No. | Characteristic                          | Condition                                                      | Symbol           | Min   | Тур           | Мах          | Unit |

|-----|-----------------------------------------|----------------------------------------------------------------|------------------|-------|---------------|--------------|------|

| 7   | Ideal resolution (1 LSB) <sup>5</sup>   | $2.08V \le V_{DDAD} \le 3.6V$                                  | RES              | 2.031 |               | 3.516        | mV   |

|     |                                         | $1.80V \le V_{DDAD} < 2.08V$                                   |                  | 1.758 | _             | 2.031        |      |

| 8   | Differential non-linearity <sup>6</sup> | $1.80V \le V_{DDAD} \le 3.6V$                                  | DNL              | _     | <u>+</u> 0.5  | <u>+</u> 1.0 | LSB  |

| 9   | Integral non-linearity <sup>7</sup>     | $1.80 \text{ V} \leq \text{V}_{\text{DDAD}} \leq 3.6 \text{V}$ | INL              | _     | <u>+</u> 0.5  | <u>+</u> 1.0 | LSB  |

| 10  | Zero-scale error <sup>8</sup>           | $1.80V \le V_{DDAD} \le 3.6V$                                  | E <sub>ZS</sub>  | _     | <u>+</u> 0.4  | <u>+</u> 1.0 | LSB  |

| 11  | Full-scale error <sup>9</sup>           | $1.80V \le V_{DDAD} \le 3.6V$                                  | E <sub>FS</sub>  | —     | <u>+</u> 0.4  | <u>+</u> 1.0 | LSB  |

| 12  | Input leakage error <sup>10</sup>       | $1.80V \le V_{DDAD} \le 3.6V$                                  | E <sub>IL</sub>  | _     | <u>+</u> 0.05 | <u>+</u> 5   | LSB  |

| 13  | Total unadjusted error <sup>11</sup>    | $1.80V \le V_{DDAD} \le 3.6V$                                  | Ε <sub>Τυ</sub>  | _     | <u>+</u> 1.1  | <u>+</u> 2.5 | LSB  |

| 14  | Input resistance                        |                                                                | R <sub>AIN</sub> | _     | 5             | 7            | kΩ   |

| 15  | Input capacitance                       |                                                                | C <sub>AIN</sub> | —     | _             | 25           | pF   |

| Table A-9. ATD Timing/Performance Characteristics <sup>1</sup> (con | tinued) |

|---------------------------------------------------------------------|---------|

|---------------------------------------------------------------------|---------|

<sup>1</sup> All ACCURACY numbers are based on processor and system being in WAIT state (very little activity and no IO switching) and that adequate low-pass filtering is present on analog input pins (filter with 0.01 μF to 0.1 μF capacitor between analog input and V<sub>REFL</sub>). Failure to observe these guidelines may result in system or microcontroller noise causing accuracy errors which will vary based on board layout and the type and magnitude of the activity.

<sup>2</sup> This is the conversion time for subsequent conversions in continuous convert mode. Actual conversion time for single conversions or the first conversion in continuous mode is extended by one ATD clock cycle and 2 bus cycles due to starting the conversion and setting the CCF flag. The total conversion time in Bus Cycles for a conversion is:

SC Bus Cycles = ((PRS+1)\*2) \* (28+1) + 2 CC Bus Cycles = ((PRS+1)\*2) \* (28)

- <sup>3</sup> R<sub>AS</sub> is the real portion of the impedance of the network driving the analog input pin. Values greater than this amount may not fully charge the input circuitry of the ATD resulting in accuracy error.

- <sup>4</sup> Analog input must be between V<sub>REFL</sub> and V<sub>REFH</sub> for valid conversion. Values greater than V<sub>REFH</sub> will convert to \$3FF less the full scale error (E<sub>FS</sub>).

- <sup>5</sup> The resolution is the ideal step size or  $1LSB = (V_{REFH} V_{REFL})/1024$

- <sup>6</sup> Differential non-linearity is the difference between the current code width and the ideal code width (1LSB). The current code width is the difference in the transition voltages to and from the current code.

- <sup>7</sup> Integral non-linearity is the difference between the transition voltage to the current code and the adjusted ideal transition voltage for the current code. The adjusted ideal transition voltage is (Current Code–1/2)\*(1/((V<sub>REFH</sub>+E<sub>FS</sub>)–(V<sub>REFL</sub>+E<sub>ZS</sub>))).

- <sup>8</sup> Zero-scale error is the difference between the transition to the first valid code and the ideal transition to that code. The Ideal transition voltage to a given code is (Code–1/2)\*(1/(V<sub>REFH</sub>–V<sub>REFL</sub>)).

- <sup>9</sup> Full-scale error is the difference between the transition to the last valid code and the ideal transition to that code. The ideal transition voltage to a given code is (Code–1/2)\*(1/(V<sub>REFH</sub>–V<sub>REFL</sub>)).

- <sup>10</sup> Input leakage error is error due to input leakage across the real portion of the impedance of the network driving the analog pin. Reducing the impedance of the network reduces this error.

- <sup>11</sup> Total unadjusted error is the difference between the transition voltage to the current code and the ideal straight-line transfer function. This measure of error includes inherent quantization error (1/2LSB) and circuit error (differential, integral, zero-scale, and full-scale) error. The specified value of E<sub>T</sub> assumes zero E<sub>IL</sub> (no leakage or zero real source impedance).

#### **Electrical Characteristics**

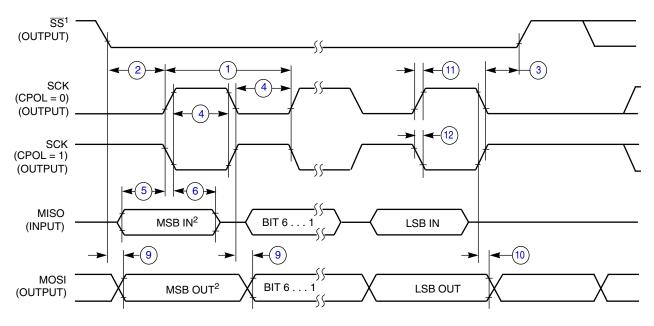

NOTES:

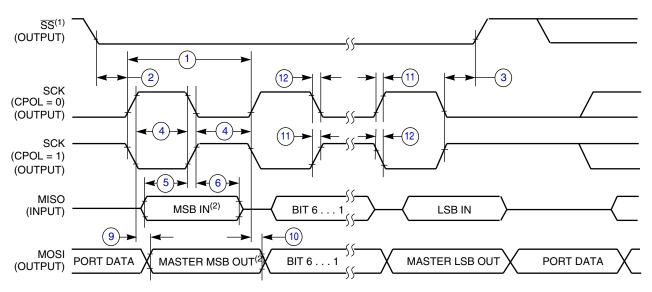

1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

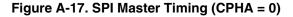

NOTES:

1.  $\overline{SS}$  output mode (DDS7 = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure A-18. SPI Master Timing (CPHA = 1)

# A.11 FLASH Specifications

This section provides details about program/erase times and program-erase endurance for the FLASH memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see Chapter 4, "Memory."

| Characteristic                                                                                       | Symbol                  | Min         | Typical | Мах        | Unit              |

|------------------------------------------------------------------------------------------------------|-------------------------|-------------|---------|------------|-------------------|

| Supply voltage for program/erase $T \le 85^{\circ}C$<br>T > 85^{\circ}C                              | V <sub>prog/erase</sub> | 1.8<br>2.1  |         | 3.6<br>3.6 | V<br>V            |

| Supply voltage for read operation<br>0 < f <sub>Bus</sub> < 8 MHz<br>0 < f <sub>Bus</sub> < 20 MHz   | V <sub>Read</sub>       | 1.8<br>2.08 |         | 3.6<br>3.6 | v                 |

| Internal FCLK frequency <sup>1</sup>                                                                 | f <sub>FCLK</sub>       | 150         |         | 200        | kHz               |

| Internal FCLK period (1/FCLK)                                                                        | t <sub>Fcyc</sub>       | 5           |         | 6.67       | μs                |

| Byte program time (random location) <sup>(2)</sup>                                                   | t <sub>prog</sub>       |             | 9       |            | t <sub>Fcyc</sub> |

| Byte program time (burst mode) <sup>(2)</sup>                                                        | t <sub>Burst</sub>      | 4           |         |            | t <sub>Fcyc</sub> |

| Page erase time <sup>2</sup>                                                                         | t <sub>Page</sub>       | 4000        |         |            | t <sub>Fcyc</sub> |

| Mass erase time <sup>(2)</sup>                                                                       | t <sub>Mass</sub>       | 20,000      |         |            | t <sub>Fcyc</sub> |

| Byte program current <sup>3</sup>                                                                    | RI <sub>DDBP</sub>      | _           | 4       |            | mA                |

| Page erase current <sup>3</sup>                                                                      | RI <sub>DDPE</sub>      | _           | 6       |            | mA                |

| Program/erase endurance <sup>4</sup><br>$T_L$ to $T_H = -40^{\circ}C$ to +125°C<br>$T = 25^{\circ}C$ |                         | 10,000      | 100,000 |            | cycles            |

| Data retention <sup>5</sup>                                                                          | t <sub>D_ret</sub>      | 15          | 100     |            | years             |

<sup>1</sup> The frequency of this clock is controlled by a software setting.

<sup>2</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

- <sup>3</sup> The program and erase currents are additional to the standard run  $I_{DD}$ . These values were measured at room temperatures with  $V_{DD}$  = 3.0 V, bus frequency = 4.0 MHz.

- <sup>4</sup> Typical endurance for FLASH was evaluated for this product family on the 9S12Dx64. For additional information on how Freescale Semiconductor defines typical endurance, please refer to Engineering Bulletin EB619/D, *Typical Endurance for Nonvolatile Memory*.

- <sup>5</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines typical data retention, please refer to Engineering Bulletin EB618/D, *Typical Data Retention for Nonvolatile Memory.*

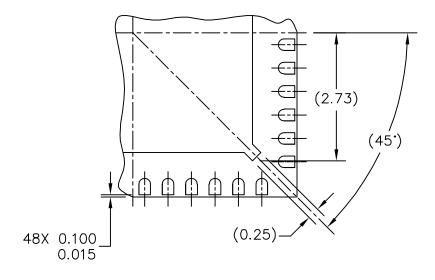

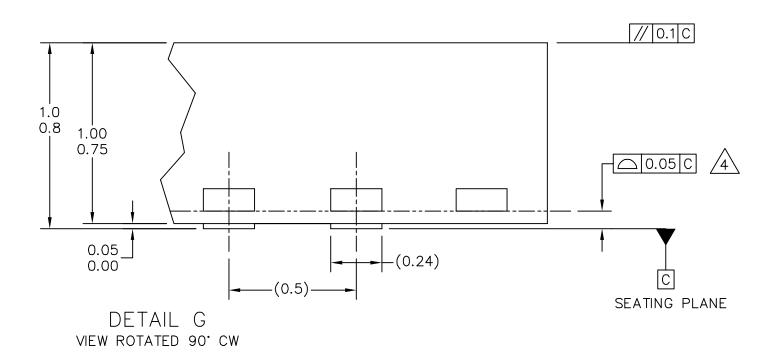

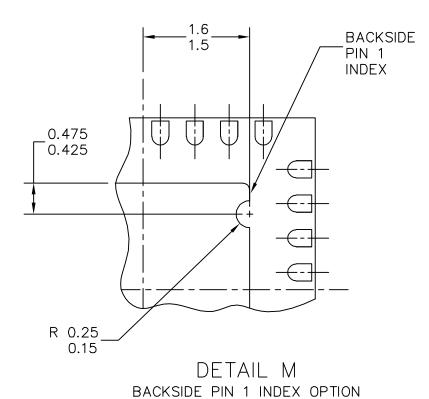

DETAIL M PREFERED PIN 1 BACKSIDE IDENTIFIER

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLINE   |                               | PRINT VERSION NOT TO SCALE |        |

|---------------------------------------------------------|----------------------|-------------------------------|----------------------------|--------|

| TITLE: THERMALLY ENHANCED QUAD                          |                      | DOCUMENT NO: 98ARH99048A      |                            | REV: F |

| FLAT NON-LEADED PACKA                                   | CASE NUMBER: 1314-05 |                               | 05 DEC 2005                |        |

| 48 TERMINAL, 0.5 PITCH (7                               | ′ X / X 1)           | STANDARD: JEDEC-MO-220 VKKD-2 |                            | 2      |

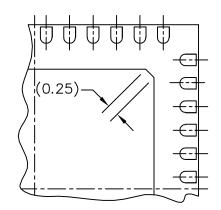

DETAIL M BACKSIDE PIN 1 INDEX OPTION

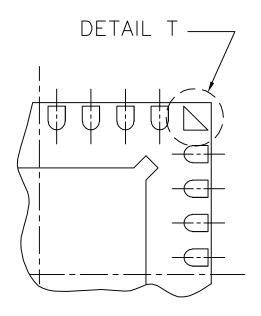

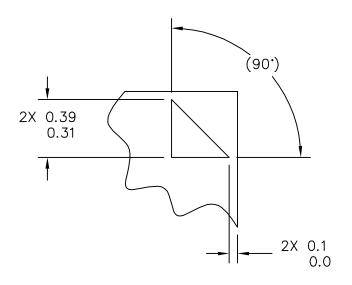

DETAIL T BACKSIDE PIN 1 INDEX OPTION

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                                               | MECHANICAL OUTLINE |                               | PRINT VERSION NOT TO SCALE |             |

|-----------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------|----------------------------|-------------|

| TITLE: THERMALLY ENHANCED QUAD<br>FLAT NON-LEADED PACKAGE (QFN)<br>32 TERMINAL, 0.5 PITCH (5 X 5 X 1)<br>CASE OUTLINE |                    | DOCUMENT NO: 98ARH99035A      |                            | REV: J      |

|                                                                                                                       |                    | CASE NUMBER: 1311-06          |                            | 17 MAR 2006 |

|                                                                                                                       |                    | STANDARD: JEDEC-MO-220 VHHD-2 |                            |             |

#### How to Reach Us:

#### USA/Europe/Locations not listed:

Freescale Semiconductor Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

#### Japan:

Freescale Semiconductor Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku Tokyo 106-8573, Japan 81-3-3440-3569

#### Asia/Pacific:

Freescale Semiconductor H.K. Ltd. 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong 852-26668334

#### Learn More: For more information about Freescale Semiconductor products, please visit http://www.freescale.com

MC9S08GT16A Rev. 1 7/2006 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2004. All rights reserved.