Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | R8C                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20MHz                                                                          |

| Connectivity               | SIO, SSU, UART/USART                                                           |

| Peripherals                | LED, POR, Voltage Detect, WDT                                                  |

| Number of I/O              | 13                                                                             |

| Program Memory Size        | 16KB (16K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                |

| Supplier Device Package    | 20-LSSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f21154sp-u0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# R8C/14 Group, R8C/15 Group SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

REJ03B0102-0200 Rev.2.00 Jan 30, 2006

## 1. Overview

This MCU is built using the high-performance silicon gate CMOS process using a R8C/Tiny Series CPU core and is packaged in a 20-pin plastic molded LSSOP. This MCU operates using sophisticated instructions featuring a high level of instruction efficiency. With 1 Mbyte of address space, it is capable of executing instructions at high speed.

Furthermore, the data flash ROM (1KB x 2blocks) is embedded in the R8C/15 group.

The difference between R8C/14 and R8C/15 groups is only the existence of the data flash ROM. Their peripheral functions are the same.

## 1.1 Applications

Electric household appliance, office equipment, housing equipment (sensor, security), general industrial equipment, audio, etc.

## 1.2 Performance Overview

Table 1.1 lists the Performance Outline of the R8C/14 Group and Table 1.2 lists the Performance Outline of the R8C/15 Group.

Table 1.1 Performance Outline of the R8C/14 Group

|                 | Item                         | Performance                                                    |

|-----------------|------------------------------|----------------------------------------------------------------|

| CPU             | Number of Basic Instructions |                                                                |

|                 | Minimum Instruction          | 50ns(f(XIN)=20MHz, VCC=3.0 to 5.5V)                            |

|                 | Execution Time               | 100ns(f(XIN)=10MHz, VCC=2.7 to 5.5V)                           |

|                 | Operating Mode               | Single-chip                                                    |

|                 | Memory Space                 | 1 Mbyte                                                        |

|                 | Memory Capacity              | See Table 1.3 R8C/14 Group Product Information                 |

| Peripheral      | Port                         | I/O port : 13 pins (including LED drive port),                 |

| Function        |                              | Input: 2 pins                                                  |

|                 | LED Drive Port               | I/O port: 4 pins                                               |

|                 | Timer                        | Timer X: 8 bits x 1 channel, Timer Z: 8 bits x 1 channel       |

|                 |                              | (Each timer equipped with 8-bit prescaler)                     |

|                 |                              | Timer C: 16 bits x 1 channel                                   |

|                 |                              | (Circuits of input capture and output compare)                 |

|                 | Serial Interface             | 1 channel                                                      |

|                 |                              | Clock synchronous serial I/O, UART                             |

|                 | Chip-Select Clock            | 1 channel                                                      |

|                 | Synchronous Serial I/O       |                                                                |

|                 | (SSU)                        |                                                                |

|                 | A/D Converter                | 10-bit A/D converter: 1 circuit, 4 channels                    |

|                 | Watchdog Timer               | 15 bits ×1 channel (with prescaler)                            |

|                 |                              | Reset start selectable, Count source protection mode           |

|                 | Interrupt                    | Internal: 9 factors, External: 4 factors, Software: 4 factors, |

|                 | ·                            | Priority level: 7 levels                                       |

|                 | Clock Generation Circuit     | 2 circuits                                                     |

|                 |                              | Main clock oscillation circuit (Equipped with a built-in       |

|                 |                              | feedback resistor)                                             |

|                 |                              | On-chip oscillator (high speed, low speed)                     |

|                 |                              | Equipped with frequency adjustment function on high-           |

|                 |                              | speed on-chip oscillator                                       |

|                 | Oscillation Stop Detection   | Main clock oscillation stop detection function                 |

|                 | Function                     | Thair order decimation dep added for randien                   |

|                 | Voltage Detection Circuit    | Included                                                       |

|                 | Power-On Reset Circuit       | Included                                                       |

| Electric        | Supply Voltage               | VCC=3.0 to 5.5V (f(XIN)=20MHz)                                 |

| Characteristics | 3 1 1 7 3 3 3                | VCC=2.7 to 5.5V (f(XIN)=10MHz)                                 |

|                 | Power Consumption            | Typ. 9mA (VCC=5.0V, f(XIN)=20MHz)                              |

|                 |                              | Typ. 5mA (VCC=3.0V, f(XIN)=10MHz)                              |

|                 |                              | Typ. 35μA (VCC=3.0V, wait mode, peripheral clock off)          |

|                 |                              | Typ. 0.7μA (VCC=3.0V, wait mode)                               |

| Flash Memory    | Program/Erase Supply         | VCC=2.7 to 5.5V                                                |

| I lasti wellory | Voltage                      | V00-2.7 t0 0.0 V                                               |

|                 | Program/Erase Endurance      | 100 times                                                      |

| Operating Ambi  | ent Temperature              | -20 to 85°C                                                    |

|                 | on romporatore               | -40 to 85°C (D Version)                                        |

| Package         |                              | 20-pin plastic mold LSSOP                                      |

| i ackaye        |                              | 20 pin piastic mola 2000i                                      |

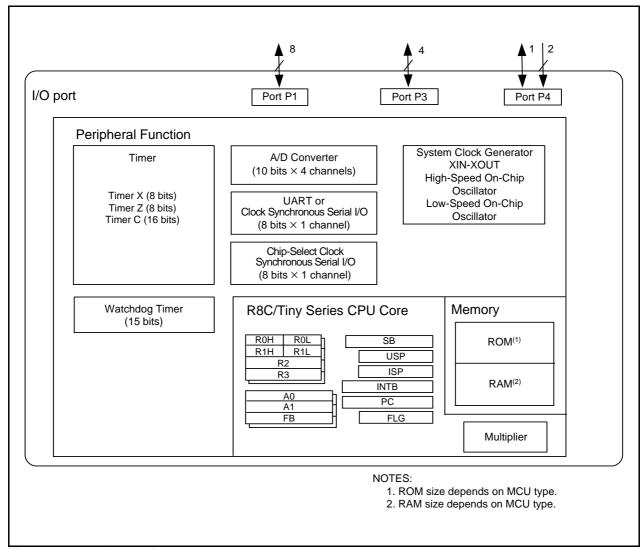

## 1.3 Block Diagram

Figure 1.1 shows a Block Diagram.

Figure 1.1 Block Diagram

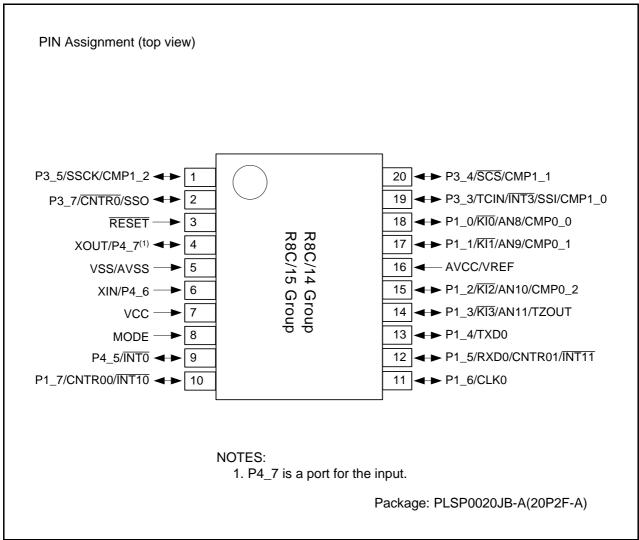

## 1.5 Pin Assignments

Figure 1.4 shows the PLSP0020JB-A Package Pin Assignment (top view).

Figure 1.4 PLSP0020JB-A Package Pin Assignment (top view)

Table 1.6 Pin Name Information by Pin Number

|               |                |      |           | I/O Pin of Peripheral Function |                     |                                                        |                  |  |  |

|---------------|----------------|------|-----------|--------------------------------|---------------------|--------------------------------------------------------|------------------|--|--|

| Pin<br>Number | Control<br>Pin | Port | Interrupt | Timer                          | Serial<br>Interface | Clock<br>Synchronous<br>Serial I/O with<br>Chip Select | A/D<br>Converter |  |  |

| 1             |                | P3_5 |           | CMP1_2                         |                     | SSCK                                                   |                  |  |  |

| 2             |                | P3_7 |           | CNTR0                          |                     | SSO                                                    |                  |  |  |

| 3             | RESET          |      |           |                                |                     |                                                        |                  |  |  |

| 4             | XOUT           | P4_7 |           |                                |                     |                                                        |                  |  |  |

| 5             | VSS/AVSS       |      |           |                                |                     |                                                        |                  |  |  |

| 6             | XIN            | P4_6 |           |                                |                     |                                                        |                  |  |  |

| 7             | VCC            |      |           |                                |                     |                                                        |                  |  |  |

| 8             | MODE           |      |           |                                |                     |                                                        |                  |  |  |

| 9             |                | P4_5 | ĪNT0      |                                |                     |                                                        |                  |  |  |

| 10            |                | P1_7 | INT10     | CNTR00                         |                     |                                                        |                  |  |  |

| 11            |                | P1_6 |           |                                | CLK0                |                                                        |                  |  |  |

| 12            |                | P1_5 | INT11     | CNTR01                         | RXD0                |                                                        |                  |  |  |

| 13            |                | P1_4 |           |                                | TXD0                |                                                        |                  |  |  |

| 14            |                | P1_3 | KI3       | TZOUT                          |                     |                                                        | AN11             |  |  |

| 15            |                | P1_2 | KI2       | CMP0_2                         |                     |                                                        | AN10             |  |  |

| 16            | AVCC/VREF      |      |           |                                |                     |                                                        |                  |  |  |

| 17            |                | P1_1 | KI1       | CMP0_1                         |                     |                                                        | AN9              |  |  |

| 18            |                | P1_0 | KI0       | CMP0_0                         |                     |                                                        | AN8              |  |  |

| 19            |                | P3_3 | ĪNT3      | TCIN/CMP1_0                    |                     | SSI                                                    |                  |  |  |

| 20            |                | P3_4 |           | CMP1_1                         |                     | SCS                                                    |                  |  |  |

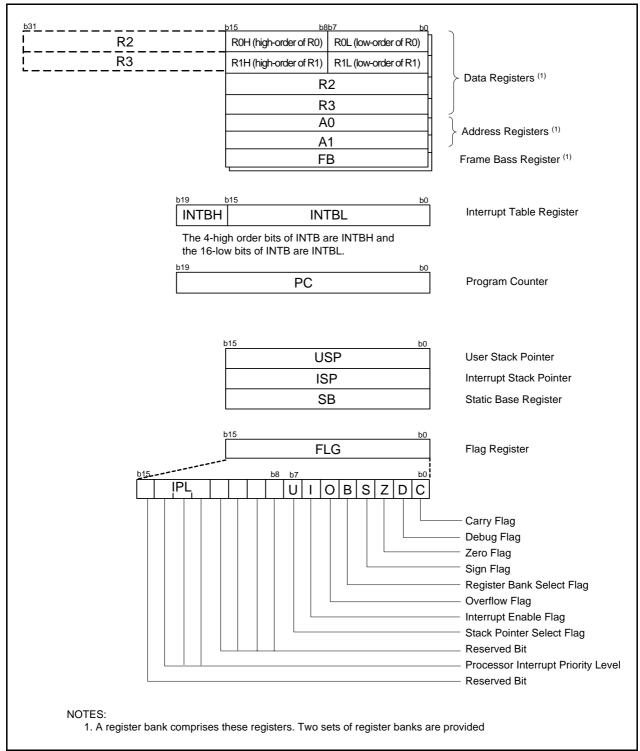

## 2. Central Processing Unit (CPU)

Figure 2.1 shows the CPU Register. The CPU contains 13 registers. Of these, R0, R1, R2, R3, A0, A1 and FB comprise a register bank. Two sets of register banks are provided.

Figure 2.1 CPU Register

## 2.1 Data Registers (R0, R1, R2 and R3)

R0 is a 16-bit register for transfer, arithmetic and logic operations. The same applies to R1 to R3. The R0 can be split into high-order bit (R0H) and low-order bit (R0L) to be used separately as 8-bit data registers. The same applies to R1H and R1L as R0H and R0L. R2 can be combined with R0 to be used as a 32-bit data register (R2R0). The same applies to R3R1 as R2R0.

## 2.2 Address Registers (A0 and A1)

A0 is a 16-bit register for address register indirect addressing and address register relative addressing. They also are used for transfer, arithmetic and logic operations. The same applies to A1 as A0. A0 can be combined with A0 to be used as a 32-bit address register (A1A0).

## 2.3 Frame Base Register (FB)

FB is a 16-bit register for FB relative addressing.

## 2.4 Interrupt Table Register (INTB)

INTB is a 20-bit register indicates the start address of an interrupt vector table.

## 2.5 Program Counter (PC)

PC, 20 bits wide, indicates the address of an instruction to be executed.

### 2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

The stack pointer (SP), USP and ISP, are 16 bits wide each. The U flag of FLG is used to switch between USP and ISP.

## 2.7 Static Base Register (SB)

SB is a 16-bit register for SB relative addressing.

## 2.8 Flag Register (FLG)

FLG is a 11-bit register indicating the CPU state.

## 2.8.1 **Carry Flag (C)**

The C flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic logic unit.

## 2.8.2 Debug Flag (D)

The D flag is for debug only. Set to "0".

## 2.8.3 **Zero Flag (Z)**

The Z flag is set to "1" when an arithmetic operation resulted in 0; otherwise, "0".

## 2.8.4 Sign Flag (S)

The S flag is set to "1" when an arithmetic operation resulted in a negative value; otherwise, "0".

## 2.8.5 Register Bank Select Flag (B)

The register bank 0 is selected when the B flag is "0". The register bank 1 is selected when this flag is set to "1".

## 2.8.6 Overflow Flag (O)

The O flag is set to "1" when the operation resulted in an overflow; otherwise, "0".

#### 2.8.7 Interrupt Enable Flag (I Flag)

The I flag enables a maskable interrupt.

An interrupt is disabled when the I flag is set to "0", and are enabled when the I flag is set to "1". The I flag is set to "0" when an interrupt request is acknowledged.

#### 2.8.8 Stack Pointer Select Flag (U Flag)

ISP is selected when the U flag is set to "0", USP is selected when the U flag is set to "1". The U flag is set to "0" when a hardware interrupt request is acknowledged or the INT instruction of software interrupt numbers 0 to 31 is executed.

#### 2.8.9 **Processor Interrupt Priority Level (IPL)**

IPL, 3 bits wide, assigns processor interrupt priority levels from level 0 to level 7. If a requested interrupt has greater priority than IPL, the interrupt is enabled.

#### 2.8.10 **Reserved Bit**

When write to this bit, set to "0". When read, its content is indeterminate.

#### **Special Function Register (SFR)** 4.

SFR (Special Function Register) is the control register of peripheral functions. Tables 4.1 to 4.4 list the SFR information.

SFR Information(1)(1) Table 4.1

| A -1 -1        | Devision Devision                                | O. made at | A 64 4                   |

|----------------|--------------------------------------------------|------------|--------------------------|

| Address        | Register                                         | Symbol     | After reset              |

| 0000h          |                                                  |            |                          |

| 0001h          |                                                  |            |                          |

| 0002h          |                                                  |            |                          |

| 0003h          |                                                  |            |                          |

| 0004h          | Processor Mode Register 0                        | PM0        | 00h                      |

| 0005h          | Processor Mode Register 1                        | PM1        | 00h                      |

| 0006h          | System Clock Control Register 0                  | CM0        | 01101000b                |

| 0007h          | System Clock Control Register 1                  | CM1        | 00100000b                |

| 0008h          |                                                  |            |                          |

| 0009h          | Address Match Interrupt Enable Register          | AIER       | 00h                      |

| 000Ah          | Protect Register                                 | PRCR       | 00h                      |

| 000Bh          |                                                  |            |                          |

| 000Ch          | Oscillation Stop Detection Register              | OCD        | 00000100b                |

| 000Dh          | Watchdog Timer Reset Register                    | WDTR       | XXh                      |

| 000Eh          | Watchdog Timer Start Register                    | WDTS       | XXh                      |

| 000Fh          | Watchdog Timer Control Register                  | WDC        | 00011111b                |

| 0010h          | Address Match Interrupt Register 0               | RMAD0      | 00h                      |

| 0011h          | 7 radioso mator monaper rogistor o               | 120        | 00h                      |

| 0012h          |                                                  |            | X0h                      |

| 0012h          |                                                  |            | Xon                      |

| 0013h          | Address Match Interrupt Register 1               | RMAD1      | 00h                      |

| 0014H          | Tradicas Materialicitus register 1               | KIVIAD I   | 00h                      |

| 0015h          |                                                  |            |                          |

| 0016h<br>0017h |                                                  |            | X0h                      |

|                |                                                  |            |                          |

| 0018h          |                                                  |            |                          |

| 0019h          |                                                  |            |                          |

| 001Ah          |                                                  |            |                          |

| 001Bh          |                                                  |            |                          |

| 001Ch          | Count Source Protection Mode Register            | CSPR       | 00h                      |

| 001Dh          |                                                  |            |                          |

| 001Eh          | INT0 Input Filter Select Register                | INT0F      | 00h                      |

| 001Fh          | · · · · · · · · · · · · · · · · · · ·            |            |                          |

| 0020h          | High-Speed On-Chip Oscillator Control Register 0 | HRA0       | 00h                      |

| 0021h          | High-Speed On-Chip Oscillator Control Register 1 | HRA1       | When shipping            |

| 0022h          | High-Speed On-Chip Oscillator Control Register 2 | HRA2       | 00h                      |

| 0023h          | The speed on only occurate control regions 2     |            | 00.1                     |

| 0020           |                                                  |            |                          |

| 002Ah          |                                                  |            |                          |

| 002/th         |                                                  |            |                          |

| 002Dh          |                                                  |            |                          |

| 002Ch          |                                                  |            |                          |

| 002DH          |                                                  |            |                          |

|                |                                                  |            |                          |

| 002Fh          |                                                  |            |                          |

| 0030h          |                                                  |            | 00004063                 |

| 0031h          | Voltage Detection Register 1 <sup>(2)</sup>      | VCA1       | 00001000b                |

| 0032h          | Voltage Detection Register 2 <sup>(2)</sup>      | VCA2       | 00h <sup>(3)</sup>       |

|                |                                                  |            | 0100000b(4)              |

| 0033h          |                                                  | İ          |                          |

| 0034h          |                                                  |            |                          |

| 0035h          |                                                  |            |                          |

| 0036h          | Voltage Monitor 1 Circuit Control Register (2)   | VW1C       | 0000X000b <sup>(3)</sup> |

|                | Total State of Control Mogister Co               | 1          | 0100X000b <sup>(4)</sup> |

| 0037h          | Voltage Monitor 2 Circuit Control Register (5)   | VW2C       | 00h                      |

|                | voltage ivionitor 2 Circuit Control Register (9) | VVVZC      | OUII                     |

| 0038h          |                                                  |            |                          |

| 0039h          |                                                  |            |                          |

| 003Ah          |                                                  |            |                          |

| 003Bh          |                                                  |            |                          |

| 003Ch          |                                                  |            |                          |

| 003Dh          |                                                  |            |                          |

| 003Eh          |                                                  |            |                          |

|                |                                                  |            |                          |

### X: Undefined

- 1. Blank spaces are reserved. No access is allowed.

- 2. Software reset, the watchdog timer reset or the voltage monitor 2 reset does not affect this register.

- 3. Owing to Hardware reset.

- 4. Owing to Power-on reset or the voltage monitor 1 reset.

- 5. Software reset, the watchdog timer reset or the voltage monitor 2 reset does not affect the b2 and b3.

SFR Information(3)(1) Table 4.3

|                                                                                                                                                                                           | Register                                                                                                                                                                       | Symbol                                      | After reset                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------|

| Address<br>0080h                                                                                                                                                                          | Timer Z Mode Register                                                                                                                                                          | TZMR                                        | 00h                                                  |

| 0081h                                                                                                                                                                                     | Timer Z Wode Register                                                                                                                                                          | 1 ZIVII (                                   | 0011                                                 |

| 0082h                                                                                                                                                                                     |                                                                                                                                                                                |                                             |                                                      |

| 0083h                                                                                                                                                                                     |                                                                                                                                                                                |                                             |                                                      |

|                                                                                                                                                                                           | Times 7 Westerform Outrast Control Deviator                                                                                                                                    | DUM                                         | 001-                                                 |

| 0084h                                                                                                                                                                                     | Timer Z Waveform Output Control Register                                                                                                                                       | PUM                                         | 00h                                                  |

| 0085h                                                                                                                                                                                     | Prescaler Z Register                                                                                                                                                           | PREZ                                        | FFh                                                  |

| 0086h                                                                                                                                                                                     | Timer Z Secondary Register                                                                                                                                                     | TZSC                                        | FFh                                                  |

| 0087h                                                                                                                                                                                     | Timer Z Primary Register                                                                                                                                                       | TZPR                                        | FFh                                                  |

| 0088h                                                                                                                                                                                     |                                                                                                                                                                                |                                             |                                                      |

| 0089h                                                                                                                                                                                     |                                                                                                                                                                                |                                             |                                                      |

| 008Ah                                                                                                                                                                                     | Timer Z Output Control Register                                                                                                                                                | TZOC                                        | 00h                                                  |

| 008Bh                                                                                                                                                                                     | Timer X Mode Register                                                                                                                                                          | TXMR                                        | 00h                                                  |

| 008Ch                                                                                                                                                                                     | Prescaler X Register                                                                                                                                                           | PREX                                        | FFh                                                  |

| 008Dh                                                                                                                                                                                     | Timer X Register                                                                                                                                                               | TX                                          | FFh                                                  |

| 008Eh                                                                                                                                                                                     | Timer Count Source Setting Register                                                                                                                                            | TCSS                                        | 00h                                                  |

| 008Fh                                                                                                                                                                                     | <u> </u>                                                                                                                                                                       |                                             |                                                      |

| 0090h                                                                                                                                                                                     | Timer C Register                                                                                                                                                               | тс                                          | 00h                                                  |

| 0091h                                                                                                                                                                                     |                                                                                                                                                                                | 1.0                                         | 00h                                                  |

| 0092h                                                                                                                                                                                     |                                                                                                                                                                                |                                             | 0011                                                 |

| 0092h                                                                                                                                                                                     |                                                                                                                                                                                |                                             |                                                      |

|                                                                                                                                                                                           |                                                                                                                                                                                |                                             |                                                      |

| 0094h                                                                                                                                                                                     | <del> </del>                                                                                                                                                                   |                                             |                                                      |

| 0095h                                                                                                                                                                                     | Futured brook Facility Devictor                                                                                                                                                | I INITENI                                   | Look                                                 |

| 0096h                                                                                                                                                                                     | External Input Enable Register                                                                                                                                                 | INTEN                                       | 00h                                                  |

| 0097h                                                                                                                                                                                     |                                                                                                                                                                                |                                             |                                                      |

| 0098h                                                                                                                                                                                     | Key Input Enable Register                                                                                                                                                      | KIEN                                        | 00h                                                  |

| 0099h                                                                                                                                                                                     |                                                                                                                                                                                |                                             |                                                      |

| 009Ah                                                                                                                                                                                     | Timer C Control Register 0                                                                                                                                                     | TCC0                                        | 00h                                                  |

| 009Bh                                                                                                                                                                                     | Timer C Control Register 1                                                                                                                                                     | TCC1                                        | 00h                                                  |

| 009Ch                                                                                                                                                                                     | Capture, Compare 0 Register                                                                                                                                                    | TMO                                         | 00h                                                  |

| 009Dh                                                                                                                                                                                     | <b>†</b> • • • • • • • • • • • • • • • • • • •                                                                                                                                 |                                             | 00h <sup>(2)</sup>                                   |

| 009Eh                                                                                                                                                                                     | Compare 1 Register                                                                                                                                                             | TM1                                         | FFh                                                  |

| 009Fh                                                                                                                                                                                     |                                                                                                                                                                                |                                             | FFh                                                  |

| 00A0h                                                                                                                                                                                     | UART0 Transmit/Receive Mode Register                                                                                                                                           | U0MR                                        | 00h                                                  |

| 00A011                                                                                                                                                                                    | UARTO Bit Rate Register                                                                                                                                                        | U0BRG                                       | XXh                                                  |

| 00A111                                                                                                                                                                                    | UART0 Transmit Buffer Register                                                                                                                                                 | UOTB                                        | XXh                                                  |

| 00A2H                                                                                                                                                                                     | - OAKTO Hansilii Buller Kegister                                                                                                                                               | 0018                                        | XXh                                                  |

|                                                                                                                                                                                           | HARTO Transmit/Passing Control Basistan C                                                                                                                                      | 11000                                       |                                                      |

| 00A4h                                                                                                                                                                                     | UART0 Transmit/Receive Control Register 0                                                                                                                                      | U0C0<br>U0C1                                | 00001000b<br>00000010b                               |

| 00A5h                                                                                                                                                                                     | UART0 Transmit/Receive Control Register 1                                                                                                                                      |                                             | 1.000000100                                          |

| 00A6h                                                                                                                                                                                     | I I I A P I () Pacalva Buttar Pagistar                                                                                                                                         |                                             |                                                      |

| 00A7h                                                                                                                                                                                     | UART0 Receive Buffer Register                                                                                                                                                  | UORB                                        | XXh                                                  |

|                                                                                                                                                                                           | OAKTO Receive Bullet Register                                                                                                                                                  |                                             |                                                      |

| 00A8h                                                                                                                                                                                     | OAKTO Receive Bullet Register                                                                                                                                                  |                                             | XXh                                                  |

| 00A8h<br>00A9h                                                                                                                                                                            | OAKTO Receive Bullet Register                                                                                                                                                  |                                             | XXh                                                  |

| 00A9h<br>00AAh                                                                                                                                                                            | OAKTO Receive Bullet Register                                                                                                                                                  |                                             | XXh                                                  |

| 00A9h                                                                                                                                                                                     | OAKTO Necewe Bullet Kegister                                                                                                                                                   |                                             | XXh                                                  |

| 00A9h<br>00AAh                                                                                                                                                                            | DARTO Receive Bullet Register                                                                                                                                                  |                                             | XXh                                                  |

| 00A9h<br>00AAh<br>00ABh                                                                                                                                                                   | DARTO Receive Bullet Register                                                                                                                                                  |                                             | XXh                                                  |

| 00A9h<br>00AAh<br>00ABh<br>00ACh                                                                                                                                                          | DARTO Receive Bullet Register                                                                                                                                                  |                                             | XXh                                                  |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh                                                                                                                                                 | OAKTO Necewe Bullet Kegister                                                                                                                                                   |                                             | XXh                                                  |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AFh                                                                                                                               |                                                                                                                                                                                | UORB                                        | XXh<br>XXh                                           |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AFh<br>00B0h                                                                                                                      | UART Transmit/Receive Control Register 2                                                                                                                                       |                                             | XXh                                                  |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AFh<br>00B0h                                                                                                                      |                                                                                                                                                                                | UORB                                        | XXh<br>XXh                                           |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AFh<br>00B0h<br>00B1h                                                                                                             |                                                                                                                                                                                | UORB                                        | XXh<br>XXh                                           |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AFh<br>00B0h<br>00B1h<br>00B2h                                                                                                    |                                                                                                                                                                                | UORB                                        | XXh<br>XXh                                           |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ADh<br>00AEh<br>00AFh<br>00B0h<br>00B1h<br>00B2h<br>00B3h                                                                                           |                                                                                                                                                                                | UORB                                        | XXh<br>XXh                                           |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ACh<br>00AEh<br>00AEh<br>00B0h<br>00B1h<br>00B3h<br>00B3h<br>00B4h                                                                                  |                                                                                                                                                                                | UORB                                        | XXh<br>XXh                                           |

| 00A9h<br>00AAh<br>00ABh<br>00ACh<br>00ACh<br>00AEh<br>00AEh<br>00B0h<br>00B1h<br>00B3h<br>00B3h<br>00B4h<br>00B5h                                                                         |                                                                                                                                                                                | UORB                                        | XXh<br>XXh                                           |

| 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00AFh 00BOh 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h                                                                                                       | UART Transmit/Receive Control Register 2                                                                                                                                       | UCON                                        | XXh<br>XXh                                           |

| 00A9h 00AAh 00ABh 00ACh 00ACh 00ACh 00AFh 00B0h 00B1h 00B2h 00B3h 00B4h 00B5h 00B6h 00B7h 00B8h                                                                                           | UART Transmit/Receive Control Register 2  SS Control Register H                                                                                                                | UCON                                        | XXh<br>XXh<br>00h                                    |

| 00A9h 00AAh 00ABh 00ACh 00ACh 00ADh 00AEh 00BOh | UART Transmit/Receive Control Register 2  SS Control Register H SS Control Register L                                                                                          | UCON  UCON  SSCRH SSCRL                     | XXh<br>XXh<br>00h<br>00h<br>7Dh                      |

| 00A9h 00AAh 00ABh 00ACh 00ADh 00AEh 00AEh 00B0h 00B1h 00B3h 00B4h 00B5h 00B6h 00B7h 00B8h 00B8h 00B8h                                                                                     | UART Transmit/Receive Control Register 2  SS Control Register H SS Control Register L SS Mode Register                                                                         | UCON  UCON  SSCRH SSCRL SSMR                | XXh<br>XXh<br>00h<br>00h<br>7Dh<br>18h               |

| 00A9h 00AAh 00ABh 00ACh 00ACh 00ADh 00AEh 00BOh | UART Transmit/Receive Control Register 2  SS Control Register H SS Control Register L SS Mode Register SS Enable Register                                                      | UCON  UCON  SSCRH SSCRL SSMR SSER           | XXh<br>XXh<br>00h<br>00h<br>7Dh                      |

| 00A9h 00AAh 00ABh 00ACh 00ADh 00AEh 00AEh 00B0h 00B1h 00B3h 00B4h 00B5h 00B6h 00B7h 00B8h 00B8h 00B8h                                                                                     | UART Transmit/Receive Control Register 2  SS Control Register H SS Control Register L SS Mode Register                                                                         | UCON  UCON  SSCRH SSCRL SSMR                | XXh<br>XXh<br>00h<br>00h<br>7Dh<br>18h               |

| 00A9h 00AAh 00ABh 00ACh 00ADh 00AEh 00AEh 00BOh 00BOh 00BOh 00BSh 00BSh 00BSh 00BSh 00BSh 00BSh                                                                                           | UART Transmit/Receive Control Register 2  SS Control Register H SS Control Register L SS Mode Register SS Enable Register SS Status Register SS Mode Register SS Mode Register | UCON  UCON  SSCRH SSCRL SSMR SSER           | XXh XXh  Ooh  Ooh  TDh  18h  Ooh                     |

| 00A9h 00AAh 00AAh 00ACh 00ACh 00ACh 00ACh 00AEh 00BCh 00B1h 00B2h 00B3h 00B6h 00B7h 00B8h 00B9h 00B9h 00BAh 00BBh                                                                         | UART Transmit/Receive Control Register 2  SS Control Register H SS Control Register L SS Mode Register SS Enable Register SS Enable Register SS Status Register                | UCON  UCON  SSCRH SSCRL SSMR SSER SSER SSSR | XXh<br>XXh<br>00h<br>00h<br>7Dh<br>18h<br>00h<br>00h |

### X: Undefined

- Blank spaces are reserved. No access is allowed.

When output compare mode (the TCC13 bit in the TCC1 register = 1) is selected, the value after reset is "FFFFh".

SFR Information(4)(1) Table 4.4

| Addroce          | Register                                | Symbol | After reset      |

|------------------|-----------------------------------------|--------|------------------|

| Address<br>00C0h | A/D Register                            | AD     | XXh              |

| 00C1h            | A/D Negister                            | AD     | XXh              |

| 00C2h            |                                         |        | AAII             |

|                  |                                         |        |                  |

| 00C3h            |                                         |        |                  |

| 00C4h            |                                         |        |                  |

| 00C5h            |                                         |        |                  |

| 00C6h            |                                         |        |                  |

| 00C7h            |                                         |        |                  |

| 00C8h            |                                         |        |                  |

| 00C9h            |                                         |        |                  |

| 00CAh            |                                         |        |                  |

| 00CBh            |                                         |        |                  |

| 00CCh            |                                         |        |                  |

| 00CDh            |                                         |        |                  |

| 00CEh            |                                         |        |                  |

| 00CFh            |                                         |        |                  |

| 00D0h            |                                         |        |                  |

|                  |                                         |        |                  |

| 00D1h            |                                         |        |                  |

| 00D2h            |                                         |        |                  |

| 00D3h            |                                         |        |                  |

| 00D4h            | A/D Control Register 2                  | ADCON2 | 00h              |

| 00D5h            |                                         |        |                  |

| 00D6h            | A/D Control Register 0                  | ADCON0 | 00000XXXb        |

| 00D7h            | A/D Control Register 1                  | ADCON1 | 00h              |

| 00D8h            | · ·                                     |        |                  |

| 00D9h            |                                         |        |                  |

| 00DAh            |                                         |        |                  |

| 00DRh            |                                         |        |                  |

| 00DCh            |                                         |        |                  |

| 00DDh            |                                         |        |                  |

|                  |                                         |        |                  |

| 00DEh            |                                         |        |                  |

| 00DFh            |                                         |        |                  |

| 00E0h            |                                         |        |                  |

| 00E1h            | Port P1 Register                        | P1     | XXh              |

| 00E2h            |                                         |        |                  |

| 00E3h            | Port P1 Direction Register              | PD1    | 00h              |

| 00E4h            |                                         |        |                  |

| 00E5h            | Port P3 Register                        | P3     | XXh              |

| 00E6h            | - Civi o registor                       |        | 70               |

| 00E7h            | Port P3 Direction Register              | PD3    | 00h              |

| 00E8h            | Port P4 Register                        | P4     | XXh              |

| 00E9h            | 1 OIL 1 4 IVegister                     | 1 7    | XXII             |

| 00EAh            | Port P4 Direction Register              | PD4    | 00h              |

|                  | FOILE 4 DIRECTION REGISTER              | FD4    | 0011             |

| 00EBh            |                                         |        |                  |

| 00ECh            |                                         |        |                  |

| 00EDh            |                                         |        |                  |

| 00EEh            |                                         |        |                  |

| 00EFh            |                                         |        |                  |

| 00F0h            |                                         |        |                  |

| 00F1h            |                                         |        |                  |

| 00F2h            |                                         |        |                  |

| 00F3h            |                                         |        |                  |

| 00F4h            |                                         |        |                  |

| 00F5h            |                                         |        |                  |

| 00F6h            |                                         |        |                  |

| 00F7h            |                                         |        |                  |

| 00F8h            |                                         |        |                  |

| 00F9h            |                                         |        |                  |

|                  |                                         |        |                  |

| 00FAh            |                                         |        |                  |

| 00FBh            | Pull Ha Control Devictor O              | DUDO   | LOOVY0000h       |

| 00FCh            | Pull-Up Control Register 0              | PUR0   | 00XX0000b        |

| 00FDh            | Pull-Up Control Register 1              | PUR1   | XXXXXX0Xb        |

| 00FEh            | Port P1 Drive Capacity Control Register | DRR    | 00h              |

| 00FFh            | Timer C Output Control Register         | TCOUT  | 00h              |

|                  |                                         |        |                  |

| 01B3h            | Flash Memory Control Register 4         | FMR4   | 01000000b        |

| 01B4h            |                                         |        |                  |

| 01B5h            | Flash Memory Control Register 1         | FMR1   | 1000000Xb        |

| 01B6h            | ,                                       |        |                  |

| 01B7h            | Flash Memory Control Register 0         | FMR0   | 00000001b        |

| 0.0711           | aaa                                     |        | 1 223000015      |

| 0FFFFh           | Optional Function Select Register       | OFS    | (2)              |

|                  | Optional Canonion Coloct Regiotes       |        | \ <del>-</del> / |

### X: Undefined NOTES:

- Blank columns, 0100h to 01B2h and 01B8h to 02FFh are all reserved. No access is allowed.

The OFS register cannot be changed by program. Use a flash programmer to write to it.

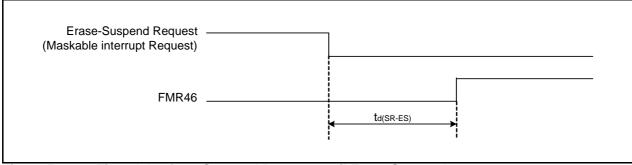

Time delay from Suspend Request until Erase Suspend Figure 5.2

Table 5.6 **Voltage Detection 1 Circuit Electrical Characteristics**

| Symbol  | Parameter                                                                    | Condition             |      | Unit |      |       |

|---------|------------------------------------------------------------------------------|-----------------------|------|------|------|-------|

| Symbol  | raidilletei                                                                  | Condition             | Min. | Тур. | Max. | Offic |

| Vdet1   | Voltage Detection Level <sup>(3)</sup>                                       |                       | 2.70 | 2.85 | 3.00 | V     |

| =       | Voltage Detection Circuit Self Power Consumption                             | VCA26 = 1, Vcc = 5.0V | =    | 600  | =    | nA    |

| td(E-A) | Waiting Time until Voltage Detection Circuit Operation Starts <sup>(2)</sup> |                       | =    | =    | 100  | μS    |

| Vccmin  | Microcomputer Operating Voltage Minimum Value                                |                       | 2.7  | -    | -    | V     |

### NOTES:

- 1. The measurement condition is Vcc = AVcc = 2.7V to 5.5V and Topr = -40°C to 85 °C.

- 2. Necessary time until the voltage detection circuit operates when setting to "1" again after setting the VCA26 bit in the VCA2 register to "0".

- 3. Hold Vdet2 > Vdet1.

Table 5.7 **Voltage Detection 2 Circuit Electrical Characteristics**

| Symbol  | Parameter                                                                    | Condition             |      | Unit |      |       |

|---------|------------------------------------------------------------------------------|-----------------------|------|------|------|-------|

| Symbol  | Farameter                                                                    | Condition             | Min. | Тур. | Max. | Offic |

| Vdet2   | Voltage Detection Level <sup>(4)</sup>                                       |                       | 3.00 | 3.30 | 3.60 | V     |

| -       | Voltage Monitor 2 Interrupt Request Generation Time <sup>(2)</sup>           |                       | -    | 40   | -    | μS    |

| =       | Voltage Detection Circuit Self Power Consumption                             | VCA27 = 1, Vcc = 5.0V | =    | 600  | =    | nA    |

| td(E-A) | Waiting Time until Voltage Detection Circuit Operation Starts <sup>(3)</sup> |                       | =    | =    | 100  | μS    |

- 1. The measurement condition is Vcc = AVcc = 2.7V to 5.5V and Topr = -40°C to 85 °C.

- 2. Time until the voltage monitor 2 interrupt request is generated since the voltage passes Vdet1.

- 3. Necessary time until the voltage detection circuit operates when setting to "1" again after setting the VCA27 bit in the VCA2 register to "0".

- 4. Hold Vdet2 > Vdet1.

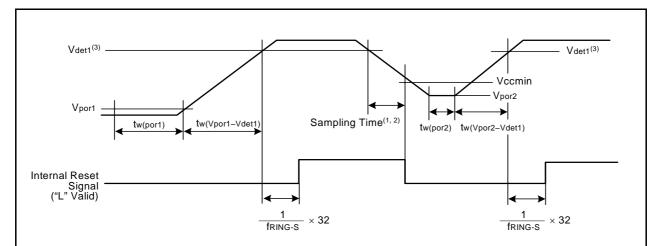

Reset Circuit Electrical Characteristics (When Using Voltage Monitor 1 Reset) Table 5.8

| Symbol          | Parameter                                         | Condition                              | Standard |      | Unit  |    |

|-----------------|---------------------------------------------------|----------------------------------------|----------|------|-------|----|

|                 |                                                   |                                        | Min.     | Тур. | Max.  |    |

| Vpor2           | Power-On Reset Valid Voltage                      | $-20^{\circ}C \leq Topr < 85^{\circ}C$ | =        | =    | Vdet1 | V  |

| tw(Vpor2-Vdet1) | Supply Voltage Rising Time When Power-On Reset is | -20°C ≤ Topr < 85°C,                   | -        | -    | 100   | ms |

|                 | Deasserted <sup>(1)</sup>                         | $t_{\text{w(por2)}} \ge 0s^{(3)}$      |          |      |       |    |

#### NOTES:

- 1. This condition is not applicable when using with  $Vcc \ge 1.0V$ .

- 2. When turning power on after the time to hold the external power below effective voltage (Vport) exceeds10s, refer to Table 5.9 Reset Circuit Electrical Characteristics (When Not Using Voltage Monitor 1 Reset).

- 3. tw(por2) is time to hold the external power below effective voltage (Vpor2).

Table 5.9 Reset Circuit Electrical Characteristics (When Not Using Voltage Monitor 1 Reset)

| Symbol          | Parameter                                                    | Condition                                                                                          | Standard |      | Unit |    |

|-----------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------|------|------|----|

|                 |                                                              |                                                                                                    | Min.     | Тур. | Max. |    |

| Vpor1           | Power-On Reset Valid Voltage                                 | -20°C ≤ Topr < 85°C                                                                                | =        | =    | 0.1  | V  |

| tw(Vpor1-Vdet1) | Supply Voltage Rising Time When Power-On Reset is Deasserted | $0^{\circ}C \leq Topr \leq 85^{\circ}C$ ,<br>$tw(por1) \geq 10s^{(2)}$                             | -        | =    | 100  | ms |

| tw(Vpor1-Vdet1) | Supply Voltage Rising Time When Power-On Reset is Deasserted | $ -20^{\circ}C \leq Topr < 0^{\circ}C, $ $ tw(por1) \geq 30s^{(2)} $                               | -        | =    | 100  | ms |

| tw(Vpor1-Vdet1) | Supply Voltage Rising Time When Power-On Reset is Deasserted | $ -20^{\circ}C \leq Topr < 0^{\circ}C, \\ tw(por1) \geq 10s^{(2)} $                                | -        | _    | 1    | ms |

| tw(Vpor1-Vdet1) | Supply Voltage Rising Time When Power-On Reset is Deasserted | $\begin{array}{l} 0^{\circ}C \leq Topr \leq 85^{\circ}C, \\ t_{W(por1)} \geq 1s^{(2)} \end{array}$ | -        | -    | 0.5  | ms |

### NOTES:

- 1. When not using the voltage monitor 1 reset, use with Vcc≥ 2.7V.

- 2. tw(por1) is time to hold the external power below effective voltage (Vpor1).

- Hold the voltage of the microcomputer operation voltage range (Vccmin or above) within sampling time.

A sampling clock can be selected. Refer to 6. Voltage Detection Circuit of Hardware Manual for details.

Vdet1 indicates the voltage detection level of the voltage detection 1 circuit. Refer to 6. Voltage Detection Circuit of Hardware Manual for details.

Figure 5.3 **Reset Circuit Electrical Characteristics**

**Table 5.10 High-speed On-Chip Oscillator Circuit Electrical Characteristics**

| Council of |                                                                                  | Condition                                   |      | Lloit |      |      |

|------------|----------------------------------------------------------------------------------|---------------------------------------------|------|-------|------|------|

| Symbol     |                                                                                  | Condition                                   | Min. | Тур.  | Max. | Unit |

| _          | High-Speed On-Chip Oscillator Frequency When the Reset is Deasserted             | Vcc = 5.0V, Topr = 25 °C                    | -    | 8     | ı    | MHz  |

| _          | High-Speed On-Chip Oscillator Frequency Temperature • Supplay Voltage Dependence | 0 to +60 °C / 5 V ± 5 % <sup>(2)</sup>      | 7.44 | -     | 8.56 | MHz  |

|            |                                                                                  | -20 to +85 °C / 2.7 to 5.5 V <sup>(2)</sup> | 7.04 | _     | 8.96 | MHz  |

|            |                                                                                  | -40 to +85 °C / 2.7 to 5.5 V <sup>(2)</sup> | 6.80 | =     | 9.20 | MHz  |

#### NOTES:

- 1. The measurement condition is Vcc = AVcc = 5.0V and Topr = 25 °C.

- 2. The standard value shows when the HRA1 register is assumed as the value in shipping and the HRA2 register value is set to

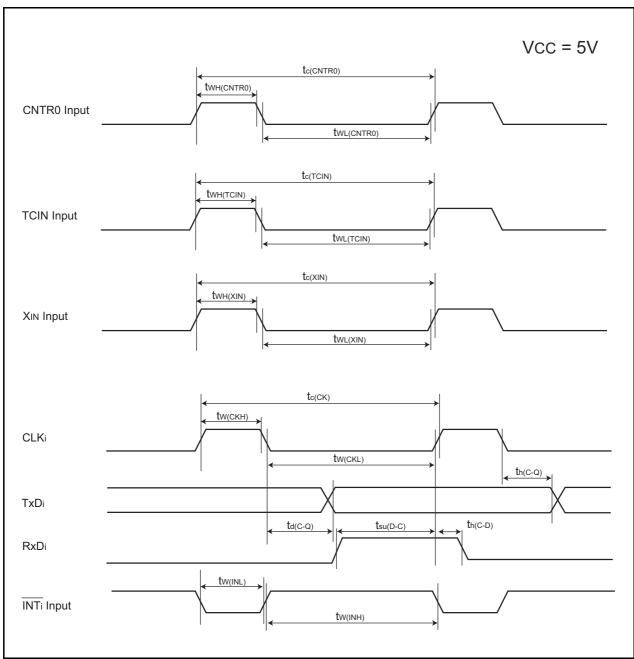

**Table 5.11 Power Supply Circuit Timing Characteristics**

| Symbol  | Parameter                                                                   | Condition | Standard |      |      | Unit |

|---------|-----------------------------------------------------------------------------|-----------|----------|------|------|------|

|         |                                                                             | Condition | Min.     | Тур. | Max. | Unit |

| td(P-R) | Time for Internal Power Supply Stabilization during Power-On <sup>(2)</sup> |           | 1        | =    | 2000 | μS   |

| td(R-S) | STOP Exit Time <sup>(3)</sup>                                               |           | =        | -    | 150  | μS   |

### NOTES:

- 1. The measurement condition is Vcc = AVcc = 2.7 to 5.5V and  $T_{opr} = 25$  °C.

- 2. Waiting time until the internal power supply generation circuit stabilizes during power-on.

- 3. Time until CPU clock supply starts since the interrupt is acknowledged to exit stop mode.

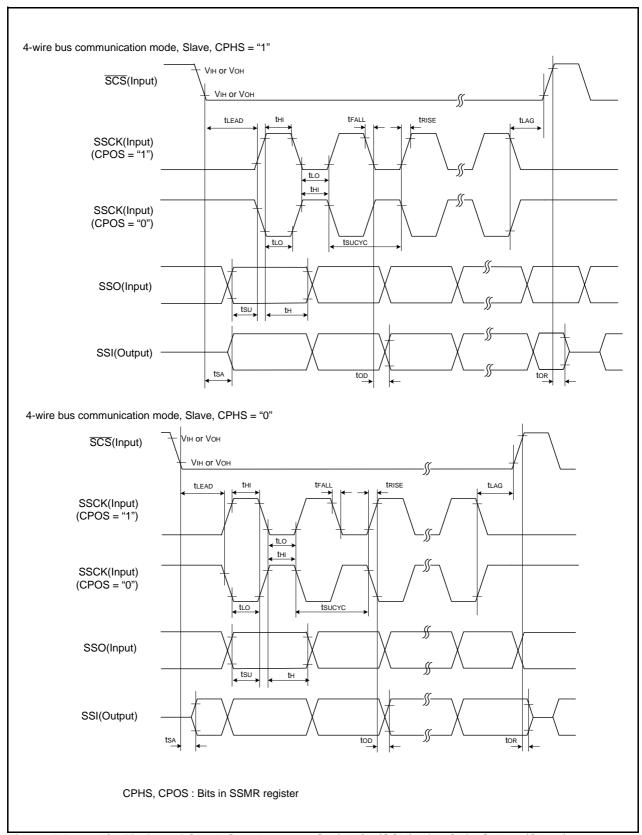

Timing Requirements of Clock Synchronous Serial I/O (SSU) with Chip Select(1) **Table 5.12**

| Symbol | Parameter                       |        | Conditions - |          | Standard |             |         |

|--------|---------------------------------|--------|--------------|----------|----------|-------------|---------|

| Symbol |                                 |        |              | Min.     | Тур.     | Max.        | Unit    |

| tsucyc | SSCK Clock Cycle Time           |        |              | 4        | =        | =           | tcyc(2) |

| tHI    | SSCK Clock "H" Width            |        |              | 0.4      | _        | 0.6         | tsucyc  |

| tLO    | SSCK Clock "L" Width            |        |              | 0.4      | -        | 0.6         | tsucyc  |

| trise  | SSCK Clock Rising Time          | Master |              | _        | _        | 1           | tcyc(2) |

|        |                                 | Slave  |              | =        | _        | 1           | μS      |

| tfall  | SSCK Clock Falling Time         | Master |              | =        | =        | 1           | tcyc(2) |

|        |                                 | Slave  |              | =        | _        | 1           | μS      |

| tsu    | SSO, SSI Data Input Setup Time  |        |              | 100      | _        | -           | ns      |

| tH     | SSO, SSI Data Input Hold T      | ïme    |              | 1        | _        | -           | tcyc(2) |

| tLEAD  | SCS Setup Time                  | Slave  |              | 1tcyc+50 | -        | -           | ns      |

| tlag   | SCS Hold Time                   | Slave  |              | 1tcyc+50 | _        | -           | ns      |

| top    | SSO, SSI Data Output Delay Time |        |              | =        | -        | 1           | tcyc(2) |

| tsa    | SSI Slave Access Time           |        |              | -        | _        | 1.5tcyc+100 | ns      |

| tor    | SSI Slave Out Open Time         |        |              | =        | _        | 1.5tcyc+100 | ns      |

- 1. Vcc = AVcc = 2.7 to 5.5V, Vss = 0V at Topr = -20 to 85 °C / -40 to 85 °C, unless otherwise specified.

- 2. 1tcyc = 1/f1(s)

Figure 5.5 I/O Timing of Clock Synchronous Serial I/O (SSU) with Chip Select (Slave)