#### NXP USA Inc. - KMC8144SVT800A Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                                         |

|-------------------------|----------------------------------------------------------------------------------|

| Туре                    | SC3400 Core                                                                      |

| Interface               | EBI/EMI, Ethernet, I <sup>2</sup> C, PCI, Serial RapidIO, SPI, TDM, UART, UTOPIA |

| Clock Rate              | 800MHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                       |

| On-Chip RAM             | 10.5MB                                                                           |

| Voltage - I/O           | 3.30V                                                                            |

| Voltage - Core          | 1.00V                                                                            |

| Operating Temperature   | 0°C ~ 105°C (TJ)                                                                 |

| Mounting Type           | Surface Mount                                                                    |

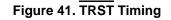

| Package / Case          | 783-BBGA, FCBGA                                                                  |

| Supplier Device Package | 783-FCPBGA (29x29)                                                               |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmc8144svt800a           |

|                         |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Pin A | ssignments and Reset States4                           |

|---|-------|--------------------------------------------------------|

|   | 1.1   | FC-PBGA Ball Layout Diagrams4                          |

|   | 1.2   | Signal List By Ball Location                           |

| 2 | Elect | rical Characteristics                                  |

|   | 2.1   | Maximum Ratings                                        |

|   | 2.2   | Recommended Operating Conditions27                     |

|   | 2.3   | Default Output Driver Characteristics                  |

|   | 2.4   | Thermal Characteristics                                |

|   | 2.5   | DC Electrical Characteristics                          |

|   | 2.6   | AC Timings                                             |

| 3 | Hard  | ware Design Considerations64                           |

|   | 3.1   | Start-up Sequencing Recommendations64                  |

|   | 3.2   | Power Supply Design Considerations                     |

|   | 3.3   | Clock and Timing Signal Board Layout Considerations 67 |

|   | 3.4   | Connectivity Guidelines                                |

| 4 | Orde  | ring Information                                       |

| 5 | Pack  | age Information                                        |

| 6 | Produ | uct Documentation                                      |

| 7 | Revis | ion History                                            |

|   |       |                                                        |

## List of Figures

| Figure 1. | MSC8144 Block Diagram                                                       |

|-----------|-----------------------------------------------------------------------------|

| Figure 2. | StarCore SC3400 DSP Core Subsystem Block Diagram 3                          |

| Figure 3. | MSC8144 FC-PBGA Package, Top View 4                                         |

| Figure 4. | MSC8144 FC-PBGA Package, Bottom View 5                                      |

| Figure 5. | SerDes Reference Clocks Input Stage                                         |

| Figure 6. | Start-Up Sequence with V <sub>DD</sub> Raised Before V <sub>DDIO</sub> with |

|           | CLKIN Started with V <sub>DDIO</sub>                                        |

|           | Timing for a Reset Configuration Write                                      |

| Figure 8. | Timing for t <sub>DDKHMH</sub>                                              |

|           | DDR SDRAM Output Timing                                                     |

| Figure 10 | .DDR AC Test Load 42                                                        |

| Figure 11 | .Differential V <sub>PP</sub> of Transmitter or Receiver                    |

| Figure 12. I ransmitter Output Compliance Mask             | 46 |

|------------------------------------------------------------|----|

| Figure 13.Single Frequency Sinusoidal Jitter Limits        | 48 |

| Figure 14. Receiver Input Compliance Mask                  | 49 |

| Figure 15.PCI AC Test Load                                 | 51 |

| Figure 16.PCI Input AC Timing Measurement Conditions       |    |

| Figure 17.PCI Output AC Timing Measurement Condition       | 51 |

| Figure 18.TDM Inputs Signals                               | 52 |

| Figure 20.TDM Output Signals                               |    |

| Figure 21.UART Input Timing                                |    |

| Figure 22.UART Output Timing                               | 53 |

| Figure 23.Timer Timing                                     |    |

| Figure 24.MII Management Interface Timing                  | 55 |

| Figure 25.MII Transmit AC Timing                           | 55 |

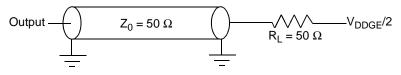

| Figure 26.AC Test Load                                     | 56 |

| Figure 27.MII Receive AC Timing                            |    |

| Figure 28.RMII Transmit and Receive AC Timing              | 57 |

| Figure 29.AC Test Load                                     |    |

| Figure 30.SMII Mode Signal Timing.                         |    |

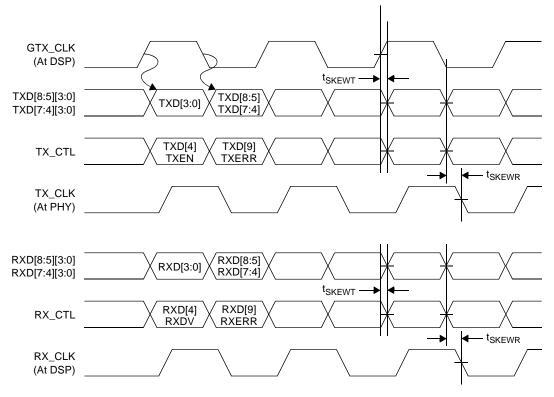

| Figure 31.RGMII AC Timing and Multiplexing                 |    |

| Figure 32.ATM/UTOPIA/POS AC Test Load                      |    |

| Figure 33.ATM/UTOPIAPOS AC Timing (External Clock)         |    |

| Figure 34.SPI AC Test Load                                 |    |

| Figure 35.SPI AC Timing in Slave Mode (External Clock)     |    |

| Figure 36.SPI AC Timing in Master Mode (Internal Clock)    |    |

| Figure 37.Asynchronous Signal Timing                       |    |

| Figure 38.Test Clock Input Timing                          |    |

| Figure 39.Boundary Scan (JTAG) Timing                      |    |

| Figure 40.Test Access Port Timing                          | 64 |

| Figure 41.TRST Timing                                      |    |

| Figure 42.V_DDM3, V_DDM3IO and V_25M3 Power-on Sequence    | 65 |

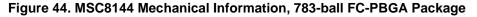

| Figure 44.MSC8144 Mechanical Information, 783-ball FC-PBGA |    |

| Package                                                    | 77 |

|                |                                      | Power- I/O Multiplexing Mode <sup>2</sup> |         |           |           |           |            |           |              |         |                       |

|----------------|--------------------------------------|-------------------------------------------|---------|-----------|-----------|-----------|------------|-----------|--------------|---------|-----------------------|

| Ball<br>Number | Signal Name                          | On<br>Reset<br>Value                      | 0 (000) | 1 (001)   | 2 (010)   | 3 (011)   | 4 (100)    | 5 (101)   | 6 (110)      | 7 (111) | Ref.<br>Supply        |

| B10            | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | —                     |

| B11            | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | _                     |

| B12            | SRIO_RXD0                            |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXC</sub>    |

| B13            | GND <sub>SXC</sub>                   |                                           |         |           |           |           |            |           |              |         | GND <sub>SXC</sub>    |

| B14            | SRIO_RXD1                            |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXC</sub>    |

| B15            | GND <sub>SXC</sub>                   |                                           |         |           |           |           |            |           |              |         | GND <sub>SXC</sub>    |

| B16            | SRIO_REF_CLK                         |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXC</sub>    |

| B17            | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | _                     |

| B18            | V <sub>DDSXC</sub>                   |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXC</sub>    |

| B19            | SRIO_RXD2/<br>GE1_SGMII_RX           |                                           | SG      | MII suppo | rt on SER | DES is en | abled by I | Reset Con | figuration V | Vord    | V <sub>DDSXC</sub>    |

| B20            | GND <sub>SXC</sub>                   |                                           |         |           |           |           |            |           |              |         | GND <sub>SXC</sub>    |

| B21            | SRIO_RXD3/<br>GE2_SGMII_RX           |                                           | SG      | MII suppo | rt on SER | DES is en | abled by F | Reset Con | figuration V | Vord    | V <sub>DDSXC</sub>    |

| B22            | GND <sub>SXC</sub>                   |                                           |         |           |           |           |            |           |              |         | GND <sub>SXC</sub>    |

| B23            | GND <sub>SXP</sub>                   |                                           |         |           |           |           |            |           |              |         | GND <sub>SXP</sub>    |

| B24            | MDQ27                                |                                           |         |           |           |           |            |           |              |         | V <sub>DDDDR</sub>    |

| B25            | V <sub>DDDDR</sub>                   |                                           |         |           |           |           |            |           |              |         | V <sub>DDDDR</sub>    |

| B26            | GND                                  |                                           |         |           |           |           |            |           |              |         | GND                   |

| B27            | V <sub>DDDDR</sub>                   |                                           |         |           |           |           |            |           |              |         | V <sub>DDDDR</sub>    |

| B28            | MDQS3                                |                                           |         |           |           |           |            |           |              |         | V <sub>DDDDR</sub>    |

| C1             | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | _                     |

| C2             | GE2_RX_CLK/PCI_AD29                  |                                           |         | Ethe      | rnet 2    | 1         | PCI        |           | Ethernet 2   | 1       | V <sub>DDGE2</sub>    |

| C3             | V <sub>DDGE2</sub>                   |                                           |         |           |           |           |            |           |              |         | V <sub>DDGE2</sub>    |

| C4             | TDM7RSYN/GE2_TD2/<br>PCI_AD2/UTP_TER |                                           | Т       | DM        |           | PCI       |            | Ethe      | ernet 2      | UTOPIA  |                       |

| C5             | TDM7RCLK/GE2_RD2/<br>PCI_AD0/UTP_RVL |                                           | т       | DM        |           | PCI       |            | Ethe      | ernet 2      | UTOPIA  | V <sub>DDGE2</sub>    |

| C6             | V <sub>DDGE2</sub>                   |                                           |         |           |           |           |            |           |              |         | V <sub>DDGE2</sub>    |

| C7             | GE2_RD0/PCI_AD27                     |                                           |         | Ethe      | rnet 2    |           | PCI        |           | Ethernet 2   |         | V <sub>DDGE2</sub>    |

| C8             | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | —                     |

| C9             | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | _                     |

| C10            | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | —                     |

| C11            | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | —                     |

| C12            | V <sub>DDSXP</sub>                   |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXP</sub>    |

| C13            | SRIO_TXD0                            |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXP</sub>    |

| C14            | V <sub>DDSXP</sub>                   |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXP</sub>    |

| C15            | SRIO_TXD1                            |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXP</sub>    |

| C16            | GND <sub>SXC</sub>                   |                                           |         |           |           |           |            |           |              |         | GND <sub>SXC</sub>    |

| C17            | GND <sub>RIOPLL</sub>                |                                           |         |           |           |           |            |           |              |         | GND <sub>RIOPLL</sub> |

| C18            | Reserved <sup>1</sup>                |                                           |         |           |           |           |            |           |              |         | _                     |

| C19            | V <sub>DDSXP</sub>                   |                                           |         |           |           |           |            |           |              |         | V <sub>DDSXP</sub>    |

| C20            | SRIO_TXD2/GE1_SGMII_T                |                                           | SG      | MII suppo | rt on SER | DES is en | abled by I | Reset Con | figuration V | Vord    | V <sub>DDSXP</sub>    |

Table 1. Signal List by Ball Number (continued)

|                |                                                              | Power- I/O Multiplexing Mode <sup>2</sup> |         |         |              |                   |          |         |          |         |                    |

|----------------|--------------------------------------------------------------|-------------------------------------------|---------|---------|--------------|-------------------|----------|---------|----------|---------|--------------------|

| Ball<br>Number | Signal Name                                                  | On<br>Reset<br>Value                      | 0 (000) | 1 (001) | 2 (010)      | 3 (011)           | 4 (100)  | 5 (101) | 6 (110)  | 7 (111) | Ref.<br>Supply     |

| K23            | MBA2                                                         |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| K24            | MA10                                                         |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| K25            | MA12                                                         |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| K26            | MA14                                                         |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| K27            | MA4                                                          |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| K28            | MV <sub>REF</sub>                                            |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| L1             | Reserved <sup>1</sup>                                        |                                           |         |         |              |                   |          |         |          |         | _                  |

| L2             | CLKOUT                                                       |                                           |         |         |              |                   |          |         |          |         | V <sub>DDIO</sub>  |

| L3             | TMR1/UTP_IR/PCI_CBE3/<br>GPIO17 <sup>3, 6</sup>              |                                           | UTC     | OPIA    | TMR/<br>GPIO | UTOPIA            | PCI      |         | UTOPIA   |         | V <sub>DDIO</sub>  |

| L4             | TMR4/PCI_PAR/GPIO20 <sup>3,</sup><br><sup>6</sup> / UTP_REOP |                                           |         | TIMEF   | R/GPIO       |                   | PCI      | Г       | IMER/GPI | 0       | V <sub>DDIO</sub>  |

| L5             | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L6             | TMR2/PCI_FRAME/<br>GPIO18 <sup>3, 6</sup>                    |                                           |         | TIMEF   | R/GPIO       |                   | PCI      | TIME    | R/GPIO   | UTOPIA  | V <sub>DDIO</sub>  |

| L7             | SCL/GPIO26 <sup>3, 4, 6</sup>                                |                                           |         |         |              | l <sup>2</sup> C/ | GPIO     |         |          |         | V <sub>DDIO</sub>  |

| L8             | UTXD/GPIO15/IRQ9 <sup>3, 6</sup>                             |                                           |         |         |              | UART/C            | SPIO/IRQ |         |          |         | V <sub>DDIO</sub>  |

| L9             | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L10            | V <sub>DD</sub>                                              |                                           |         |         |              |                   |          |         |          |         | V <sub>DD</sub>    |

| L11            | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L12            | V <sub>DD</sub>                                              |                                           |         |         |              |                   |          |         |          |         | V <sub>DD</sub>    |

| L13            | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L14            | V <sub>DD</sub>                                              |                                           |         |         |              |                   |          |         |          |         | V <sub>DD</sub>    |

| L15            | Reserved <sup>1</sup>                                        |                                           |         |         |              |                   |          |         |          |         | GND                |

| L16            | V <sub>DD</sub>                                              |                                           |         |         |              |                   |          |         |          |         | V <sub>DD</sub>    |

| L17            | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L18            | V <sub>DD</sub>                                              |                                           |         |         |              |                   |          |         |          |         | V <sub>DD</sub>    |

| L19            | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L20            | V <sub>DD</sub>                                              |                                           |         |         |              |                   |          |         |          |         | V <sub>DD</sub>    |

| L21            | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L22            | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L23            | MCKE1                                                        |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| L24            | MA1                                                          |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| L25            | V <sub>DDDDR</sub>                                           |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| L26            | GND                                                          |                                           |         |         |              |                   |          |         |          |         | GND                |

| L27            | V <sub>DDDDR</sub>                                           |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| L28            | MCK1                                                         |                                           |         |         |              |                   |          |         |          |         | V <sub>DDDDR</sub> |

| M1             | Reserved <sup>1</sup>                                        |                                           |         |         |              |                   |          |         |          |         | _                  |

| M2             | TRST                                                         |                                           |         |         |              |                   |          |         |          |         | V <sub>DDIO</sub>  |

| M3             | EE0                                                          |                                           |         |         |              |                   |          |         |          |         | V <sub>DDIO</sub>  |

| M4             | EE1                                                          |                                           |         |         |              |                   |          |         |          |         | V <sub>DDIO</sub>  |

| M5             | UTP_RCLK/PCI_AD13                                            |                                           | UTC     | OPIA    | PCI          |                   |          | UTOPIA  |          |         | V <sub>DDIO</sub>  |

| M6             | UTP_RADDR0/PCI_AD7                                           |                                           | UTC     | OPIA    | PCI          |                   |          | UTOPIA  |          |         | V <sub>DDIO</sub>  |

| M7             | UTP_TD8/PCI_AD30                                             |                                           | UTC     | OPIA    | PCI          |                   |          | UTOPIA  |          |         | V <sub>DDIO</sub>  |

## Table 1. Signal List by Ball Number (continued)

|                | Signal Name           | Power-               |         |         |         |         |         |         |         |         |                    |

|----------------|-----------------------|----------------------|---------|---------|---------|---------|---------|---------|---------|---------|--------------------|

| Ball<br>Number |                       | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011) | 4 (100) | 5 (101) | 6 (110) | 7 (111) | Ref.<br>Supply     |

| V8             | V <sub>DDIO</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDIO</sub>  |

| V9             | Reserved <sup>1</sup> |                      |         |         |         |         |         |         |         |         | V <sub>DDIO</sub>  |

| V10            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| V11            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| V12            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| V13            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| V14            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| V15            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| V16            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| V17            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| V18            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| V19            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| V20            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| V21            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| V22            | V <sub>DDDDR</sub>    |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub> |

| V23            | MDQ2                  |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub> |

| V24            | V <sub>DDDDR</sub>    |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub> |

| V25            | MDQ6                  |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub> |

| V26            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| V27            | V <sub>DDDDR</sub>    |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub> |

| V28            | MDQS0                 |                      |         |         |         |         |         |         |         |         | V <sub>DDDDR</sub> |

| W1             | Reserved <sup>1</sup> |                      |         |         |         |         |         |         |         |         | _                  |

| W2             | UTP_TD12/PCI_CBE2     |                      | UTC     | OPIA    | PCI     |         |         | UTOPIA  |         |         | V <sub>DDIO</sub>  |

| W3             | UTP_TD11/PCI_CBE1     |                      | UTC     | OPIA    | PCI     |         |         | UTOPIA  |         |         | V <sub>DDIO</sub>  |

| W4             | V <sub>DDIO</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDIO</sub>  |

| W5             | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| W6             | UTP_TD15/PCI_IRDY     |                      | UTC     | OPIA    | PCI     |         |         | UTOPIA  |         |         | V <sub>DDIO</sub>  |

| W7             | UTP_TD0/PCI_SERR      |                      | UTC     | OPIA    | Р       | CI      |         | UT      | OPIA    |         | V <sub>DDIO</sub>  |

| W8             | UTP_RSOC/PCI_AD22     |                      | UTC     | OPIA    | PCI     |         |         | UTOPIA  |         |         | V <sub>DDIO</sub>  |

| W9             | Reserved <sup>1</sup> |                      |         |         |         |         |         |         |         |         | V <sub>DDIO</sub>  |

| W10            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| W11            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| W12            | V <sub>25M3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>25M3</sub>  |

| W13            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| W14            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| W15            | V <sub>25M3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>25M3</sub>  |

| W16            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| W17            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| W18            | V <sub>25M3</sub>     |                      |         |         |         |         |         |         |         | 1       | V <sub>25M3</sub>  |

| W19            | GND                   |                      |         |         |         |         |         |         |         | 1       | GND                |

| W20            | V <sub>DDM3</sub>     |                      |         |         |         |         |         |         |         |         | V <sub>DDM3</sub>  |

| W21            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

| W22            | GND                   |                      |         |         |         |         |         |         |         |         | GND                |

## Table 1. Signal List by Ball Number (continued)

rical Characteristics

# 2 Electrical Characteristics

This document contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the *MSC8144 Reference Manual*.

# 2.1 Maximum Ratings

## CAUTION

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

Table 2 describes the maximum electrical ratings for the MSC8144.

|                                                                           | 1                                                                 | 1                                | n      |

|---------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------|--------|

| Rating                                                                    | Symbol                                                            | Value                            | Unit   |

| Core supply voltage                                                       | V <sub>dd</sub>                                                   | -0.3 to 1.1                      | V      |

| PLL supply voltage <sup>3</sup>                                           | V <sub>DDPLL0</sub><br>V <sub>DDPLL1</sub><br>V <sub>DDPLL2</sub> | -0.3 to 1.1                      | V      |

| M3 memory Internal voltage                                                | V <sub>DDM3</sub>                                                 | -0.3 to 1.32                     | V      |

| DDR memory supply voltage <ul> <li>DDR mode</li> <li>DDR2 mode</li> </ul> | V <sub>ddddr</sub>                                                | -0.3 to 2.75<br>-0.3 to 1.98     | V<br>V |

| DDR reference voltage                                                     | MV <sub>REF</sub>                                                 | –0.3 to 0.51 $\timesV_{DDDDR}$   | V      |

| Input DDR voltage                                                         | V <sub>INDDR</sub>                                                | –0.3 to V <sub>DDDDR</sub> + 0.3 | V      |

| Ethernet 1 I/O voltage                                                    | V <sub>DDGE1</sub>                                                | -0.3 to 3.465                    | V      |

| Input Ethernet 1 I/O voltage                                              | V <sub>INGE1</sub>                                                | –0.3 to V <sub>DDGE1</sub> + 0.3 | V      |

| Ethernet 2 I/O voltage                                                    | V <sub>DDGE2</sub>                                                | -0.3 to 3.465                    | V      |

| Input Ethernet 2I/O voltage                                               | V <sub>INGE2</sub>                                                | –0.3 to V <sub>DDGE2</sub> + 0.3 | V      |

| I/O voltage excluding Ethernet, DDR, M3, and RapidIO lines                | V <sub>DDIO</sub>                                                 | -0.3 to 3.465                    | V      |

| Input I/O voltage                                                         | V <sub>INIO</sub>                                                 | –0.3 to V <sub>DDIO</sub> + 0.3  | V      |

#### **Table 2. Absolute Maximum Ratings**

## 2.5 DC Electrical Characteristics

This section describes the DC electrical characteristics for the MSC8144.

## 2.5.1 DDR SDRAM DC Electrical Characteristics

This section describes the DC electrical specifications for the DDR SDRAM interface of the MSC8144.

Note: DDR SDRAM uses  $V_{DDDDR}(typ) = 2.5 V$  and DDR2 SDRAM uses  $V_{DDDDR}(typ) = 1.8 V$ .

## 2.5.1.1 DDR2 (1.8 V) SDRAM DC Electrical Characteristics

Table 6 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the MSC8144 when  $V_{DDDDR}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol             | Min                       | Мах                       | Unit |

|--------------------------------------------------|--------------------|---------------------------|---------------------------|------|

| I/O supply voltage <sup>1</sup>                  | V <sub>DDDDR</sub> | 1.7                       | 1.9                       | V    |

| I/O reference voltage <sup>2</sup>               | MV <sub>REF</sub>  | $0.49 \times V_{DDDDR}$   | $0.51 	imes V_{DDDDR}$    | V    |

| I/O termination voltage <sup>3</sup>             | V <sub>TT</sub>    | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    |

| Input high voltage                               | V <sub>IH</sub>    | MV <sub>REF</sub> + 0.125 | V <sub>DDDDR</sub> + 0.3  | V    |

| Input low voltage                                | V <sub>IL</sub>    | -0.3                      | MV <sub>REF</sub> – 0.125 | V    |

| Output leakage current <sup>4</sup>              | I <sub>OZ</sub>    | -50                       | 50                        | μA   |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>    | -13.4                     | —                         | mA   |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>    | 13.4                      | —                         | mA   |

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times V_{DDDDR}$ , and to track  $V_{DDDDR}$  DC variations as measured at the receiver.

Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of V<sub>DDDDR</sub>.

4. Output leakage is measured with all outputs are disabled,  $0 V \le V_{OUT} \le V_{DDDDR}$ .

rical Characteristics

## 2.5.2.2 Spread Spectrum Clock

SRIO\_REF\_CLK/ SRIO\_REF\_CLK is designed to work with a spread spectrum clock (0 to 0.5% spreading at 3033 kHz rate is allowed), assuming both ends have same reference clock. For better results use a source without significant unintended modulation.

# 2.5.3 PCI DC Electrical Characteristics

#### **Table 9. PCI DC Electrical Characteristics**

| Characteristic                                                                                 | Symbol             | Min                    | Max                    | Unit |

|------------------------------------------------------------------------------------------------|--------------------|------------------------|------------------------|------|

| Supply voltage 3.3 V                                                                           | V <sub>DDPCI</sub> | 3.135                  | 3.465                  | V    |

| Input high voltage                                                                             | V <sub>IH</sub>    | $0.5 	imes V_{DDPCI}$  | 3.465                  | V    |

| Input low voltage                                                                              | V <sub>IL</sub>    | -0.5                   | $0.3 	imes V_{DDPCI}$  | V    |

| Input Pull-up voltage <sup>1</sup>                                                             | V <sub>IPU</sub>   | $0.7 \times V_{DDPCI}$ |                        |      |

| Input leakage current, 0 <v<sub>IN <v<sub>DDPCI</v<sub></v<sub>                                | I <sub>IN</sub>    | -30                    | 30                     | μA   |

| Tri-state (high impedance off state) leakage current, 0 <v<sub>IN <v<sub>DDPCI</v<sub></v<sub> | I <sub>OZ</sub>    | -30                    | 30                     | μA   |

| Signal low input current, V <sub>IL</sub> = 0.4 V <sup>1</sup>                                 | ΙL                 | -30                    | 30                     | μA   |

| Signal high input current, V <sub>IH</sub> = 2.0 V <sup>1</sup>                                | Ι <sub>Η</sub>     | -30                    | 30                     | μA   |

| Output high voltage, I <sub>OH</sub> = -0.5 mA, except open drain pins                         | V <sub>OH</sub>    | $0.9 \times V_{DDPCI}$ | —                      | V    |

| Output low voltage, I <sub>OL</sub> = 1.5 mA                                                   | V <sub>OL</sub>    | —                      | $0.1 \times V_{DDPCI}$ | V    |

| Input Pin Capacitance <sup>1</sup>                                                             | C <sub>IN</sub>    |                        | 10                     | pF   |

| Notes: 1. Not tested. Guaranteed by design.                                                    | •                  |                        | •                      | •    |

## 2.5.4 TDM DC Electrical Characteristics

## Table 10. TDM DC Electrical Characteristics

| Characteristic                                                 | Symbol             | Min   | Max   | Unit |

|----------------------------------------------------------------|--------------------|-------|-------|------|

| Supply voltage 3.3 V                                           | V <sub>DDTDM</sub> | 3.135 | 3.465 | V    |

| Input high voltage                                             | V <sub>IH</sub>    | 2.0   | 3.465 | V    |

| Input low voltage                                              | V <sub>IL</sub>    | -0.3  | 0.8   | V    |

| Input leakage current 0 <v<sub>IN <v<sub>DDTDM</v<sub></v<sub> | I <sub>IN</sub>    | -30   | 30    | μΑ   |

| Tri-state (high impedance off state) leakage current           | I <sub>OZ</sub>    | -30   | 30    | μΑ   |

| Output high voltage, I <sub>OH</sub> = -1.6 mA                 | V <sub>OH</sub>    | 2.4   | —     | V    |

| Output low voltage, I <sub>OL</sub> = 0.4mA                    | V <sub>OL</sub>    | —     | 0.4   | V    |

rical Characteristics

## 2.5.6 ATM/UTOPIA/POS DC Electrical Characteristics

| Characteristic                                                 | Symbol            | Min   | Max   | Unit |

|----------------------------------------------------------------|-------------------|-------|-------|------|

| Supply voltage 3.3 V                                           | V <sub>DDIO</sub> | 3.135 | 3.465 | V    |

| Input high voltage                                             | V <sub>IH</sub>   | 2.0   | 3.465 | V    |

| Input low voltage                                              | V <sub>IL</sub>   | -0.3  | 0.8   | V    |

| Input leakage current, V <sub>IN</sub> = supply voltage        | I <sub>IN</sub>   | -30   | 30    | μΑ   |

| Signal low input current, V <sub>IL</sub> = 0.4 V <sup>1</sup> | ΙL                | -30   | 30    | μΑ   |

| Signal high input current, $V_{IH} = 2.4 V^1$                  | I <sub>Н</sub>    | -30   | 30    | μΑ   |

| Output high voltage, $I_{OH} = -4 \text{ mA}$                  | V <sub>OH</sub>   | 2.4   | 3.465 | V    |

| Output low voltage, I <sub>OL</sub> = 4 mA                     | V <sub>OL</sub>   | _     | 0.5   | V    |

| Notes: 1. Not tested. Guaranteed by design.                    |                   |       | -     |      |

## 2.5.7 SPI DC Electrical Characteristics

Table 14 provides the SPI DC electrical characteristics.

**Table 14. SPI DC Electrical Characteristics**

| Characteristic                                 | Symbol          | Min  | Мах   | Unit |

|------------------------------------------------|-----------------|------|-------|------|

| Input high voltage                             | V <sub>IH</sub> | 2.0  | 3.465 | V    |

| Input low voltage                              | V <sub>IL</sub> | -0.3 | 0.8   | V    |

| Input current                                  | I <sub>IN</sub> |      | 30    | μΑ   |

| Output high voltage, I <sub>OH</sub> = -4.0 mA | V <sub>OH</sub> | 2.4  | _     | V    |

| Output low voltage, I <sub>OL</sub> = 4.0 mA   | V <sub>OL</sub> | _    | 0.5   | V    |

# 2.5.8 GPIO, UART, TIMER, EE, STOP\_BS, I<sup>2</sup>C, IRQn, NMI\_OUT, INT\_OUT, CLKIN, JTAG Ports DC Electrical Characteristics

Table 15. GPIO, UART, Timer, EE, STOP\_BS, I<sup>2</sup>C, IRQn, NMI\_OUT, INT\_OUT, CLKIN, and JTAG Port<sup>1</sup> DC Electrical Characteristics

| Characteristic                                                                                                                        | Symbol            | Min   | Max   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------|------|

| Supply voltage 3.3 V                                                                                                                  | V <sub>DDIO</sub> | 3.135 | 3.465 | V    |

| Input high voltage                                                                                                                    | V <sub>IH</sub>   | 2.0   | 3.465 | V    |

| Input low voltage                                                                                                                     | V <sub>IL</sub>   | -0.3  | 0.8   | V    |

| Input leakage current, V <sub>IN</sub> = supply voltage                                                                               | I <sub>IN</sub>   | -30   | 30    | μA   |

| Tri-state (high impedance off state) leakage current, $V_{IN}$ = supply voltage                                                       | I <sub>OZ</sub>   | -30   | 30    | μA   |

| Signal low input current, $V_{IL} = 0.4 V^2$                                                                                          | ΙL                | -30   | 30    | μΑ   |

| Signal high input current, $V_{IH} = 2.0 V^2$                                                                                         | Ι <sub>Η</sub>    | -30   | 30    | μA   |

| Output high voltage, I <sub>OH</sub> = -2 mA,<br>except open drain pins                                                               | V <sub>OH</sub>   | 2.4   | 3.465 | V    |

| Output low voltage, I <sub>OL</sub> = 3.2 mA                                                                                          | V <sub>OL</sub>   |       | 0.4   | V    |

| <ul> <li>Notes: 1. This does not include TDI and TMS, which have internal pu</li> <li>2. Not tested. Guaranteed by design.</li> </ul> | ullup resistors.  |       |       | ·    |

| Reset Action/Reset Source                                                   | Po <u>wer-On Re</u> set<br>(PORESET) | Hard Reset (HRESET)                                                 | Sof                                 | t Reset (SRESET)                            |

|-----------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------|-------------------------------------|---------------------------------------------|

| Reset Action/Reset Source                                                   | External only                        | External or Internal<br>(Software Watchdog,<br>Software or RapidIO) | External or<br>internal<br>Software | JTAG Command:<br>EXTEST, CLAMP, or<br>HIGHZ |

| HRESET driven                                                               | Yes                                  | Yes                                                                 | No                                  | No                                          |

| IPBus modules reset (TDM, UART, SWT, DDRC, IPBus master, GIC, HS, and GPIO) | Yes                                  | Yes                                                                 | Yes                                 | Yes                                         |

| SRESET driven                                                               | Yes                                  | Yes                                                                 | Yes                                 | Depends on command                          |

| Extended cores reset                                                        | Yes                                  | Yes                                                                 | Yes                                 | Yes                                         |

| CLASS registers reset                                                       | Yes                                  | Yes                                                                 | Some<br>registers                   | Some registers                              |

| Timers, Performance Monitor                                                 | Yes                                  | Yes                                                                 | No                                  | No                                          |

| QUICC Engine subsystem, PCI, DMA                                            | Yes                                  | Yes                                                                 | Most<br>registers                   | Most registers                              |

#### Table 18. Reset Actions for Each Reset Source (continued)

## 2.6.3.1 Power-On Reset (PORESET) Pin

Asserting  $\overrightarrow{PORESET}$  initiates the power-on reset flow.  $\overrightarrow{PORESET}$  must be asserted externally for at least 32 CLKIN cycles after V<sub>DD</sub> and V<sub>DDIO</sub> are both at their nominal levels.

## 2.6.3.2 Reset Configuration

The MSC8144 has two mechanisms for writing the reset configuration:

- Through the  $I^2C$  port

- Through external pins

- Through internal hard coded

Twenty-three signals (see **Section 1** for signal description details) are sampled during the power-on reset sequence to define the Reset Word Configuration Source and operating conditions:

- RCW\_SRC[2–0]

- RC[16–0]

The RCFG\_CLKIN\_RNG pin must be valid during power-on or hard reset sequence. The STOP\_BS pin must be always valid and is also sampled during power-on reset sequence for RCW loading from an I<sup>2</sup>C EEPROM.

## 2.6.3.3 Reset Timing Tables

Table 19 and Figure 7 describe the reset timing for a reset configuration.

| Table 19 | . Timing f | or a Reset | Configuration | Write |

|----------|------------|------------|---------------|-------|

|----------|------------|------------|---------------|-------|

| No. | Characteristics                                      | Expression | Max  | Min | Unit |

|-----|------------------------------------------------------|------------|------|-----|------|

| 1   | Required external PORESET duration minimum           | 32/CLKIN   |      |     |      |

|     | • 33 MHz <= CLKIN < 44 MHz                           |            | 1280 | 727 | ns   |

|     | • 44 MHz <= CLKIN < 66 MHz                           |            | 728  | 484 | ns   |

|     | • 66 MHz <= CLKIN < 100 MHz                          |            | 485  | 320 | ns   |

|     | <ul> <li>100 MHz &lt;= CLKIN &lt; 133 MHz</li> </ul> |            | 320  | 241 | ns   |

NP-

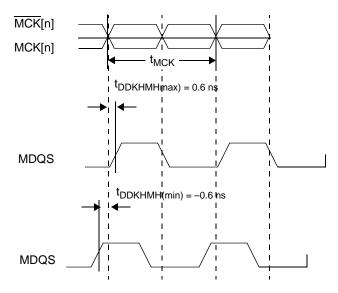

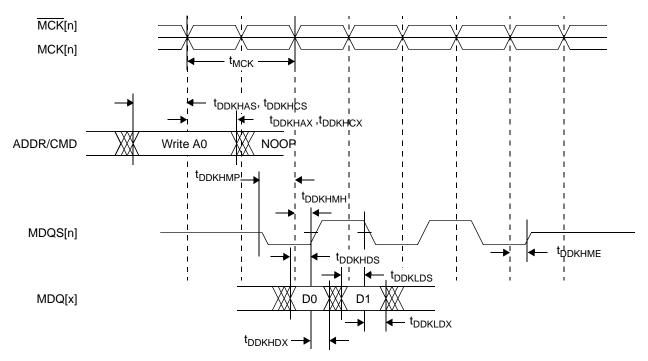

Figure 8 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 8. Timing for t<sub>DDKHMH</sub>

Figure 9. DDR SDRAM Output Timing

#### rical Characteristics

| Ol and startistic                                  | Cumb al         | Rai  | nge               | 11               | Natar                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------|-----------------|------|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min  | Max               | Unit             | Notes                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 |                   | UI <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 |                   | UI <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

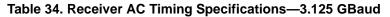

| Total Jitter Tolerance                             | JT              | 0.65 |                   | UI <sub>PP</sub> | Measured at receiver. Total jitter is composed of<br>three components, deterministic jitter, random jitter<br>and single frequency sinusoidal jitter. The sinusoidal<br>jitter may have any amplitude and frequency in the<br>unshaded region of Figure 13. The sinusoidal jitter<br>component is included to ensure margin for low<br>frequency jitter, wander, noise, crosstalk and other<br>variable system effects. |

| Multiple Input Skew                                | S <sub>MI</sub> |      | 22                | ns               | Skew at the receiver input between lanes of a multilane link                                                                                                                                                                                                                                                                                                                                                            |

| Bit Error Rate                                     | BER             |      | 10 <sup>-12</sup> |                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Unit Interval                                      | UI              | 320  | 320               | ps               | ±100 ppm                                                                                                                                                                                                                                                                                                                                                                                                                |

Figure 13. Single Frequency Sinusoidal Jitter Limits

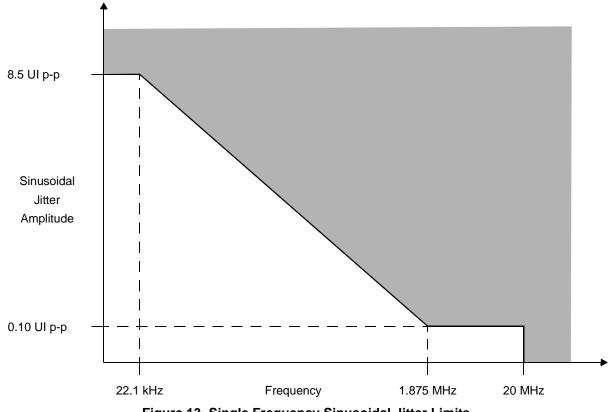

Figure 28 shows the RMII transmit and receive AC timing diagram.

Figure 28. RMII Transmit and Receive AC Timing

Figure 29 provides the AC test load.

Figure 29. AC Test Load

## 2.6.10.5 SMII AC Timing Specification

#### Table 44. SMII Mode Signal Timing

| Characteristics                                                                                                                   | Symbol              | Min | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|------|

| ETHSYNC_IN, ETHRXD to ETHCLOCK rising edge setup time                                                                             | t <sub>SMDVKH</sub> | 1.5 | —   | ns   |

| ETHCLOCK rising edge to ETHSYNC_IN, ETHRXD hold time                                                                              | t <sub>SMDXKH</sub> | 1.0 | —   | ns   |

| ETHCLOCK rising edge to ETHSYNC, ETHTXD output delay                                                                              | t <sub>SMXR</sub>   | 1.5 | 5.0 | ns   |

| Notes:1.Typical REF_CLK clock period is 8ns2.Measured using a 5 pF load.3.Measured using a 15 pF load4.Program GCR4 as 0x00002008 |                     |     |     |      |

Figure 30 shows the SMII Mode signal timing.

Figure 31 shows the RGMII AC timing and multiplexing diagrams.

Figure 31. RGMII AC Timing and Multiplexing

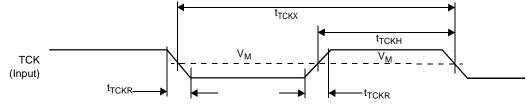

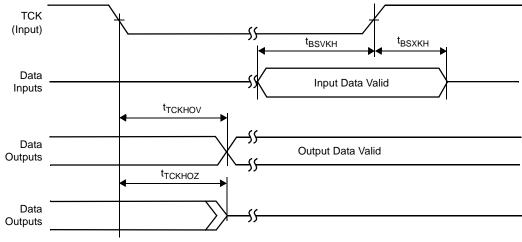

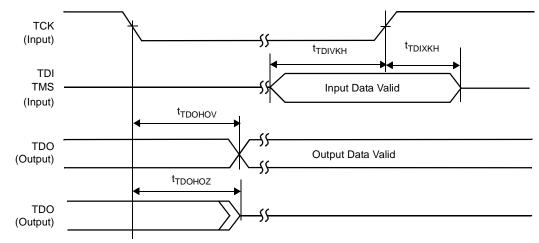

# 2.6.14 JTAG Signals

| Characteristics                                                            | Cumula al                       | All frequencies |      | 11   |

|----------------------------------------------------------------------------|---------------------------------|-----------------|------|------|

| Characteristics                                                            | Symbol                          | Min             | Max  | Unit |

| TCK cycle time                                                             | t <sub>TCKX</sub>               | 36.0            | —    | ns   |

| TCK clock high phase measured at $V_{M} = 1.6 V$                           | t <sub>тскн</sub>               | 15.0            | —    | ns   |

| Boundary scan input data setup time                                        | t <sub>BSVKH</sub>              | 0.0             | —    | ns   |

| Boundary scan input data hold time                                         | t <sub>вsxкн</sub>              | 15.0            | —    | ns   |

| TCK fall to output data valid                                              | tтскноv                         | —               | 20.0 | ns   |

| TCK fall to output high impedance                                          | t <sub>тскног</sub>             | —               | 24.0 | ns   |

| TMS, TDI data setup time                                                   | t <sub>тоіvкн</sub>             | 0.0             | _    | ns   |

| TMS, TDI data hold time                                                    | t <sub>тоіхкн</sub>             | 5.0             | _    | ns   |

| TCK fall to TDO data valid                                                 | tтроноv                         | _               | 10.0 | ns   |

| TCK fall to TDO high impedance                                             | t <sub>TDOHOZ</sub>             | —               | 12.0 | ns   |

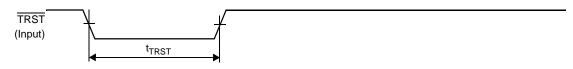

| TRST assert time                                                           | t <sub>TRST</sub>               | 100.0           | —    | ns   |

| Note: All timings apply to OnCE module data transfers as well as any other | er transfers via the JTAG port. | •               | •    |      |

#### Table 50. JTAG Timing

Figure 38 shows the Test Clock Input Timing Diagram

Figure 38. Test Clock Input Timing

Figure 39 shows the boundary scan (JTAG) timing diagram.

Figure 39. Boundary Scan (JTAG) Timing

Figure 40 shows the test access port timing diagram

Figure 40. Test Access Port Timing

Figure 41 shows the TRST timing diagram.

# 3 Hardware Design Considerations

The following sections discuss areas to consider when the MSC8144 device is designed into a system.

# 3.1 Start-up Sequencing Recommendations

## 3.1.1 Power-on Sequence

Use the following guidelines for power-on sequencing:

- There are no dependencies in power-on/power-off sequence between V<sub>DDM3</sub> and V<sub>DD</sub> supplies.

- There are no dependencies in power-on/power-off sequence between RapidIO supplies: V<sub>DDSXC</sub>, V<sub>DDSXP</sub>, V<sub>DDSXP</sub>, V<sub>DDRIOPLL</sub> and other MSC8144 supplies.

- V<sub>DDPLL</sub> should be coupled with the V<sub>DD</sub> power rail with extremely low impedance path.

External voltage applied to any input line must not exceed the related to this port I/O supply by more than 0.6 V at any time, including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for configuration purposes. This is an acceptable exception to the rule during start-up. However, each such input can draw up to 80 mA per input pin per MSC8144 device in the system during start-up. An assertion of the inputs to the high voltage level before power-up should be with slew rate less than 4 V/ns.

# 3.3 Clock and Timing Signal Board Layout Considerations

When laying out the system board, use the following guidelines:

- Keep clock and timing signal paths as short as possible and route with 50  $\Omega$  impedance.

- Use a serial termination resistor placed close to the clock buffer to minimize signal reflection. Use the following equation to compute the resistor value:

Rterm = Rim - Rbuf

where Rim = trace characteristic impedance

Rbuf = clock buffer internal impedance.

Note: See MSC8144 CLKIN and PCI\_CLK\_IN Board Layout (AN3440) for an example layout.

# 3.4 Connectivity Guidelines

**Note:** Although the package actually uses a ball grid array, the more conventional term pin is used to denote signal connections in this discussion.

First, select the pin multiplexing mode to allocate the required I/O signals. Then use the guidelines presented in the following subsections for board design and connections. The following conventions are used in describing the connectivity requirements:

- 1. GND indicates using a  $10 \text{ k}\Omega$  pull-down resistor (recommended) or a direct connection to the ground plane. Direct connections to the ground plane may yield DC current up to 50mA through the I/O supply that adds to overall power consumption.

- 2.  $V_{DD}$  indicates using a 10 k $\Omega$  pull-up resistor (recommended) or a direct connection to the appropriate power supply. Direct connections to the supply may yield DC current up to 50mA through the I/O supply that adds to overall power consumption.

- 3. Mandatory use of a pull-up or pull-down resistor it is clearly indicated as "pull-up/pull-down".

- 4. NC indicates "not connected" and means do not connect anything to the pin.

- 5. The phrase "in use" indicates a typical pin connection for the required function.

- **Note:** Please see recommendations #1 and #2 as mandatory pull-down or pull-up connection for unused pins in case of subset interface connection.

## 3.4.1 DDR Memory Related Pins

This section discusses the various scenarios that can be used with DDR1 and DDR2 memory.

**Note:** For information about unused differential/non-differential pins in DDR1/DDR2 modes (that is, unused negative lines of strobes in DDR1), please refer to Table 51.

## 3.4.1.1 DDR Interface Is Not Used

| Signal Name | Pin Connection |

|-------------|----------------|

| MDQ[0-31]   | NC             |

| MDQS[0-3]   | NC             |

| MDQS[0-3]   | NC             |

| MA[0–15]    | NC             |

| MCK[0-2]    | NC             |

| MCK[0-2]    | NC             |

| MCS[0-1]    | NC             |

#### Table 51. Connectivity of DDR Related Pins When the DDR Interface Is Not Used

ware Design Considerations

| Signal Name        | Pin Connection |

|--------------------|----------------|

| MDM[0-3]           | NC             |

| MBA[0-2]           | NC             |

| MCAS               | NC             |

| MCKE[0-1]          | NC             |

| MODT[0-1]          | NC             |

| MDIC[0-1]          | NC             |

| MRAS               | NC             |

| MWE                | NC             |

| MECC[0-7]          | NC             |

| ECC_MDM            | NC             |

| ECC_MDQS           | NC             |

| ECC_MDQS           | NC             |

| MV <sub>REF</sub>  | GND            |

| V <sub>DDDDR</sub> | GND            |

### Table 51. Connectivity of DDR Related Pins When the DDR Interface Is Not Used (continued)

## 3.4.1.2 16-Bit DDR Memory Only

Table 52 lists unused pin connection when using 16-bit DDR memory. The 16 most significant data lines are not used.

| Signal Name | Pin connection                |

|-------------|-------------------------------|

| MDQ[0-15]   | in use                        |

| MDQ[16-31]  | pull-up to V <sub>DDDDR</sub> |

| MDQS[0-1]   | in use                        |

| MDQS[2-3]   | pull-down to GND              |

| MDQS[0-1]   | in use                        |

| MDQS[2-3]   | pull-up to V <sub>DDDDR</sub> |

| MA[0–15]    | in use                        |

| MCK[0-2]    | in use                        |

| MCK[0-2]    | in use                        |

| MCS[0-1]    | in use                        |

| MDM[0-1]    | in use                        |

| MDM[2-3]    | NC                            |

| MBA[0-2]    | in use                        |

| MCAS        | in use                        |

| MCKE[0-1]   | in use                        |

| MODT[0-1]   | in use                        |

| MDIC[0-1]   | in use                        |

| MRAS        | in use                        |

| Table 52. Connectivity | of DDR Related Pin | s When Usina 16- | bit DDR Memory Only |

|------------------------|--------------------|------------------|---------------------|

|                        |                    | o                |                     |

#### Table 60. Connectivity of GE1 Related Pins When only a subset of the GE1 Interface Is required (continued)

| Signal Name  | Pin Connection     |

|--------------|--------------------|

| GE2_SGMII_RX | GND <sub>SXC</sub> |

| GE2_SGMII_TX | NC                 |

| GE2_SGMII_TX | NC                 |

| GE2_TCK      | NC                 |

| GE2_TD[0-3]  | NC                 |

| GE2_TX_EN    | NC                 |

## 3.4.4.3 GE1 and GE2 Management Pins

GE\_MDC and GE\_MDIO pins should be connected as required by the specified protocol. If neither GE1 nor GE2 is used (that is,  $V_{DDGE2}$  is connected to GND), Table 61 lists the recommended management pin connections.

#### Table 61. Connectivity of GE Management Pins When GE1 and GE2 Are Not Used

| Signal Name | Pin Connection |

|-------------|----------------|

| GE_MDC      | NC             |

| GE_MDIO     | NC             |

## 3.4.5 UTOPIA/POS Related Pins

Table 62 lists the board connections of the UTOPIA/POS pins when the entire UTOPIA/POS interface is not used or subset of UTOPIA/POS interface is used. For multiplexing options that select a subset of the UTOPIA/POS interface, use the connections described in Table 62 for those signals that are not selected. Table 62 assumes that the alternate function of the specified pin is not used. If the alternate function is used, connect that pin as required to support the selected function.

#### Table 62. Connectivity of UTOPIA/POS Related Pins When UTOPIA/POS Interface Is Not Used

| Signal Name       | Pin Connection    |

|-------------------|-------------------|

| UTP_IR            | GND               |

| UTP_RADDR[0-4]    | V <sub>DDIO</sub> |

| UTP_RCLAV_PDRPA   | NC                |

| UTP_RCLK          | GND               |

| UTP_RD[0-15]      | GND               |

| UTP_REN           | V <sub>DDIO</sub> |

| UTP_RPRTY         | GND               |

| UTP_RSOC          | GND               |

| UTP_TADDR[0-4]    | V <sub>DDIO</sub> |

| UTP_TCLAV         | NC                |

| UTP_TCLK          | GND               |

| UTP_TD[0-15]      | NC                |

| UTP_TEN           | V <sub>DDIO</sub> |

| UTP_TPRTY         | NC                |

| UTP_TSOC          | NC                |

| V <sub>DDIO</sub> | 3.3 V             |

5

# Package Information

# 6 **Product Documentation**

- *MSC8144 Technical Data Sheet* (MSC8144). Details the signals, AC/DC characteristics, clock signal characteristics, package and pinout, and electrical design considerations of the MSC8144 device.

- *MSC8144 Reference Manual* (MSC8144RM). Includes functional descriptions of the extended cores and all the internal subsystems including configuration and programming information.

- Application Notes. Cover various programming topics related to the StarCore DSP core and the MSC8144 device.

- *SC3400 DSP Core Reference Manual*. Covers the SC3400 core architecture, control registers, clock registers, program control, and instruction set.

- *MSC8144 SC3400 DSP Core Subsystem Reference Manual*. Covers core subsystem architecture, functionality, and registers.

## Table 66. Document Revision History (continued)

| Rev. | Date       | Description                                                                                                                                                                                                                                    |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Dec 2007   | • Changed minimum voltage level for V <sub>DDM3</sub> to 1.213 (1.25 – 3%) in Table 3.                                                                                                                                                         |

|      |            | • Added POS to titles in Section 2.6.6.                                                                                                                                                                                                        |

|      |            | <ul> <li>Added additional signals to titles in Section 2.6.8. Added high and low voltage ranges to Table 19.</li> <li>Added ATM and POS to headings in Section 2.7.11. Changed characteristics to generic input/output in Table 52,</li> </ul> |

|      |            | Figure 33, and Figure 34.                                                                                                                                                                                                                      |

|      |            | • Replaced Sections 2.7.13 and 2.7.14 with new Section 2.7.13, Asynchronous Signal Timing. Renumbered                                                                                                                                          |

|      |            | <ul> <li>subsequent sections, tables, and figures.</li> <li>Added POS to all UTOPIA references in Section 3.4.5.</li> </ul>                                                                                                                    |

| 8    | Dec 2007   | <ul> <li>Changed GCR4 program value to 0x0004C130 in Note 7 in Table 51.</li> </ul>                                                                                                                                                            |

| 9    | Mar 2008   | Changed description of Table 20 in Section 2.7.2.                                                                                                                                                                                              |