### NXP USA Inc. - KMC8144VT1000A Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                                         |

|-------------------------|----------------------------------------------------------------------------------|

| Туре                    | SC3400 Core                                                                      |

| Interface               | EBI/EMI, Ethernet, I <sup>2</sup> C, PCI, Serial RapidIO, SPI, TDM, UART, UTOPIA |

| Clock Rate              | 1GHz                                                                             |

| Non-Volatile Memory     | ROM (96kB)                                                                       |

| On-Chip RAM             | 10.5MB                                                                           |

| Voltage - I/O           | 3.30V                                                                            |

| Voltage - Core          | 1.00V                                                                            |

| Operating Temperature   | 0°C ~ 90°C (TJ)                                                                  |

| Mounting Type           | Surface Mount                                                                    |

| Package / Case          | 783-BBGA, FCBGA                                                                  |

| Supplier Device Package | 783-FCPBGA (29x29)                                                               |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmc8144vt1000a           |

|                         |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

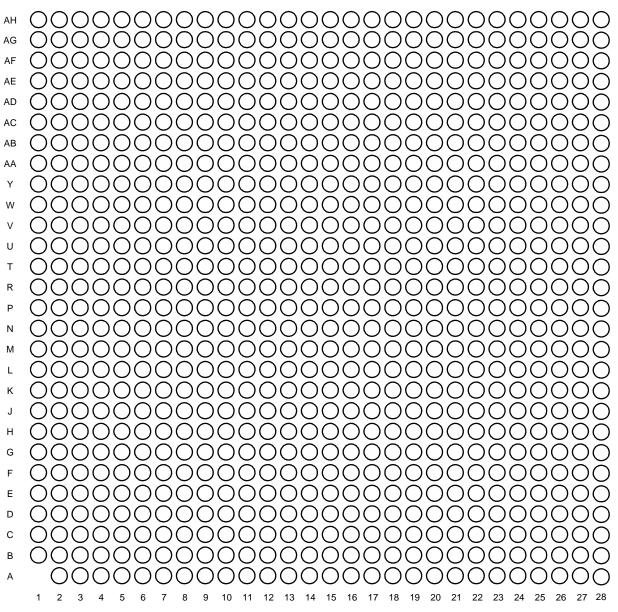

**Bottom View**

Figure 4. MSC8144 FC-PBGA Package, Bottom View

|                |                                                             | Power-               |              |               | I/      | O Multipl | exing Mo | de <sup>2</sup> |         |                   |                    |

|----------------|-------------------------------------------------------------|----------------------|--------------|---------------|---------|-----------|----------|-----------------|---------|-------------------|--------------------|

| Ball<br>Number | Signal Name                                                 | On<br>Reset<br>Value | 0 (000)      | 1 (001)       | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110) | 7 (111)           | Ref.<br>Supply     |

| G23            | MBA1                                                        |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| G24            | MA3                                                         |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| G25            | MA8                                                         |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| G26            | V <sub>DDDDR</sub>                                          |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| G27            | GND                                                         |                      |              |               |         |           |          |                 |         |                   | GND                |

| G28            | MCK0                                                        |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| H1             | Reserved <sup>1</sup>                                       |                      |              |               |         |           |          |                 |         |                   | _                  |

| H2             | CLKIN                                                       |                      |              |               |         |           |          |                 |         |                   | V <sub>DDIO</sub>  |

| H3             | HRESET                                                      |                      |              |               |         |           |          |                 |         |                   | V <sub>DDIO</sub>  |

| H4             | PCI_CLK_IN                                                  |                      |              |               |         |           |          |                 |         |                   | V <sub>DDIO</sub>  |

| H5             | NMI                                                         |                      |              |               |         |           |          |                 |         |                   | V <sub>DDIO</sub>  |

| H6             | URXD/GPIO14/IRQ8/<br>RC_LDF <sup>3, 6</sup>                 | RC_LDF               |              |               | UA      | ART/GPIO  | /IRQ     |                 |         |                   | V <sub>DDIO</sub>  |

| H7             | GE1_RX <u>_ER/P</u> CI_AD6/<br>GPIO25/IRQ15 <sup>3, 6</sup> |                      | GPIO/<br>IRQ | Ethernet<br>1 |         | PCI       |          | GPIO/<br>IRQ    | Ether   | net 1             | V <sub>DDIO</sub>  |

| H8             | GE1_CRS/PCI_AD5                                             |                      | PCI          | Ethernet<br>1 |         | PCI       |          | Ethernet 1      |         | V <sub>DDIO</sub> |                    |

| H9             | GND                                                         |                      |              |               |         |           |          |                 |         |                   | GND                |

| H10            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |                   | V <sub>DD</sub>    |

| H11            | GND                                                         |                      |              |               |         |           |          |                 |         |                   | GND                |

| H12            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |                   | V <sub>DD</sub>    |

| H13            | GND                                                         |                      |              |               |         |           |          |                 |         |                   | GND                |

| H14            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |                   | V <sub>DD</sub>    |

| H15            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |                   | V <sub>DD</sub>    |

| H16            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |                   | V <sub>DD</sub>    |

| H17            | GND                                                         |                      |              |               |         |           |          |                 |         |                   | GND                |

| H18            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |                   | V <sub>DD</sub>    |

| H19            | GND                                                         |                      |              |               |         |           |          |                 |         |                   | GND                |

| H20            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |                   | V <sub>DD</sub>    |

| H21            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |                   | V <sub>DD</sub>    |

| H22            | V <sub>DDDDR</sub>                                          |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| H23            | MBA0                                                        |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| H24            | MA15                                                        |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| H25            | V <sub>DDDDR</sub>                                          |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| H26            | MA9                                                         |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| H27            | MA7                                                         |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| H28            | МСК0                                                        |                      |              |               |         |           |          |                 |         |                   | V <sub>DDDDR</sub> |

| J1             | Reserved <sup>1</sup>                                       |                      |              | 1             |         |           | Ī        |                 |         |                   | _                  |

| J2             | GND                                                         |                      |              |               |         |           |          |                 |         |                   | GND                |

| J3             | V <sub>DDIO</sub>                                           |                      |              | 1             |         |           |          |                 |         |                   | V <sub>DDIO</sub>  |

| J4             | STOP_BS                                                     |                      |              | 1             |         |           |          |                 |         |                   | V <sub>DDIO</sub>  |

| J5             | NMI_OUT <sup>4</sup>                                        |                      |              | 1             |         |           |          |                 |         |                   | V <sub>DDIO</sub>  |

| J6             | INT_OUT <sup>4</sup>                                        |                      |              |               |         |           |          |                 |         |                   | V <sub>DDIO</sub>  |

| J7             | SDA/GPIO27 <sup>3, 4, 6</sup>                               |                      |              | •             |         | I2C/GPIC  |          |                 |         |                   | V <sub>DDIO</sub>  |

### Table 1. Signal List by Ball Number (continued)

| Dell           |                                      | Power-                 |         |         | I/      | O Multipl | exing Mo | de <sup>2</sup> |         |                   | Def                 |

|----------------|--------------------------------------|------------------------|---------|---------|---------|-----------|----------|-----------------|---------|-------------------|---------------------|

| Ball<br>Number | Signal Name                          | On<br>Reset<br>Value   | 0 (000) | 1 (001) | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110) | 7 (111)           | Ref.<br>Supply      |

| AE19           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AE20           | V <sub>DDM3IO</sub>                  |                        |         |         |         |           |          |                 |         |                   | V <sub>DDM3IO</sub> |

| AE21           | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |                   | _                   |

| AE22           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AE23           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AE24           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AE25           | V <sub>DDDDR</sub>                   |                        |         |         |         |           |          |                 |         |                   | V <sub>DDDDR</sub>  |

| AE26           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AE27           | V <sub>DDDDR</sub>                   |                        |         |         |         |           |          |                 |         |                   | V <sub>DDDDR</sub>  |

| AE28           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF1            | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |                   | _                   |

| AF2            | V <sub>DDIO</sub>                    |                        |         |         |         |           |          |                 |         |                   | V <sub>DDIO</sub>   |

| AF3            | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF4            | TDM0RDAT/<br>RCFG_CLKIN_RNG          | RCFG_<br>CLKIN_<br>RNG |         | TDM     |         |           |          |                 |         | V <sub>DDIO</sub> |                     |

| AF5            | TDM0TSYN/RCW_SRC2                    | RCW_<br>SRC2           |         | TDM     |         |           |          |                 |         | V <sub>DDIO</sub> |                     |

| AF6            | TDM1RDAT/RC0                         | RC0                    |         |         |         | Т         | DM       |                 |         |                   | V <sub>DDIO</sub>   |

| AF7            | V <sub>DDIO</sub>                    |                        |         |         |         |           |          |                 |         |                   | V <sub>DDIO</sub>   |

| AF8            | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF9            | TDM2RDAT/RC4                         | RC4                    |         | TDM     |         |           |          |                 |         | V <sub>DDIO</sub> |                     |

| AF10           | TDM2TCLK                             |                        |         |         |         | Т         | DM       |                 |         |                   | V <sub>DDIO</sub>   |

| AF11           | GPIO22/IRQ4 <sup>3, 6</sup> /SPIMOSI |                        |         |         |         | GPIO/     | IRQ/SPI  |                 |         |                   | V <sub>DDIO</sub>   |

| AF12           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF13           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF14           | V <sub>DDM3IO</sub>                  |                        |         |         |         |           |          |                 |         |                   | V <sub>DDM3IO</sub> |

| AF15           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF16           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF17           | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |                   | _                   |

| AF18           | V <sub>DDM3IO</sub>                  |                        |         |         |         |           |          |                 |         |                   | V <sub>DDM3IO</sub> |

| AF19           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF20           | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |                   | _                   |

| AF21           | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |                   | _                   |

| AF22           | M3_RESET                             |                        |         |         |         |           |          |                 |         |                   | V <sub>DDM3IO</sub> |

| AF23           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF24           | V <sub>DDDDR</sub>                   |                        |         |         |         |           |          |                 |         |                   | V <sub>DDDDR</sub>  |

| AF25           | GND                                  | 1                      |         |         |         |           |          |                 |         | 1                 | GND                 |

| AF26           | V <sub>DDDDR</sub>                   | 1                      |         |         |         |           |          |                 |         | 1                 | V <sub>DDDDR</sub>  |

| AF27           | GND                                  |                        |         |         |         |           |          |                 |         |                   | GND                 |

| AF28           | V <sub>DDDDR</sub>                   |                        |         |         |         |           |          |                 |         |                   | V <sub>DDDDR</sub>  |

| AG1            | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |                   | _                   |

| AG2            | GPIO16/IRQ0 <sup>3, 6</sup>          |                        |         |         |         | GPI       | 0/IRQ    |                 |         |                   | V <sub>DDIO</sub>   |

| AG3            | TDM0TCLK                             | 1                      | İ       |         |         |           | DM       |                 |         |                   | V <sub>DDIO</sub>   |

### Table 1. Signal List by Ball Number (continued)

|                |                                     | Power-               |         | List by |         | -       | exing Mo | -       |         |         |                     |

|----------------|-------------------------------------|----------------------|---------|---------|---------|---------|----------|---------|---------|---------|---------------------|

| Ball<br>Number | Signal Name                         | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011) | 4 (100)  | 5 (101) | 6 (110) | 7 (111) | Ref.<br>Supply      |

| AG4            | TDM0RSYN/RCW_SRC0                   | RCW_<br>SRC0         |         | TDM     |         |         |          |         |         |         | V <sub>DDIO</sub>   |

| AG5            | TDMORCLK                            |                      |         |         |         | т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG6            | TDM0TDAT/RCW_SRC1                   | RCW_<br>SRC1         |         |         |         | Т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG7            | TDM2TSYN/RC7                        | RC7                  |         | TDM     |         |         |          |         |         |         | V <sub>DDIO</sub>   |

| AG8            | TDM2RCLK                            |                      |         |         |         | Т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG9            | TDM2RSYN/RC5                        | RC5                  |         |         |         | Т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG10           | GPIO24/IRQ6 <sup>3, 6</sup> /SPISEL |                      |         |         |         | GPIO/   | IRQ/SPI  |         |         |         | V <sub>DDIO</sub>   |

| AG11           | GPIO23/IRQ53, 6/SPIMISO             |                      |         |         |         | GPIO/   | IRQ/SPI  |         |         |         | V <sub>DDIO</sub>   |

| AG12           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | —                   |

| AG13           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG14           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG15           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG16           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG17           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | _                   |

| AG18           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AG19           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG20           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG21           | V <sub>DDM3IO</sub>                 |                      |         |         |         |         |          |         |         |         | V <sub>DDM3IO</sub> |

| AG22           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG23           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG24           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG25           | V <sub>DDDDR</sub>                  |                      |         |         |         |         |          |         |         |         | V <sub>DDDDR</sub>  |

| AG26           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG27           | V <sub>DDDDR</sub>                  |                      |         |         |         |         |          |         |         |         | V <sub>DDDDR</sub>  |

| AG28           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AH1            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | _                   |

| AH2            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH3            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH4            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | _                   |

| AH5            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH6            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH7            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | <u> </u>            |

| AH8            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH9            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | _                   |

|                | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH10           | Reserved <sup>1</sup>               | -                    |         |         |         |         |          |         |         |         |                     |

| AH11           |                                     | -                    |         |         |         |         |          |         |         |         |                     |

| AH12           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH13           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH14           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH15           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | —                   |

| AH16           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | —                   |

Table 1. Signal List by Ball Number (continued)

rical Characteristics

# 2.3 Default Output Driver Characteristics

Table 4 provides information on the characteristics of the output driver strengths.

#### Table 4. Output Drive Impedance

| Driver Type | Output Impedance (Ω)          |

|-------------|-------------------------------|

| DDR signal  | 18                            |

| DDR2 signal | 18<br>35 (half strength mode) |

# 2.4 Thermal Characteristics

Table 5 describes thermal characteristics of the MSC8144 for the FC-PBGA packages.

| Table 5. | Thermal      | Characteristics | for | the | MSC8144  |

|----------|--------------|-----------------|-----|-----|----------|

|          | I IIGI IIIGI | onunuotoristios |     |     | 11000144 |

| Characteristic                                                                                            | Symbol                   | FC-<br>29 ×           | Unit                          |      |

|-----------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|-------------------------------|------|

| Characteristic                                                                                            | Symbol                   | Natural<br>Convection | 200 ft/min<br>(1 m/s) airflow |      |

| Junction-to-ambient <sup>1, 2</sup>                                                                       | R <sub>θJA</sub>         | 20                    | 15                            | °C/W |

| Junction-to-ambient, four-layer board <sup>1, 3</sup>                                                     | R <sub>θJA</sub>         | 15                    | 12                            | °C/W |

| Junction-to-board (bottom) <sup>4</sup>                                                                   | R <sub>θJB</sub>         | 7                     |                               | °C/W |

| Junction-to-case <sup>5</sup>                                                                             | R <sub>θJC</sub>         | 0.8                   |                               | °C/W |

| Notes: 1. Junction temperature is a function of die temperature, ambient temperature, air fle resistance. | size, on-chip power diss |                       |                               | ```  |

2. Per JEDEC JESD51-2 with the single layer board (JESD51-3) horizontal.

3. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD 51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature.

rical Characteristics

#### **DDR (2.5V) SDRAM DC Electrical Characteristics** 2.5.1.2

Table 7 provides the recommended operating conditions for the DDR SDRAM component(s) of the MSC8144 when  $V_{DDDDR}(typ) = 2.5 V.$

| Parameter/Condition                             | Symbol             | Min                      | Мах                      | Unit |  |

|-------------------------------------------------|--------------------|--------------------------|--------------------------|------|--|

| I/O supply voltage <sup>1</sup>                 | V <sub>DDDDR</sub> | 2.3                      | 2.7                      | V    |  |

| I/O reference voltage <sup>2</sup>              | MV <sub>REF</sub>  | $0.49 \times V_{DDDDR}$  | $0.51 \times V_{DDDDR}$  | V    |  |

| I/O termination voltage <sup>3</sup>            | V <sub>TT</sub>    | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    |  |

| Input high voltage                              | V <sub>IH</sub>    | MV <sub>REF</sub> + 0.15 | V <sub>DDDDR</sub> + 0.3 | V    |  |

| Input low voltage                               | V <sub>IL</sub>    | -0.3                     | MV <sub>REF</sub> – 0.15 | V    |  |

| Output leakage current <sup>4</sup>             | I <sub>OZ</sub>    | -50                      | 50                       | μA   |  |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub>    | -16.2                    | —                        | mA   |  |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>    | 16.2                     | —                        | mA   |  |

### Table 7. DDR SDRAM DC Electrical Characteristics for V<sub>DDDDR</sub> (typ) = 2.5 V

Peak-to-peak noise on MV<sub>RFF</sub> may not exceed ±2% of the DC value.

V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be 3. equal to  $MV_{REF}$ . This rail should track variations in the DC level of  $V_{DDDDR}$ .

Output leakage is measured with all outputs are disabled,  $0 \text{ V} \leq \text{V}_{\text{OUT}} \leq \text{V}_{\text{DDDDR}}$ . 4.

Table 8 lists the current draw characteristics for MV<sub>REF</sub>.

### Table 8. Current Draw Characteristics for MV<sub>REF</sub>

|         | Parameter / Condition                                                                        |                    | Min | Max | Unit |  |  |

|---------|----------------------------------------------------------------------------------------------|--------------------|-----|-----|------|--|--|

| Current | draw for MV <sub>REF</sub>                                                                   | I <sub>MVREF</sub> | —   | 500 | μΑ   |  |  |

| Note:   | Note: The voltage regulator for $MV_{REF}$ must be able to supply up to 500 $\mu$ A current. |                    |     |     |      |  |  |

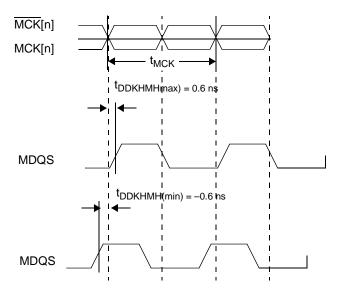

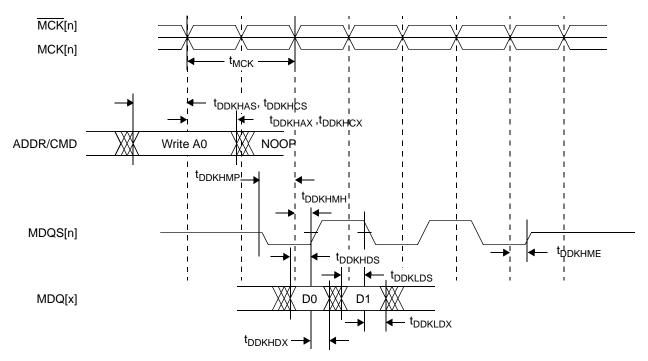

Figure 8 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 8. Timing for t<sub>DDKHMH</sub>

Figure 9. DDR SDRAM Output Timing

### rical Characteristics

### Table 25. Short Run Transmitter AC Timing Specifications—1.25 GBaud (continued)

| Characteristic       | Symbol          | Ra      | nge  | 11:0:4 | Netco                                                            |  |

|----------------------|-----------------|---------|------|--------|------------------------------------------------------------------|--|

| Characteristic       | Symbol          | Min Max |      | Unit   | Notes                                                            |  |

| Multiple output skew | S <sub>MO</sub> |         | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link |  |

| Unit Interval        | UI              | 800     | 800  | ps     | ±100 ppm                                                         |  |

### Table 26. Short Run Transmitter AC Timing Specifications—2.5 GBaud

| Characteristic              | Symbol              | Rai   | nge  | Unit             | Notes                                                                         |

|-----------------------------|---------------------|-------|------|------------------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit             | Notes                                                                         |

| Output Voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V                | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV <sub>PP</sub> |                                                                               |

| Deterministic Jitter        | J <sub>D</sub>      |       | 0.17 | UI <sub>PP</sub> |                                                                               |

| Total Jitter                | J <sub>T</sub>      |       | 0.35 | UI <sub>PP</sub> |                                                                               |

| Multiple Output skew        | S <sub>MO</sub>     |       | 1000 | ps               | Skew at the transmitter output between lanes of a multilane link              |

| Unit Interval               | UI                  | 400   | 400  | ps               | ±100 ppm                                                                      |

### Table 27. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Chanastanistia              | Complete            | Rai   | nge  | 11               | Netes                                                                         |

|-----------------------------|---------------------|-------|------|------------------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit             | Notes                                                                         |

| Output Voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V                | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV <sub>PP</sub> |                                                                               |

| Deterministic Jitter        | J <sub>D</sub>      |       | 0.17 | UI <sub>PP</sub> |                                                                               |

| Total Jitter                | J <sub>T</sub>      |       | 0.35 | UI <sub>PP</sub> |                                                                               |

| Multiple output skew        | S <sub>MO</sub>     |       | 1000 | ps               | Skew at the transmitter output between lanes of a multilane link              |

| Unit Interval               | UI                  | 320   | 320  | ps               | ±100 ppm                                                                      |

### Table 28. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Okonostariatia              | Complexed           | Rai   | nge  | 11               | Natas                                                                         |

|-----------------------------|---------------------|-------|------|------------------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit             | Notes                                                                         |

| Output Voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V                | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV <sub>PP</sub> |                                                                               |

| Deterministic Jitter        | J <sub>D</sub>      |       | 0.17 | UI <sub>PP</sub> |                                                                               |

| Total Jitter                | J <sub>T</sub>      |       | 0.35 | UI <sub>PP</sub> |                                                                               |

| Multiple output skew        | S <sub>MO</sub>     |       | 1000 | ps               | Skew at the transmitter output between lanes of a multilane link              |

| Unit Interval               | UI                  | 800   | 800  | ps               | ±100 ppm                                                                      |

# NP

## 2.6.5.5 Receiver Specifications

LP-Serial receiver electrical and timing specifications are stated in the text and tables of this section. Receiver input impedance shall result in a differential return loss better that 10 dB and a common mode return loss better than 6 dB from 100 MHz to 0.8 × baud frequency. This includes contributions from internal circuitry, the package, and any external components related to the receiver. AC coupling components are included in this requirement. The reference impedance for return loss measurements is 100  $\Omega$  resistive for differential return loss and 25  $\Omega$  resistive for common mode.

|                                                    |                 | Ra   | nge               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------|-----------------|------|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min  | Max               | Unit             | Notes                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Differential Input Voltage                         | V <sub>IN</sub> | 200  | 1600              | mV <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>  | 0.37 |                   | UI <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

| Combined Deterministic and Random Jitter Tolerance | J <sub>DR</sub> | 0.55 |                   | UI <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

| Total Jitter Tolerance                             | JT              | 0.65 |                   | UI <sub>PP</sub> | Measured at receiver. Total jitter is composed of<br>three components, deterministic jitter, random jitter<br>and single frequency sinusoidal jitter. The sinusoidal<br>jitter may have any amplitude and frequency in the<br>unshaded region of Figure 13. The sinusoidal jitter<br>component is included to ensure margin for low<br>frequency jitter, wander, noise, crosstalk and other<br>variable system effects. |

| Multiple Input Skew                                | S <sub>MI</sub> |      | 24                | ns               | Skew at the receiver input between lanes of a multilane link                                                                                                                                                                                                                                                                                                                                                            |

| Bit Error Rate                                     | BER             |      | 10 <sup>-12</sup> |                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Unit Interval                                      | UI              | 800  | 800               | ps               | ±100 ppm                                                                                                                                                                                                                                                                                                                                                                                                                |

### Table 32. Receiver AC Timing Specifications—1.25 GBaud

### Table 33. Receiver AC Timing Specifications—2.5 GBaud

| Ol anna faciatia                                   | Characteristic Symbol Range |      | 11-24             | Natar            |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------|-----------------------------|------|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                     | Symbol                      | Min  | Max               | Unit             | Notes                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Differential Input Voltage                         | V <sub>IN</sub>             | 200  | 1600              | mV <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

| Deterministic Jitter Tolerance                     | J <sub>D</sub>              | 0.37 |                   | UI <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

| Combined Deterministic and Random Jitter Tolerance | $J_DR$                      | 0.55 |                   | UI <sub>PP</sub> | Measured at receiver                                                                                                                                                                                                                                                                                                                                                                                                    |

| Total Jitter Tolerance                             | JT                          | 0.65 |                   | UI <sub>PP</sub> | Measured at receiver. Total jitter is composed of<br>three components, deterministic jitter, random jitter<br>and single frequency sinusoidal jitter. The sinusoidal<br>jitter may have any amplitude and frequency in the<br>unshaded region of Figure 13. The sinusoidal jitter<br>component is included to ensure margin for low<br>frequency jitter, wander, noise, crosstalk and other<br>variable system effects. |

| Multiple Input Skew                                | S <sub>MI</sub>             |      | 24                | ns               | Skew at the receiver input between lanes of a multilane link                                                                                                                                                                                                                                                                                                                                                            |

| Bit Error Rate                                     | BER                         |      | 10 <sup>-12</sup> |                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Unit Interval                                      | UI                          | 400  | 400               | ps               | ±100 ppm                                                                                                                                                                                                                                                                                                                                                                                                                |

**Electrical Characteristics**

### Table 36. PCI AC Timing Specifications (continued)

|        |                                           | Devementer                                                                                                                                      | Symphol                                                                                                              | 33               | MHz            | 66  | WHz | Unit |

|--------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------|----------------|-----|-----|------|

|        | Parameter                                 |                                                                                                                                                 | Symbol                                                                                                               | Min              | Max            | Min | Max | Unit |

| Notes: | 1.                                        | See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.                                                                  |                                                                                                                      |                  |                |     |     |      |

|        | 2.                                        | All PCI signals are measured from $0.5 \times V_{DDIO}$ of the rising edge of PCI_CLK_IN to $0.4 \times V_{DDIO}$ of the signal in question for |                                                                                                                      |                  |                |     |     |      |

|        |                                           | 3.3-V PCI signaling levels.                                                                                                                     |                                                                                                                      |                  |                |     |     |      |

|        | 3.                                        | For purposes of active/float timing                                                                                                             | urposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered |                  |                |     |     |      |

|        |                                           | through the component pin is less than or equal to the leakage current specification.                                                           |                                                                                                                      |                  |                |     |     |      |

|        | 4. Input timings are measured at the pin. |                                                                                                                                                 |                                                                                                                      |                  |                |     |     |      |

|        | 5.                                        | The reset assertion timing requirer                                                                                                             | ment for HRES                                                                                                        | ET is in Table 1 | 9 and Figure 7 |     |     |      |

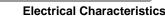

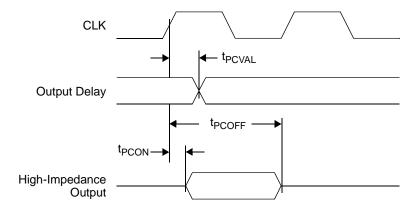

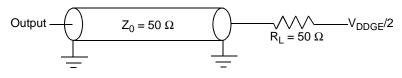

Figure 15 provides the AC test load for the PCI.

Figure 15. PCI AC Test Load

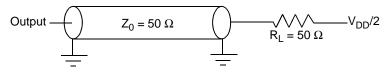

Figure 16 shows the PCI input AC timing conditions.

Figure 16. PCI Input AC Timing Measurement Conditions

Figure 17 shows the PCI output AC timing conditions.

Figure 17. PCI Output AC Timing Measurement Condition

#### **TDM** Timing 2.6.7

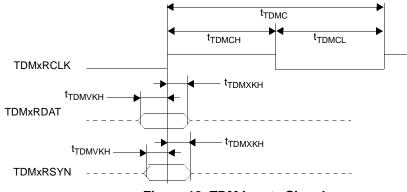

Table 37. TDM Timing

| Characteristic                                                                                                      | Symbol               | Expression               | Min | Max  | Units |

|---------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------|-----|------|-------|

| TDMxRCLK/TDMxTCLK                                                                                                   | t <sub>TDMC</sub>    | TC1                      | 16  | —    | ns    |

| TDMxRCLK/TDMxTCLK high pulse width                                                                                  | t <sub>TDMCH</sub>   | $(0.5\pm0.1)\times TC^4$ | 7   | —    | ns    |

| TDMxRCLK/TDMxTCLK low pulse width                                                                                   | t <sub>TDMCL</sub>   | $(0.5\pm0.1)\times TC^4$ | 7   | —    | ns    |

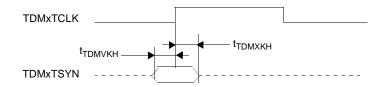

| TDM receive all input setup time related to TDMxRCLK<br>TDMxTSYN input setup time related to TDMxTCLK in TSO=0 mode | <sup>t</sup> томукн  |                          | 3.6 | _    | ns    |

| TDM receive all input hold time related to TDMxRCLK<br>TDMxTSYN input hold time related to TDMxTCLK in TSO=0 mode   | <sup>t</sup> томхкн  |                          | 1.9 | -    | ns    |

| TDMxTCLK high to TDMxTDAT output active <sup>2</sup>                                                                | t <sub>TDMDHOX</sub> |                          | 2.5 | _    | ns    |

| TDMxTCLK high to TDMxTDAT output valid <sup>2</sup>                                                                 | t <sub>TDMDHOV</sub> |                          | _   | 9.8  | ns    |

| All output hold time (except TDMxTSYN) <sup>3</sup>                                                                 | t <sub>TDMHOX</sub>  |                          | 2.5 | _    | ns    |

| TDMxTCLK high to TDMxTDAT output high impedance <sup>2</sup>                                                        | t <sub>TDMDHOZ</sub> |                          | _   | 9.8  | ns    |

| TDMxTCLK high to TDMxTSYN output valid <sup>2</sup>                                                                 | t <sub>TDMSHOV</sub> |                          |     | 9.25 | ns    |

| TDMxTSYN output hold time <sup>3</sup>                                                                              | t <sub>TDMSHOX</sub> |                          | 2.0 | 1 –  | ns    |

- Values are based on 20 pF capacitive load. 2.

- Values are based on 10 pF capacitive load. 3.

- 4. The expression is for common calculations only.

Figure 18 shows the TDM input AC timing.

For some TDM modes, receive data and receive sync are input on other pins. This timing is also valid for them. See Note: the MSC8144 Reference Manual.

Figure 19 shows TDMxTSYN AC timing in TSO=0 mode.

Figure 20 shows the TDM Output AC timing

Figure 26 provides the AC test load.

Figure 26. AC Test Load

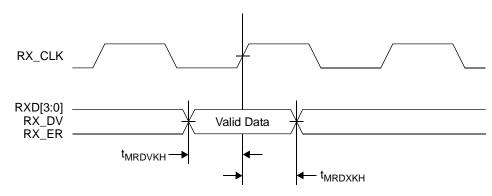

Figure 27 shows the MII receive AC timing diagram.

Figure 27. MII Receive AC Timing

## 2.6.10.4 RMII Transmit and Receive AC Timing Specifications

Table 43 provides the RMII transmit and receive AC timing specifications.

| Parameter/Condition                                                                           | Symbol <sup>1</sup>                 | Min | Max | Unit |

|-----------------------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|

| REF_CLK duty cycle                                                                            | t <sub>RMXH</sub> /t <sub>RMX</sub> | 35  | 65  | %    |

| REF_CLK to RMII data TXD[1–0], TX_EN delay                                                    | t <sub>RMTKHDX</sub>                | 2   | 10  | ns   |

| RXD[1–0], CRS_DV, RX_ER setup time to REF_CLK                                                 | t <sub>RMRDVKH</sub>                | 4.0 | —   | ns   |

| RXD[1–0], CRS_DV, RX_ER hold time to REF_CLK                                                  | t <sub>RMRDXKH</sub>                | 2.0 | _   | ns   |

| Typical REF_CLK clock period (t <sub>RMX</sub> ) is 20 ns                                     |                                     |     |     |      |

| Notes:1.Typical REF_CLK clock period (t <sub>RMX</sub> ) is 20 ns2.Program GCR4 as 0x00001405 |                                     |     |     |      |

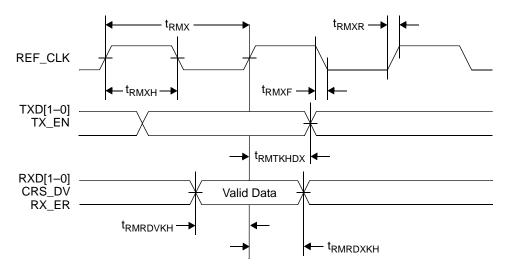

Figure 28 shows the RMII transmit and receive AC timing diagram.

Figure 28. RMII Transmit and Receive AC Timing

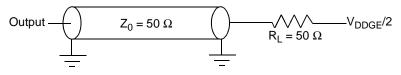

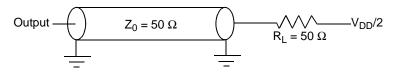

Figure 29 provides the AC test load.

Figure 29. AC Test Load

### 2.6.10.5 SMII AC Timing Specification

### Table 44. SMII Mode Signal Timing

| Characteristics                                                                                                                   | Symbol              | Min | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|------|

| ETHSYNC_IN, ETHRXD to ETHCLOCK rising edge setup time                                                                             | t <sub>SMDVKH</sub> | 1.5 | —   | ns   |

| ETHCLOCK rising edge to ETHSYNC_IN, ETHRXD hold time                                                                              | t <sub>SMDXKH</sub> | 1.0 | —   | ns   |

| ETHCLOCK rising edge to ETHSYNC, ETHTXD output delay                                                                              | t <sub>SMXR</sub>   | 1.5 | 5.0 | ns   |

| Notes:1.Typical REF_CLK clock period is 8ns2.Measured using a 5 pF load.3.Measured using a 15 pF load4.Program GCR4 as 0x00002008 |                     |     |     |      |

Figure 30 shows the SMII Mode signal timing.

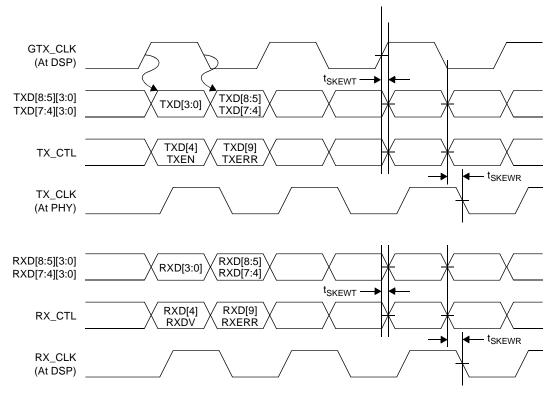

Figure 31 shows the RGMII AC timing and multiplexing diagrams.

Figure 31. RGMII AC Timing and Multiplexing

# 2.6.11 ATM/UTOPIA/POS Timing

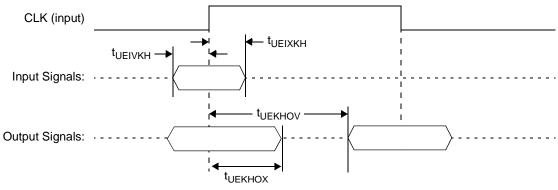

Table 47 provides the ATM/UTOPIA/POS input and output AC timing specifications.

| Characteristic                                     | Symbol              | Min | Max | Unit |  |  |

|----------------------------------------------------|---------------------|-----|-----|------|--|--|

| Outputs—External clock delay                       | t <sub>UEKHOV</sub> | 1   | 9   | ns   |  |  |

| Outputs—External clock High Impedance <sup>1</sup> | t <sub>UEKHOX</sub> | 1   | 9   | ns   |  |  |

**t**UEIVKH

t<sub>UEIXKH</sub>

#### Table 47. ATM/UTOPIA/POS AC Timing (External Clock) Specifications

Notes: 1. Not tested. Guaranteed by design.

Inputs-External clock input setup time

Inputs-External clock input hold time

Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are

measured at the pin. Although the specifications generally reference the rising edge of the clock, these AC timing diagrams

also apply when the falling edge is the active edge.

4

1

Figure 32 provides the AC test load for the ATM/UTOPIA/POS.

Figure 32. ATM/UTOPIA/POS AC Test Load

Figure 33 shows the ATM/UTOPIA/UTOPIA timing with external clock.

Figure 33. ATM/UTOPIAPOS AC Timing (External Clock)

ns

ns

# 2.6.12 SPI Timing

Table 48 lists the SPI input and output AC timing specifications.

Table 48. SPI AC Timing Specifications <sup>1</sup>

| Characteristic                                           | Symbol <sup>2</sup> | Min | Max | Unit |

|----------------------------------------------------------|---------------------|-----|-----|------|

| SPI outputs valid—Master mode (internal clock) delay     | t <sub>NIKHOV</sub> |     | 6   | ns   |

| SPI outputs hold—Master mode (internal clock) delay      | t <sub>NIKHOX</sub> | 0.5 |     | ns   |

| SPI outputs valid—Slave mode (external clock) delay      | t <sub>NEKHOV</sub> |     | 8   | ns   |

| SPI outputs hold—Slave mode (external clock) delay       | t <sub>NEKHOX</sub> | 2   |     | ns   |

| SPI inputs—Master mode (internal clock input) setup time | t <sub>NIIVKH</sub> | 4   |     | ns   |

| SPI inputs—Master mode (internal clock) input hold time  | t <sub>NIIXKH</sub> | 0   |     | ns   |

| SPI inputs—Slave mode (external clock) input setup time  | t <sub>NEIVKH</sub> | 4   |     | ns   |

| SPI inputs—Slave mode (external clock) input hold time   | t <sub>NEIXKH</sub> | 2   |     | ns   |

Notes: 1. Output specifications are measured from the 50 percent level of the rising edge of CLKIN to the 50 percent level of the signal. Timings are measured at the pin.

2. The symbols for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>NIKHOX</sub> symbolizes the internal timing (NI) for the time SPICLK clock reference (K) goes to the high state (H) until outputs (O) are invalid (X).</sub>

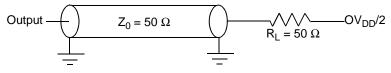

Figure 34 provides the AC test load for the SPI.

Figure 34. SPI AC Test Load

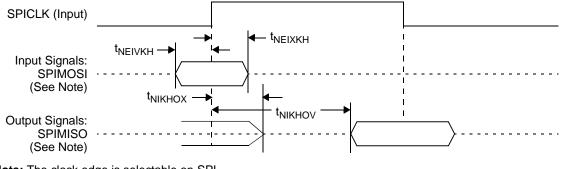

Figure 35 and Figure 36 represent the AC timings from Table 48. Note that although the specifications generally reference the rising edge of the clock, these AC timing diagrams also apply when the falling edge is the active edge.

Figure 35 shows the SPI timings in slave mode (external clock).

Note: The clock edge is selectable on SPI.

### Figure 35. SPI AC Timing in Slave Mode (External Clock)

Figure 36 shows the SPI timings in master mode (internal clock).

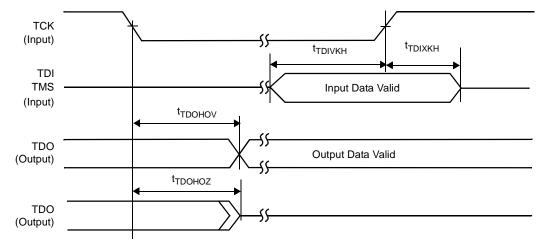

Figure 40 shows the test access port timing diagram

Figure 40. Test Access Port Timing

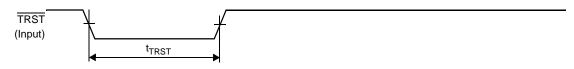

Figure 41 shows the TRST timing diagram.

# 3 Hardware Design Considerations

The following sections discuss areas to consider when the MSC8144 device is designed into a system.

# 3.1 Start-up Sequencing Recommendations

# 3.1.1 Power-on Sequence

Use the following guidelines for power-on sequencing:

- There are no dependencies in power-on/power-off sequence between V<sub>DDM3</sub> and V<sub>DD</sub> supplies.

- There are no dependencies in power-on/power-off sequence between RapidIO supplies:  $V_{DDSXC}$ ,  $V_{DDSXP}$ ,  $V_{DDRIOPLL}$  and other MSC8144 supplies.

- V<sub>DDPLL</sub> should be coupled with the V<sub>DD</sub> power rail with extremely low impedance path.

External voltage applied to any input line must not exceed the related to this port I/O supply by more than 0.6 V at any time, including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for configuration purposes. This is an acceptable exception to the rule during start-up. However, each such input can draw up to 80 mA per input pin per MSC8144 device in the system during start-up. An assertion of the inputs to the high voltage level before power-up should be with slew rate less than 4 V/ns.

ware Design Considerations

| Signal Name        | Pin Connection |

|--------------------|----------------|

| MDM[0-3]           | NC             |

| MBA[0-2]           | NC             |

| MCAS               | NC             |

| MCKE[0-1]          | NC             |

| MODT[0-1]          | NC             |

| MDIC[0-1]          | NC             |

| MRAS               | NC             |

| MWE                | NC             |

| MECC[0-7]          | NC             |

| ECC_MDM            | NC             |

| ECC_MDQS           | NC             |

| ECC_MDQS           | NC             |

| MV <sub>REF</sub>  | GND            |

| V <sub>DDDDR</sub> | GND            |

### Table 51. Connectivity of DDR Related Pins When the DDR Interface Is Not Used (continued)

## 3.4.1.2 16-Bit DDR Memory Only

Table 52 lists unused pin connection when using 16-bit DDR memory. The 16 most significant data lines are not used.

| Signal Name | Pin connection                |

|-------------|-------------------------------|

| MDQ[0-15]   | in use                        |

| MDQ[16-31]  | pull-up to V <sub>DDDDR</sub> |

| MDQS[0-1]   | in use                        |

| MDQS[2-3]   | pull-down to GND              |

| MDQS[0-1]   | in use                        |

| MDQS[2-3]   | pull-up to V <sub>DDDDR</sub> |

| MA[0–15]    | in use                        |

| MCK[0-2]    | in use                        |

| MCK[0-2]    | in use                        |

| MCS[0-1]    | in use                        |

| MDM[0-1]    | in use                        |

| MDM[2-3]    | NC                            |

| MBA[0-2]    | in use                        |

| MCAS        | in use                        |

| MCKE[0-1]   | in use                        |

| MODT[0-1]   | in use                        |

| MDIC[0-1]   | in use                        |

| MRAS        | in use                        |

| Table 52 Connectivity | of DDR Related Pins When Using 16-bit DDR Mem | ory Only |

|-----------------------|-----------------------------------------------|----------|

|                       | of DDR Related 1 m3 when OSing 10-bit DDR Men |          |

ware Design Considerations

### Table 58. Connectivity of GE1 Related Pins When only a subset of the GE1 Interface Is required (continued)

| Signal Name  | Pin Connection |

|--------------|----------------|

| GE1_SGMII_TX | NC             |

| GE1_TD[0-3]  | NC             |

| GE1_TX_CLK   | GND            |

| GE1_TX_EN    | NC             |

| GE1_TX_ER    | NC             |

### 3.4.4.2 Ethernet Controller 2 (GE2) Related Pins

**Note:** Table 59 through Table 61 assume that the alternate function of the specified pin is not used. If the alternate function is used, connect the pin as required to support that function.

### 3.4.4.2.1 GE2 interface Is Not Used

Table 59 assumes that the GE2 pins are not used for any purpose (including any multiplexed function) and that  $V_{DDGE2}$  is tied to GND.

Table 59. Connectivity of GE2 Related Pins When the GE2 Interface Is Not Used

| Signal Name  | Pin Connection     |

|--------------|--------------------|

| GE2_RD[0-3]  | NC                 |

| GE2_RX_CLK   | NC                 |

| GE2_RX_DV    | NC                 |

| GE2_RX_ER    | NC                 |

| GE2_SGMII_RX | GND <sub>SXC</sub> |

| GE2_SGMII_RX | GND <sub>SXC</sub> |

| GE2_SGMII_TX | NC                 |

| GE2_SGMII_TX | NC                 |

| GE2_TCK      | Nc                 |

| GE2_TD[0-3]  | Nc                 |

| GE2_TX_EN    | NC                 |

### 3.4.4.2.2 Subset of GE2 Pins Required

When only a subset of the whole GE2 interface is used, such as for RMII, the unused GE2 pins should be connected as described in Table 60. The table assumes that the unused GE2 pins are not used for any purpose (including any multiplexed functions) and that  $V_{DDGE2}$  is tied to either 2.5 V or 3.3 V.

### Table 60. Connectivity of GE1 Related Pins When only a subset of the GE1 Interface Is required

| Signal Name  | Pin Connection     |

|--------------|--------------------|

| GE2_RD[0-3]  | GND                |

| GE2_RX_CLK   | GND                |

| GE2_RX_DV    | GND                |

| GE2_RX_ER    | GND                |

| GE2_SGMII_RX | GND <sub>SXC</sub> |

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale, the Freescale logo, CodeWarrior, and StarCore are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. QUICC Engine is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2007-2010 Freescale Semiconductor, Inc.

Document Number: MSC8144 Rev. 16 5/2010