# E·XFL

### NXP USA Inc. - KMC8144VT800B Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                                         |

|-------------------------|----------------------------------------------------------------------------------|

| Туре                    | SC3400 Core                                                                      |

| Interface               | EBI/EMI, Ethernet, I <sup>2</sup> C, PCI, Serial RapidIO, SPI, TDM, UART, UTOPIA |

| Clock Rate              | 800MHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                       |

| On-Chip RAM             | 10.5MB                                                                           |

| Voltage - I/O           | 3.30V                                                                            |

| Voltage - Core          | 1.00V                                                                            |

| Operating Temperature   | 0°C ~ 90°C (TJ)                                                                  |

| Mounting Type           | Surface Mount                                                                    |

| Package / Case          | 783-BBGA, FCBGA                                                                  |

| Supplier Device Package | 783-FCPBGA (29x29)                                                               |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmc8144vt800b            |

|                         |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ssignments and Reset States

## 1 Pin Assignments and Reset States

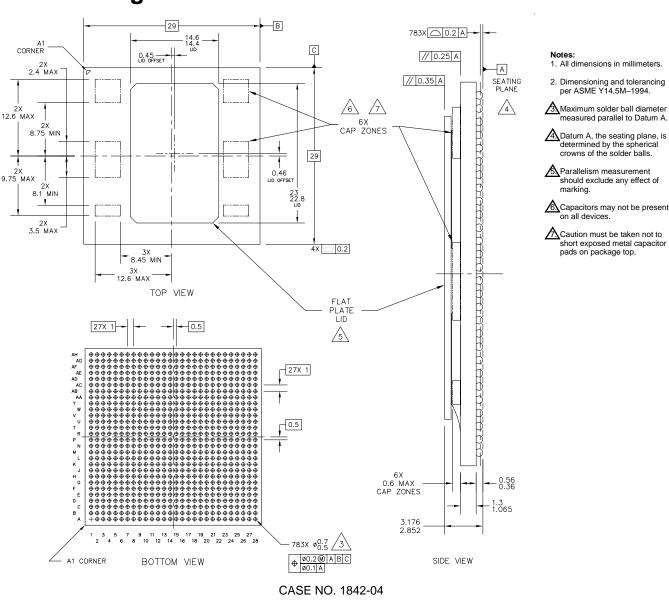

This section includes diagrams of the MSC8144 package ball grid array layouts and tables showing how the pinouts are allocated for the package.

## 1.1 FC-PBGA Ball Layout Diagrams

Top and bottom views of the FC-PBGA package are shown in Figure 3 and Figure 4 with their ball location index numbers.

#### Top View 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 1 2 3 4 5 6 7 8 9 26 27 28 А В С D Е F G н J Κ L Μ Ν Р R т U V W Υ AA AB AC AD AE AF AG AH

Figure 3. MSC8144 FC-PBGA Package, Top View

|                |                                      | Power- I/O Multiplexing Mode <sup>2</sup> |         |                                                                |           |           |            |           |              |                    |                       |

|----------------|--------------------------------------|-------------------------------------------|---------|----------------------------------------------------------------|-----------|-----------|------------|-----------|--------------|--------------------|-----------------------|

| Ball<br>Number | Signal Name                          | On<br>Reset<br>Value                      | 0 (000) | 1 (001)                                                        | 2 (010)   | 3 (011)   | 4 (100)    | 5 (101)   | 6 (110)      | 7 (111)            | Ref.<br>Supply        |

| B10            | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | —                     |

| B11            | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | _                     |

| B12            | SRIO_RXD0                            |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXC</sub>    |

| B13            | GND <sub>SXC</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | GND <sub>SXC</sub>    |

| B14            | SRIO_RXD1                            |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXC</sub>    |

| B15            | GND <sub>SXC</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | GND <sub>SXC</sub>    |

| B16            | SRIO_REF_CLK                         |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXC</sub>    |

| B17            | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | _                     |

| B18            | V <sub>DDSXC</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXC</sub>    |

| B19            | SRIO_RXD2/<br>GE1_SGMII_RX           |                                           | SG      | MII suppo                                                      | rt on SER | DES is en | abled by I | Reset Con | figuration V | Vord               | V <sub>DDSXC</sub>    |

| B20            | GND <sub>SXC</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | GND <sub>SXC</sub>    |

| B21            | SRIO_RXD3/<br>GE2_SGMII_RX           |                                           | SG      | SGMII support on SERDES is enabled by Reset Configuration Word |           |           |            |           |              | V <sub>DDSXC</sub> |                       |

| B22            | GND <sub>SXC</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | GND <sub>SXC</sub>    |

| B23            | GND <sub>SXP</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | GND <sub>SXP</sub>    |

| B24            | MDQ27                                |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDDDR</sub>    |

| B25            | V <sub>DDDDR</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDDDR</sub>    |

| B26            | GND                                  |                                           |         |                                                                |           |           |            |           |              |                    | GND                   |

| B27            | V <sub>DDDDR</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDDDR</sub>    |

| B28            | MDQS3                                |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDDDR</sub>    |

| C1             | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | _                     |

| C2             | GE2_RX_CLK/PCI_AD29                  |                                           |         | Ethe                                                           | rnet 2    | 1         | PCI        |           | Ethernet 2   | 1                  | V <sub>DDGE2</sub>    |

| C3             | V <sub>DDGE2</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDGE2</sub>    |

| C4             | TDM7RSYN/GE2_TD2/<br>PCI_AD2/UTP_TER |                                           | Т       | DM                                                             |           | PCI       |            | Ethe      | ernet 2      | UTOPIA             |                       |

| C5             | TDM7RCLK/GE2_RD2/<br>PCI_AD0/UTP_RVL |                                           | т       | DM                                                             |           | PCI       |            | Ethe      | ernet 2      | UTOPIA             | V <sub>DDGE2</sub>    |

| C6             | V <sub>DDGE2</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDGE2</sub>    |

| C7             | GE2_RD0/PCI_AD27                     |                                           |         | Ethe                                                           | rnet 2    |           | PCI        |           | Ethernet 2   |                    | V <sub>DDGE2</sub>    |

| C8             | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | —                     |

| C9             | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | _                     |

| C10            | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | —                     |

| C11            | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | —                     |

| C12            | V <sub>DDSXP</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXP</sub>    |

| C13            | SRIO_TXD0                            |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXP</sub>    |

| C14            | V <sub>DDSXP</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXP</sub>    |

| C15            | SRIO_TXD1                            |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXP</sub>    |

| C16            | GND <sub>SXC</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | GND <sub>SXC</sub>    |

| C17            | GND <sub>RIOPLL</sub>                |                                           |         |                                                                |           |           |            |           |              |                    | GND <sub>RIOPLL</sub> |

| C18            | Reserved <sup>1</sup>                |                                           |         |                                                                |           |           |            |           |              |                    | _                     |

| C19            | V <sub>DDSXP</sub>                   |                                           |         |                                                                |           |           |            |           |              |                    | V <sub>DDSXP</sub>    |

| C20            | SRIO_TXD2/GE1_SGMII_T                |                                           | SG      | MII suppo                                                      | rt on SER | DES is en | abled by I | Reset Con | figuration V | Vord               | V <sub>DDSXP</sub>    |

Table 1. Signal List by Ball Number (continued)

|                |                                      | Power-               | Power- I/O Multiplexing Mode <sup>2</sup> |                       |           |           |                    |           |               |                    |                    |

|----------------|--------------------------------------|----------------------|-------------------------------------------|-----------------------|-----------|-----------|--------------------|-----------|---------------|--------------------|--------------------|

| Ball<br>Number | Signal Name                          | On<br>Reset<br>Value | 0 (000)                                   | 1 (001)               | 2 (010)   | 3 (011)   | 4 (100)            | 5 (101)   | 6 (110)       | 7 (111)            | Ref.<br>Supply     |

| C21            | V <sub>DDSXP</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDSXP</sub> |

| C22            | SRIO_TXD3/GE2_SGMII_T                |                      | SG                                        | MII suppo             | rt on SER | DES is en | abled by I         | Reset Cor | nfiguration V | Vord               | V <sub>DDSXP</sub> |

| C23            | V <sub>DDSXP</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDSXP</sub> |

| C24            | MDQ26                                |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDDDR</sub> |

| C25            | MDQ25                                |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDDDR</sub> |

| C26            | MDM3                                 |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDDDR</sub> |

| C27            | GND                                  |                      |                                           |                       |           |           |                    |           |               |                    | GND                |

| C28            | MDQ24                                |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDDDR</sub> |

| D1             | Reserved <sup>1</sup>                |                      |                                           |                       |           |           |                    |           |               |                    | _                  |

| D2             | GE2_RD1/PCI_AD28                     |                      |                                           | Ethe                  | rnet 2    |           | PCI                |           | Ethernet 2    |                    | V <sub>DDGE2</sub> |

| D3             | GND                                  |                      |                                           |                       |           |           |                    |           |               |                    | GND                |

| D4             | TDM7TDAT/GE2_TD3/<br>PCI_AD3/UTP_TMD |                      | TC                                        | M                     |           | PCI       |                    | Eth       | ernet 2       | UTOPIA             | V <sub>DDGE2</sub> |

| D5             | TDM7RDAT/GE2_RD3/<br>PCI_AD1/UTP_STA |                      | TC                                        | рм                    |           | PCI       | Ethernet 2         |           | UTOPIA        | V <sub>DDGE2</sub> |                    |

| D6             | GE1_RD0/UTP_RD2/<br>PCI_CBE2         |                      | UTOPIA                                    | Ethe                  | rnet 1    | PCI       | UTC                | OPIA      | Ethernet 1    | UTOPIA             | V <sub>DDGE1</sub> |

| D7             | TDM7TCLK/GE2_TCK/<br>PCI_IDS/UTP_RER |                      | TC                                        | TDM PCI Ethernet 2 UT |           | UTOPIA    | V <sub>DDGE2</sub> |           |               |                    |                    |

| D8             | Reserved <sup>1</sup>                |                      |                                           |                       |           |           |                    |           |               |                    | _                  |

| D9             | Reserved <sup>1</sup>                |                      |                                           |                       |           |           |                    |           |               |                    | _                  |

| D10            | Reserved <sup>1</sup>                |                      |                                           |                       |           |           |                    |           |               |                    | _                  |

| D11            | Reserved <sup>1</sup>                |                      |                                           |                       |           |           |                    |           |               |                    | _                  |

| D12            | GND <sub>SXP</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | GND <sub>SXP</sub> |

| D13            | SRIO_TXD0                            |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDSXP</sub> |

| D14            | GND <sub>SXP</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | GND <sub>SXP</sub> |

| D15            | SRIO_TXD1                            |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDSXP</sub> |

| D16            | V <sub>DDSXC</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDSXC</sub> |

| D17            | Reserved <sup>1</sup>                |                      |                                           |                       |           |           |                    |           |               |                    |                    |

| D18            | Reserved <sup>1</sup>                |                      |                                           |                       |           |           |                    |           |               |                    |                    |

| D19            | GND <sub>SXP</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | GND <sub>SXP</sub> |

| D20            | SRIO_TXD2/GE1_SGMII_T<br>X           |                      | SG                                        | MII suppo             | rt on SER | DES is en | abled by I         | Reset Cor | nfiguration V | /ord               | V <sub>DDSXP</sub> |

| D21            | GND <sub>SXP</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | GND <sub>SXP</sub> |

| D22            | SRIO_TXD3/GE2_SGMII_T<br>X           |                      | SG                                        | MII suppo             | rt on SER | DES is en | abled by I         | Reset Cor | nfiguration V | /ord               | V <sub>DDSXP</sub> |

| D23            | GND <sub>SXP</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | GND <sub>SXP</sub> |

| D24            | MDQ23                                |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDDDR</sub> |

| D25            | V <sub>DDDDR</sub>                   |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDDDR</sub> |

| D26            | MDQ22                                |                      |                                           |                       |           |           |                    |           | 1             |                    | V <sub>DDDDR</sub> |

| D27            | MDQ21                                |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDDDR</sub> |

| D28            | MDQS2                                |                      |                                           |                       |           |           |                    |           |               |                    | V <sub>DDDDR</sub> |

| E1             | Reserved <sup>1</sup>                |                      |                                           |                       |           |           |                    |           |               |                    |                    |

| Ball   |                       | Power-<br>On   |         |         |         |         |         |         |         |          | Ref.                |

|--------|-----------------------|----------------|---------|---------|---------|---------|---------|---------|---------|----------|---------------------|

| Number | Signal Name           | Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011) | 4 (100) | 5 (101) | 6 (110) | 7 (111)  | Supply              |

| J8     | V <sub>DDIO</sub>     |                |         |         |         |         |         |         |         |          | V <sub>DDIO</sub>   |

| J9     | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J10    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J11    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J12    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J13    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J14    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J15    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J16    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J17    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J18    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J19    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J20    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J21    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J22    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J23    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J24    | V <sub>DDDDR</sub>    |                |         |         |         |         |         |         |         |          | V <sub>DDDDR</sub>  |

| J25    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J26    | V <sub>DDDDR</sub>    |                |         |         |         |         |         |         |         |          | V <sub>DDDDR</sub>  |

| J27    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J28    | V <sub>DDDDR</sub>    |                |         |         |         |         |         |         |         |          | V <sub>DDDDR</sub>  |

| K1     | Reserved <sup>1</sup> |                |         |         |         |         |         |         |         |          |                     |

| K2     | Reserved <sup>1</sup> |                |         |         |         |         |         |         |         |          | _                   |

| K3     | Reserved <sup>1</sup> |                |         |         |         |         |         |         |         |          | _                   |

| K4     | Reserved <sup>1</sup> |                |         |         |         |         |         |         |         |          |                     |

| K5     | V <sub>DDPLL2A</sub>  |                |         |         |         |         |         |         |         |          | V <sub>DDPLL2</sub> |

| K6     | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K7     | V <sub>DDPLL0A</sub>  |                |         |         |         |         |         |         |         |          | V <sub>DDPLL0</sub> |

| K8     | V <sub>DDPLL1A</sub>  |                |         |         |         |         |         |         |         |          | V <sub>DDPLL1</sub> |

| K9     | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K10    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K11    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K12    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K13    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K14    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K15    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K16    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K17    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K18    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K19    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K20    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K21    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K22    | V <sub>DDDDR</sub>    | _              |         |         |         |         |         |         |         | <u> </u> | V <sub>DDDDR</sub>  |

|                |                                            | Power-               | I/O Multiplexing Mode <sup>2</sup> |         |         |         |         |         |          |                   |                    |

|----------------|--------------------------------------------|----------------------|------------------------------------|---------|---------|---------|---------|---------|----------|-------------------|--------------------|

| Ball<br>Number | Signal Name                                | On<br>Reset<br>Value | 0 (000)                            | 1 (001) | 2 (010) | 3 (011) | 4 (100) | 5 (101) | 6 (110)  | 7 (111)           | Ref.<br>Supply     |

| R7             | V <sub>DDIO</sub>                          |                      |                                    |         |         |         |         |         |          |                   | V <sub>DDIO</sub>  |

| R8             | PCI_REQ                                    |                      |                                    | PCI     |         |         |         |         |          | V <sub>DDIO</sub> |                    |

| R9             | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R10            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R11            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R12            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R13            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R14            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R15            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R16            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R17            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R18            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R19            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R20            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R21            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R22            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| R23            | MODT0                                      |                      |                                    |         |         |         |         |         |          |                   | V <sub>DDDDR</sub> |

| R24            | MDIC1                                      |                      |                                    |         |         |         |         |         |          |                   | V <sub>DDDDR</sub> |

| R25            | MDIC0                                      |                      |                                    |         |         |         |         |         |          |                   | V <sub>DDDDR</sub> |

| R26            | MCAS                                       |                      |                                    |         |         |         |         |         |          |                   | V <sub>DDDDR</sub> |

| R27            | MWE                                        |                      |                                    |         |         |         |         |         |          |                   | V <sub>DDDDR</sub> |

| R28            | MCK2                                       |                      |                                    |         |         |         |         |         |          |                   | V <sub>DDDDR</sub> |

| T1             | Reserved <sup>1</sup>                      |                      |                                    |         |         |         |         |         |          |                   | _                  |

| T2             | UTP_RPRTY/PCI_AD21                         |                      | UTC                                | PIA     | PCI     |         | •       | UTOPIA  |          | •                 | V <sub>DDIO</sub>  |

| Т3             | UTP_RD13/PCI_AD17                          |                      | UTC                                | OPIA    | PCI     |         |         | UTOPIA  | L.       |                   | V <sub>DDIO</sub>  |

| T4             | V <sub>DDIO</sub>                          |                      |                                    |         |         |         |         |         |          |                   | V <sub>DDIO</sub>  |

| T5             | UTP_RD14/PCI_AD18                          |                      | UTC                                | DPIA    | PCI     |         | •       | UTOPIA  |          | •                 | V <sub>DDIO</sub>  |

| Т6             | UTP_RD15/PCI_AD19                          |                      | UTC                                | OPIA    | PCI     |         |         | UTOPIA  | L.       |                   | V <sub>DDIO</sub>  |

| T7             | PCI_TRDY                                   |                      |                                    |         |         | F       | PCI     |         |          |                   | V <sub>DDIO</sub>  |

| Т8             | PCI_DEVSEL/GPIO31/<br>IRQ3 <sup>3, 6</sup> |                      | GPIC                               | )/IRQ   |         | PCI     |         |         | GPIO/IRQ |                   | V <sub>DDIO</sub>  |

| Т9             | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T10            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T11            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T12            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T13            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T14            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T15            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T16            | GND                                        |                      | Ī                                  |         |         |         |         |         |          | Ī                 | GND                |

| T17            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T18            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T19            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| T20            | GND                                        |                      |                                    |         |         |         |         |         |          |                   | GND                |

| Dell           |                                      | Power- I/O Multiplexing Mode <sup>2</sup> |         |         |         |         |         |         |         |                   | Def                 |

|----------------|--------------------------------------|-------------------------------------------|---------|---------|---------|---------|---------|---------|---------|-------------------|---------------------|

| Ball<br>Number | Signal Name                          | Reset<br>Value                            | 0 (000) | 1 (001) | 2 (010) | 3 (011) | 4 (100) | 5 (101) | 6 (110) | 7 (111)           | Ref.<br>Supply      |

| AE19           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AE20           | V <sub>DDM3IO</sub>                  |                                           |         |         |         |         |         |         |         |                   | V <sub>DDM3IO</sub> |

| AE21           | Reserved <sup>1</sup>                |                                           |         |         |         |         |         |         |         |                   | _                   |

| AE22           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AE23           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AE24           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AE25           | V <sub>DDDDR</sub>                   |                                           |         |         |         |         |         |         |         |                   | V <sub>DDDDR</sub>  |

| AE26           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AE27           | V <sub>DDDDR</sub>                   |                                           |         |         |         |         |         |         |         |                   | V <sub>DDDDR</sub>  |

| AE28           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF1            | Reserved <sup>1</sup>                |                                           |         |         |         |         |         |         |         |                   | _                   |

| AF2            | V <sub>DDIO</sub>                    |                                           |         |         |         |         |         |         |         |                   | V <sub>DDIO</sub>   |

| AF3            | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF4            | TDM0RDAT/<br>RCFG_CLKIN_RNG          | RCFG_<br>CLKIN_<br>RNG                    |         | TDM     |         |         |         |         |         |                   | V <sub>DDIO</sub>   |

| AF5            | TDM0TSYN/RCW_SRC2                    | RCW_<br>SRC2                              |         | TDM     |         |         |         |         |         | V <sub>DDIO</sub> |                     |

| AF6            | TDM1RDAT/RC0                         | RC0                                       |         | TDM     |         |         |         |         |         | V <sub>DDIO</sub> |                     |

| AF7            | V <sub>DDIO</sub>                    |                                           |         |         |         |         |         |         |         |                   | V <sub>DDIO</sub>   |

| AF8            | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF9            | TDM2RDAT/RC4                         | RC4                                       |         |         | •       | Т       | DM      | •       |         |                   | V <sub>DDIO</sub>   |

| AF10           | TDM2TCLK                             |                                           |         |         |         | Т       | DM      |         |         |                   | V <sub>DDIO</sub>   |

| AF11           | GPIO22/IRQ4 <sup>3, 6</sup> /SPIMOSI |                                           |         |         |         | GPIO/   | IRQ/SPI |         |         |                   | V <sub>DDIO</sub>   |

| AF12           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF13           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF14           | V <sub>DDM3IO</sub>                  |                                           |         |         |         |         |         |         |         |                   | V <sub>DDM3IO</sub> |

| AF15           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF16           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF17           | Reserved <sup>1</sup>                |                                           |         |         |         |         |         |         |         |                   | _                   |

| AF18           | V <sub>DDM3IO</sub>                  |                                           |         |         |         |         |         |         |         |                   | V <sub>DDM3IO</sub> |

| AF19           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF20           | Reserved <sup>1</sup>                |                                           |         |         |         |         |         |         |         |                   | _                   |

| AF21           | Reserved <sup>1</sup>                |                                           |         |         |         |         |         |         |         |                   | _                   |

| AF22           | M3_RESET                             |                                           |         |         |         |         |         |         |         |                   | V <sub>DDM3IO</sub> |

| AF23           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF24           | V <sub>DDDDR</sub>                   |                                           |         |         |         |         |         |         |         |                   | V <sub>DDDDR</sub>  |

| AF25           | GND                                  | 1                                         |         |         |         |         |         |         |         | 1                 | GND                 |

| AF26           | V <sub>DDDDR</sub>                   | 1                                         |         |         |         |         |         |         |         | 1                 | V <sub>DDDDR</sub>  |

| AF27           | GND                                  |                                           |         |         |         |         |         |         |         |                   | GND                 |

| AF28           | V <sub>DDDDR</sub>                   |                                           |         |         |         |         |         |         |         |                   | V <sub>DDDDR</sub>  |

| AG1            | Reserved <sup>1</sup>                |                                           |         |         |         |         |         |         |         |                   | _                   |

| AG2            | GPIO16/IRQ0 <sup>3, 6</sup>          |                                           |         |         |         | GPI     | 0/IRQ   |         |         |                   | V <sub>DDIO</sub>   |

| AG3            | TDM0TCLK                             | 1                                         | İ       |         |         |         | DM      |         |         |                   | V <sub>DDIO</sub>   |

| Rating                                          | Symbol                                   | Value                             | Unit |  |

|-------------------------------------------------|------------------------------------------|-----------------------------------|------|--|

| M3 memory I/O and M3 memory charge pump voltage | V <sub>DDM3IO</sub><br>V <sub>25M3</sub> | -0.3 to 2.75                      | V    |  |

| Input M3 memory I/O voltage                     | V <sub>INM3IO</sub>                      | -0.3 to V <sub>DDM3IO</sub> + 0.3 | V    |  |

| Rapid I/O C voltage                             | V <sub>DDSXC</sub>                       | -0.3 to 1.21                      | V    |  |

| Rapid I/O P voltage                             | V <sub>DDSXP</sub>                       | -0.3 to 1.26                      | V    |  |

| Rapid I/O PLL voltage                           | V <sub>DDRIOPLL</sub>                    | -0.3 to 1.21                      | V    |  |

| Operating temperature                           | TJ                                       | -40 to 105                        | °C   |  |

| Storage temperature range                       | T <sub>STG</sub>                         | -55 to +150                       | °C   |  |

### Table 2. Absolute Maximum Ratings

2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

3. PLL supply voltage is specified at input of the filter and not at pin of the MSC8144 (see Figure 43)

## 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Rating                                                                                      | Symbol                                                               | Min                             | Nominal                      | Мах                           | Unit           |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------|------------------------------|-------------------------------|----------------|

| Core supply voltage<br>• 800 MHz (VT, SVT, TVT) and<br>1000 MHz (VT)                        | V <sub>DD</sub>                                                      | 0.97                            | 1.0                          | 1.05                          | V              |

| • 1000 MHz (SVT, TVT)                                                                       |                                                                      | 0.97                            | 1.0                          | 1.03                          | V              |

| PLL supply voltage<br>• 800 MHz (VT, SVT, TVT) and<br>1000 MHz (VT)                         | V <sub>DDPLL0</sub><br>V <sub>DDPLL1</sub><br>V <sub>DDPLL2</sub>    | 0.97                            | 1.0                          | 1.05                          | V              |

| • 1000 MHz (SVT, TVT)                                                                       | DDFLLZ                                                               | 0.97                            | 1.0                          | 1.03                          | V              |

| M3 memory Internal voltage                                                                  | V <sub>DDM3</sub>                                                    | 1.213                           | 1.25                         | 1.313                         | V              |

| DDR memory supply voltage <ul> <li>DDR mode</li> <li>DDR2 mode</li> </ul>                   | V <sub>DDDDR</sub>                                                   | 2.375<br>1.71                   | 2.5<br>1.8                   | 2.625<br>1.89                 | V<br>V         |

| DDR reference voltage                                                                       | MV <sub>REF</sub>                                                    | $0.49 \times V_{DDDDR}$ (nom)   | $0.5 \times V_{DDDDR}$ (nom) | $0.51 \times V_{DDDDR}$ (nom) | V              |

| Ethernet 1 I/O voltage<br>• 2.5 V mode<br>• 3.3 V mode                                      | V <sub>DDGE1</sub>                                                   | 2.375<br>3.135                  | 2.5<br>3.3                   | 2.625<br>3.465                | V<br>V         |

| Ethernet 2 I/O voltage<br>• 2.5 V mode<br>• 3.3 V mode                                      | V <sub>DDGE2</sub>                                                   | 2.375<br>3.135                  | 2.5<br>3.3                   | 2.625<br>3.465                | V<br>V         |

| I/O voltage excluding Ethernet,<br>DDR, M3, and RapidIO lines                               | V <sub>DDIO</sub>                                                    | 3.135                           | 3.3                          | 3.465                         | V              |

| M3 memory I/O and M3 charge<br>pump voltage                                                 | V <sub>DDM3IO</sub><br>V <sub>25M3</sub>                             | 2.375                           | 2.5                          | 2.625                         | V              |

| Rapid I/O C voltage                                                                         | V <sub>DDSXC</sub>                                                   | 0.97                            | 1.0                          | 1.05                          | V              |

| Rapid I/O P voltage<br>• Short run (haul) mode<br>• Long run (haul) mode                    | V <sub>DDSXP</sub>                                                   | 0.97<br>1.14                    | 1.0<br>1.2                   | 1.05<br>1.26                  | V<br>V         |

| Rapid I/O PLL voltage                                                                       | V <sub>DDRIOPLL</sub>                                                | 0.97                            | 1.0                          | 1.05                          | V              |

| Operating temperature range:<br>• Standard (VT)<br>• Intermediate (SVT)<br>• Extended (TVT) | T <sub>J</sub><br>T <sub>J</sub><br>T <sub>A</sub><br>T <sub>I</sub> | 0<br>0<br>40                    |                              | 90<br>105<br>—<br>105         | ວ°<br>ວິ<br>ວິ |

| Note: PLL supply voltage is sp                                                              | J                                                                    | he filter and not at pin of the | ne MSC8144 (see Figure       |                               | -              |

### **Table 3. Recommended Operating Conditions**

## 2.3 Default Output Driver Characteristics

Table 4 provides information on the characteristics of the output driver strengths.

#### Table 4. Output Drive Impedance

| Driver Type | Output Impedance (Ω)          |

|-------------|-------------------------------|

| DDR signal  | 18                            |

| DDR2 signal | 18<br>35 (half strength mode) |

## 2.4 Thermal Characteristics

Table 5 describes thermal characteristics of the MSC8144 for the FC-PBGA packages.

| Table 5. | Thermal      | Characteristics | for | the | MSC8144  |

|----------|--------------|-----------------|-----|-----|----------|

|          | I IIGI IIIGI | onunuotonistios |     |     | 11000144 |

| Characteristic                                                                                            | Symbol                   | FC-<br>29 ×           | Unit                          |      |

|-----------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|-------------------------------|------|

| Characteristic                                                                                            | Symbol                   | Natural<br>Convection | 200 ft/min<br>(1 m/s) airflow |      |

| Junction-to-ambient <sup>1, 2</sup>                                                                       | R <sub>θJA</sub>         | 20                    | 15                            | °C/W |

| Junction-to-ambient, four-layer board <sup>1, 3</sup>                                                     | R <sub>θJA</sub>         | 15                    | 12                            | °C/W |

| Junction-to-board (bottom) <sup>4</sup>                                                                   | R <sub>θJB</sub>         | 7                     |                               | °C/W |

| Junction-to-case <sup>5</sup>                                                                             | R <sub>θJC</sub>         | 0.8                   |                               | °C/W |

| Notes: 1. Junction temperature is a function of die temperature, ambient temperature, air fle resistance. | size, on-chip power diss |                       |                               | ```  |

2. Per JEDEC JESD51-2 with the single layer board (JESD51-3) horizontal.

3. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD 51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature.

### 2.5 DC Electrical Characteristics

This section describes the DC electrical characteristics for the MSC8144.

### 2.5.1 DDR SDRAM DC Electrical Characteristics

This section describes the DC electrical specifications for the DDR SDRAM interface of the MSC8144.

Note: DDR SDRAM uses  $V_{DDDDR}(typ) = 2.5 V$  and DDR2 SDRAM uses  $V_{DDDDR}(typ) = 1.8 V$ .

### 2.5.1.1 DDR2 (1.8 V) SDRAM DC Electrical Characteristics

Table 6 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the MSC8144 when  $V_{DDDDR}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol             | Min                       | Мах                       | Unit |

|--------------------------------------------------|--------------------|---------------------------|---------------------------|------|

| I/O supply voltage <sup>1</sup>                  | V <sub>DDDDR</sub> | 1.7                       | 1.9                       | V    |

| I/O reference voltage <sup>2</sup>               | MV <sub>REF</sub>  | $0.49 \times V_{DDDDR}$   | $0.51 	imes V_{DDDDR}$    | V    |

| I/O termination voltage <sup>3</sup>             | V <sub>TT</sub>    | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    |

| Input high voltage                               | V <sub>IH</sub>    | MV <sub>REF</sub> + 0.125 | V <sub>DDDDR</sub> + 0.3  | V    |

| Input low voltage                                | V <sub>IL</sub>    | -0.3                      | MV <sub>REF</sub> – 0.125 | V    |

| Output leakage current <sup>4</sup>              | I <sub>OZ</sub>    | -50                       | 50                        | μΑ   |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>    | -13.4                     | _                         | mA   |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>    | 13.4                      | —                         | mA   |

MV<sub>REF</sub> is expected to be equal to 0.5 × V<sub>DDDDR</sub>, and to track V<sub>DDDDR</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of V<sub>DDDDR</sub>.

4. Output leakage is measured with all outputs are disabled,  $0 V \le V_{OUT} \le V_{DDDDR}$ .

#### **DDR (2.5V) SDRAM DC Electrical Characteristics** 2.5.1.2

Table 7 provides the recommended operating conditions for the DDR SDRAM component(s) of the MSC8144 when  $V_{DDDDR}(typ) = 2.5 V.$

| Parameter/Condition                             | Symbol             | Min                      | Мах                      | Unit |  |

|-------------------------------------------------|--------------------|--------------------------|--------------------------|------|--|

| I/O supply voltage <sup>1</sup>                 | V <sub>DDDDR</sub> | 2.3                      | 2.7                      | V    |  |

| I/O reference voltage <sup>2</sup>              | MV <sub>REF</sub>  | $0.49 \times V_{DDDDR}$  | $0.51 \times V_{DDDDR}$  | V    |  |

| I/O termination voltage <sup>3</sup>            | V <sub>TT</sub>    | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    |  |

| Input high voltage                              | V <sub>IH</sub>    | MV <sub>REF</sub> + 0.15 | V <sub>DDDDR</sub> + 0.3 | V    |  |

| Input low voltage                               | V <sub>IL</sub>    | -0.3                     | MV <sub>REF</sub> – 0.15 | V    |  |

| Output leakage current <sup>4</sup>             | I <sub>OZ</sub>    | -50                      | 50                       | μA   |  |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub>    | -16.2                    | —                        | mA   |  |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>    | 16.2                     | —                        | mA   |  |

### Table 7. DDR SDRAM DC Electrical Characteristics for V<sub>DDDDR</sub> (typ) = 2.5 V

Peak-to-peak noise on MV<sub>RFF</sub> may not exceed ±2% of the DC value.

V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be 3. equal to  $MV_{REF}$ . This rail should track variations in the DC level of  $V_{DDDDR}$ .

Output leakage is measured with all outputs are disabled,  $0 \text{ V} \leq \text{V}_{\text{OUT}} \leq \text{V}_{\text{DDDDR}}$ . 4.

Table 8 lists the current draw characteristics for MV<sub>REF</sub>.

### Table 8. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition              |                                                                                                | Symbol             | Min | Max | Unit |  |

|------------------------------------|------------------------------------------------------------------------------------------------|--------------------|-----|-----|------|--|

| Current draw for MV <sub>REF</sub> |                                                                                                | I <sub>MVREF</sub> | —   | 500 | μΑ   |  |

| Note:                              | Note: The voltage regulator for MV <sub>REF</sub> must be able to supply up to 500 μA current. |                    |     |     |      |  |

### 2.6.3 Reset Timing

The MSC8144 has several inputs to the reset logic:

- Power-on reset (PORESET)

- External hard reset (HRESET)

- External soft reset (SRESET)

- Software watchdog reset

- JTAG reset

- RapidIO reset

- Software hard reset

- Software soft reset

All MSC8144 reset sources are fed into the reset controller, which takes different actions depending on the source of the reset. The reset status register indicates the most recent sources to cause a reset. Table 17 describes the reset sources.

| Name                                     | Direction     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-on reset<br>(PORESET)              | Input         | Initiates the power-on reset flow that resets the MSC8144 and configures various attributes of the MSC8144. On PORESET, the entire MSC8144 device is reset. All PLLs states is reset, HRESET and SRESET are driven, the extended cores are reset, and system configuration is sampled. The reset source and word are configured only when PORESET is asserted.                                                                                                                                                |

| Extern <u>al hard</u><br>reset (HRESET)  | Input/ Output | Initiates the hard reset flow that configures various attributes of the MSC8144. While HRESET is asserted, SRESET is also asserted. HRESET is an open-drain pin. Upon hard reset, HRESET and SRESET are driven, the extended cores are reset, and system configuration is sampled. Note that the RCW (reset Configuration Word) is not reloaded during HRESET assertion after out of power on reset sequence. The reset configuration word is described in the Reset chapter in the MSC8144 Reference Manual. |

| External soft reset<br>(SRESET)          | Input/ Output | Initiates the soft reset flow. The MSC8144 detects an external assertion of SRESET only if it occurs while the MSC8144 is not asserting reset. SRESET is an open-drain pin. Upon soft reset, SRESET is driven, the extended cores are reset, and system configuration is maintained.                                                                                                                                                                                                                          |

| Host reset<br>command through<br>the TAP | Internal      | When a host reset command is written through the Test Access Port (TAP), the TAP logic asserts the soft reset signal and an internal soft reset sequence is generated.                                                                                                                                                                                                                                                                                                                                        |

| Software<br>watchdog reset               | Internal      | When the MSC8144 watchdog count reaches zero, a software watchdog reset is signalled. The enabled software watchdog event then generates an internal hard reset sequence.                                                                                                                                                                                                                                                                                                                                     |

| RapidIO reset                            | Internal      | When the RapidIO logic asserts the RapidIO hard reset signal, it generates an internal hard reset sequence.                                                                                                                                                                                                                                                                                                                                                                                                   |

| Software hard reset                      | Internal      | A hard reset sequence can be initialized by writing to a memory mapped register (RCR)                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Software soft reset                      | Internal      | A soft reset sequence can be initialized by writing to a memory mapped register (RCR)                                                                                                                                                                                                                                                                                                                                                                                                                         |

### Table 17. Reset Sources

#### Table 18 summarizes the reset actions that occur as a result of the different reset sources. Table 18. Reset Actions for Each Reset Source

| Reset Action/Reset Source                                                 | Po <u>wer-On Re</u> set<br>(PORESET) | Hard Reset (HRESET)                                                 | Sof                                 | t Reset (SRESET)                            |

|---------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------|-------------------------------------|---------------------------------------------|

| Resel Action/Resel Source                                                 | External only                        | External or Internal<br>(Software Watchdog,<br>Software or RapidIO) | External or<br>internal<br>Software | JTAG Command:<br>EXTEST, CLAMP, or<br>HIGHZ |

| Configuration pins sampled (Refer to <b>Section 2.6.3.2</b> for details). | Yes                                  | No                                                                  | No                                  | No                                          |

| PLL state reset                                                           | Yes                                  | No                                                                  | No                                  | No                                          |

| Select reset configuration source                                         | Yes                                  | No                                                                  | No                                  | No                                          |

| System reset configuration write                                          | Yes                                  | No                                                                  | No                                  | No                                          |

### 2.6.5.8 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (baud frequency)/1667 is applied to the jitter. The data pattern for template measurements is the continuous jitter test pattern (CJPAT) defined in Annex 48A of **IEEE** Std. 802.3ae. All lanes of the LP-Serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. The amount of data represented in the eye shall be adequate to ensure that the bit error ratio is less than  $10^{-12}$ . The eye pattern shall be measured with AC coupling and the compliance template centered at 0 Volts differential. The left and right edges of the template shall be aligned with the mean zero crossing points of the measured data eye. The load for this test shall be 100  $\Omega$  resistive ±5% differential to 2.5 GHz.

### 2.6.5.9 Jitter Test Measurements

For the purpose of jitter measurement, the effects of a single-pole high pass filter with a 3 dB point at (baud frequency)/1667 is applied to the jitter. The data pattern for jitter measurements is the Continuous Jitter Test Pattern (CJPAT) pattern defined in Annex 48A of **IEEE** Std. 802.3ae. All lanes of the LP-Serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. Jitter shall be measured with AC coupling and at 0 V differential. Jitter measurement for the transmitter (or for calibration of a jitter tolerance setup) shall be performed with a test procedure resulting in a BER curve such as that described in Annex 48B of **IEEE** Std. 802.3ae.

### 2.6.5.10 Transmit Jitter