### NXP USA Inc. - MSC8144TVT1000B Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | SC3400 Core                                                             |

| Interface               | Ethernet, I <sup>2</sup> C, SPI, TDM, UART, UTOPIA                      |

| Clock Rate              | 1GHz                                                                    |

| Non-Volatile Memory     | External                                                                |

| On-Chip RAM             | 10.5MB                                                                  |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 1.00V                                                                   |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 783-BBGA, FCBGA                                                         |

| Supplier Device Package | 783-FCPBGA (29x29)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8144tvt1000b |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                |                                      | Power-               |         | -         |           |           | exing Mo   |           |               |         |                    |

|----------------|--------------------------------------|----------------------|---------|-----------|-----------|-----------|------------|-----------|---------------|---------|--------------------|

| Ball<br>Number | Signal Name                          | On<br>Reset<br>Value | 0 (000) | 1 (001)   | 2 (010)   | 3 (011)   | 4 (100)    | 5 (101)   | 6 (110)       | 7 (111) | Ref.<br>Supply     |

| C21            | V <sub>DDSXP</sub>                   |                      |         |           |           |           |            |           |               |         | V <sub>DDSXP</sub> |

| C22            | SRIO_TXD3/GE2_SGMII_T                |                      | SG      | MII suppo | rt on SER | DES is en | abled by I | Reset Cor | nfiguration V | Vord    | V <sub>DDSXP</sub> |

| C23            | V <sub>DDSXP</sub>                   |                      |         |           |           |           |            |           |               |         | V <sub>DDSXP</sub> |

| C24            | MDQ26                                |                      |         |           |           |           |            |           |               |         | V <sub>DDDDR</sub> |

| C25            | MDQ25                                |                      |         |           |           |           |            |           |               |         | V <sub>DDDDR</sub> |

| C26            | MDM3                                 |                      |         |           |           |           |            |           |               |         | V <sub>DDDDR</sub> |

| C27            | GND                                  |                      |         |           |           |           |            |           |               |         | GND                |

| C28            | MDQ24                                |                      |         |           |           |           |            |           |               |         | V <sub>DDDDR</sub> |

| D1             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |           |               |         | _                  |

| D2             | GE2_RD1/PCI_AD28                     |                      |         | Ethe      | rnet 2    |           | PCI        |           | Ethernet 2    |         | V <sub>DDGE2</sub> |

| D3             | GND                                  |                      |         |           |           |           |            |           |               |         | GND                |

| D4             | TDM7TDAT/GE2_TD3/<br>PCI_AD3/UTP_TMD |                      | TC      | рм        |           | PCI       |            | Eth       | ernet 2       | UTOPIA  | V <sub>DDGE2</sub> |

| D5             | TDM7RDAT/GE2_RD3/<br>PCI_AD1/UTP_STA |                      | TC      | рм        |           | PCI       |            | Eth       | ernet 2       | UTOPIA  | V <sub>DDGE2</sub> |

| D6             | GE1_RD0/UTP_RD2/<br>PCI_CBE2         |                      | UTOPIA  | Ethe      | rnet 1    | PCI       | UTC        | OPIA      | Ethernet 1    | UTOPIA  | V <sub>DDGE1</sub> |

| D7             | TDM7TCLK/GE2_TCK/<br>PCI_IDS/UTP_RER |                      | TC      | M         |           | PCI       | •          | Eth       | ernet 2       | UTOPIA  | V <sub>DDGE2</sub> |

| D8             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |           |               |         | _                  |

| D9             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |           |               |         | _                  |

| D10            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |           |               |         | _                  |

| D11            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |           |               |         | _                  |

| D12            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |           |               |         | GND <sub>SXP</sub> |

| D13            | SRIO_TXD0                            |                      |         |           |           |           |            |           |               |         | V <sub>DDSXP</sub> |

| D14            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |           |               |         | GND <sub>SXP</sub> |

| D15            | SRIO_TXD1                            |                      |         |           |           |           |            |           |               |         | V <sub>DDSXP</sub> |

| D16            | V <sub>DDSXC</sub>                   |                      |         |           |           |           |            |           |               |         | V <sub>DDSXC</sub> |

| D17            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |           |               |         |                    |

| D18            | Reserved <sup>1</sup>                |                      |         |           |           |           |            |           |               |         |                    |

| D19            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |           |               |         | GND <sub>SXP</sub> |

| D20            | SRIO_TXD2/GE1_SGMII_T<br>X           |                      | SG      | MII suppo | rt on SER | DES is en | abled by I | Reset Cor | nfiguration V | /ord    | V <sub>DDSXP</sub> |

| D21            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |           |               |         | GND <sub>SXP</sub> |

| D22            | SRIO_TXD3/GE2_SGMII_T<br>X           |                      | SG      | MII suppo | rt on SER | DES is en | abled by I | Reset Cor | nfiguration V | /ord    | V <sub>DDSXP</sub> |

| D23            | GND <sub>SXP</sub>                   |                      |         |           |           |           |            |           |               |         | GND <sub>SXP</sub> |

| D24            | MDQ23                                |                      |         |           |           |           |            |           |               |         | V <sub>DDDDR</sub> |

| D25            | V <sub>DDDDR</sub>                   |                      |         |           |           |           |            |           |               |         | V <sub>DDDDR</sub> |

| D26            | MDQ22                                |                      |         |           |           |           |            |           | 1             |         | V <sub>DDDDR</sub> |

| D27            | MDQ21                                |                      |         |           |           |           |            |           |               |         | V <sub>DDDDR</sub> |

| D28            | MDQS2                                |                      |         |           |           |           |            |           |               |         | V <sub>DDDDR</sub> |

| E1             | Reserved <sup>1</sup>                |                      |         |           |           |           |            |           |               |         |                    |

|                |                                 | Power-               |         |         | I/      | O Multipl | exing Mo | de <sup>2</sup> |            |         |                    |

|----------------|---------------------------------|----------------------|---------|---------|---------|-----------|----------|-----------------|------------|---------|--------------------|

| Ball<br>Number | Signal Name                     | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110)    | 7 (111) | Ref.<br>Supply     |

| E2             | GE1_RX_CLK/UTP_RD6/<br>PCI_PAR  |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E3             | GE1_RD2/UTP_RD4/<br>PCI_FRAME   |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E4             | GE1_RD1/UTP_RD3/<br>PCI_CBE3    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E5             | GE1_RD3/UTP_RD5/<br>PCI_IRDY    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E6             | V <sub>DDGE1</sub>              |                      |         |         |         |           |          |                 |            |         | V <sub>DDGE1</sub> |

| E7             | GE1_TX_EN/UTP_TD6/<br>PCI_CBE0  |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E8             | Reserved <sup>1</sup>           |                      |         |         |         |           |          |                 |            |         | —                  |

| E9             | Reserved <sup>1</sup>           |                      |         |         |         |           |          |                 |            |         | _                  |

| E10            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E11            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E12            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E13            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E14            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E15            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E16            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E17            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E18            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E19            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E20            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E21            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E22            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E23            | V <sub>DDDDR</sub>              |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| E24            | MDQ20                           |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| E25            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

|                |                                 |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| E27            | V <sub>DDDDR</sub><br>GND       |                      |         |         |         |           |          |                 |            |         | GND                |

| E28            | MDQS2                           |                      |         |         |         |           |          |                 |            |         |                    |

| F1             | Reserved <sup>1</sup>           |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| F2             | GE1_TX_CLK/UTP_RD0/<br>PCI_AD31 |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | )<br>PIA        | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| F3             | V <sub>DDGE1</sub>              |                      |         | ļ       |         |           |          |                 |            |         | V <sub>DDGE1</sub> |

| F4             | GE1_TD3/UTP_TD5/<br>PCI_AD30    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | DPIA            | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| F5             | GE1_TD1/UTP_TD3/<br>PCI_AD28    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | DPIA            | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| F6             | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| F7             | GE1_TD0/UTP_TD2/<br>PCI_AD27    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | )<br>PIA        | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| F8             | V <sub>DDGE1</sub>              |                      |         |         |         |           |          |                 |            |         | V <sub>DDGE1</sub> |

| F9             | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

|                |                                                             | Power- I/O Multiplexing Mode <sup>2</sup> |              |               |         |          |         |              |         |         |                    |

|----------------|-------------------------------------------------------------|-------------------------------------------|--------------|---------------|---------|----------|---------|--------------|---------|---------|--------------------|

| Ball<br>Number | Signal Name                                                 | On<br>Reset<br>Value                      | 0 (000)      | 1 (001)       | 2 (010) | 3 (011)  | 4 (100) | 5 (101)      | 6 (110) | 7 (111) | Ref.<br>Supply     |

| G23            | MBA1                                                        |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| G24            | MA3                                                         |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| G25            | MA8                                                         |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| G26            | V <sub>DDDDR</sub>                                          |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| G27            | GND                                                         |                                           |              |               |         |          |         |              |         |         | GND                |

| G28            | MCK0                                                        |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| H1             | Reserved <sup>1</sup>                                       |                                           |              |               |         |          |         |              |         |         | _                  |

| H2             | CLKIN                                                       |                                           |              |               |         |          |         |              |         |         | V <sub>DDIO</sub>  |

| H3             | HRESET                                                      |                                           |              |               |         |          |         |              |         |         | V <sub>DDIO</sub>  |

| H4             | PCI_CLK_IN                                                  |                                           |              |               |         |          |         |              |         |         | V <sub>DDIO</sub>  |

| H5             | NMI                                                         |                                           |              |               |         |          |         |              |         |         | V <sub>DDIO</sub>  |

| H6             | URXD/GPIO14/IRQ8/<br>RC_LDF <sup>3, 6</sup>                 | RC_LDF                                    |              |               | UA      | ART/GPIO | /IRQ    |              |         |         | V <sub>DDIO</sub>  |

| H7             | GE1_RX <u>_ER/P</u> CI_AD6/<br>GPIO25/IRQ15 <sup>3, 6</sup> |                                           | GPIO/<br>IRQ | Ethernet<br>1 |         | PCI      |         | GPIO/<br>IRQ | Ether   | net 1   | V <sub>DDIO</sub>  |

| H8             | GE1_CRS/PCI_AD5                                             |                                           | PCI          | Ethernet<br>1 |         | Р        | CI      |              | Ether   | net 1   | V <sub>DDIO</sub>  |

| H9             | GND                                                         |                                           |              |               |         |          |         |              |         |         | GND                |

| H10            | V <sub>DD</sub>                                             |                                           |              |               |         |          |         |              |         |         | V <sub>DD</sub>    |

| H11            | GND                                                         |                                           |              |               |         |          |         |              |         |         | GND                |

| H12            | V <sub>DD</sub>                                             |                                           |              |               |         |          |         |              |         |         | V <sub>DD</sub>    |

| H13            | GND                                                         |                                           |              |               |         |          |         |              |         |         | GND                |

| H14            | V <sub>DD</sub>                                             |                                           |              |               |         |          |         |              |         |         | V <sub>DD</sub>    |

| H15            | V <sub>DD</sub>                                             |                                           |              |               |         |          |         |              |         |         | V <sub>DD</sub>    |

| H16            | V <sub>DD</sub>                                             |                                           |              |               |         |          |         |              |         |         | V <sub>DD</sub>    |

| H17            | GND                                                         |                                           |              |               |         |          |         |              |         |         | GND                |

| H18            | V <sub>DD</sub>                                             |                                           |              |               |         |          |         |              |         |         | V <sub>DD</sub>    |

| H19            | GND                                                         |                                           |              |               |         |          |         |              |         |         | GND                |

| H20            | V <sub>DD</sub>                                             |                                           |              |               |         |          |         |              |         |         | V <sub>DD</sub>    |

| H21            | V <sub>DD</sub>                                             |                                           |              |               |         |          |         |              |         |         | V <sub>DD</sub>    |

| H22            | V <sub>DDDDR</sub>                                          |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| H23            | MBA0                                                        |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| H24            | MA15                                                        |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| H25            | V <sub>DDDDR</sub>                                          |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| H26            | MA9                                                         |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| H27            | MA7                                                         |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| H28            | МСК0                                                        |                                           |              |               |         |          |         |              |         |         | V <sub>DDDDR</sub> |

| J1             | Reserved <sup>1</sup>                                       |                                           |              | 1             |         |          | Ī       |              |         |         | _                  |

| J2             | GND                                                         |                                           |              |               |         |          |         |              |         |         | GND                |

| J3             | V <sub>DDIO</sub>                                           |                                           |              | 1             |         |          |         |              |         |         | V <sub>DDIO</sub>  |

| J4             | STOP_BS                                                     |                                           |              | 1             |         |          |         |              |         |         | V <sub>DDIO</sub>  |

| J5             | NMI_OUT <sup>4</sup>                                        |                                           |              | 1             |         |          |         |              |         |         | V <sub>DDIO</sub>  |

| J6             | INT_OUT <sup>4</sup>                                        |                                           |              |               |         |          |         |              |         |         | V <sub>DDIO</sub>  |

| J7             | SDA/GPIO27 <sup>3, 4, 6</sup>                               |                                           |              | •             |         | I2C/GPIC |         |              |         |         | V <sub>DDIO</sub>  |

|                |                                               | Power-               |         |          | I/      | O Multipl | exing Mo | de <sup>2</sup> |          |                   |                    |

|----------------|-----------------------------------------------|----------------------|---------|----------|---------|-----------|----------|-----------------|----------|-------------------|--------------------|

| Ball<br>Number | Signal Name                                   | On<br>Reset<br>Value | 0 (000) | 1 (001)  | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110)  | 7 (111)           | Ref.<br>Supply     |

| W23            | MDQ10                                         |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| W24            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| W25            | MDQ11                                         |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| W26            | MDM0                                          |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| W27            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| W28            | MDQS0                                         |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| Y1             | Reserved <sup>1</sup>                         |                      |         |          |         |           |          |                 |          |                   | -                  |

| Y2             | UTP_TD14/PCI_FRAME                            |                      | UTC     | PIA      | PCI     |           |          | UTOPIA          | L        |                   | V <sub>DDIO</sub>  |

| Y3             | TDM5TSYN/PCI_AD18/<br>GPIO12 <sup>3, 6</sup>  |                      | -       | TDM/GPIC | C       | P         | CI       |                 | TDM/GPIC | )                 | V <sub>DDIO</sub>  |

| Y4             | TDM5TCLK/PCI_AD16                             |                      |         | TDM      |         | Р         | CI       |                 | TDM      |                   | V <sub>DDIO</sub>  |

| Y5             | TDM4RCLK/PCI_AD7                              |                      |         | TDM      |         | Р         | CI       |                 | TDM      |                   | V <sub>DDIO</sub>  |

| Y6             | TDM4TSYN/PCI_AD12                             |                      |         | TDM      |         | Р         | CI       |                 | TDM      |                   | V <sub>DDIO</sub>  |

| Y7             | UTP_TPRTY/RC14                                | RC14                 |         |          |         | UT        | OPIA     |                 |          |                   | V <sub>DDIO</sub>  |

| Y8             | UTP_TEN/PCI_PAR                               |                      | UTC     | PIA      | PCI     |           |          | UTOPIA          |          |                   | V <sub>DDIO</sub>  |

| Y9             | Reserved <sup>1</sup>                         |                      |         |          |         |           |          |                 |          |                   | V <sub>DDIO</sub>  |

| Y10            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| Y11            | V <sub>DDM3</sub>                             |                      |         |          |         |           |          |                 |          |                   | V <sub>DDM3</sub>  |

| Y12            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| Y13            | V <sub>DDM3</sub>                             |                      |         |          |         |           |          |                 |          |                   | V <sub>DDM3</sub>  |

| Y14            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| Y15            | V <sub>DDM3</sub>                             |                      |         |          |         |           |          |                 |          |                   | V <sub>DDM3</sub>  |

| Y16            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| Y17            | V <sub>DDM3</sub>                             |                      |         |          |         |           |          |                 |          |                   | V <sub>DDM3</sub>  |

| Y18            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| Y19            | V <sub>DDM3</sub>                             |                      |         |          |         |           |          |                 |          |                   | V <sub>DDM3</sub>  |

| Y20            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| Y21            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| Y22            | V <sub>DDDDR</sub>                            |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| Y23            | MDQ13                                         |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| Y24            | V <sub>DDDDR</sub>                            |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| Y25            | GND                                           |                      |         |          |         |           |          |                 |          |                   | GND                |

| Y26            | MDQ9                                          |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| Y27            | V <sub>DDDDR</sub>                            |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| Y28            | MDQ8                                          |                      |         |          |         |           |          |                 |          |                   | V <sub>DDDDR</sub> |

| AA1            | Reserved <sup>1</sup>                         |                      |         |          |         |           |          |                 |          |                   | _                  |

| AA2            | UTP_TD13/PCI_CBE3                             |                      | UTC     | PIA      | PCI     |           |          | UTOPIA          |          | •                 | V <sub>DDIO</sub>  |

| AA3            | TDM5RSYN/PCI_AD15/<br>GPIO10 <sup>3, 6</sup>  |                      | -       | TDM/GPIC | D       | Р         | CI       |                 | TDM/GPIC | )                 | V <sub>DDIO</sub>  |

| AA4            | TDM5TDAT, AT/PCI_AD17/<br>GPIO11 <sup>6</sup> |                      | -       | TDM/GPIC | C       | Р         | CI       | TDM/GPIO        |          | V <sub>DDIO</sub> |                    |

| AA5            | TDM5RCLK/PCI_AD13/<br>GPIO28 <sup>3, 6</sup>  |                      | -       | TDM/GPIC | C       | Р         | CI       |                 | TDM/GPIC | )                 | V <sub>DDIO</sub>  |

| AA6            | GND                                           |                      |         |          |         | İ         |          | İ               |          |                   | GND                |

Table 1. Signal List by Ball Number (continued)

|                |                                                            | Power-               |         |           |         |         |         |         |             |         |                    |

|----------------|------------------------------------------------------------|----------------------|---------|-----------|---------|---------|---------|---------|-------------|---------|--------------------|

| Ball<br>Number | Signal Name                                                | On<br>Reset<br>Value | 0 (000) | 1 (001)   | 2 (010) | 3 (011) | 4 (100) | 5 (101) | 6 (110)     | 7 (111) | Ref.<br>Supply     |

| AA7            | TDM4TCLK/PCI_AD10                                          |                      |         | TDM       |         | P       | CI      |         | TDM         |         | V <sub>DDIO</sub>  |

| AA8            | TDM4TDAT/PCI_AD11                                          |                      |         | TDM       |         | P       | CI      |         | TDM         |         | V <sub>DDIO</sub>  |

| AA9            | V <sub>DDIO</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDIO</sub>  |

| AA10           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AA11           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AA12           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AA13           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AA14           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AA15           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AA16           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AA17           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AA18           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AA19           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AA20           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AA21           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AA22           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AA23           | MDQ15                                                      |                      |         |           |         |         |         |         |             |         | V <sub>DDDDR</sub> |

| AA24           | MDQ14                                                      |                      |         |           |         |         |         |         |             |         | V <sub>DDDDR</sub> |

| AA25           | MDM1                                                       |                      |         |           |         |         |         |         |             |         | V <sub>DDDDR</sub> |

| AA26           | MDQ12                                                      |                      |         |           |         |         |         |         |             |         | V <sub>DDDDR</sub> |

| AA27           | MDQS1                                                      |                      |         |           |         |         |         |         |             |         | V <sub>DDDDR</sub> |

| AA28           | MDQS1                                                      |                      |         |           |         |         |         |         |             |         | V <sub>DDDDR</sub> |

| AB1            | Reserved <sup>1</sup>                                      |                      |         |           |         |         |         |         |             |         | -                  |

| AB2            | UTP_TSOC/RC15                                              | RC15                 |         |           |         | UT      | OPIA    |         |             |         | V <sub>DDIO</sub>  |

| AB3            | V <sub>DDIO</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDIO</sub>  |

| AB4            | TDM6RDAT/PCI_AD20/<br>GPI05/IRQ11 <sup>3, 6</sup>          |                      | TD      | M/GPIO/ I | RQ      | P       | CI      | TC      | )M/GPIO/ II | RQ      | V <sub>DDIO</sub>  |

| AB5            | TDM5RDAT/PCI_AD14/<br>GPIO9 <sup>3, 6</sup>                |                      | -       | TDM/GPI0  | )       | P       | CI      |         | TDM/GPIC    | )       | V <sub>DDIO</sub>  |

| AB6            | TDM6TSYN/PCI_AD24/<br>GPIO8/ IRQ14 <sup>3, 6</sup>         |                      | TD      | M/GPIO/I  | RQ      | P       | CI      | Т       | DM/GPIO/IF  | RQ      | V <sub>DDIO</sub>  |

| AB7            | TDM6R <u>CLK/PCI_</u> AD19/<br>GPIO4/IRQ10 <sup>3, 6</sup> |                      | TD      | M/GPIO/I  | RQ      | P       | CI      | Т       | DM/GPIO/IF  | RQ      | V <sub>DDIO</sub>  |

| AB8            | TDM4RSYN/PCI_AD9                                           |                      |         | TDM       |         | P       | CI      |         | TDM         |         | V <sub>DDIO</sub>  |

| AB9            | TDM4RDAT/PCI_AD8                                           |                      |         | TDM       |         | P       | CI      |         | TDM         |         | V <sub>DDIO</sub>  |

| AB10           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AB11           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AB12           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AB13           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AB14           | GND                                                        |                      |         |           |         |         |         |         |             |         | GND                |

| AB15           | V <sub>DDM3</sub>                                          |                      |         |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AB16           | GND                                                        |                      | 1       |           |         |         |         |         |             |         | GND                |

| AB17           | V <sub>DDM3</sub>                                          |                      | 1       |           |         |         |         |         |             |         | V <sub>DDM3</sub>  |

| AB18           | GND                                                        |                      |         |           |         |         |         |         |             | 1       | GND                |

|                |                       | Power-               |         |         | I/      | O Multipl | exing Mo | de <sup>2</sup> |         |           |                |

|----------------|-----------------------|----------------------|---------|---------|---------|-----------|----------|-----------------|---------|-----------|----------------|

| Ball<br>Number | Signal Name           | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110) | 7 (111)   | Ref.<br>Supply |

| AH17           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH18           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH19           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | —              |

| AH20           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH21           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH22           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | —              |

| AH23           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH24           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH25           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH26           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH27           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| AH28           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |           | _              |

| Notes:         |                       |                      |         |         |         |           |          |                 |         | apter 23, |                |

*GPIO* in the *MSC8144 Reference Manual*.**4.** Open-drain signal.

**5.** Internal 20 K $\Omega$  pull-up resistor.

6. For signals with GPIO functionality, the open-drain and internal 20 KΩ pull-up resistor can be configured by GPIO register programming. See Chapter 23, GPIO of the MSC8144 Reference Manual for configuration details.

# 2.5.2 Serial RapidIO DC Electrical Characteristics

DC receiver logic levels are not defined since the receiver is AC-coupled.

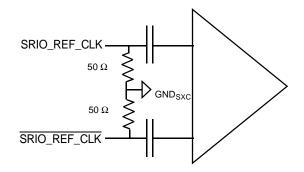

### 2.5.2.1 DC Requirements for SerDes Reference Clocks

The SerDes reference clocks SRIO\_REF\_CLK and  $\overline{\text{SRIO}_{\text{REF}}\text{CLK}}$  are AC-coupled differential inputs. Each differential clock input has an internal 50  $\Omega$  termination to  $\text{GND}_{\text{SXC}}$ . The reference clock must be able to drive this termination. The recommended minimum operating voltage is -0.4 V; the recommended maximum operating voltage is 1.32 V; and the maximum absolute voltage is 1.72 V.

The maximum average current allowed in each input is 8 mA. This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50  $\Omega$  = 8 mA) while the minimum common mode input level is GND<sub>SXC</sub>. For example, a clock with a 50/50 duty cycle can be driven by a current source output that ranges from 0 mA to 16 mA (0–0.8 V). The input is AC-coupled internally, so, therefore, the exact common mode input voltage is not critical.

Note: This internal AC-couple network does not function correctly with reference clock frequencies below 90 MHz.

If the device driving the  $\overline{\text{SRIO}\_\text{REF}\_\text{CLK}}$  inputs cannot drive 50  $\Omega$  to  $\text{GND}_{\text{SXC}}$ , or if it exceeds the maximum input current limitations, then it must use external AC-coupling. The minimum differential peak-to-peak amplitude of the input clock is 0.4 V (0.2 V peak-to-peak per phase). The maximum differential peak-to-peak amplitude of the input clock is 1.6 V peak-to-peak (see Figure 5. The termination to  $\text{GND}_{\text{SXC}}$  allows compatibility with HCSL type reference clocks specified for PCI-Express applications. Many other low voltage differential type outputs can be used but will probably need to be AC-coupled due to the limited common mode input range. LVPECL outputs can produce too large an amplitude and may need to be source terminated with a divider network to reduce the amplitude. The amplitude of the clock must be at least a 400 mV differential peak-peak for single-ended clock. If driven differentially, each signal wire needs to drive 100 mV around common mode voltage. The differential reference clock (SRIO\\_REF\\_CLK/SRIO\\_REF\\_CLK) input is HCSL-compatible DC coupled or LVDS-compatible with AC-coupling.

Figure 5. SerDes Reference Clocks Input Stage

rical Characteristics

# 2.5.2.2 Spread Spectrum Clock

SRIO\_REF\_CLK/ SRIO\_REF\_CLK is designed to work with a spread spectrum clock (0 to 0.5% spreading at 3033 kHz rate is allowed), assuming both ends have same reference clock. For better results use a source without significant unintended modulation.

# 2.5.3 PCI DC Electrical Characteristics

### **Table 9. PCI DC Electrical Characteristics**

| Characteristic                                                                                 | Symbol             | Min                    | Max                    | Unit |

|------------------------------------------------------------------------------------------------|--------------------|------------------------|------------------------|------|

| Supply voltage 3.3 V                                                                           | V <sub>DDPCI</sub> | 3.135                  | 3.465                  | V    |

| Input high voltage                                                                             | V <sub>IH</sub>    | $0.5 	imes V_{DDPCI}$  | 3.465                  | V    |

| Input low voltage                                                                              | V <sub>IL</sub>    | -0.5                   | $0.3 	imes V_{DDPCI}$  | V    |

| Input Pull-up voltage <sup>1</sup>                                                             | V <sub>IPU</sub>   | $0.7 \times V_{DDPCI}$ |                        |      |

| Input leakage current, 0 <v<sub>IN <v<sub>DDPCI</v<sub></v<sub>                                | I <sub>IN</sub>    | -30                    | 30                     | μA   |

| Tri-state (high impedance off state) leakage current, 0 <v<sub>IN <v<sub>DDPCI</v<sub></v<sub> | I <sub>OZ</sub>    | -30                    | 30                     | μA   |

| Signal low input current, V <sub>IL</sub> = 0.4 V <sup>1</sup>                                 | ΙL                 | -30                    | 30                     | μA   |

| Signal high input current, V <sub>IH</sub> = 2.0 V <sup>1</sup>                                | Ι <sub>Η</sub>     | -30                    | 30                     | μA   |

| Output high voltage, I <sub>OH</sub> = -0.5 mA, except open drain pins                         | V <sub>OH</sub>    | $0.9 \times V_{DDPCI}$ | —                      | V    |

| Output low voltage, I <sub>OL</sub> = 1.5 mA                                                   | V <sub>OL</sub>    | —                      | $0.1 \times V_{DDPCI}$ | V    |

| Input Pin Capacitance <sup>1</sup>                                                             | C <sub>IN</sub>    |                        | 10                     | pF   |

| Notes: 1. Not tested. Guaranteed by design.                                                    |                    |                        | •                      | •    |

# 2.5.4 TDM DC Electrical Characteristics

### Table 10. TDM DC Electrical Characteristics

| Characteristic                                                 | Symbol             | Min   | Max   | Unit |

|----------------------------------------------------------------|--------------------|-------|-------|------|

| Supply voltage 3.3 V                                           | V <sub>DDTDM</sub> | 3.135 | 3.465 | V    |

| Input high voltage                                             | V <sub>IH</sub>    | 2.0   | 3.465 | V    |

| Input low voltage                                              | V <sub>IL</sub>    | -0.3  | 0.8   | V    |

| Input leakage current 0 <v<sub>IN <v<sub>DDTDM</v<sub></v<sub> | I <sub>IN</sub>    | -30   | 30    | μΑ   |

| Tri-state (high impedance off state) leakage current           | I <sub>OZ</sub>    | -30   | 30    | μΑ   |

| Output high voltage, I <sub>OH</sub> = -1.6 mA                 | V <sub>OH</sub>    | 2.4   | —     | V    |

| Output low voltage, I <sub>OL</sub> = 0.4mA                    | V <sub>OL</sub>    | —     | 0.4   | V    |

rical Characteristics

# 2.5.6 ATM/UTOPIA/POS DC Electrical Characteristics

| Characteristic                                                 | Symbol            | Min   | Max   | Unit |

|----------------------------------------------------------------|-------------------|-------|-------|------|

| Supply voltage 3.3 V                                           | V <sub>DDIO</sub> | 3.135 | 3.465 | V    |

| Input high voltage                                             | V <sub>IH</sub>   | 2.0   | 3.465 | V    |

| Input low voltage                                              | V <sub>IL</sub>   | -0.3  | 0.8   | V    |

| Input leakage current, V <sub>IN</sub> = supply voltage        | I <sub>IN</sub>   | -30   | 30    | μΑ   |

| Signal low input current, V <sub>IL</sub> = 0.4 V <sup>1</sup> | ΙL                | -30   | 30    | μA   |

| Signal high input current, $V_{IH} = 2.4 V^1$                  | Ι <sub>Η</sub>    | -30   | 30    | μΑ   |

| Output high voltage, I <sub>OH</sub> = -4 mA                   | V <sub>OH</sub>   | 2.4   | 3.465 | V    |

| Output low voltage, I <sub>OL</sub> = 4 mA                     | V <sub>OL</sub>   | _     | 0.5   | V    |

| Notes: 1. Not tested. Guaranteed by design.                    | ÷                 | •     | *     |      |

# 2.5.7 SPI DC Electrical Characteristics

Table 14 provides the SPI DC electrical characteristics.

**Table 14. SPI DC Electrical Characteristics**

| Characteristic                                 | Symbol          | Min  | Мах   | Unit |

|------------------------------------------------|-----------------|------|-------|------|

| Input high voltage                             | V <sub>IH</sub> | 2.0  | 3.465 | V    |

| Input low voltage                              | V <sub>IL</sub> | -0.3 | 0.8   | V    |

| Input current                                  | I <sub>IN</sub> |      | 30    | μΑ   |

| Output high voltage, I <sub>OH</sub> = -4.0 mA | V <sub>OH</sub> | 2.4  | _     | V    |

| Output low voltage, I <sub>OL</sub> = 4.0 mA   | V <sub>OL</sub> | _    | 0.5   | V    |

# 2.5.8 GPIO, UART, TIMER, EE, STOP\_BS, I<sup>2</sup>C, IRQn, NMI\_OUT, INT\_OUT, CLKIN, JTAG Ports DC Electrical Characteristics

Table 15. GPIO, UART, Timer, EE, STOP\_BS, I<sup>2</sup>C, IRQn, NMI\_OUT, INT\_OUT, CLKIN, and JTAG Port<sup>1</sup> DC Electrical Characteristics

| Characteristic                                                                                                                                       | Symbol            | Min   | Max   | Unit |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------|------|--|--|

| Supply voltage 3.3 V                                                                                                                                 | V <sub>DDIO</sub> | 3.135 | 3.465 | V    |  |  |

| Input high voltage                                                                                                                                   | V <sub>IH</sub>   | 2.0   | 3.465 | V    |  |  |

| Input low voltage                                                                                                                                    | V <sub>IL</sub>   | -0.3  | 0.8   | V    |  |  |

| Input leakage current, V <sub>IN</sub> = supply voltage                                                                                              | I <sub>IN</sub>   | -30   | 30    | μΑ   |  |  |

| Tri-state (high impedance off state) leakage current, $V_{IN}$ = supply voltage                                                                      | I <sub>OZ</sub>   | -30   | 30    | μΑ   |  |  |

| Signal low input current, $V_{IL} = 0.4 V^2$                                                                                                         | ١                 | -30   | 30    | μΑ   |  |  |

| Signal high input current, V <sub>IH</sub> = 2.0 V <sup>2</sup>                                                                                      | Ι <sub>Η</sub>    | -30   | 30    | μΑ   |  |  |

| Output high voltage, I <sub>OH</sub> = -2 mA,<br>except open drain pins                                                                              | V <sub>OH</sub>   | 2.4   | 3.465 | V    |  |  |

| Output low voltage, I <sub>OL</sub> = 3.2 mA                                                                                                         | V <sub>OL</sub>   | _     | 0.4   | V    |  |  |

| <ol> <li>Notes: 1. This does not include TDI and TMS, which have internal pullup resistors.</li> <li>2. Not tested. Guaranteed by design.</li> </ol> |                   |       |       |      |  |  |

# 2.6.4 DDR SDRAM AC Timing Specifications

This section describes the AC electrical characteristics for the DDR SDRAM interface.

### 2.6.4.1 DDR SDRAM Input Timings

Table 20 provides the input AC timing specifications for the DDR SDRAM when  $V_{DDDDR}$  (typ) = 2.5 V.

### Table 20. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

| Parameter                                                                      | Symbol          | Min                      | Мах                      | Unit |  |  |

|--------------------------------------------------------------------------------|-----------------|--------------------------|--------------------------|------|--|--|

| AC input low voltage                                                           | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.31 | V    |  |  |

| AC input high voltage                                                          | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | —                        | V    |  |  |

| <b>Note:</b> At recommended operating conditions with $V_{DDDDR}$ of 2.5 ± 5%. |                 |                          |                          |      |  |  |

Table 21 provides the input AC timing specifications for the DDR SDRAM when  $V_{DDDDR}$  (typ) = 1.8 V.

### Table 21. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

| Parameter                                                               |                 | Min                      | Мах                      | Unit |  |

|-------------------------------------------------------------------------|-----------------|--------------------------|--------------------------|------|--|

| AC input low voltage                                                    | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    |  |

| AC input high voltage                                                   | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | —                        | V    |  |

| Note: At recommended operating conditions with $V_{DDDDR}$ of 1.8 ± 5%. |                 |                          |                          |      |  |

Table 22 provides the input AC timing specifications for the DDR SDRAM interface.

### Table 22. DDR SDRAM Input AC Timing Specifications

|                                                                                                                                                                                                                         | Parameter                             | Symbol              | Min  | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------|------|-----|------|

| Controller Sk                                                                                                                                                                                                           | ew for MDQS—MDQ/MECC/MDM <sup>1</sup> | t <sub>CISKEW</sub> |      |     |      |

| • 400 MHz                                                                                                                                                                                                               |                                       |                     | -365 | 365 | ps   |

| • 333 MHz                                                                                                                                                                                                               |                                       |                     | -390 | 390 | ps   |

| • 266 MHz                                                                                                                                                                                                               |                                       |                     | -428 | 428 | ps   |

| • 200 MHz                                                                                                                                                                                                               |                                       |                     | -490 | 490 | ps   |

| Notes: 1. t <sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. Subtract this value from the total timing budget. |                                       |                     |      |     |      |

| <b>2.</b> At recommended operating conditions with $V_{\text{OPD},\text{OPD}}$ (1.8 V or 2.5 V) ± 5%                                                                                                                    |                                       |                     |      |     |      |

2. At recommended operating conditions with  $V_{DDDDR}$  (1.8 V or 2.5 V)  $\pm$  5%

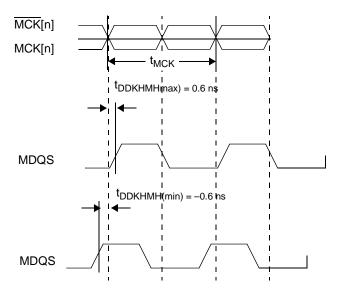

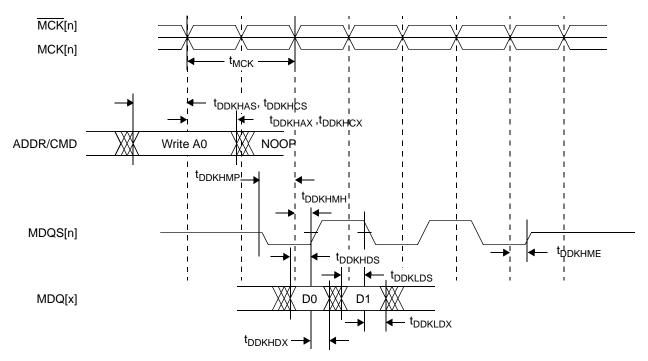

Figure 8 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 8. Timing for t<sub>DDKHMH</sub>

Figure 9. DDR SDRAM Output Timing

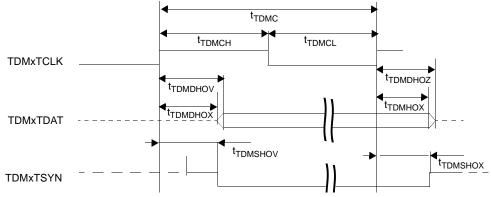

Figure 20. TDM Output Signals

**Note:** For some TDM modes, transmit data is output on other pins. This timing is also valid for those pins. See the *MSC8144 Reference Manual*

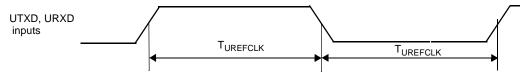

# 2.6.8 UART Timing

Table 38. UART Timing

| Characteristics                                                  | Symbol               | Expression             | Min | Max | Unit |

|------------------------------------------------------------------|----------------------|------------------------|-----|-----|------|

| URXD and UTXD inputs high/low duration                           | T <sub>UREFCLK</sub> | $16 \times T_{REFCLK}$ | 160 | —   | ns   |

| <b>Note:</b> $T_{UREFCLK} = T_{REFCLK}$ is guaranteed by design. |                      |                        |     |     |      |

Figure 21 shows the UART input AC timing

Figure 21. UART Input Timing

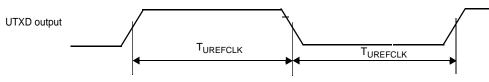

Figure 22 shows the UART output AC timing

Figure 22. UART Output Timing

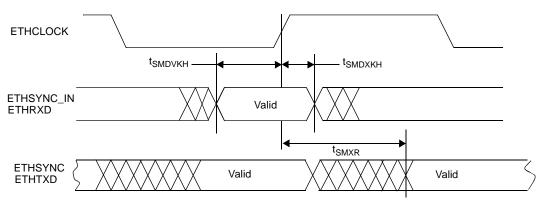

Figure 30. SMII Mode Signal Timing

# 2.6.10.6 RGMII AC Timing Specifications

Table 45 presents the RGMII AC timing specifications for applications requiring an on-board delayed clock.

| Table 45. RGMII with On-Board Delay AC Timing S | Specifications |

|-------------------------------------------------|----------------|

|-------------------------------------------------|----------------|

|                                                                                                                                                                                                                                                                                                                                             | Parameter/Condition |                    |                    | Min     | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|--------------------|---------|-----|-----|------|

| Data to clock output skew (at transmitter)                                                                                                                                                                                                                                                                                                  |                     | t <sub>SKEWT</sub> | -0.5               | _       | 0.5 | ns  |      |

| Data to clock input skew (at receiver) <sup>2</sup>                                                                                                                                                                                                                                                                                         |                     |                    | t <sub>SKEWR</sub> | 0.9     | _   | 2.6 | ns   |

| <ul> <li>Notes: 1. At recommended operating conditions with LV<sub>DD</sub> of 2.5 V +/- 5%.</li> <li>2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.</li> <li>3. GCR4 should be programmed as 0x00001004.</li> </ul> |                     |                    |                    | 5 ns is |     |     |      |

Table 46 presents the RGMII AC timing specification for applications required non-delayed clock on board.

### Table 46. RGMII with No On-Board Delay AC Timing Specifications

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Parameter/Condition                                 |  |  | Min  | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|------|-----|------|------|

| Data to o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Data to clock output skew (at transmitter)          |  |  | -2.6 | _   | -0.9 | ns   |

| Data to o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Data to clock input skew (at receiver) <sup>2</sup> |  |  | -0.5 | _   | 0.5  | ns   |

| Data to clock input skew (at receiver) -       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t <tht< th="">       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       t       <tht< th="">       t       <tht>t       t</tht></tht<></tht<> |                                                     |  |  |      |     |      |      |

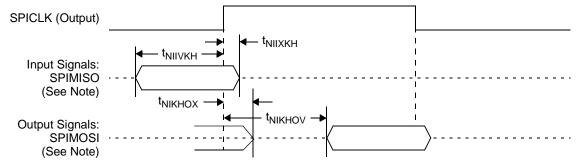

Note: The clock edge is selectable on SPI.

Figure 36. SPI AC Timing in Master Mode (Internal Clock)

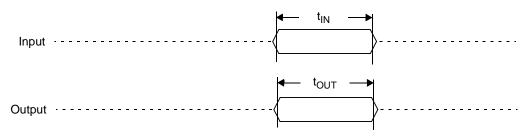

# 2.6.13 Asynchronous Signal Timing

### Table 49. Signal Timing

| Characteristics                                     | Symbol           | /mbol Type   |                              |  |  |

|-----------------------------------------------------|------------------|--------------|------------------------------|--|--|

| Input                                               | t <sub>IN</sub>  | Asynchronous | One CLKIN cycle <sup>1</sup> |  |  |

| Output                                              | t <sub>OUT</sub> | Asynchronous | Application dependent        |  |  |

| Note: 1. Relevant for EE0, IRQ[15–0], and NMI only. |                  |              |                              |  |  |

The following interfaces use the specified asynchronous signals:

- *GPIO*. Signals GPIO[31–0], when used as GPIO signals, that is, when the alternate multiplexed special functions are not selected.

- **Note:** When used as a GPI, the input should be driven until it is acknowledged by the device; the GPIO input status is read from a register.

- *EE port.* Signals EE0, EE1, EE2\_0, EE2\_1, EE2\_2, and EE2\_3.

- Boot function. Signal STOP\_BS.

- $I^2C$  interface. Signals I2C\_SCL and I2C\_SDA.

- Interrupt inputs. Signals IRQ[15–0] and NMI.

- Interrupt outputs. Signals INT\_OUT and NMI\_OUT (pulse width is 10 ns).

Figure 37 shows the behavior of the asynchronous signals.

Figure 37. Asynchronous Signal Timing

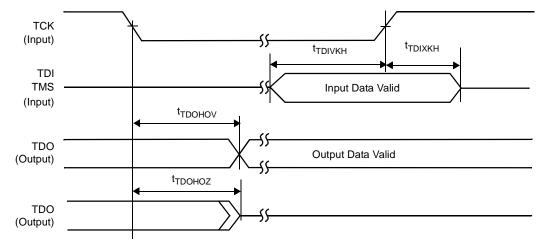

Figure 40 shows the test access port timing diagram

Figure 40. Test Access Port Timing

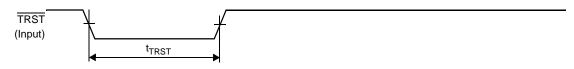

Figure 41 shows the  $\overline{\text{TRST}}$  timing diagram.

# 3 Hardware Design Considerations

The following sections discuss areas to consider when the MSC8144 device is designed into a system.

# 3.1 Start-up Sequencing Recommendations

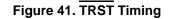

# 3.1.1 Power-on Sequence

Use the following guidelines for power-on sequencing: