## NXP USA Inc. - <u>MSC8144VT1000B Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Detuns                  |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Obsolete                                                               |

| Туре                    | SC3400 Core                                                            |

| Interface               | Ethernet, I <sup>2</sup> C, SPI, TDM, UART, UTOPIA                     |

| Clock Rate              | 1GHz                                                                   |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 10.5MB                                                                 |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.00V                                                                  |

| Operating Temperature   | 0°C ~ 90°C (TJ)                                                        |

| Mounting Type           | Surface Mount                                                          |

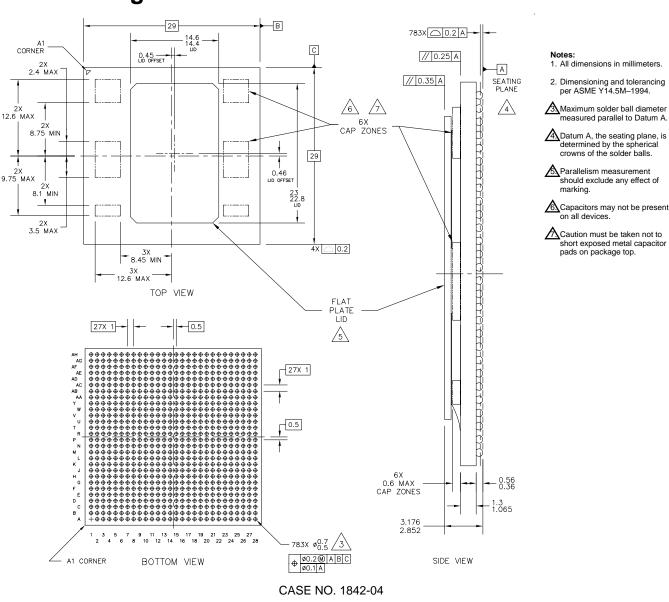

| Package / Case          | 783-BBGA, FCBGA                                                        |

| Supplier Device Package | 783-FCPBGA (29x29)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8144vt1000b |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ball   |                       | Power-<br>On   |         |         |         |         |         |         |         |          | Def                 |

|--------|-----------------------|----------------|---------|---------|---------|---------|---------|---------|---------|----------|---------------------|

| Number | Signal Name           | Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011) | 4 (100) | 5 (101) | 6 (110) | 7 (111)  | Ref.<br>Supply      |

| J8     | V <sub>DDIO</sub>     |                |         |         |         |         |         |         |         |          | V <sub>DDIO</sub>   |

| J9     | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J10    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J11    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J12    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J13    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J14    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J15    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J16    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J17    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J18    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J19    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| J20    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J21    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J22    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J23    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J24    | V <sub>DDDDR</sub>    |                |         |         |         |         |         |         |         |          | V <sub>DDDDR</sub>  |

| J25    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J26    | V <sub>DDDDR</sub>    |                |         |         |         |         |         |         |         |          | V <sub>DDDDR</sub>  |

| J27    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| J28    | V <sub>DDDDR</sub>    |                |         |         |         |         |         |         |         |          | V <sub>DDDDR</sub>  |

| K1     | Reserved <sup>1</sup> |                |         |         |         |         |         |         |         |          |                     |

| K2     | Reserved <sup>1</sup> |                |         |         |         |         |         |         |         |          | _                   |

| K3     | Reserved <sup>1</sup> |                |         |         |         |         |         |         |         |          | _                   |

| K4     | Reserved <sup>1</sup> |                |         |         |         |         |         |         |         |          |                     |

| K5     | V <sub>DDPLL2A</sub>  |                |         |         |         |         |         |         |         |          | V <sub>DDPLL2</sub> |

| K6     | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K7     | V <sub>DDPLL0A</sub>  |                |         |         |         |         |         |         |         |          | V <sub>DDPLL0</sub> |

| K8     | V <sub>DDPLL1A</sub>  |                |         |         |         |         |         |         |         |          | V <sub>DDPLL1</sub> |

| K9     | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K10    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K11    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K12    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K13    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K14    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K15    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K16    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K17    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K18    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K19    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K20    | GND                   |                |         |         |         |         |         |         |         |          | GND                 |

| K21    | V <sub>DD</sub>       |                |         |         |         |         |         |         |         |          | V <sub>DD</sub>     |

| K22    | V <sub>DDDDR</sub>    | _              |         |         |         |         |         |         |         | <u> </u> | V <sub>DDDDR</sub>  |

|                |                       | Power-               |         |           | I/      | O Multipl                                  | exing Mo | de <sup>2</sup> |          |                   |                                        |

|----------------|-----------------------|----------------------|---------|-----------|---------|--------------------------------------------|----------|-----------------|----------|-------------------|----------------------------------------|

| Ball<br>Number | Signal Name           | On<br>Reset<br>Value | 0 (000) | 1 (001)   | 2 (010) | 3 (011)                                    | 4 (100)  | 5 (101)         | 6 (110)  | 7 (111)           | Ref.<br>Supply                         |

| T21            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| T22            | V <sub>DDDDR</sub>    |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| T23            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| T24            | V <sub>DDDDR</sub>    |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| T25            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| T26            | V <sub>DDDDR</sub>    |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| T27            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| T28            | V <sub>DDDDR</sub>    |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| U1             | Reserved <sup>1</sup> |                      |         |           |         |                                            |          |                 |          |                   | _                                      |

| U2             | UTP_TCLK/PCI_AD29     |                      | UTC     | OPIA      | PCI     |                                            | •        | UTOPIA          |          | •                 | V <sub>DDIO</sub>                      |

| U3             | UTP_TADDR4/PCI_AD27   |                      | UTC     | OPIA      | PCI     |                                            |          | UTOPIA          |          |                   | V <sub>DDIO</sub>                      |

| U4             | UTP_TADDR2            |                      |         |           |         | UT                                         | OPIA     |                 |          |                   | V <sub>DDIO</sub>                      |

| U5             | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| U6             | UTP_REN/PCI_AD20      |                      | UTC     | OPIA      | PCI     |                                            |          | UTOPIA          |          | 1                 | V <sub>DDIO</sub>                      |

| U7             | PCI_AD26              |                      |         |           |         | F                                          | PCI      |                 |          |                   | V <sub>DDIO</sub>                      |

| U8             | PCI_AD25              |                      |         | PCI       |         |                                            |          |                 |          | V <sub>DDIO</sub> |                                        |

| U9             | Reserved <sup>1</sup> |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDIO</sub>                      |

| U10            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDM3</sub>                      |

| U11            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| U12            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDM3</sub>                      |

| U13            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| U14            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDM3</sub>                      |

| U15            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| U16            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDM3</sub>                      |

| U17            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| U18            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDM3</sub>                      |

| U19            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| U20            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDM3</sub>                      |

| U21            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| U22            | GND                   |                      |         |           |         |                                            |          |                 |          |                   | GND                                    |

| U23            | MDQ7                  |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| U24            | MDQ3                  |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| U25            | MDQ4                  |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| U26            | MDQ5                  |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| U27            | MDQ1                  |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| U28            | MDQ0                  |                      |         |           |         |                                            |          |                 |          |                   | V <sub>DDDDR</sub>                     |

| V1             | Reserved <sup>1</sup> |                      |         |           |         |                                            |          |                 |          |                   | אטעטט •                                |

| V2             | UTP_TD10/PCI_CBE0     |                      | UTC     | )<br>DPIA | PCI     |                                            | 1        | UTOPIA          | <u> </u> | 1                 | V <sub>DDIO</sub>                      |

| V2<br>V3       | UTP_TADDR3            |                      |         |           | 1 1 0   | і<br>— — — — — — — — — — — — — — — — — — — | OPIA     |                 |          |                   | V <sub>DDIO</sub>                      |

| V3<br>V4       | UTP_TD1/PCI_PERR      |                      |         | OPIA      | P       | CI                                         |          |                 | OPIA     |                   | V <sub>DDIO</sub>                      |

| V4<br>V5       | UTP_TADDR0/PCI_AD23   |                      |         |           | PCI     |                                            | 1        | UTOPIA          |          |                   | V <sub>DDIO</sub>                      |

| V5<br>V6       | UTP_TADDR0/PCI_AD23   |                      |         |           | PCI     |                                            |          | UTOPIA          |          |                   |                                        |

| V0<br>V7       | UTP_TCLAV/PCI_AD28    |                      |         |           | PCI     |                                            |          | UTOPIA          |          |                   | V <sub>DDIO</sub><br>V <sub>DDIO</sub> |

Table 1. Signal List by Ball Number (continued)

|                |                       | Power- I/O Multiplexing Mode <sup>2</sup> |         |         |         |            |         |         |         |         |                    |

|----------------|-----------------------|-------------------------------------------|---------|---------|---------|------------|---------|---------|---------|---------|--------------------|

| Ball<br>Number | Signal Name           | On<br>Reset<br>Value                      | 0 (000) | 1 (001) | 2 (010) | 3 (011)    | 4 (100) | 5 (101) | 6 (110) | 7 (111) | Ref.<br>Supply     |

| V8             | V <sub>DDIO</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDIO</sub>  |

| V9             | Reserved <sup>1</sup> |                                           |         |         |         |            |         |         |         |         | V <sub>DDIO</sub>  |

| V10            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| V11            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| V12            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| V13            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| V14            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| V15            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| V16            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| V17            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| V18            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| V19            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| V20            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| V21            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| V22            | V <sub>DDDDR</sub>    |                                           |         |         |         |            |         |         |         |         | V <sub>DDDDR</sub> |

| V23            | MDQ2                  |                                           |         |         |         |            |         |         |         |         | V <sub>DDDDR</sub> |

| V24            | V <sub>DDDDR</sub>    |                                           |         |         |         |            |         |         |         |         | V <sub>DDDDR</sub> |

| V25            | MDQ6                  |                                           |         |         |         |            |         |         |         |         | V <sub>DDDDR</sub> |

| V26            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| V27            | V <sub>DDDDR</sub>    |                                           |         |         |         |            |         |         |         |         | V <sub>DDDDR</sub> |

| V28            | MDQS0                 |                                           |         |         |         |            |         |         |         |         | V <sub>DDDDR</sub> |

| W1             | Reserved <sup>1</sup> |                                           |         |         |         |            |         |         |         |         | _                  |

| W2             | UTP_TD12/PCI_CBE2     |                                           | UTC     | OPIA    | PCI     |            |         | UTOPIA  |         |         | V <sub>DDIO</sub>  |

| W3             | UTP_TD11/PCI_CBE1     |                                           | UTC     | OPIA    | PCI     |            |         | UTOPIA  |         |         | V <sub>DDIO</sub>  |

| W4             | V <sub>DDIO</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDIO</sub>  |

| W5             | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| W6             | UTP_TD15/PCI_IRDY     |                                           | UTC     | OPIA    | PCI     |            |         | UTOPIA  |         |         | V <sub>DDIO</sub>  |

| W7             | UTP_TD0/PCI_SERR      |                                           | UTC     | OPIA    | Р       | PCI UTOPIA |         |         |         |         | V <sub>DDIO</sub>  |

| W8             | UTP_RSOC/PCI_AD22     |                                           | UTC     | OPIA    | PCI     |            |         | UTOPIA  |         |         | V <sub>DDIO</sub>  |

| W9             | Reserved <sup>1</sup> |                                           |         |         |         |            |         |         |         |         | V <sub>DDIO</sub>  |

| W10            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| W11            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| W12            | V <sub>25M3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>25M3</sub>  |

| W13            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| W14            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| W15            | V <sub>25M3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>25M3</sub>  |

| W16            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| W17            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| W18            | V <sub>25M3</sub>     |                                           |         |         |         |            |         |         |         | 1       | V <sub>25M3</sub>  |

| W19            | GND                   |                                           |         |         |         |            |         |         |         | 1       | GND                |

| W20            | V <sub>DDM3</sub>     |                                           |         |         |         |            |         |         |         |         | V <sub>DDM3</sub>  |

| W21            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

| W22            | GND                   |                                           |         |         |         |            |         |         |         |         | GND                |

|                |                                                                          | Power-               |                               |                  | I/      | O Multipl         | exing Mo | de <sup>2</sup>   |                   |         |                     |

|----------------|--------------------------------------------------------------------------|----------------------|-------------------------------|------------------|---------|-------------------|----------|-------------------|-------------------|---------|---------------------|

| Ball<br>Number | Signal Name                                                              | On<br>Reset<br>Value | 0 (000)                       | 1 (001)          | 2 (010) | 3 (011)           | 4 (100)  | 5 (101)           | 6 (110)           | 7 (111) | Ref.<br>Supply      |

| AB19           | V <sub>DDM3</sub>                                                        |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDM3</sub>   |

| AB20           | GND                                                                      |                      |                               |                  |         |                   |          |                   |                   |         | GND                 |

| AB21           | GND                                                                      |                      |                               |                  |         |                   |          |                   |                   |         | GND                 |

| AB22           | V <sub>DDDDR</sub>                                                       |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AB23           | MECC7                                                                    |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AB24           | MECC1                                                                    |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AB25           | MECC4                                                                    |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AB26           | MECC5                                                                    |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AB27           | MECC2                                                                    |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AB28           | ECC_MDQS                                                                 |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AC1            | Reserved <sup>1</sup>                                                    |                      |                               |                  |         |                   |          |                   |                   |         | _                   |

| AC2            | UTP_RD9/RC13                                                             | RC13                 |                               | UTOPIA           |         |                   |          |                   |                   |         | V <sub>DDIO</sub>   |

| AC3            | UTP_RD8/RC12                                                             | RC12                 |                               | UTOPIA           |         |                   |          |                   | V <sub>DDIO</sub> |         |                     |

| AC4            | TDM6TCLK/PCI_AD22                                                        |                      |                               | TDM PCI TDM      |         | V <sub>DDIO</sub> |          |                   |                   |         |                     |

| AC5            | TDM6RSYN/PCI_AD21/<br>GPIO6/ IRQ12 <sup>3, 6</sup>                       |                      | TDM/GPIO/IRQ PCI TDM/GPIO/IRQ |                  | RQ      | V <sub>DDIO</sub> |          |                   |                   |         |                     |

| AC6            | V <sub>DDIO</sub>                                                        |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDIO</sub>   |

| AC7            | TDM3TSYN/RC11                                                            | RC11                 | TDM                           |                  |         |                   |          | V <sub>DDIO</sub> |                   |         |                     |

| AC8            | PCI_AD23/GPIO7/ <del>IRQ13</del> /<br>TDM6TDAT <sup>3, 6</sup> /UTP_RMOD |                      | TD                            | TDM/GPIO/IRQ PCI |         | TDM/G             | PIO/IRQ  | UTOPIA            | V <sub>DDIO</sub> |         |                     |

| AC9            | TDM7TSYN/ PCI_AD4                                                        |                      | TC                            | DM               |         | PCI               |          |                   | reserved          | eserved |                     |

| AC10           | V <sub>DDM3IO</sub>                                                      |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDM3IO</sub> |

| AC11           | GND                                                                      |                      |                               |                  |         |                   |          |                   |                   |         | GND                 |

| AC12           | V <sub>DDM3</sub>                                                        |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDM3</sub>   |

| AC13           | GND                                                                      |                      |                               |                  |         |                   |          |                   |                   |         | GND                 |

| AC14           | V <sub>DDM3</sub>                                                        |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDM3</sub>   |

| AC15           | GND                                                                      |                      |                               |                  |         |                   |          |                   |                   |         | GND                 |

| AC16           | V <sub>DDM3</sub>                                                        |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDM3</sub>   |

| AC17           | GND                                                                      |                      |                               |                  |         |                   |          |                   |                   |         | GND                 |

| AC18           | V <sub>DDM3</sub>                                                        |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDM3</sub>   |

| AC19           | GND                                                                      |                      |                               |                  |         |                   |          |                   |                   |         | GND                 |

| AC20           | V <sub>DDM3IO</sub>                                                      |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDM3IO</sub> |

| AC21           | Reserved <sup>1</sup>                                                    |                      |                               |                  |         |                   |          |                   |                   |         |                     |

| AC22           | MECC6                                                                    |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AC23           | MECC3                                                                    |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AC24           | ECC_MDM                                                                  | -                    |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AC25           | V <sub>DDDDR</sub>                                                       | -                    |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AC26           | MECC0                                                                    |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AC27           | V <sub>DDDDR</sub>                                                       |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AC28           | ECC_MDQS                                                                 |                      |                               |                  |         |                   |          |                   |                   |         | V <sub>DDDDR</sub>  |

| AD1            | Reserved <sup>1</sup>                                                    |                      |                               |                  |         |                   |          |                   |                   |         | - אטעעע             |

| AD2            | GPIO1 <sup>3, 6</sup>                                                    |                      |                               | 1                | 1       | <u>ر</u>          | PIO      | 1                 | <u> </u>          | 1       | V <sub>DDIO</sub>   |

| AD2            | TMR0/GPIO13                                                              |                      |                               |                  |         |                   | R/GPIO   |                   |                   |         | V <sub>DDIO</sub>   |

|                |                       | Power-               |         |         | I/      | O Multipl | exing Mo | de <sup>2</sup> |         |         |                |

|----------------|-----------------------|----------------------|---------|---------|---------|-----------|----------|-----------------|---------|---------|----------------|

| Ball<br>Number | Signal Name           | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110) | 7 (111) | Ref.<br>Supply |

| AH17           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH18           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH19           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | —              |

| AH20           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH21           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH22           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | —              |

| AH23           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH24           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH25           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH26           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH27           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| AH28           | Reserved <sup>1</sup> |                      |         |         |         |           |          |                 |         |         | _              |

| Notes:         |                       |                      |         |         |         |           |          |                 |         |         |                |

*GPIO* in the *MSC8144 Reference Manual*.**4.** Open-drain signal.

**5.** Internal 20 K $\Omega$  pull-up resistor.

6. For signals with GPIO functionality, the open-drain and internal 20 KΩ pull-up resistor can be configured by GPIO register programming. See Chapter 23, GPIO of the MSC8144 Reference Manual for configuration details.

rical Characteristics

## 2.5.6 ATM/UTOPIA/POS DC Electrical Characteristics

| Characteristic                                                 | Symbol            | Min   | Max   | Unit |

|----------------------------------------------------------------|-------------------|-------|-------|------|

| Supply voltage 3.3 V                                           | V <sub>DDIO</sub> | 3.135 | 3.465 | V    |

| Input high voltage                                             | V <sub>IH</sub>   | 2.0   | 3.465 | V    |

| Input low voltage                                              | V <sub>IL</sub>   | -0.3  | 0.8   | V    |

| Input leakage current, V <sub>IN</sub> = supply voltage        | I <sub>IN</sub>   | -30   | 30    | μA   |

| Signal low input current, V <sub>IL</sub> = 0.4 V <sup>1</sup> | ΙL                | -30   | 30    | μA   |

| Signal high input current, $V_{IH} = 2.4 V^1$                  | Ι <sub>Η</sub>    | -30   | 30    | μΑ   |

| Output high voltage, I <sub>OH</sub> = -4 mA                   | V <sub>OH</sub>   | 2.4   | 3.465 | V    |

| Output low voltage, I <sub>OL</sub> = 4 mA                     | V <sub>OL</sub>   | _     | 0.5   | V    |

| Notes: 1. Not tested. Guaranteed by design.                    | ÷                 | •     | *     |      |

## 2.5.7 SPI DC Electrical Characteristics

Table 14 provides the SPI DC electrical characteristics.

**Table 14. SPI DC Electrical Characteristics**

| Characteristic                                 | Symbol          | Min  | Мах   | Unit |

|------------------------------------------------|-----------------|------|-------|------|

| Input high voltage                             | V <sub>IH</sub> | 2.0  | 3.465 | V    |

| Input low voltage                              | V <sub>IL</sub> | -0.3 | 0.8   | V    |

| Input current                                  | I <sub>IN</sub> |      | 30    | μΑ   |

| Output high voltage, I <sub>OH</sub> = -4.0 mA | V <sub>OH</sub> | 2.4  | _     | V    |

| Output low voltage, I <sub>OL</sub> = 4.0 mA   | V <sub>OL</sub> | _    | 0.5   | V    |

# 2.5.8 GPIO, UART, TIMER, EE, STOP\_BS, I<sup>2</sup>C, IRQn, NMI\_OUT, INT\_OUT, CLKIN, JTAG Ports DC Electrical Characteristics

Table 15. GPIO, UART, Timer, EE, STOP\_BS, I<sup>2</sup>C, IRQn, NMI\_OUT, INT\_OUT, CLKIN, and JTAG Port<sup>1</sup> DC Electrical Characteristics

| Characteristic                                                                                                                        | Symbol            | Min   | Max   | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|-------|------|

| Supply voltage 3.3 V                                                                                                                  | V <sub>DDIO</sub> | 3.135 | 3.465 | V    |

| Input high voltage                                                                                                                    | V <sub>IH</sub>   | 2.0   | 3.465 | V    |

| Input low voltage                                                                                                                     | V <sub>IL</sub>   | -0.3  | 0.8   | V    |

| Input leakage current, V <sub>IN</sub> = supply voltage                                                                               | I <sub>IN</sub>   | -30   | 30    | μΑ   |

| Tri-state (high impedance off state) leakage current, $V_{IN}$ = supply voltage                                                       | I <sub>OZ</sub>   | -30   | 30    | μΑ   |

| Signal low input current, $V_{IL} = 0.4 V^2$                                                                                          | ١                 | -30   | 30    | μΑ   |

| Signal high input current, V <sub>IH</sub> = 2.0 V <sup>2</sup>                                                                       | Ι <sub>Η</sub>    | -30   | 30    | μΑ   |

| Output high voltage, I <sub>OH</sub> = -2 mA,<br>except open drain pins                                                               | V <sub>OH</sub>   | 2.4   | 3.465 | V    |

| Output low voltage, I <sub>OL</sub> = 3.2 mA                                                                                          | V <sub>OL</sub>   | _     | 0.4   | V    |

| <ul> <li>Notes: 1. This does not include TDI and TMS, which have internal pu</li> <li>2. Not tested. Guaranteed by design.</li> </ul> | Illup resistors.  | •     | •     | ·    |

## 2.6.4 DDR SDRAM AC Timing Specifications

This section describes the AC electrical characteristics for the DDR SDRAM interface.

## 2.6.4.1 DDR SDRAM Input Timings

Table 20 provides the input AC timing specifications for the DDR SDRAM when  $V_{DDDDR}$  (typ) = 2.5 V.

#### Table 20. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

| Parameter                                                                      | Symbol          | Min                      | Мах                      | Unit |

|--------------------------------------------------------------------------------|-----------------|--------------------------|--------------------------|------|

| AC input low voltage                                                           | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.31 | V    |

| AC input high voltage                                                          | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | —                        | V    |

| <b>Note:</b> At recommended operating conditions with $V_{DDDDR}$ of 2.5 ± 5%. |                 |                          |                          |      |

Table 21 provides the input AC timing specifications for the DDR SDRAM when  $V_{DDDDR}$  (typ) = 1.8 V.

#### Table 21. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

| Parameter                                                               | Symbol          | Min                      | Мах                      | Unit |

|-------------------------------------------------------------------------|-----------------|--------------------------|--------------------------|------|

| AC input low voltage                                                    | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    |

| AC input high voltage                                                   | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | —                        | V    |

| Note: At recommended operating conditions with $V_{DDDDR}$ of 1.8 ± 5%. |                 |                          |                          |      |

Table 22 provides the input AC timing specifications for the DDR SDRAM interface.

#### Table 22. DDR SDRAM Input AC Timing Specifications

|                                                                                                                                                                                                                    | Parameter                                                               | Symbol              | Min  | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|------|-----|------|

| Controller Sk                                                                                                                                                                                                      | ew for MDQS—MDQ/MECC/MDM <sup>1</sup>                                   | t <sub>CISKEW</sub> |      |     |      |

| • 400 MHz                                                                                                                                                                                                          |                                                                         |                     | -365 | 365 | ps   |

| • 333 MHz                                                                                                                                                                                                          |                                                                         |                     | -390 | 390 | ps   |

| • 266 MHz                                                                                                                                                                                                          |                                                                         |                     | -428 | 428 | ps   |

| • 200 MHz                                                                                                                                                                                                          |                                                                         |                     | -490 | 490 | ps   |

| <b>Notes:</b> 1. t <sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding captured with MDQS[n]. Subtract this value from the total timing budget. |                                                                         |                     |      |     |      |

| 2.                                                                                                                                                                                                                 | At recommended operating conditions with V <sub>and</sub> (1.8 V or 2.5 | 0                   |      |     |      |

2. At recommended operating conditions with  $V_{DDDDR}$  (1.8 V or 2.5 V)  $\pm$  5%

#### rical Characteristics

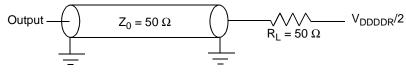

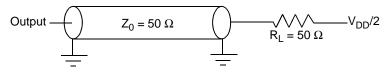

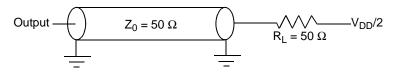

Figure 10 provides the AC test load for the DDR bus.

Figure 10. DDR AC Test Load

## 2.6.5 Serial RapidIO Timing and SGMII Timing

## 2.6.5.1 AC Requirements for SRIO\_REF\_CLK and SRIO\_REF\_CLK

Table 24 lists AC signal specifications.

| Parameter Description | Symbol           | Min | Typical     | Max | Units | Comments                                                                                                                                                                                                                        |

|-----------------------|------------------|-----|-------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK cycle time     | t <sub>REF</sub> | _   | 10 (8, 6.4) | _   | ns    | 8 ns applies only to serial RapidIO system<br>with 125-MHz reference clock. 6.4 ns<br>applies only to serial RapidIO systems with<br>a 156.25 MHz reference clock.<br><b>Note:</b> SGMII uses the 8 ns (125 MHz)<br>value only. |

## 2.6.5.2 Signal Definitions

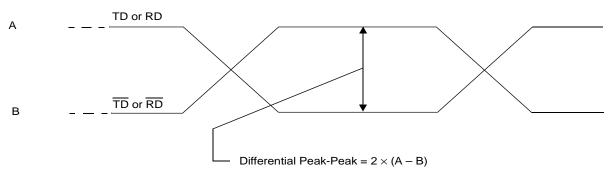

LP-Serial links use differential signaling. This section defines terms used in the description and specification of differential signals. Figure 11 shows how the signals are defined. The figure shows waveforms for either a transmitter output (TD and  $\overline{\text{TD}}$ ) or a receiver input (RD and  $\overline{\text{RD}}$ ). Each signal swings between voltage levels A and B, where A > B.

Figure 11. Differential  $V_{PP}$  of Transmitter or Receiver

**Note:** This explanation uses generic TD/TD/RD/RD signal names. These correspond to SRIO\_TXD/SRIO\_TXD/SRIO\_RXD/SRIO\_RXD respectively.

#### **Electrical Characteristics**

| Chamatariatia               | Complexed           | Range |      | 11               | Natas                                                                         |

|-----------------------------|---------------------|-------|------|------------------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit             | Notes                                                                         |

| Output Voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V                | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV <sub>PP</sub> |                                                                               |

| Deterministic Jitter        | J <sub>D</sub>      |       | 0.17 | UI <sub>PP</sub> |                                                                               |

| Total Jitter                | J <sub>T</sub>      |       | 0.35 | UI <sub>PP</sub> |                                                                               |

| Multiple output skew        | S <sub>MO</sub>     |       | 1000 | ps               | Skew at the transmitter output between lanes of a multilane link              |

| Unit Interval               | UI                  | 400   | 400  | ps               | ±100 ppm                                                                      |

#### Table 29. Long Run Transmitter AC Timing Specifications—2.5 GBaud

#### Table 30. Long Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Cumula al           | Range |      | l lucit          | Netes                                                                         |

|-----------------------------|---------------------|-------|------|------------------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit             | Notes                                                                         |

| Output Voltage              | Vo                  | -0.40 | 2.30 | V                | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential Output Voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mV <sub>PP</sub> |                                                                               |

| Deterministic Jitter        | J <sub>D</sub>      |       | 0.17 | UI <sub>PP</sub> |                                                                               |

| Total Jitter                | J <sub>T</sub>      |       | 0.35 | UI <sub>PP</sub> |                                                                               |

| Multiple output skew        | S <sub>MO</sub>     |       | 1000 | ps               | Skew at the transmitter output between lanes of a multilane link              |

| Unit Interval               | UI                  | 320   | 320  | ps               | ±100 ppm                                                                      |

For each baud rate at which an LP-Serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the transmitter output compliance mask shown in Figure 12 with the parameters specified in Table 31 when measured at the output pins of the device and the device is driving a  $100 \Omega \pm 5\%$  differential resistive load. The output eye pattern of an LP-Serial transmitter that implements pre-emphasis (to equalize the link and reduce inter-symbol interference) need only comply with the transmitter output compliance mask when pre-emphasis is disabled or minimized.

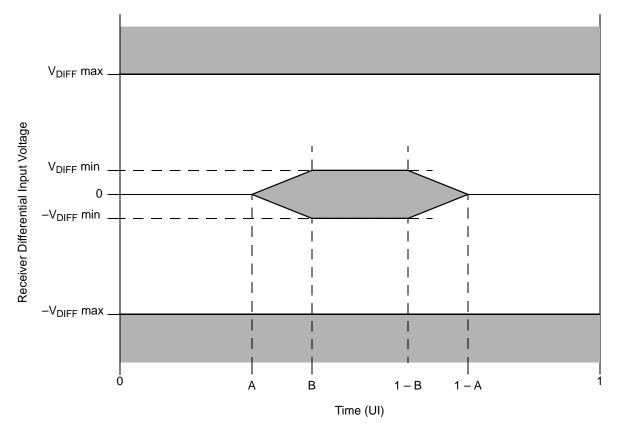

## 2.6.5.6 Receiver Eye Diagrams

For each baud rate at which an LP-Serial receiver is specified to operate, the receiver shall meet the corresponding bit error rate specification (Table 32, Table 33, and Table 34) when the eye pattern of the receiver test signal (exclusive of sinusoidal jitter) falls entirely within the unshaded portion of the receiver input compliance mask shown in Figure 14 with the parameters specified in Table 35. The eye pattern of the receiver test signal is measured at the input pins of the receiving device with the device replaced with a 100  $\Omega \pm 5\%$  differential resistive load.

Figure 14. Receiver Input Compliance Mask

| Receiver Type | V <sub>DIFF</sub> min (mV) | V <sub>DIFF</sub> max (mV) | A (UI) | B (UI) |  |

|---------------|----------------------------|----------------------------|--------|--------|--|

| 1.25 GBaud    | 100                        | 800                        | 0.275  | 0.400  |  |

| 2.5 GBaud     | 100                        | 800                        | 0.275  | 0.400  |  |

| 3.125 GBaud   | 100                        | 800                        | 0.275  | 0.400  |  |

## 2.6.5.7 Measurement and Test Requirements

Since the LP-Serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of **IEEE** Std. 802.3ae-2002<sup>TM</sup>, the measurement and test requirements defined here are similarly guided by Clause 47. In addition, the CJPAT test pattern defined in Annex 48A of **IEEE** Std. 802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of **IEEE** Std. 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

**Electrical Characteristics**

#### Table 36. PCI AC Timing Specifications (continued)

|        |                                                                                                                                                                                    | Devementer                                                                            | Symphol       | 33 MHz           |                | 66  | Unit |                |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------|------------------|----------------|-----|------|----------------|--|

|        | Parameter                                                                                                                                                                          |                                                                                       | Symbol        | Min              | Max            | Min | Max  | Unit           |  |

| Notes: | Notes: 1. See the timing measurement conditions in the PCI 2.2 Local Bus Specifications.                                                                                           |                                                                                       |               |                  |                |     |      |                |  |

|        | 2. All PCI signals are measured from $0.5 \times V_{DDIO}$ of the rising edge of PCI_CLK_IN to $0.4 \times V_{DDIO}$ of the signal in question fo                                  |                                                                                       |               |                  |                |     |      | n question for |  |

|        | <ul><li>3.3-V PCI signaling levels.</li><li>3. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered</li></ul> |                                                                                       |               |                  |                |     |      |                |  |

|        |                                                                                                                                                                                    |                                                                                       |               |                  |                |     |      | elivered       |  |

|        |                                                                                                                                                                                    | through the component pin is less than or equal to the leakage current specification. |               |                  |                |     |      |                |  |

|        | 4.                                                                                                                                                                                 | Input timings are measured at the pin.                                                |               |                  |                |     |      |                |  |

|        | 5.                                                                                                                                                                                 | The reset assertion timing requirer                                                   | ment for HRES | ET is in Table 1 | 9 and Figure 7 |     |      |                |  |

Figure 15 provides the AC test load for the PCI.

Figure 15. PCI AC Test Load

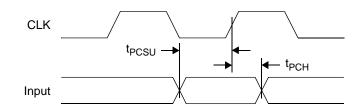

Figure 16 shows the PCI input AC timing conditions.

Figure 16. PCI Input AC Timing Measurement Conditions

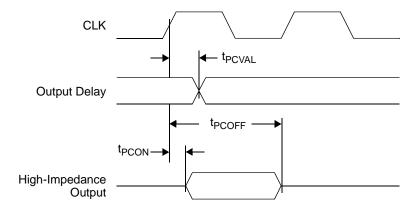

Figure 17 shows the PCI output AC timing conditions.

Figure 17. PCI Output AC Timing Measurement Condition

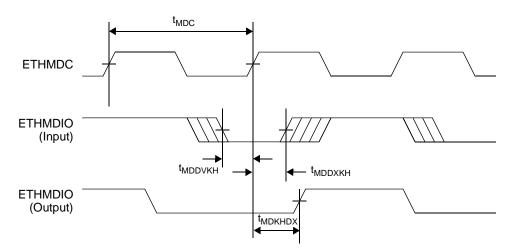

Figure 24. MII Management Interface Timing

## 2.6.10.2 MII Transmit AC Timing Specifications

Table 41 provides the MII transmit AC timing specifications.

| Table 41 | MII | <b>Transmit AC</b> | <b>Timing</b> | Specifications |

|----------|-----|--------------------|---------------|----------------|

|----------|-----|--------------------|---------------|----------------|

|                                                                                                                                                                     |      | Parameter/Condition                  | Symbol <sup>1</sup> | Min | Max | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------|---------------------|-----|-----|------|

| TX_CLK                                                                                                                                                              | to M | II data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub> | 0   | 25  | ns   |

| Notes:         1.         Typical TX_CLK period (t <sub>MTX</sub> ) for 10 Mbps is 400 ns and for 100 Mbps is 40 ns.         2.         Program GCR4 as 0x00030CC3. |      |                                      |                     |     |     |      |

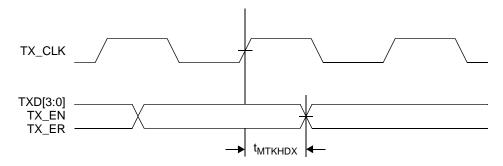

Figure 25 shows the MII transmit AC timing diagram.

Figure 25. MII Transmit AC Timing

## 2.6.10.3 MII Receive AC Timing Specifications

Table 42 provides the MII receive AC timing specifications.

| Parameter/Condition                                                                                                                                                 | Symbol <sup>1</sup> | Min  | Max | Unit |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-----|------|--|--|

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK                                                                                                                         | t <sub>mrdvkh</sub> | 10.0 |     | ns   |  |  |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK                                                                                                                          | t <sub>mrdxkh</sub> | 2    | _   | ns   |  |  |

| Notes:         1.         Typical RX_CLK period (t <sub>MRX</sub> ) for 10 Mbps is 400 ns and for 100 Mbps is 40 ns.         2.         Program GCR4 as 0x00030CC3. |                     |      |     |      |  |  |

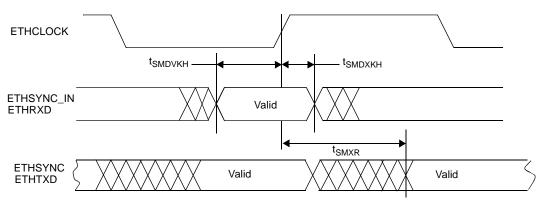

Figure 30. SMII Mode Signal Timing

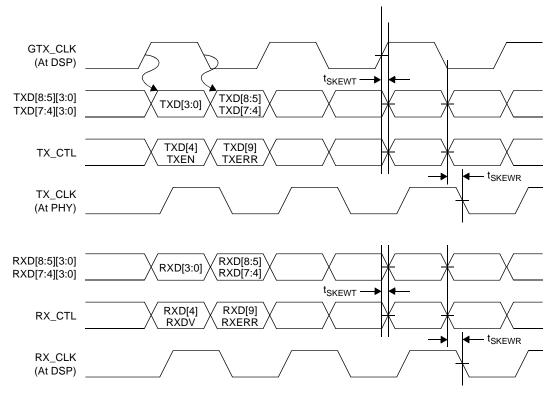

## 2.6.10.6 RGMII AC Timing Specifications

Table 45 presents the RGMII AC timing specifications for applications requiring an on-board delayed clock.

|                                                     |                | Parameter/Condition                                                                                                                                                                                                                                                   | Symbol             | Min     | Тур | Max | Unit |

|-----------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-----|-----|------|

| Data to o                                           | clock          | output skew (at transmitter)                                                                                                                                                                                                                                          | t <sub>SKEWT</sub> | -0.5    | _   | 0.5 | ns   |

| Data to clock input skew (at receiver) <sup>2</sup> |                |                                                                                                                                                                                                                                                                       | t <sub>SKEWR</sub> | 0.9     | _   | 2.6 | ns   |

| Notes:                                              | 1.<br>2.<br>3. | <ul> <li>At recommended operating conditions with LV<sub>DD</sub> of 2.5 V +/- 5%.</li> <li>This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 n added to the associated clock signal.</li> </ul> |                    | 5 ns is |     |     |      |

Table 46 presents the RGMII AC timing specification for applications required non-delayed clock on board.

### Table 46. RGMII with No On-Board Delay AC Timing Specifications

|                                                                                                                                                                                                                                                                            | Parameter/Condition                                 |  |                    | Min  | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--------------------|------|-----|------|------|

| Data to                                                                                                                                                                                                                                                                    | Data to clock output skew (at transmitter)          |  |                    | -2.6 | _   | -0.9 | ns   |

| Data to                                                                                                                                                                                                                                                                    | Data to clock input skew (at receiver) <sup>2</sup> |  | t <sub>SKEWR</sub> | -0.5 | _   | 0.5  | ns   |

| <ol> <li>Notes: 1. At recommended operating conditions with LV<sub>DD</sub> of 2.5 V +/- 5%.</li> <li>2. This implies that PC board design will require clocks to be routed with no additional trace delay</li> <li>3. GCR4 should be programmed as 0x0004C130.</li> </ol> |                                                     |  |                    |      |     |      |      |

Figure 31 shows the RGMII AC timing and multiplexing diagrams.

Figure 31. RGMII AC Timing and Multiplexing

## 2.6.11 ATM/UTOPIA/POS Timing

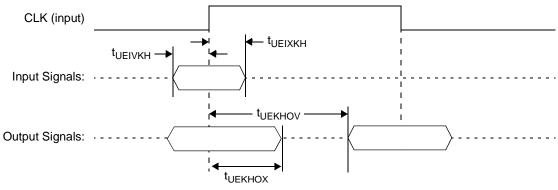

Table 47 provides the ATM/UTOPIA/POS input and output AC timing specifications.

| Characteristic                                     | Symbol              | Min | Max | Unit |  |

|----------------------------------------------------|---------------------|-----|-----|------|--|

| Outputs—External clock delay                       | t <sub>UEKHOV</sub> | 1   | 9   | ns   |  |

| Outputs—External clock High Impedance <sup>1</sup> | t <sub>UEKHOX</sub> | 1   | 9   | ns   |  |

**t**UEIVKH

t<sub>UEIXKH</sub>

#### Table 47. ATM/UTOPIA/POS AC Timing (External Clock) Specifications

Notes: 1. Not tested. Guaranteed by design.

Inputs-External clock input setup time

Inputs-External clock input hold time

Output specifications are measured from the 50% level of the rising edge of CLKIN to the 50% level of the signal. Timings are

measured at the pin. Although the specifications generally reference the rising edge of the clock, these AC timing diagrams

also apply when the falling edge is the active edge.

4

1

Figure 32 provides the AC test load for the ATM/UTOPIA/POS.

Figure 32. ATM/UTOPIA/POS AC Test Load

Figure 33 shows the ATM/UTOPIA/UTOPIA timing with external clock.

Figure 33. ATM/UTOPIAPOS AC Timing (External Clock)

ns

ns

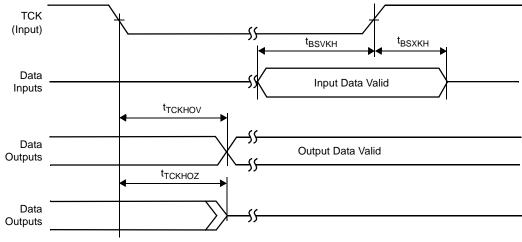

## 2.6.14 JTAG Signals

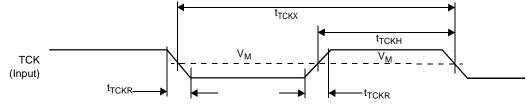

| Characteristics                                                                                         | Symbol             | All frequencies |      | 11-14 |

|---------------------------------------------------------------------------------------------------------|--------------------|-----------------|------|-------|

| Characteristics                                                                                         | Symbol             | Min             | Max  | Unit  |

| TCK cycle time                                                                                          | t <sub>тскх</sub>  | 36.0            | —    | ns    |

| TCK clock high phase measured at $V_{M}$ = 1.6 V                                                        | t <sub>тскн</sub>  | 15.0            | —    | ns    |

| Boundary scan input data setup time                                                                     | t <sub>BSVKH</sub> | 0.0             | —    | ns    |

| Boundary scan input data hold time                                                                      |                    | 15.0            | —    | ns    |

| TCK fall to output data valid                                                                           |                    | —               | 20.0 | ns    |

| TCK fall to output high impedance                                                                       |                    | —               | 24.0 | ns    |

| TMS, TDI data setup time                                                                                |                    | 0.0             | —    | ns    |

| TMS, TDI data hold time                                                                                 |                    | 5.0             | —    | ns    |

| TCK fall to TDO data valid                                                                              |                    | —               | 10.0 | ns    |

| TCK fall to TDO high impedance                                                                          |                    | —               | 12.0 | ns    |

| TRST assert time                                                                                        |                    | 100.0           | —    | ns    |

| Note: All timings apply to OnCE module data transfers as well as any other transfers via the JTAG port. |                    |                 |      |       |

#### Table 50. JTAG Timing

Figure 38 shows the Test Clock Input Timing Diagram

Figure 38. Test Clock Input Timing

Figure 39 shows the boundary scan (JTAG) timing diagram.

Figure 39. Boundary Scan (JTAG) Timing

ware Design Considerations

## Table 58. Connectivity of GE1 Related Pins When only a subset of the GE1 Interface Is required (continued)