# E·XFL

### NXP USA Inc. - MSC8144VT800A Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                              |

|-------------------------|-----------------------------------------------------------------------|

| Туре                    | SC3400 Core                                                           |

| Interface               | Ethernet, I <sup>2</sup> C, SPI, TDM, UART, UTOPIA                    |

| Clock Rate              | 800MHz                                                                |

| Non-Volatile Memory     | External                                                              |

| On-Chip RAM             | 10.5MB                                                                |

| Voltage - I/O           | 3.30V                                                                 |

| Voltage - Core          | 1.00V                                                                 |

| Operating Temperature   | 0°C ~ 90°C (TJ)                                                       |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 783-BBGA, FCBGA                                                       |

| Supplier Device Package | 783-FCPBGA (29x29)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8144vt800a |

|                         |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

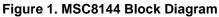

Figure 2. StarCore SC3400 DSP Core Subsystem Block Diagram

|                |                                 | Power-               |         |         | I/      | O Multipl | exing Mo | de <sup>2</sup> |            |         |                    |

|----------------|---------------------------------|----------------------|---------|---------|---------|-----------|----------|-----------------|------------|---------|--------------------|

| Ball<br>Number | Signal Name                     | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110)    | 7 (111) | Ref.<br>Supply     |

| E2             | GE1_RX_CLK/UTP_RD6/<br>PCI_PAR  |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E3             | GE1_RD2/UTP_RD4/<br>PCI_FRAME   |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E4             | GE1_RD1/UTP_RD3/<br>PCI_CBE3    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E5             | GE1_RD3/UTP_RD5/<br>PCI_IRDY    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E6             | V <sub>DDGE1</sub>              |                      |         |         |         |           |          |                 |            |         | V <sub>DDGE1</sub> |

| E7             | GE1_TX_EN/UTP_TD6/<br>PCI_CBE0  |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | PIA             | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| E8             | Reserved <sup>1</sup>           |                      |         |         |         |           |          |                 |            |         | —                  |

| E9             | Reserved <sup>1</sup>           |                      |         |         |         |           |          |                 |            |         | _                  |

| E10            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E11            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E12            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E13            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E14            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E15            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E16            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E17            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E18            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E19            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E20            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E21            | V <sub>DD</sub>                 |                      |         |         |         |           |          |                 |            |         | V <sub>DD</sub>    |

| E22            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| E23            | V <sub>DDDDR</sub>              |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| E24            | MDQ20                           |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| E25            | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

|                |                                 |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| E27            | V <sub>DDDDR</sub><br>GND       |                      |         |         |         |           |          |                 |            |         | GND                |

| E28            | MDQS2                           |                      |         |         |         |           |          |                 |            |         |                    |

| F1             | Reserved <sup>1</sup>           |                      |         |         |         |           |          |                 |            |         | V <sub>DDDDR</sub> |

| F2             | GE1_TX_CLK/UTP_RD0/<br>PCI_AD31 |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | )<br>PIA        | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| F3             | V <sub>DDGE1</sub>              |                      |         | ļ       |         |           |          |                 |            |         | V <sub>DDGE1</sub> |

| F4             | GE1_TD3/UTP_TD5/<br>PCI_AD30    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | DPIA            | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| F5             | GE1_TD1/UTP_TD3/<br>PCI_AD28    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | DPIA            | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| F6             | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

| F7             | GE1_TD0/UTP_TD2/<br>PCI_AD27    |                      | UTOPIA  | Ethe    | rnet 1  | PCI       | UTC      | )<br>PIA        | Ethernet 1 | UTOPIA  | V <sub>DDGE1</sub> |

| F8             | V <sub>DDGE1</sub>              |                      |         |         |         |           |          |                 |            |         | V <sub>DDGE1</sub> |

| F9             | GND                             |                      |         |         |         |           |          |                 |            |         | GND                |

|                |                                                             | Power-               |              |               | I/      | O Multipl | exing Mo | de <sup>2</sup> |         |         |                    |

|----------------|-------------------------------------------------------------|----------------------|--------------|---------------|---------|-----------|----------|-----------------|---------|---------|--------------------|

| Ball<br>Number | Signal Name                                                 | On<br>Reset<br>Value | 0 (000)      | 1 (001)       | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110) | 7 (111) | Ref.<br>Supply     |

| G23            | MBA1                                                        |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| G24            | MA3                                                         |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| G25            | MA8                                                         |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| G26            | V <sub>DDDDR</sub>                                          |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| G27            | GND                                                         |                      |              |               |         |           |          |                 |         |         | GND                |

| G28            | MCK0                                                        |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| H1             | Reserved <sup>1</sup>                                       |                      |              |               |         |           |          |                 |         |         | _                  |

| H2             | CLKIN                                                       |                      |              |               |         |           |          |                 |         |         | V <sub>DDIO</sub>  |

| H3             | HRESET                                                      |                      |              |               |         |           |          |                 |         |         | V <sub>DDIO</sub>  |

| H4             | PCI_CLK_IN                                                  |                      |              |               |         |           |          |                 |         |         | V <sub>DDIO</sub>  |

| H5             | NMI                                                         |                      |              |               |         |           |          |                 |         |         | V <sub>DDIO</sub>  |

| H6             | URXD/GPIO14/IRQ8/<br>RC_LDF <sup>3, 6</sup>                 | RC_LDF               |              |               | UA      | ART/GPIO  | /IRQ     |                 |         |         | V <sub>DDIO</sub>  |

| H7             | GE1_RX <u>_ER/P</u> CI_AD6/<br>GPIO25/IRQ15 <sup>3, 6</sup> |                      | GPIO/<br>IRQ | Ethernet<br>1 |         | PCI       |          | GPIO/<br>IRQ    | Ether   | net 1   | V <sub>DDIO</sub>  |

| H8             | GE1_CRS/PCI_AD5                                             |                      | PCI          | Ethernet<br>1 |         | Р         | CI       |                 | Ether   | net 1   | V <sub>DDIO</sub>  |

| H9             | GND                                                         |                      |              |               |         |           |          |                 |         |         | GND                |

| H10            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |         | V <sub>DD</sub>    |

| H11            | GND                                                         |                      |              |               |         |           |          |                 |         |         | GND                |

| H12            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |         | V <sub>DD</sub>    |

| H13            | GND                                                         |                      |              |               |         |           |          |                 |         |         | GND                |

| H14            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |         | V <sub>DD</sub>    |

| H15            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |         | V <sub>DD</sub>    |

| H16            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |         | V <sub>DD</sub>    |

| H17            | GND                                                         |                      |              |               |         |           |          |                 |         |         | GND                |

| H18            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |         | V <sub>DD</sub>    |

| H19            | GND                                                         |                      |              |               |         |           |          |                 |         |         | GND                |

| H20            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |         | V <sub>DD</sub>    |

| H21            | V <sub>DD</sub>                                             |                      |              |               |         |           |          |                 |         |         | V <sub>DD</sub>    |

| H22            | V <sub>DDDDR</sub>                                          |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| H23            | MBA0                                                        |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| H24            | MA15                                                        |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| H25            | V <sub>DDDDR</sub>                                          |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| H26            | MA9                                                         |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| H27            | MA7                                                         |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| H28            | МСК0                                                        |                      |              |               |         |           |          |                 |         |         | V <sub>DDDDR</sub> |

| J1             | Reserved <sup>1</sup>                                       |                      |              | 1             |         |           | Ī        |                 |         |         | _                  |

| J2             | GND                                                         |                      |              |               |         |           |          |                 |         |         | GND                |

| J3             | V <sub>DDIO</sub>                                           |                      |              | 1             |         |           |          |                 |         |         | V <sub>DDIO</sub>  |

| J4             | STOP_BS                                                     |                      |              | 1             |         |           |          |                 |         |         | V <sub>DDIO</sub>  |

| J5             | NMI_OUT <sup>4</sup>                                        |                      |              | 1             |         |           |          |                 |         |         | V <sub>DDIO</sub>  |

| J6             | INT_OUT <sup>4</sup>                                        |                      |              |               |         |           |          |                 |         |         | V <sub>DDIO</sub>  |

| J7             | SDA/GPIO27 <sup>3, 4, 6</sup>                               |                      |              | •             |         | I2C/GPIC  |          |                 |         |         | V <sub>DDIO</sub>  |

|                |                       | Power-               |         |           | I/      | O Multipl                                  | exing Mo | de <sup>2</sup> |          |         |                                        |

|----------------|-----------------------|----------------------|---------|-----------|---------|--------------------------------------------|----------|-----------------|----------|---------|----------------------------------------|

| Ball<br>Number | Signal Name           | On<br>Reset<br>Value | 0 (000) | 1 (001)   | 2 (010) | 3 (011)                                    | 4 (100)  | 5 (101)         | 6 (110)  | 7 (111) | Ref.<br>Supply                         |

| T21            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| T22            | V <sub>DDDDR</sub>    |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| T23            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| T24            | V <sub>DDDDR</sub>    |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| T25            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| T26            | V <sub>DDDDR</sub>    |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| T27            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| T28            | V <sub>DDDDR</sub>    |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| U1             | Reserved <sup>1</sup> |                      |         |           |         |                                            |          |                 |          |         | _                                      |

| U2             | UTP_TCLK/PCI_AD29     |                      | UTC     | OPIA      | PCI     |                                            | •        | UTOPIA          |          | •       | V <sub>DDIO</sub>                      |

| U3             | UTP_TADDR4/PCI_AD27   |                      | UTC     | OPIA      | PCI     |                                            |          | UTOPIA          |          |         | V <sub>DDIO</sub>                      |

| U4             | UTP_TADDR2            |                      |         |           |         | UT                                         | OPIA     |                 |          |         | V <sub>DDIO</sub>                      |

| U5             | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| U6             | UTP_REN/PCI_AD20      |                      | UTC     | OPIA      | PCI     |                                            |          | UTOPIA          |          | 1       | V <sub>DDIO</sub>                      |

| U7             | PCI_AD26              |                      |         |           |         | F                                          | PCI      |                 |          |         | V <sub>DDIO</sub>                      |

| U8             | PCI_AD25              |                      |         |           |         | F                                          | PCI      |                 |          |         | V <sub>DDIO</sub>                      |

| U9             | Reserved <sup>1</sup> |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDIO</sub>                      |

| U10            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDM3</sub>                      |

| U11            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| U12            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDM3</sub>                      |

| U13            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| U14            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDM3</sub>                      |

| U15            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| U16            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDM3</sub>                      |

| U17            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| U18            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDM3</sub>                      |

| U19            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| U20            | V <sub>DDM3</sub>     |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDM3</sub>                      |

| U21            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| U22            | GND                   |                      |         |           |         |                                            |          |                 |          |         | GND                                    |

| U23            | MDQ7                  |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| U24            | MDQ3                  |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| U25            | MDQ4                  |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| U26            | MDQ5                  |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| U27            | MDQ1                  |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| U28            | MDQ0                  |                      |         |           |         |                                            |          |                 |          |         | V <sub>DDDDR</sub>                     |

| V1             | Reserved <sup>1</sup> |                      |         |           |         |                                            |          |                 |          |         | אטעטט •                                |

| V2             | UTP_TD10/PCI_CBE0     |                      | UTC     | )<br>DPIA | PCI     |                                            | 1        | UTOPIA          | <u> </u> | 1       | V <sub>DDIO</sub>                      |

| V2<br>V3       | UTP_TADDR3            |                      |         |           | 1 1 0   | і<br>— — — — — — — — — — — — — — — — — — — | OPIA     |                 |          |         | V <sub>DDIO</sub>                      |

| V3<br>V4       | UTP_TD1/PCI_PERR      |                      |         | OPIA      | P       | CI                                         |          |                 | OPIA     |         | V <sub>DDIO</sub>                      |

| V4<br>V5       | UTP_TADDR0/PCI_AD23   |                      |         |           | PCI     |                                            | 1        | UTOPIA          |          |         | V <sub>DDIO</sub>                      |

| V5<br>V6       | UTP_TADDR0/PCI_AD23   |                      |         |           | PCI     |                                            |          | UTOPIA          |          |         |                                        |

| V0<br>V7       | UTP_TCLAV/PCI_AD28    |                      |         |           | PCI     |                                            |          | UTOPIA          |          |         | V <sub>DDIO</sub><br>V <sub>DDIO</sub> |

Table 1. Signal List by Ball Number (continued)

|                |                                                            | Power-               |         |           | I/      | O Multiple | exing Mo | de <sup>2</sup> |             |         |                    |

|----------------|------------------------------------------------------------|----------------------|---------|-----------|---------|------------|----------|-----------------|-------------|---------|--------------------|

| Ball<br>Number | Signal Name                                                | On<br>Reset<br>Value | 0 (000) | 1 (001)   | 2 (010) | 3 (011)    | 4 (100)  | 5 (101)         | 6 (110)     | 7 (111) | Ref.<br>Supply     |

| AA7            | TDM4TCLK/PCI_AD10                                          |                      |         | TDM       |         | P          | CI       |                 | TDM         |         | V <sub>DDIO</sub>  |

| AA8            | TDM4TDAT/PCI_AD11                                          |                      |         | TDM       |         | P          | CI       |                 | TDM         |         | V <sub>DDIO</sub>  |

| AA9            | V <sub>DDIO</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDIO</sub>  |

| AA10           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AA11           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AA12           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AA13           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AA14           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AA15           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AA16           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AA17           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AA18           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AA19           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AA20           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AA21           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AA22           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AA23           | MDQ15                                                      |                      |         |           |         |            |          |                 |             |         | V <sub>DDDDR</sub> |

| AA24           | MDQ14                                                      |                      |         |           |         |            |          |                 |             |         | V <sub>DDDDR</sub> |

| AA25           | MDM1                                                       |                      |         |           |         |            |          |                 |             |         | V <sub>DDDDR</sub> |

| AA26           | MDQ12                                                      |                      |         |           |         |            |          |                 |             |         | V <sub>DDDDR</sub> |

| AA27           | MDQS1                                                      |                      |         |           |         |            |          |                 |             |         | V <sub>DDDDR</sub> |

| AA28           | MDQS1                                                      |                      |         |           |         |            |          |                 |             |         | V <sub>DDDDR</sub> |

| AB1            | Reserved <sup>1</sup>                                      |                      |         |           |         |            |          |                 |             |         | -                  |

| AB2            | UTP_TSOC/RC15                                              | RC15                 |         |           |         | UT         | OPIA     |                 |             |         | V <sub>DDIO</sub>  |

| AB3            | V <sub>DDIO</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDIO</sub>  |

| AB4            | TDM6RDAT/PCI_AD20/<br>GPI05/IRQ11 <sup>3, 6</sup>          |                      | TD      | M/GPIO/ I | RQ      | P          | CI       | TC              | )M/GPIO/ II | RQ      | V <sub>DDIO</sub>  |

| AB5            | TDM5RDAT/PCI_AD14/<br>GPIO9 <sup>3, 6</sup>                |                      | -       | TDM/GPI0  | )       | P          | CI       |                 | TDM/GPIC    | )       | V <sub>DDIO</sub>  |

| AB6            | TDM6TSYN/PCI_AD24/<br>GPIO8/ IRQ14 <sup>3, 6</sup>         |                      | TD      | M/GPIO/I  | RQ      | P          | CI       | Т               | DM/GPIO/IF  | RQ      | V <sub>DDIO</sub>  |

| AB7            | TDM6R <u>CLK/PCI_</u> AD19/<br>GPIO4/IRQ10 <sup>3, 6</sup> |                      | TD      | M/GPIO/I  | RQ      | P          | CI       | Т               | DM/GPIO/IF  | RQ      | V <sub>DDIO</sub>  |

| AB8            | TDM4RSYN/PCI_AD9                                           |                      |         | TDM       |         | P          | CI       |                 | TDM         |         | V <sub>DDIO</sub>  |

| AB9            | TDM4RDAT/PCI_AD8                                           |                      |         | TDM       |         | P          | CI       |                 | TDM         |         | V <sub>DDIO</sub>  |

| AB10           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AB11           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AB12           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AB13           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AB14           | GND                                                        |                      |         |           |         |            |          |                 |             |         | GND                |

| AB15           | V <sub>DDM3</sub>                                          |                      |         |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AB16           | GND                                                        |                      | 1       |           |         |            |          |                 |             |         | GND                |

| AB17           | V <sub>DDM3</sub>                                          |                      | 1       |           |         |            |          |                 |             |         | V <sub>DDM3</sub>  |

| AB18           | GND                                                        |                      |         |           |         |            |          |                 |             | 1       | GND                |

| Dell           |                                      | Power-                 |         |         | I/      | O Multipl | exing Mo | de <sup>2</sup> |         |         | Def                 |

|----------------|--------------------------------------|------------------------|---------|---------|---------|-----------|----------|-----------------|---------|---------|---------------------|

| Ball<br>Number | Signal Name                          | On<br>Reset<br>Value   | 0 (000) | 1 (001) | 2 (010) | 3 (011)   | 4 (100)  | 5 (101)         | 6 (110) | 7 (111) | Ref.<br>Supply      |

| AE19           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AE20           | V <sub>DDM3IO</sub>                  |                        |         |         |         |           |          |                 |         |         | V <sub>DDM3IO</sub> |

| AE21           | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |         | _                   |

| AE22           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AE23           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AE24           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AE25           | V <sub>DDDDR</sub>                   |                        |         |         |         |           |          |                 |         |         | V <sub>DDDDR</sub>  |

| AE26           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AE27           | V <sub>DDDDR</sub>                   |                        |         |         |         |           |          |                 |         |         | V <sub>DDDDR</sub>  |

| AE28           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF1            | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |         | _                   |

| AF2            | V <sub>DDIO</sub>                    |                        |         |         |         |           |          |                 |         |         | V <sub>DDIO</sub>   |

| AF3            | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF4            | TDM0RDAT/<br>RCFG_CLKIN_RNG          | RCFG_<br>CLKIN_<br>RNG |         |         |         | Т         | DM       |                 |         |         | V <sub>DDIO</sub>   |

| AF5            | TDM0TSYN/RCW_SRC2                    | RCW_<br>SRC2           |         |         |         | Т         | DM       |                 |         |         | V <sub>DDIO</sub>   |

| AF6            | TDM1RDAT/RC0                         | RC0                    |         |         |         | Т         | DM       |                 |         |         | V <sub>DDIO</sub>   |

| AF7            | V <sub>DDIO</sub>                    |                        |         |         |         |           |          |                 |         |         | V <sub>DDIO</sub>   |

| AF8            | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF9            | TDM2RDAT/RC4                         | RC4                    |         |         | •       | Т         | DM       | •               |         |         | V <sub>DDIO</sub>   |

| AF10           | TDM2TCLK                             |                        |         |         |         | Т         | DM       |                 |         |         | V <sub>DDIO</sub>   |

| AF11           | GPIO22/IRQ4 <sup>3, 6</sup> /SPIMOSI |                        |         |         |         | GPIO/     | IRQ/SPI  |                 |         |         | V <sub>DDIO</sub>   |

| AF12           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF13           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF14           | V <sub>DDM3IO</sub>                  |                        |         |         |         |           |          |                 |         |         | V <sub>DDM3IO</sub> |

| AF15           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF16           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF17           | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |         | _                   |

| AF18           | V <sub>DDM3IO</sub>                  |                        |         |         |         |           |          |                 |         |         | V <sub>DDM3IO</sub> |

| AF19           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF20           | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |         | _                   |

| AF21           | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |         | _                   |

| AF22           | M3_RESET                             |                        |         |         |         |           |          |                 |         |         | V <sub>DDM3IO</sub> |

| AF23           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF24           | V <sub>DDDDR</sub>                   |                        |         |         |         |           |          |                 |         |         | V <sub>DDDDR</sub>  |

| AF25           | GND                                  | 1                      |         |         |         |           |          |                 |         | 1       | GND                 |

| AF26           | V <sub>DDDDR</sub>                   | 1                      |         |         |         |           |          |                 |         | 1       | V <sub>DDDDR</sub>  |

| AF27           | GND                                  |                        |         |         |         |           |          |                 |         |         | GND                 |

| AF28           | V <sub>DDDDR</sub>                   |                        |         |         |         |           |          |                 |         |         | V <sub>DDDDR</sub>  |

| AG1            | Reserved <sup>1</sup>                |                        |         |         |         |           |          |                 |         |         | _                   |

| AG2            | GPIO16/IRQ0 <sup>3, 6</sup>          |                        |         |         |         | GPI       | 0/IRQ    |                 |         |         | V <sub>DDIO</sub>   |

| AG3            | TDM0TCLK                             | 1                      |         |         |         |           | DM       |                 |         |         | V <sub>DDIO</sub>   |

|                |                                     | Power-               |         | List by |         | -       | exing Mo | -       |         |         |                     |

|----------------|-------------------------------------|----------------------|---------|---------|---------|---------|----------|---------|---------|---------|---------------------|

| Ball<br>Number | Signal Name                         | On<br>Reset<br>Value | 0 (000) | 1 (001) | 2 (010) | 3 (011) | 4 (100)  | 5 (101) | 6 (110) | 7 (111) | Ref.<br>Supply      |

| AG4            | TDM0RSYN/RCW_SRC0                   | RCW_<br>SRC0         |         | •       | ·       | Т       | DM       | •       |         | •       | V <sub>DDIO</sub>   |

| AG5            | TDMORCLK                            |                      |         |         |         | Т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG6            | TDM0TDAT/RCW_SRC1                   | RCW_<br>SRC1         |         |         |         | Т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG7            | TDM2TSYN/RC7                        | RC7                  |         |         |         | Т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG8            | TDM2RCLK                            |                      |         |         |         | Т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG9            | TDM2RSYN/RC5                        | RC5                  |         |         |         | Т       | DM       |         |         |         | V <sub>DDIO</sub>   |

| AG10           | GPIO24/IRQ6 <sup>3, 6</sup> /SPISEL |                      |         |         |         | GPIO/   | IRQ/SPI  |         |         |         | V <sub>DDIO</sub>   |

| AG11           | GPIO23/IRQ53, 6/SPIMISO             |                      |         |         |         | GPIO/   | IRQ/SPI  |         |         |         | V <sub>DDIO</sub>   |

| AG12           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | —                   |

| AG13           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG14           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG15           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG16           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG17           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | _                   |

| AG18           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AG19           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG20           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG21           | V <sub>DDM3IO</sub>                 |                      |         |         |         |         |          |         |         |         | V <sub>DDM3IO</sub> |

| AG22           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG23           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG24           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG25           | V <sub>DDDDR</sub>                  |                      |         |         |         |         |          |         |         |         | V <sub>DDDDR</sub>  |

| AG26           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AG27           | V <sub>DDDDR</sub>                  |                      |         |         |         |         |          |         |         |         | V <sub>DDDDR</sub>  |

| AG28           | GND                                 |                      |         |         |         |         |          |         |         |         | GND                 |

| AH1            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | _                   |

| AH2            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH3            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH4            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | _                   |

| AH5            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH6            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH7            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | <u> </u>            |

| AH8            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH9            | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | _                   |

|                | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH10           | Reserved <sup>1</sup>               | -                    |         |         |         |         |          |         |         |         |                     |

| AH11           |                                     | -                    |         |         |         |         |          |         |         |         |                     |

| AH12           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH13           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH14           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         |                     |

| AH15           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | —                   |

| AH16           | Reserved <sup>1</sup>               |                      |         |         |         |         |          |         |         |         | —                   |

Table 1. Signal List by Ball Number (continued)

rical Characteristics

# 2 Electrical Characteristics

This document contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications. For additional information, see the *MSC8144 Reference Manual*.

# 2.1 Maximum Ratings

### CAUTION

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (for example, either GND or  $V_{DD}$ ).

In calculating timing requirements, adding a maximum value of one specification to a minimum value of another specification does not yield a reasonable sum. A maximum specification is calculated using a worst case variation of process parameter values in one direction. The minimum specification is calculated using the worst case for the same parameters in the opposite direction. Therefore, a "maximum" value for a specification never occurs in the same device with a "minimum" value for another specification; adding a maximum to a minimum represents a condition that can never exist.

Table 2 describes the maximum electrical ratings for the MSC8144.

| Rating                                                     | Symbol                                                            | Value                            | Unit   |

|------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------|--------|

| Core supply voltage                                        | V <sub>dd</sub>                                                   | -0.3 to 1.1                      | V      |

| PLL supply voltage <sup>3</sup>                            | V <sub>DDPLL0</sub><br>V <sub>DDPLL1</sub><br>V <sub>DDPLL2</sub> | -0.3 to 1.1                      | V      |

| M3 memory Internal voltage                                 | V <sub>DDM3</sub>                                                 | -0.3 to 1.32                     | V      |

| DDR memory supply voltage<br>• DDR mode<br>• DDR2 mode     | V <sub>DDDDR</sub>                                                | -0.3 to 2.75<br>-0.3 to 1.98     | V<br>V |

| DDR reference voltage                                      | MV <sub>REF</sub>                                                 | –0.3 to 0.51 $\timesV_{DDDDR}$   | V      |

| Input DDR voltage                                          | V <sub>INDDR</sub>                                                | –0.3 to V <sub>DDDDR</sub> + 0.3 | V      |

| Ethernet 1 I/O voltage                                     | V <sub>DDGE1</sub>                                                | -0.3 to 3.465                    | V      |

| Input Ethernet 1 I/O voltage                               | V <sub>INGE1</sub>                                                | –0.3 to V <sub>DDGE1</sub> + 0.3 | V      |

| Ethernet 2 I/O voltage                                     | V <sub>DDGE2</sub>                                                | -0.3 to 3.465                    | V      |

| Input Ethernet 2I/O voltage                                | V <sub>INGE2</sub>                                                | -0.3 to V <sub>DDGE2</sub> + 0.3 | V      |

| I/O voltage excluding Ethernet, DDR, M3, and RapidIO lines | V <sub>DDIO</sub>                                                 | -0.3 to 3.465                    | V      |

| Input I/O voltage                                          | V <sub>INIO</sub>                                                 | –0.3 to V <sub>DDIO</sub> + 0.3  | V      |

### Table 2. Absolute Maximum Ratings

| Rating                                          | Symbol                                   | Value                             | Unit |

|-------------------------------------------------|------------------------------------------|-----------------------------------|------|

| M3 memory I/O and M3 memory charge pump voltage | V <sub>DDM3IO</sub><br>V <sub>25M3</sub> | -0.3 to 2.75                      | V    |

| Input M3 memory I/O voltage                     | V <sub>INM3IO</sub>                      | -0.3 to V <sub>DDM3IO</sub> + 0.3 | V    |

| Rapid I/O C voltage                             | V <sub>DDSXC</sub>                       | -0.3 to 1.21                      | V    |

| Rapid I/O P voltage                             | V <sub>DDSXP</sub>                       | -0.3 to 1.26                      | V    |

| Rapid I/O PLL voltage                           | V <sub>DDRIOPLL</sub>                    | -0.3 to 1.21                      | V    |

| Operating temperature                           | TJ                                       | -40 to 105                        | °C   |

| Storage temperature range                       | T <sub>STG</sub>                         | -55 to +150                       | °C   |

### Table 2. Absolute Maximum Ratings

2. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond the listed limits may affect device reliability or cause permanent damage.

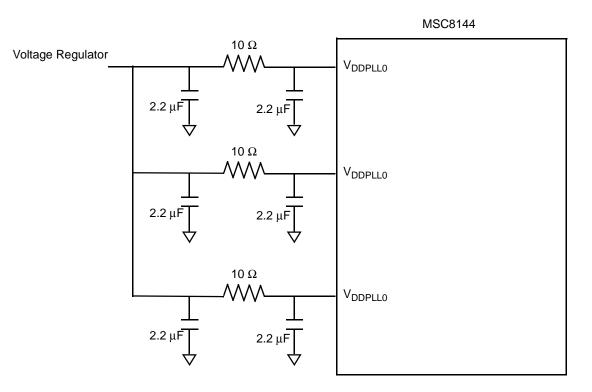

3. PLL supply voltage is specified at input of the filter and not at pin of the MSC8144 (see Figure 43)

# 2.2 Recommended Operating Conditions

Table 3 lists recommended operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Rating                                                                                      | Symbol                                                               | Min                             | Nominal                      | Мах                           | Unit           |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------|------------------------------|-------------------------------|----------------|

| Core supply voltage<br>• 800 MHz (VT, SVT, TVT) and<br>1000 MHz (VT)                        | V <sub>DD</sub>                                                      | 0.97                            | 1.0                          | 1.05                          | V              |

| • 1000 MHz (SVT, TVT)                                                                       |                                                                      | 0.97                            | 1.0                          | 1.03                          | V              |

| PLL supply voltage<br>• 800 MHz (VT, SVT, TVT) and<br>1000 MHz (VT)                         | V <sub>DDPLL0</sub><br>V <sub>DDPLL1</sub><br>V <sub>DDPLL2</sub>    | 0.97                            | 1.0                          | 1.05                          | V              |

| • 1000 MHz (SVT, TVT)                                                                       | DDFLLZ                                                               | 0.97                            | 1.0                          | 1.03                          | V              |

| M3 memory Internal voltage                                                                  | V <sub>DDM3</sub>                                                    | 1.213                           | 1.25                         | 1.313                         | V              |

| DDR memory supply voltage <ul> <li>DDR mode</li> <li>DDR2 mode</li> </ul>                   | V <sub>DDDDR</sub>                                                   | 2.375<br>1.71                   | 2.5<br>1.8                   | 2.625<br>1.89                 | V<br>V         |

| DDR reference voltage                                                                       | MV <sub>REF</sub>                                                    | $0.49 \times V_{DDDDR}$ (nom)   | $0.5 \times V_{DDDDR}$ (nom) | $0.51 \times V_{DDDDR}$ (nom) | V              |

| Ethernet 1 I/O voltage<br>• 2.5 V mode<br>• 3.3 V mode                                      | V <sub>DDGE1</sub>                                                   | 2.375<br>3.135                  | 2.5<br>3.3                   | 2.625<br>3.465                | V<br>V         |

| Ethernet 2 I/O voltage<br>• 2.5 V mode<br>• 3.3 V mode                                      | V <sub>DDGE2</sub>                                                   | 2.375<br>3.135                  | 2.5<br>3.3                   | 2.625<br>3.465                | V<br>V         |

| I/O voltage excluding Ethernet,<br>DDR, M3, and RapidIO lines                               | V <sub>DDIO</sub>                                                    | 3.135                           | 3.3                          | 3.465                         | V              |

| M3 memory I/O and M3 charge<br>pump voltage                                                 | V <sub>DDM3IO</sub><br>V <sub>25M3</sub>                             | 2.375                           | 2.5                          | 2.625                         | V              |

| Rapid I/O C voltage                                                                         | V <sub>DDSXC</sub>                                                   | 0.97                            | 1.0                          | 1.05                          | V              |

| Rapid I/O P voltage<br>• Short run (haul) mode<br>• Long run (haul) mode                    | V <sub>DDSXP</sub>                                                   | 0.97<br>1.14                    | 1.0<br>1.2                   | 1.05<br>1.26                  | V<br>V         |

| Rapid I/O PLL voltage                                                                       | V <sub>DDRIOPLL</sub>                                                | 0.97                            | 1.0                          | 1.05                          | V              |

| Operating temperature range:<br>• Standard (VT)<br>• Intermediate (SVT)<br>• Extended (TVT) | T <sub>J</sub><br>T <sub>J</sub><br>T <sub>A</sub><br>T <sub>I</sub> | 0<br>0<br>40                    |                              | 90<br>105<br>—<br>105         | ວ°<br>ວິ<br>ວິ |

| Note: PLL supply voltage is sp                                                              | J                                                                    | he filter and not at pin of the | ne MSC8144 (see Figure       |                               | -              |

### **Table 3. Recommended Operating Conditions**

rical Characteristics

# 2.3 Default Output Driver Characteristics

Table 4 provides information on the characteristics of the output driver strengths.

#### Table 4. Output Drive Impedance

| Driver Type | Output Impedance (Ω)          |

|-------------|-------------------------------|

| DDR signal  | 18                            |

| DDR2 signal | 18<br>35 (half strength mode) |

# 2.4 Thermal Characteristics

Table 5 describes thermal characteristics of the MSC8144 for the FC-PBGA packages.

| Table 5. | Thermal      | Characteristics | for | the | MSC8144  |

|----------|--------------|-----------------|-----|-----|----------|

|          | I IIGI IIIGI | onunuotonistios |     |     | 11000144 |

| Characteristic                                                                                            | Symbol                   |                       | PBGA<br>29 mm <sup>5</sup>    | Unit |

|-----------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|-------------------------------|------|

| Characteristic                                                                                            | Symbol                   | Natural<br>Convection | 200 ft/min<br>(1 m/s) airflow |      |

| Junction-to-ambient <sup>1, 2</sup>                                                                       | R <sub>θJA</sub>         | 20                    | 15                            | °C/W |

| Junction-to-ambient, four-layer board <sup>1, 3</sup>                                                     | R <sub>θJA</sub>         | 15                    | 12                            | °C/W |

| Junction-to-board (bottom) <sup>4</sup>                                                                   | R <sub>θJB</sub>         | 7                     |                               | °C/W |

| Junction-to-case <sup>5</sup>                                                                             | R <sub>θJC</sub>         | 0.8                   |                               | °C/W |

| Notes: 1. Junction temperature is a function of die temperature, ambient temperature, air fle resistance. | size, on-chip power diss |                       |                               | ```  |

2. Per JEDEC JESD51-2 with the single layer board (JESD51-3) horizontal.

3. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

4. Thermal resistance between the die and the printed circuit board per JEDEC JESD 51-8. Board temperature is measured on the top surface of the board near the package.

5. Thermal resistance between the active surface of the die and the case top surface determined by the cold plate method (MIL SPEC-883 Method 1012.1) with the calculated case temperature.

| Reset Action/Reset Source                                                   | Po <u>wer-On Re</u> set<br>(PORESET)                                      | Hard Reset (HRESET) | Sof                                 | t Reset (SRESET)                            |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------|-------------------------------------|---------------------------------------------|

| Reset Action/Reset Source                                                   | External or Intern<br>External only (Software Watchd<br>Software or Rapid |                     | External or<br>internal<br>Software | JTAG Command:<br>EXTEST, CLAMP, or<br>HIGHZ |

| HRESET driven                                                               | Yes                                                                       | Yes                 | No                                  | No                                          |

| IPBus modules reset (TDM, UART, SWT, DDRC, IPBus master, GIC, HS, and GPIO) | Yes                                                                       | Yes                 | Yes                                 | Yes                                         |

| SRESET driven                                                               | Yes                                                                       | Yes                 | Yes                                 | Depends on command                          |

| Extended cores reset                                                        | Yes                                                                       | Yes                 | Yes                                 | Yes                                         |

| CLASS registers reset                                                       | Yes                                                                       | Yes                 | Some<br>registers                   | Some registers                              |

| Timers, Performance Monitor                                                 | Yes                                                                       | Yes                 | No                                  | No                                          |

| QUICC Engine subsystem, PCI, DMA                                            | Yes                                                                       | Yes                 | Most<br>registers                   | Most registers                              |

#### Table 18. Reset Actions for Each Reset Source (continued)

# 2.6.3.1 Power-On Reset (PORESET) Pin

Asserting  $\overrightarrow{PORESET}$  initiates the power-on reset flow.  $\overrightarrow{PORESET}$  must be asserted externally for at least 32 CLKIN cycles after V<sub>DD</sub> and V<sub>DDIO</sub> are both at their nominal levels.

## 2.6.3.2 Reset Configuration

The MSC8144 has two mechanisms for writing the reset configuration:

- Through the  $I^2C$  port

- Through external pins

- Through internal hard coded

Twenty-three signals (see **Section 1** for signal description details) are sampled during the power-on reset sequence to define the Reset Word Configuration Source and operating conditions:

- RCW\_SRC[2–0]

- RC[16–0]

The RCFG\_CLKIN\_RNG pin must be valid during power-on or hard reset sequence. The STOP\_BS pin must be always valid and is also sampled during power-on reset sequence for RCW loading from an I<sup>2</sup>C EEPROM.

# 2.6.3.3 Reset Timing Tables

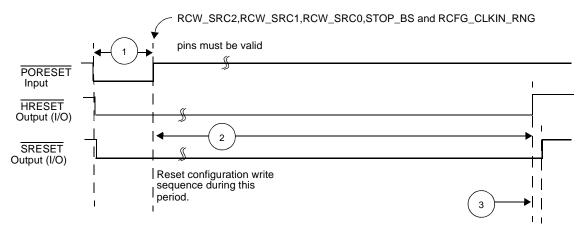

Table 19 and Figure 7 describe the reset timing for a reset configuration.

| Table 19 | . Timing f | or a Reset | Configuration | Write |

|----------|------------|------------|---------------|-------|

|----------|------------|------------|---------------|-------|

| No. | Characteristics                            | Expression | Max  | Min | Unit |

|-----|--------------------------------------------|------------|------|-----|------|

| 1   | Required external PORESET duration minimum | 32/CLKIN   |      |     |      |

|     | • 33 MHz <= CLKIN < 44 MHz                 |            | 1280 | 727 | ns   |

|     | • 44 MHz <= CLKIN < 66 MHz                 |            | 728  | 484 | ns   |

|     | • 66 MHz <= CLKIN < 100 MHz                |            | 485  | 320 | ns   |

|     | • 100 MHz <= CLKIN < 133 MHz               |            | 320  | 241 | ns   |

Table 19. Timing for a

| No.   | Characteristics                                                                                                                                        | Expression                 | Max        | Min        | Unit     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------|------------|----------|

| 2     | Delay from de-assertion of external PORESET to HRESET deassertion for external pins and hard coded RCW                                                 | 45000/01//01               | 0.15       |            |          |

|       | <ul> <li>33 MHz &lt;= CLKIN &lt; 66 MHz</li> <li>66 MHz &lt;= CLKIN &lt;= 133 MHz</li> </ul>                                                           | 15369/CLKIN<br>34825/CLKIN | 615<br>528 | 233<br>262 | μs<br>μs |

|       | Delay from de-assertion of external $\overrightarrow{PORESET}$ to $\overrightarrow{HRESET}$ deassertion for loading RCW the I <sup>2</sup> C interface |                            |            |            |          |

|       | • 33 MHz <= CLKIN < 44 MHz                                                                                                                             | 92545/CLKIN                | 3702       | 2103       | μs       |

|       | • 44 MHz <= CLKIN < 66 MHz                                                                                                                             | 107435/CLKIN               | 2441       | 1627       | μs       |

|       | • 66 MHz <= CLKIN < 100 MHz                                                                                                                            | 124208/CLKIN               | 1882       | 1242       | μs       |

|       | • 100 MHz <= CLKIN < 133 MHz                                                                                                                           | 157880/CLKIN               | 1579       | 1187       | μs       |

| 3     | Delay from HRESET deassertion to SRESET deassertion<br>• REFCLK = 33 MHz to 133 MHz                                                                    | 16/CLKIN                   | 640        | 120        | ns       |

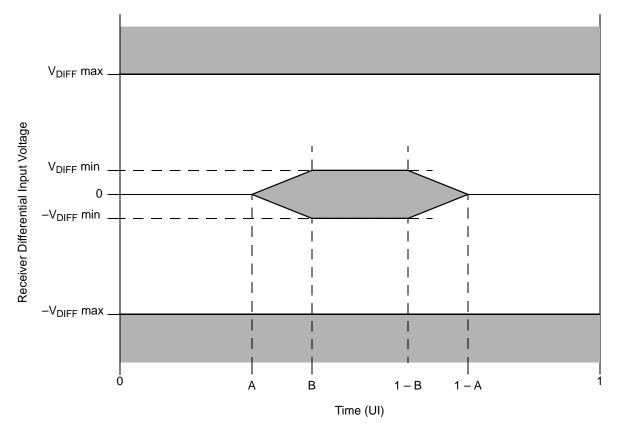

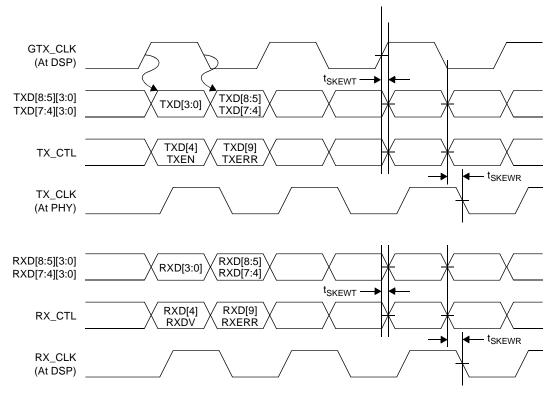

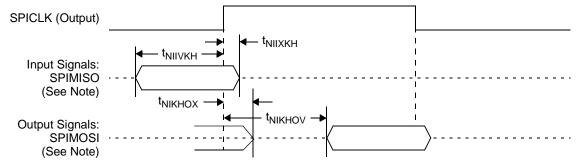

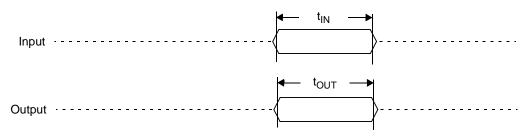

| Note: | Timings are not tested, but are guaranteed by design.                                                                                                  |                            | 1          |            |          |