#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product StatusObsoleteCore Processor80C51Core Size8-BitSpeed60MHzConnectivityIPC, SPI, UART/USARTPeripheralsPOR, PWM, WDTNumber of I/O34Program Memory Size64KB (64K × 8)Program Memory TypeFLASHEEPROM Size2K × 8RAM Size2K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-VQFP (10x10)Purchase UBLbttps://www.a.sfl.com/product.detail/microchin.techonlonu/at89c51id2.rdrim |                            |                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------|

| Core Size8-BitSpeed60MHzConnectivityIPC, SPI, UART/USARTPeripheralsPOR, PWM, WDTNumber of I/O34Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                  | Product Status             | Obsolete                                                                   |

| Speed60MHzConnectivityI²C, SPI, UART/USARTPeripheralsPOR, PWM, WDTNumber of I/O34Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                | Core Processor             | 80C51                                                                      |

| ConnectivityIPC, SPI, UART/USARTPeripheralsPOR, PWM, WDTNumber of I/O34Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                          | Core Size                  | 8-Bit                                                                      |

| PeripheralsPOR, PWM, WDTNumber of I/O34Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                          | Speed                      | 60MHz                                                                      |

| Number of I/O34Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                  | Connectivity               | I²C, SPI, UART/USART                                                       |

| Program Memory Size64KB (64K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                                 | Peripherals                | POR, PWM, WDT                                                              |

| Program Memory TypeFLASHEEPROM Size2K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                                                                  | Number of I/O              | 34                                                                         |

| EEPROM Size2K x 8RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                                                                                          | Program Memory Size        | 64KB (64K x 8)                                                             |

| RAM Size2K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                                                                                                           | Program Memory Type        | FLASH                                                                      |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 5.5VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                                                                                                                         | EEPROM Size                | 2K x 8                                                                     |

| Data Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                                                                                                                                                              | RAM Size                   | 2K x 8                                                                     |

| Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                                                                                                                                                                              | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case44-LQFPSupplier Device Package44-VQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                     | Data Converters            | -                                                                          |

| Mounting Type     Surface Mount       Package / Case     44-LQFP       Supplier Device Package     44-VQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                              | Oscillator Type            | External                                                                   |

| Package / Case     44-LQFP       Supplier Device Package     44-VQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                                                    | Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Supplier Device Package 44-VQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mounting Type              | Surface Mount                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Package / Case             | 44-LQFP                                                                    |

| Purchase URL https://www.exfl.com/product_detail/microchip_techpology/at89c51id2_rlrim                                                                                                                                                                                                                                                                                                                                                                                                          | Supplier Device Package    | 44-VQFP (10x10)                                                            |

| https://www.e-An.com/product-detai/merocmp-teermology/dc05051d2-firm                                                                                                                                                                                                                                                                                                                                                                                                                            | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51id2-rlrim |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 8. PCA SFRs

| Mnemo<br>-nic                                            | Add                                    | Name                                                                                                                                                                       | 7                                        | 6                                                    | 5                                                    | 4                                                    | 3                                               | 2                                               | 1                                               | 0                                                    |

|----------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|------------------------------------------------------|

| CCON                                                     | D8h                                    | PCA Timer/Counter Control                                                                                                                                                  | CF                                       | CR                                                   | -                                                    | CCF4                                                 | CCF3                                            | CCF2                                            | CCF1                                            | CCF0                                                 |

| CMOD                                                     | D9h                                    | PCA Timer/Counter Mode                                                                                                                                                     | CIDL                                     | WDTE                                                 | -                                                    | -                                                    | -                                               | CPS1                                            | CPS0                                            | ECF                                                  |

| CL                                                       | E9h                                    | PCA Timer/Counter Low byte                                                                                                                                                 |                                          |                                                      |                                                      |                                                      |                                                 |                                                 |                                                 |                                                      |

| СН                                                       | F9h                                    | PCA Timer/Counter High byte                                                                                                                                                |                                          |                                                      |                                                      |                                                      |                                                 |                                                 |                                                 |                                                      |

| CCAPM0<br>CCAPM1<br>CCAPM2<br>CCAPM3<br>CCAPM4<br>CCAP0H | DAh<br>DBh<br>DCh<br>DDh<br>DEh<br>FAh | PCA Timer/Counter Mode 0<br>PCA Timer/Counter Mode 1<br>PCA Timer/Counter Mode 2<br>PCA Timer/Counter Mode 3<br>PCA Timer/Counter Mode 4<br>PCA Compare Capture Module 0 H | -<br>CCAP0H7                             | ECOM0<br>ECOM1<br>ECOM2<br>ECOM3<br>ECOM4<br>CCAP0H6 | CAPP0<br>CAPP1<br>CAPP2<br>CAPP3<br>CAPP4<br>CCAP0H5 | CAPN0<br>CAPN1<br>CAPN2<br>CAPN3<br>CAPN4<br>CCAP0H4 | MAT0<br>MAT1<br>MAT2<br>MAT3<br>MAT4<br>CCAP0H3 | TOG0<br>TOG1<br>TOG2<br>TOG3<br>TOG4<br>CCAP0H2 | PWM0<br>PWM1<br>PWM2<br>PWM3<br>PWM4<br>CCAP0H1 | ECCF0<br>ECCF1<br>ECCF2<br>ECCF3<br>ECCF4<br>CCAP0H0 |

| CCAP1H<br>CCAP2H<br>CCAP3H                               | FBh<br>FCh<br>FDh                      | PCA Compare Capture Module 1 H<br>PCA Compare Capture Module 2 H<br>PCA Compare Capture Module 3 H                                                                         | CCAP2H7                                  | CCAP1H6<br>CCAP2H6<br>CCAP3H6                        | CCAP1H5<br>CCAP2H5<br>CCAP3H5                        | CCAP1H4<br>CCAP2H4<br>CCAP3H4                        | CCAP1H3<br>CCAP2H3<br>CCAP3H3                   | CCAP1H2<br>CCAP2H2<br>CCAP3H2                   | CCAP1H1<br>CCAP2H1<br>CCAP3H1                   | CCAP1H0<br>CCAP2H0<br>CCAP3H0                        |

| CCAP4H                                                   | FEh                                    | PCA Compare Capture Module 4 H                                                                                                                                             | CCAP4H7                                  | CCAP4H6                                              | CCAP4H5                                              | CCAP4H4                                              | CCAP4H3                                         | CCAP4H2                                         | CCAP4H1                                         | CCAP4H0                                              |

| CCAP0L<br>CCAP1L<br>CCAP2L<br>CCAP3L                     | EAh<br>EBh<br>ECh<br>EDh               | PCA Compare Capture Module 0 L<br>PCA Compare Capture Module 1 L<br>PCA Compare Capture Module 2 L<br>PCA Compare Capture Module 3 L                                       | CCAP0L7<br>CCAP1L7<br>CCAP2L7<br>CCAP3L7 | CCAP0L6<br>CCAP1L6<br>CCAP2L6<br>CCAP3L6             | CCAP0L5<br>CCAP1L5<br>CCAP2L5<br>CCAP3L5             | CCAP0L4<br>CCAP1L4<br>CCAP2L4<br>CCAP3L4             | CCAP0L3<br>CCAP1L3<br>CCAP2L3<br>CCAP3L3        | CCAP0L2<br>CCAP1L2<br>CCAP2L2<br>CCAP3L2        | CCAP0L1<br>CCAP1L1<br>CCAP2L1<br>CCAP3L1        | CCAP0L0<br>CCAP1L0<br>CCAP2L0<br>CCAP3L0             |

| CCAP4L                                                   | EEh                                    | PCA Compare Capture Module 4 L                                                                                                                                             | CCAP4L7                                  | CCAP4L6                                              | CCAP4L5                                              | CCAP4L4                                              | CCAP4L3                                         | CCAP4L2                                         | CCAP4L1                                         | CCAP4L0                                              |

### Table 9. Serial I/O Port SFRs

| Mnemonic | Add | Name               | 7      | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|----------|-----|--------------------|--------|-----|-----|-----|------|------|-----|-----|

| SCON     | 98h | Serial Control     | FE/SM0 | SM1 | SM2 | REN | TB8  | RB8  | ТІ  | RI  |

| SBUF     | 99h | Serial Data Buffer |        |     |     |     |      |      |     |     |

| SADEN    | B9h | Slave Address Mask |        |     |     |     |      |      |     |     |

| SADDR    | A9h | Slave Address      |        |     |     |     |      |      |     |     |

| BDRCON   | 9Bh | Baud Rate Control  |        |     |     | BRR | TBCK | RBCK | SPD | SRC |

| BRL      | 9Ah | Baud Rate Reload   |        |     |     |     |      |      |     |     |

#### Table 10. SPI Controller SFRs

| Mnemonic | Add | Name        | 7    | 6    | 5     | 4    | 3    | 2    | 1    | 0    |

|----------|-----|-------------|------|------|-------|------|------|------|------|------|

| SPCON    | C3h | SPI Control | SPR2 | SPEN | SSDIS | MSTR | CPOL | CPHA | SPR1 | SPR0 |

| SPSTA    | C4h | SPI Status  | SPIF | WCOL | SSERR | MODF | -    | -    | -    | -    |

| SPDAT    | C5h | SPI Data    | SPD7 | SPD6 | SPD5  | SPD4 | SPD3 | SPD2 | SPD1 | SPD0 |

#### Table 15. Pin Description (Continued)

|               | Pin N          | umber        | Tuno |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------------|----------------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mnemonic      | PLCC44         | VQFP44       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|               |                |              | I/O  | MOSI: SPI Master Output Slave Input line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|               |                |              |      | When SPI is in master mode, MOSI outputs data to the slave peripheral. When SPI is in slave mode, MOSI receives data from the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| XTALA1        | 21             | 15           | Ι    | Crystal A 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| XTALA2        | 20             | 14           | 0    | Crystal A 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| XTALB1        | 2              | 40           | I    | Crystal B 1: (Sub Clock) Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| XTALB2        | 1              | 39           | 0    | Crystal B 2: (Sub Clock) Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| P2.0 - P2.7   | 24 - 31        | 18 - 25      | I/O  | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. |  |  |  |  |

| P3.0 - P3.7   | 11,<br>13 - 19 | 5,<br>7 - 13 | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                     |  |  |  |  |

|               | 11             | 5            | I    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|               | 13             | 7            | 0    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|               | 14             | 8            | I    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|               | 15             | 9            | I    | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|               | 16             | 10           | I    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|               | 17             | 11           | I    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|               | 18             | 12           | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|               | 19             | 13           | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| P4.0 - P4.7   | -              | -            | I/O  | <b>Port 4:</b> Port 4 is an 8-bit bidirectional I/O port with internal pull-ups. Port 5 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 4 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| P5.0 - P5.7   | -              | -            | I/O  | <b>Port 5:</b> Port 5 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 5 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Pl2.0 - Pl2.1 | 34, 12         | 28, 6        |      | <b>Port 12:</b> Port 12 is an open drain. It can be used as inputs (must be polarized to Vcc with external resistor to prevent any parasitic current consumption).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|               | 34             | 28           | I/O  | SCL (PI2.0): 2-wire Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|               |                |              |      | SCL output the serial clock to slave peripherals<br>SCL input the serial clock from master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

## Table 19. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                                                                              | 4                                                                                                                    | 3                                | 2               | 1            | 0           |

|---------------|-----------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|--------------|-------------|

| SMOD1         | SMOD0           | -                                                                                              | POF                                                                                                                  | GF1                              | GF0             | PD           | IDL         |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                    |                                                                                                                      |                                  |                 |              |             |

| 7             | SMOD1           | Serial port N<br>Set to select                                                                 |                                                                                                                      | rate in mode 1                   | l, 2 or 3.      |              |             |

| 6             | SMOD0           |                                                                                                |                                                                                                                      | in SCON regis<br>DN register.    | ster.           |              |             |

| 5             | -               | Reserved<br>The value re                                                                       | ad from this b                                                                                                       | it is indetermi                  | nate. Do not se | et this bit. |             |

| 4             | POF             |                                                                                                | cognize next                                                                                                         |                                  | to its nominal  | voltage. Can | also be set |

| 3             | GF1             |                                                                                                | oftware for ge                                                                                                       | eneral purpose<br>al purpose usa |                 |              |             |

| 2             | GF0             | Cleared by s                                                                                   | General purpose Flag<br>Cleared by software for general purpose usage.<br>Set by software for general purpose usage. |                                  |                 |              |             |

| 1             | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode. |                                                                                                                      |                                  |                 |              |             |

| 0             | IDL             | Idle mode b<br>Cleared by h<br>Set to enter                                                    | ardware whe                                                                                                          | n interrupt or r                 | eset occurs.    |              |             |

Reset Value = 00X1 0000b Not bit addressable

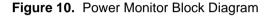

## **Power Monitor**

The POR/PFD function monitors the internal power-supply of the CPU core memories and the peripherals, and if needed, suspends their activity when the internal power supply falls below a safety threshold. This is achieved by applying an internal reset to them.

By generating the Reset the Power Monitor insures a correct start up when AT89C51ID2 is powered up.

**Description** In order to startup and maintain the microcontroller in correct operating mode, V<sub>CC</sub> has to be stabilized in the V<sub>CC</sub> operating range and the oscillator has to be stabilized with a nominal amplitude compatible with logic level VIH/VIL.

These parameters are controlled during the three phases: power-up, normal operation and power going down. See Figure 10.

Note: 1. Once XTAL1 High and low levels reach above and below VIH/VIL. a 1024 clock period delay will extend the reset coming from the Power Fail Detect. If the power falls below the Power Fail Detect threshold level, the Reset will be applied immediately.

The Voltage regulator generates a regulated internal supply for the CPU core the memories and the peripherals. Spikes on the external Vcc are smoothed by the voltage regulator.

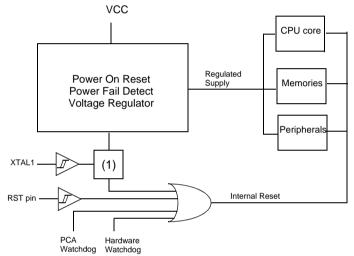

| Timer 2          | The Timer 2 in the AT89C51ID2 is the standard C52 Timer 2.<br>It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2 are cascaded. It is controlled by T2CON (Table 25) and T2MOD (Table 26) registers. Timer 2 operation is similar to Timer 0 and Timer 1.C/T2 selects $F_{OSC}/12$ (timer operation) or external pin T2 (counter operation) as the timer clock input. Setting TR2 allows TL2 to increment by the selected input. |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Timer 2 has 3 operating modes: capture, autoreload and Baud Rate Generator. These modes are selected by the combination of RCLK, TCLK and CP/RL2 (T2CON).                                                                                                                                                                                                                                                                                                                        |

|                  | Refer to the Atmel 8-bit Microcontroller Hardware description for the description of Cap-<br>ture and Baud Rate Generator Modes.                                                                                                                                                                                                                                                                                                                                                 |

|                  | Timer 2 includes the following enhancements:                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                  | Auto-reload mode with up or down counter                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  | Programmable clock-output                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Auto-Reload Mode | The auto-reload mode configures Timer 2 as a 16-bit timer or event counter with auto-<br>matic reload. If DCEN bit in T2MOD is cleared, Timer 2 behaves as in 80C52 (refer to<br>the Atmel C51 Microcontroller Hardware description). If DCEN bit is set, Timer 2 acts as<br>an Up/down timer/counter as shown in Figure 12. In this mode the T2EX pin controls the<br>direction of count.                                                                                       |

|                  | When T2EX is high, Timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.                                                                                                                                                                                                                     |

|                  | When T2EX is low, Timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.                                                                                                                                                                                                                                  |

|                  | The EXF2 bit toggles when Timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.                                                                                                                                                                                                                                                                                      |

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn | Module Function                                   |

|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | No Operation                                      |

| x     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigger on CEXn |

| х     | 0     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a negative trigger on CEXn      |

| х     | 1     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a transition on CEXn            |

| 1     | 0     | 0     | 1    | 0    | 0    | х     | 16-bit Software Timer / Compare mode.             |

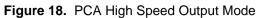

| 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

| 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer (module 4 only)                    |

Table 30. PCA Module Modes (CCAPMn Registers)

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output (See Table 31 & Table 32).

**Table 31.** CCAPnH Registers (n = 0-4)

CCAP0H - PCA Module 0 Compare/Capture Control Register High (0FAh)

CCAP1H - PCA Module 1 Compare/Capture Control Register High (0FBh)

CCAP2H - PCA Module 2 Compare/Capture Control Register High (0FCh)

CCAP3H - PCA Module 3 Compare/Capture Control Register High (0FDh)

CCAP4H - PCA Module 4 Compare/Capture Control Register High (0FEh)

| 7             | 6               | 5                        | 4 | 3           | 2    | 1 | 0 |

|---------------|-----------------|--------------------------|---|-------------|------|---|---|

| -             | -               | -                        | - | -           | -    | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |             |      |   |   |

| 7-0           | -               | PCA Module<br>CCAPnH Val |   | Capture Con | trol |   |   |

Reset Value = 0000 0000b Not bit addressable

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

**Pulse Width Modulator** Mode All of the PCA modules can be used as PWM outputs. Figure 19 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. This allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

|                                  | Figure 22. UART Timings in                                                                                                                                                                                                                                                                               | n Modes 2 and 3                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |

|                                  | Start bit                                                                                                                                                                                                                                                                                                | Data byte                                                                                                                                                                                                                                                                                 | Ninth <sup>I</sup> Stop<br>bit bit                                                                                                                                  |

|                                  | RI<br>SMOD0=0                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |

|                                  | RI<br>SMOD0=1                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |

|                                  | FESMOD0=1                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |

| Automatic Address<br>Recognition | nication feature is enabled (<br>Implemented in hardware, a<br>communication feature by<br>incoming command frame.<br>receiver sets RI bit in SCON<br>is not interrupted by comma<br>If desired, the user may ena<br>this configuration, the stop b<br>the received command fram<br>by a valid stop bit. | SM2 bit in SCON register is<br>automatic address recogniti<br>allowing the serial port to<br>Only when the serial port of<br>I register to generate an inte<br>and frames addressed to oth<br>able the automatic address<br>bit takes the place of the nint<br>ne address matches the dev | ion enhances the multiprocessor<br>o examine the address of each<br>recognizes its own address, the<br>errupt. This ensures that the CPU                            |

|                                  |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                           | address recognition features cannot register in mode 0 has no effect).                                                                                              |

| Given Address                    | register is a mask byte tha<br>device's given address. The<br>slaves at a time. The followi                                                                                                                                                                                                              | at contains don't-care bits<br>don't-care bits provide the<br>ng example illustrates how                                                                                                                                                                                                  | a in SADDR register; the SADEN<br>(defined by zeros) to form the<br>flexibility to address one or more<br>a given address is formed.<br>ADEN mask byte must be 1111 |

|                                  | The following is an example<br>Slave A:SADDR1111 0001b<br><u>SADEN1111 1010b</u><br>Given1111 0X0Xb                                                                                                                                                                                                      | of how to use given addres                                                                                                                                                                                                                                                                | sses to address different slaves:                                                                                                                                   |

|                                  | Slave B:SADDR1111 0011b<br><u>SADEN1111 1001b</u><br>Given1111 0XX1b                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |

|                                  | Slave C:SADDR1111 0010b<br><u>SADEN1111 1101b</u><br>Given1111 00X1b                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                     |

## Interrupt Sources and Vector Addresses

| Table 56. Ir | nterrupt Sources and Vector Addresses |

|--------------|---------------------------------------|

|--------------|---------------------------------------|

| Number | Polling Priority | Interrupt Source | Interrupt<br>Request | Vector<br>Address |

|--------|------------------|------------------|----------------------|-------------------|

| 0      | 0                | Reset            |                      | 0000h             |

| 1      | 1                | INT0             | IE0                  | 0003h             |

| 2      | 2                | Timer 0          | TF0                  | 000Bh             |

| 3      | 3                | INT1             | IE1                  | 0013h             |

| 4      | 4                | Timer 1          | IF1                  | 001Bh             |

| 5      | 6                | UART             | RI+TI                | 0023h             |

| 6      | 7                | Timer 2          | TF2+EXF2             | 002Bh             |

| 7      | 5                | PCA              | CF + CCFn (n = 0-4)  | 0033h             |

| 8      | 8                | Keyboard         | KBDIT                | 003Bh             |

| 9      | 9                | TWI              | тwііт                | 0043h             |

| 9      | 9                | SPI              | SPIIT                | 004Bh             |

## Description

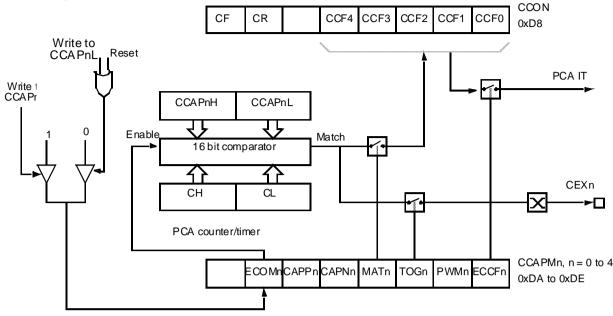

The CPU interfaces to the 2-wire logic via the following four 8-bit special function registers: the Synchronous Serial Control register (SSCON; Table 71), the Synchronous Serial Data register (SSDAT; Table 72), the Synchronous Serial Control and Status register (SSCS; Table 73) and the Synchronous Serial Address register (SSADR Table 76).

SSCON is used to enable the TWI interface, to program the bit rate (see Table 64), to enable slave modes, to acknowledge or not a received data, to send a START or a STOP condition on the 2-wire bus, and to acknowledge a serial interrupt. A hardware reset disables the TWI module.

SSCS contains a status code which reflects the status of the 2-wire logic and the 2-wire bus. The three least significant bits are always zero. The five most significant bits contains the status code. There are 26 possible status codes. When SSCS contains F8h, no relevant state information is available and no serial interrupt is requested. A valid status code is available in SSCS one machine cycle after SI is set by hardware and is still present one machine cycle after SI has been reset by software. to Table 70. give the status for the master modes and miscellaneous states.

SSDAT contains a byte of serial data to be transmitted or a byte which has just been received. It is addressable while it is not in process of shifting a byte. This occurs when 2-wire logic is in a defined state and the serial interrupt flag is set. Data in SSDAT remains stable as long as SI is set. While data is being shifted out, data on the bus is simultaneously shifted in; SSDAT always contains the last byte present on the bus.

SSADR may be loaded with the 7-bit slave address (7 most significant bits) to which the TWI module will respond when programmed as a slave transmitter or receiver. The LSB is used to enable general call address (00h) recognition.

Figure 31 shows how a data transfer is accomplished on the 2-wire bus.

Figure 31. Complete Data Transfer on 2-wire Bus

The four operating modes are:

- Master Transmitter

- Master Receiver

- Slave transmitter

- Slave receiver

Data transfer in each mode of operation is shown in Table to Table 70 and Figure 32. to Figure 35.. These figures contain the following abbreviations:

- S : START condition

- R : Read bit (high level at SDA)

| B |

|---|

| Table 68. Status | s in Slave | <b>Receiver Mode</b> |

|------------------|------------|----------------------|

|------------------|------------|----------------------|

|                |                                                                    | Application S      | Software | e Respo | nse |    |                                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------|--------------------|----------|---------|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status         |                                                                    | To/from SSDAT      |          | To SS   | CON |    |                                                                                                                                                                                      |

| Code<br>(SSCS) | Status of the 2-wire bus and<br>2-wire hardware                    |                    | STA      | ѕто     | SI  | АА | Next Action Taken By 2-wire Software                                                                                                                                                 |

| 60h            | Own SLA+W has been received: ACK has been                          | No SSDAT action or | х        | 0       | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 0011           | returned                                                           | No SSDAT action    | х        | 0       | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

| COL            | Arbitration lost in SLA+R/W as master; own SLA+W has been          | No SSDAT action or | х        | 0       | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 68h            | received; ACK has been<br>returned                                 | No SSDAT action    | х        | 0       | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

| 701            | General call address has been                                      | No SSDAT action or | х        | 0       | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 70h            | received; ACK has been<br>returned                                 | No SSDAT action    | х        | 0       | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

| 701            | Arbitration lost in SLA+R/W as master; general call address        | No SSDAT action or | х        | 0       | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 78h            | has been received; ACK has<br>been returned                        | No SSDAT action    | х        | 0       | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

| 0.01           | Previously addressed with own SLA+W; data has been                 | No SSDAT action or | х        | 0       | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 80h            | received; ACK has been returned                                    | No SSDAT action    | х        | 0       | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

|                |                                                                    | Read data byte or  | 0        | 0       | 0   | 0  | Switched to the not addressed slave mode; no recognition of own SLA or GCA                                                                                                           |

|                |                                                                    | Read data byte or  | 0        | 0       | 0   | 1  | Switched to the not addressed slave mode; own SLA will be recognised; GCA will be recognised if                                                                                      |

|                | Previously addressed with                                          | Read data byte of  | Ŭ        | 0       | Ū   |    | GC=logic 1<br>Switched to the not addressed slave mode; no                                                                                                                           |

| 88h            | own SLA+W; data has been<br>received; NOT ACK has been<br>returned | Read data byte or  | 1        | 0       | 0   | 0  | recognition of own SLA or GCA. A START<br>condition will be transmitted when the bus<br>becomes free                                                                                 |

|                |                                                                    | Read data byte     | 1        | 0       | 0   | 1  | Switched to the not addressed slave mode; own<br>SLA will be recognised; GCA will be recognised if<br>GC=logic 1. A START condition will be<br>transmitted when the bus becomes free |

| 0.01           | Previously addressed with general call; data has been              | Read data byte or  | х        | 0       | 0   | 0  | Data byte will be received and NOT ACK will be returned                                                                                                                              |

| 90h            | received; ACK has been returned                                    | Read data byte     | х        | 0       | 0   | 1  | Data byte will be received and ACK will be returned                                                                                                                                  |

| Bit<br>Number | Bit<br>Mnemonic | Description                        |

|---------------|-----------------|------------------------------------|

| 1             | SD1             | Address bit 1 or Data bit 1.       |

| 0             | SD0             | Address bit 0 (R/W) or Data bit 0. |

Table 73. SSCS (094h) read - Synchronous Serial Control and Status Register

| 7   | 6   | 5   | 4   | 3   | 2 | 1 | 0 |

|-----|-----|-----|-----|-----|---|---|---|

| SC4 | SC3 | SC2 | SC1 | SC0 | 0 | 0 | 0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                           |

|---------------|-----------------|---------------------------------------|

| 0             | 0               | Always zero                           |

| 1             | 0               | Always zero                           |

| 2             | 0               | Always zero                           |

| 3             | SC0             | Status Code bit 0<br>See to Table 70. |

| 4             | SC1             | Status Code bit 1<br>See to Table 70. |

| 5             | SC2             | Status Code bit 2<br>See to Table 70. |

| 6             | SC3             | Status Code bit 3<br>See to Table 70. |

| 7             | SC4             | Status Code bit 4<br>See to Table 70. |

#### Table 74. SSCS Register: Read Mode - Reset Value = F8h

Table 75. SSADR (096h) - Synchronus Serial Address Register (read/write)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

#### **Table 76.** SSADR Register - Reset value = FEh

| Bit<br>Number | Bit<br>Mnemonic | Description         |

|---------------|-----------------|---------------------|

| 7             | A7              | Slave Address bit 7 |

| 6             | A6              | Slave Address bit 6 |

| 5             | A5              | Slave Address bit 5 |

| 4             | A4              | Slave Address bit 4 |

| 3             | A3              | Slave Address bit 3 |

| 2             | A2              | Slave Address bit 2 |

| 1             | A1              | Slave Address bit 1 |

# Serial Port Interface (SPI)

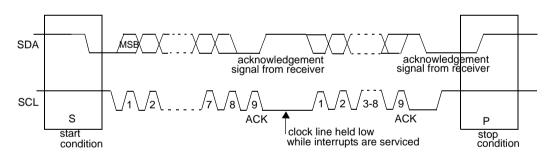

The Serial Peripheral Interface Module (SPI) allows full-duplex, synchronous, serial communication between the MCU and peripheral devices, including other MCUs.

Features

Features of the SPI Module include the following:

- Full-duplex, three-wire synchronous transfers

- Master or Slave operation

- Eight programmable Master clock rates

- Serial clock with programmable polarity and phase

- Master Mode fault error flag with MCU interrupt capability

- Write collision flag protection

Signal DescriptionFigure 36 shows a typical SPI bus configuration using one Master controller and many<br/>Slave peripherals. The bus is made of three wires connecting all the devices.

Figure 36. SPI Master/Slaves Interconnection

The Master device selects the individual Slave devices by using four pins of a parallel port to control the four  $\overline{SS}$  pins of the Slave devices.

Master Output Slave Input<br/>(MOSI)This 1-bit signal is directly connected between the Master Device and a Slave Device.<br/>The MOSI line is used to transfer data in series from the Master to the Slave. Therefore,<br/>it is an output signal from the Master, and an input signal to a Slave. A Byte (8-bit word)<br/>is transmitted most significant bit (MSB) first, least significant bit (LSB) last.

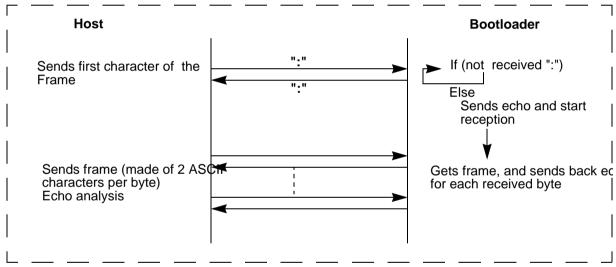

Master Input Slave Output<br/>(MISO)This 1-bit signal is directly connected between the Slave Device and a Master Device.<br/>The MISO line is used to transfer data in series from the Slave to the Master. Therefore,<br/>it is an output signal from the Slave, and an input signal to the Master. A Byte (8-bit<br/>word) is transmitted most significant bit (MSB) first, least significant bit (LSB) last.