#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status     Obsolete       Core Processor     80C51       Core Size     8-Bit    |  |

|-----------------------------------------------------------------------------------------|--|

|                                                                                         |  |

| Core Size 8-Bit                                                                         |  |

|                                                                                         |  |

| Speed 60MHz                                                                             |  |

| Connectivity I <sup>2</sup> C, SPI, UART/USART                                          |  |

| Peripherals POR, PWM, WDT                                                               |  |

| Number of I/O 34                                                                        |  |

| Program Memory Size 64KB (64K x 8)                                                      |  |

| Program Memory Type FLASH                                                               |  |

| EEPROM Size 2K x 8                                                                      |  |

| RAM Size 2K x 8                                                                         |  |

| Voltage - Supply (Vcc/Vdd) 2.7V ~ 5.5V                                                  |  |

| Data Converters -                                                                       |  |

| Oscillator Type External                                                                |  |

| Operating Temperature -40°C ~ 85°C (TA)                                                 |  |

| Mounting Type Surface Mount                                                             |  |

| Package / Case 44-LQFP                                                                  |  |

| Supplier Device Package44-VQFP (10x10)                                                  |  |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/at89c51id2-rlrum |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

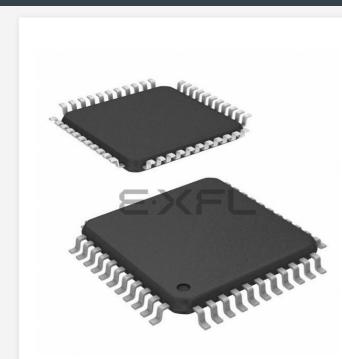

# Functional Block Diagram

## Figure 2. Functional Oscillator Block Diagram

# **Operating Modes**

#### Reset

A hardware RESET puts the Clock generator in the following state:

The selected oscillator depends on OSC bit in Hardware Security Byte (HSB).

HSB.OSC = 1 (Oscillator A selected)

- OscAEn = 1 & OscBEn = 0: OscA is running, OscB is stopped.

- CKS = 1: OscA is selected for CPU.

HSB.OSC = 0 (Oscillator B selected)

- OscAEn = 0 & OscBEn = 1: OscB is running, OscA is stopped.

- CKS = 0: OscB is selected for CPU.

## **Functional Modes**

Normal Modes

- CPU and Peripherals clock depend on the software selection using CKCON0, CKCON1 and CKRL registers

- CKS bit in CKSEL register selects either OscA or OscB

- CKRL register determines the frequency of the OscA clock.

- It is always possible to switch dynamically by software from OscA to OscB, and vice versa by changing CKS bit.

# 17 AT89C51ID2

# Enhanced Features In comparison to the

In comparison to the original 80C52, the AT89C51ID2 implements some new features, which are:

- X2 option

- Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- Hardware Watchdog

- SPI interface

- 4-level interrupt priority system

- power-off flag

- ONCE mode

- ALE disabling

- Enhanced features on the UART and the timer 2

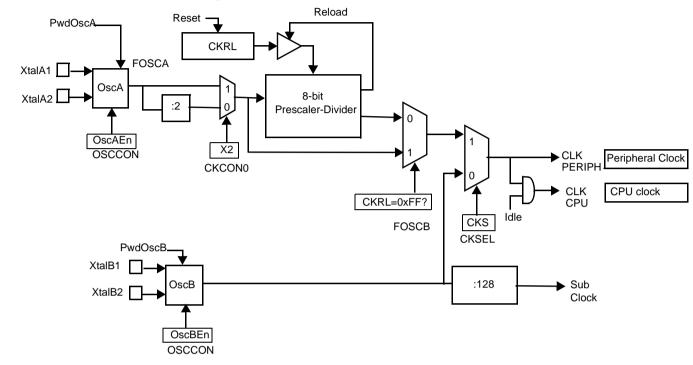

X2 Feature

Description

- The AT89C51ID2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

Figure 3 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1÷2 to avoid glitches when switching from X2 to STD mode. Figure 4 shows the switching mode waveforms.

Figure 3. Clock Generation Diagram

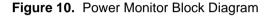

# **Power Monitor**

The POR/PFD function monitors the internal power-supply of the CPU core memories and the peripherals, and if needed, suspends their activity when the internal power supply falls below a safety threshold. This is achieved by applying an internal reset to them.

By generating the Reset the Power Monitor insures a correct start up when AT89C51ID2 is powered up.

**Description** In order to startup and maintain the microcontroller in correct operating mode, V<sub>CC</sub> has to be stabilized in the V<sub>CC</sub> operating range and the oscillator has to be stabilized with a nominal amplitude compatible with logic level VIH/VIL.

These parameters are controlled during the three phases: power-up, normal operation and power going down. See Figure 10.

Note: 1. Once XTAL1 High and low levels reach above and below VIH/VIL. a 1024 clock period delay will extend the reset coming from the Power Fail Detect. If the power falls below the Power Fail Detect threshold level, the Reset will be applied immediately.

The Voltage regulator generates a regulated internal supply for the CPU core the memories and the peripherals. Spikes on the external Vcc are smoothed by the voltage regulator.

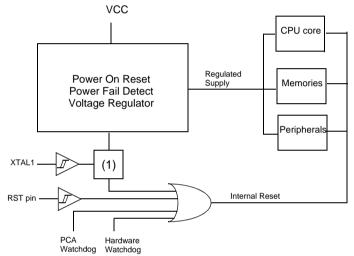

(UP COUNTING RELOAD VALUE)

# Programmable Clock-Output

In the clock-out mode, Timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 13). The input clock increments TL2 at frequency  $F_{CLK PERIPH}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$Clock-OutFrequency = \frac{F_{CLKPERIPH}}{4 \times (65536 - RCAP2H/RCAP2L)}$

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz  $(F_{CLK PERIPH}/2^{16})$  to 4 MHz  $(F_{CLK PERIPH}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2.It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn | Module Function                                   |

|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | No Operation                                      |

| x     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigger on CEXn |

| х     | 0     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a negative trigger on CEXn      |

| х     | 1     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a transition on CEXn            |

| 1     | 0     | 0     | 1    | 0    | 0    | х     | 16-bit Software Timer / Compare mode.             |

| 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

| 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer (module 4 only)                    |

Table 30. PCA Module Modes (CCAPMn Registers)

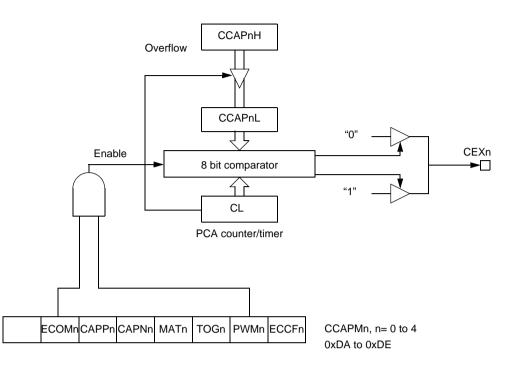

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output (See Table 31 & Table 32).

**Table 31.** CCAPnH Registers (n = 0-4)

CCAP0H - PCA Module 0 Compare/Capture Control Register High (0FAh)

CCAP1H - PCA Module 1 Compare/Capture Control Register High (0FBh)

CCAP2H - PCA Module 2 Compare/Capture Control Register High (0FCh)

CCAP3H - PCA Module 3 Compare/Capture Control Register High (0FDh)

CCAP4H - PCA Module 4 Compare/Capture Control Register High (0FEh)

| 7             | 6               | 5                        | 4 | 3           | 2    | 1 | 0 |

|---------------|-----------------|--------------------------|---|-------------|------|---|---|

| -             | -               | -                        | - | -           | -    | - | - |

| Bit<br>Number | Bit<br>Mnemonic | Description              |   |             |      |   |   |

| 7-0           | -               | PCA Module<br>CCAPnH Val |   | Capture Con | trol |   |   |

Reset Value = 0000 0000b Not bit addressable

Figure 19. PCA PWM Mode

**PCA Watchdog Timer** An on-board watchdog timer is available with the PCA to improve the reliability of the system without increasing chip count. Watchdog timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. Module 4 is the only PCA module that can be programmed as a watchdog. However, this module can still be used for other modes if the watchdog is not needed. Figure 17 shows a diagram of how the watchdog works. The user pre-loads a 16-bit value in the compare registers. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

1. periodically change the compare value so it will never match the PCA timer,

2. periodically change the PCA timer value so it will never match the compare values, or

3. disable the watchdog by clearing the WDTE bit before a match occurs and then reenable it.

The first two options are more reliable because the watchdog timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most applications the first solution is the best option.

This watchdog timer won't generate a reset out on the reset pin.

# Table 50. IPL0 Register

IPL0 - Interrupt Priority Register (B8h)

| 7             | 6               | 5                             | 4                                                                            | 3                                | 2              | 1            | 0    |  |

|---------------|-----------------|-------------------------------|------------------------------------------------------------------------------|----------------------------------|----------------|--------------|------|--|

| -             | PPCL            | PT2L                          | PSL                                                                          | PT1L                             | PX1L           | PTOL         | PX0L |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                   | Description                                                                  |                                  |                |              |      |  |

| 7             | -               | Reserved<br>The value re      | ad from this t                                                               | oit is indetermi                 | nate. Do not s | et this bit. |      |  |

| 6             | PPCL            |                               | <b>pt Priority bi</b><br>CH for priority                                     |                                  |                |              |      |  |

| 5             | PT2L            |                               | <b>rflow interru</b><br>H for priority                                       | <b>pt Priority bit</b><br>level. |                |              |      |  |

| 4             | PSL             | Serial port I<br>Refer to PSI | Priority bit<br>I for priority le                                            | evel.                            |                |              |      |  |

| 3             | PT1L            |                               | <b>rflow interru</b><br>H for priority                                       | <b>pt Priority bit</b><br>level. |                |              |      |  |

| 2             | PX1L            |                               | External interrupt 1 Priority bit<br>Refer to PX1H for priority level.       |                                  |                |              |      |  |

| 1             | PTOL            |                               | Timer 0 overflow interrupt Priority bit<br>Refer to PT0H for priority level. |                                  |                |              |      |  |

| 0             | PX0L            |                               | errupt 0 Prio<br>)H for priority                                             |                                  |                |              |      |  |

Reset Value = X000 0000b Bit addressable

AT89C51ID2

## Table 51. IPH0 Register

IPH0 - Interrupt Priority High Register (B7h)

| 7             | 6               | 5                                                                                                                                    | 4                                                                                                   | 3               | 2      | 1    | 0    |  |  |

|---------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------|--------|------|------|--|--|

| -             | PPCH            | PT2H                                                                                                                                 | PSH                                                                                                 | PT1H            | PX1H   | PT0H | PX0H |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                          | Description                                                                                         |                 |        |      |      |  |  |

| 7             | -               | <b>Reserved</b><br>The value re                                                                                                      | eserved<br>he value read from this bit is indeterminate. Do not set this bit.                       |                 |        |      |      |  |  |

| 6             | РРСН            |                                                                                                                                      |                                                                                                     | gh bit.         |        |      |      |  |  |

| 5             | PT2H            | PT2HPT2LP                                                                                                                            | imer 2 overflow interrupt Priority High bit<br><u>T2HPT2LPriority Level</u><br>0Lowest<br>1<br>0    |                 |        |      |      |  |  |

| 4             | PSH             | PSH PSLPri<br>0 0Lowest<br>0 1<br>1 0                                                                                                | 0 1<br>1 0                                                                                          |                 |        |      |      |  |  |

| 3             | PT1H            | PT1HPT1L F                                                                                                                           | Timer 1 overflow interrupt Priority High bit<br>PT1HPT1L Priority Level<br>0 0 Lowest<br>0 1<br>1 0 |                 |        |      |      |  |  |

| 2             | PX1H            | PX1HPX1LF<br>0 0Lowest<br>0 1<br>1 0                                                                                                 | External interrupt 1 Priority High bit<br><u>PX1HPX1LPriority Level</u><br>0 0Lowest<br>0 1<br>1 0  |                 |        |      |      |  |  |

| 1             | РТОН            | Timer 0 ove           PT0HPT0LP           0         0Lowest           0         1           1         0           1         1Highest | riority Level                                                                                       | pt Priority Hig | gh bit |      |      |  |  |

| 0             | РХОН            |                                                                                                                                      |                                                                                                     | rity High bit   |        |      |      |  |  |

Reset Value = X000 0000b Not bit addressable

and RAM contents are preserved. The status of the Port pins during Power-Down mode is detailed in Table 57.

Note: VCC may be reduced to as low as V<sub>RET</sub> during Power-Down mode to further reduce power dissipation. Take care, however, that VDD is not reduced until Power-Down mode is invoked.

**Entering Power-Down Mode** To enter Power-Down mode, set PD bit in PCON register. The AT89C51ID2 enters the Power-Down mode upon execution of the instruction that sets PD bit. The instruction that sets PD bit is the last instruction executed.

#### Exiting Power-Down Mode

Note: If VCC was reduced during the Power-Down mode, do not exit Power-Down mode until VCC is restored to the normal operating level.

There are two ways to exit the Power-Down mode:

- 1. Generate an enabled external interrupt.

- The AT89C51ID2 provides capability to exit from Power-Down using INT0#, INT1#.

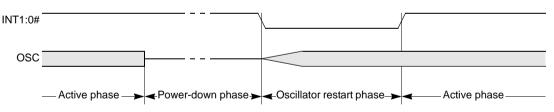

Hardware clears PD bit in PCON register which starts the oscillator and restores the clocks to the CPU and peripherals. Using INTx# input, execution resumes when the input is released (see Figure 26). Execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the instruction that activated Power-Down mode.

- Note: The external interrupt used to exit Power-Down mode must be configured as level sensitive (INT0# and INT1#) and must be assigned the highest priority. In addition, the duration of the interrupt must be long enough to allow the oscillator to stabilize. The execution will only resume when the interrupt is deasserted.

- Note: Exit from power-down by external interrupt does not affect the SFRs nor the internal RAM content.

#### Figure 26. Power-Down Exit Waveform Using INT1:0#

#### 2. Generate a reset.

- A logic high on the RST pin clears PD bit in PCON register directly and asynchronously. This starts the oscillator and restores the clock to the CPU and peripherals. Program execution momentarily resumes with the instruction immediately following the instruction that activated Power-Down mode and may continue for a number of clock cycles before the internal reset algorithm takes control. Reset initializes the AT89C51ID2 and vectors the CPU to address 0000h.

- Note: During the time that execution resumes, the internal RAM cannot be accessed; however, it is possible for the Port pins to be accessed. To avoid unexpected outputs at the Port

pins, the instruction immediately following the instruction that activated the Power-Down mode should not write to a Port pin or to the external RAM.

Note: Exit from power-down by reset redefines all the SFRs, but does not affect the internal RAM content.

| Mode                                 | Port 0 Port 1 Port 2 Port 3 Port 4        |              | Port 4 | ALE  | PSEN# |      |      |

|--------------------------------------|-------------------------------------------|--------------|--------|------|-------|------|------|

| Reset                                | Floating                                  | High         | High   | High | High  | High | High |

| Idle<br>(internal<br>code)           | Data                                      | Data Data Da |        | Data | Data  | High | High |

| Idle<br>(external<br>code)           | Floating                                  | Data         | Data   | Data | Data  | High | High |

| Power-<br>Down(inter<br>nal code)    | Data                                      | Data         | Data   | Data | Data  | Low  | Low  |

| Power-<br>Down<br>(external<br>code) | ower-<br>own<br>ternal Floating Data Data |              | Data   | Data | Low   | Low  |      |

Table 57. Pin Conditions in Special Operating Modes

# **Keyboard Interface**

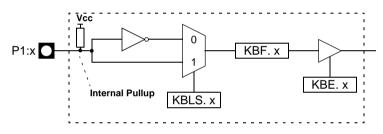

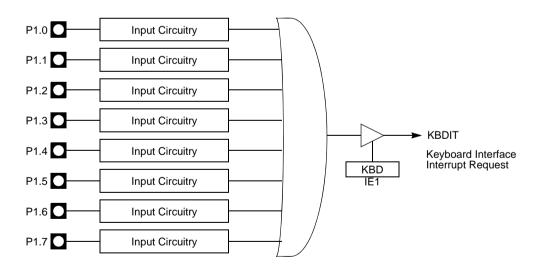

The AT89C51ID2 implements a keyboard interface allowing the connection of a 8 x n matrix keyboard. It is based on 8 inputs with programmable interrupt capability on both high or low level. These inputs are available as alternate function of P1 and allow to exit from idle and power down modes.

The keyboard interface interfaces with the C51 core through 3 special function registers: KBLS, the Keyboard Level Selection register (Table 61), KBE, The Keyboard interrupt Enable register (Table 60), and KBF, the Keyboard Flag register (Table 59).

Interrupt

The keyboard inputs are considered as 8 independent interrupt sources sharing the same interrupt vector. An interrupt enable bit (KBD in IE1) allows global enable or disable of the keyboard interrupt (see Figure 27). As detailed in Figure 28 each keyboard input has the capability to detect a programmable level according to KBLS. x bit value. Level detection is then reported in interrupt flags KBF. x that can be masked by software using KBE. x bits.

This structure allow keyboard arrangement from 1 by n to 8 by n matrix and allow usage of P1 inputs for other purpose.

Figure 27. Keyboard Interface Block Diagram

#### **Power Reduction Mode**

P1 inputs allow exit from idle and power down modes as detailed in Section "Power Management", page 72.

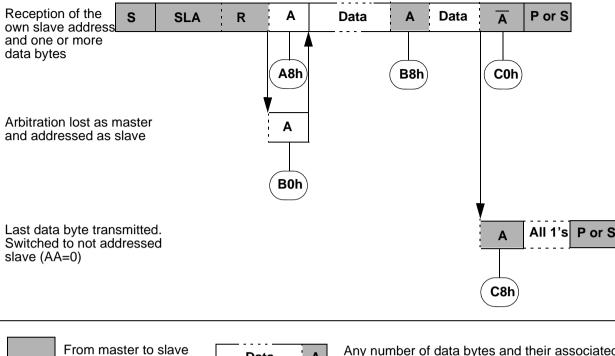

## Figure 35. Format and State in the Slave Transmitter Mode

#### Table 69. Status in Slave Transmitter Mode

|                |                                                           | Application S     | Software Response |          |    |    |                                                                 |

|----------------|-----------------------------------------------------------|-------------------|-------------------|----------|----|----|-----------------------------------------------------------------|

| Status         |                                                           | To/from SSDAT     |                   | To SSCON |    |    |                                                                 |

| Code<br>(SSCS) | Status of the 2-wire bus and 2-wire hardware              |                   | STA               | ѕто      | SI | АА | Next Action Taken By 2-wire Software                            |

| AOL            | Own SLA+R has been                                        | Load data byte or | х                 | 0        | 0  | 0  | Last data byte will be transmitted and NOT ACK will be received |

| A8h            | received; ACK has been<br>returned                        | Load data byte    | х                 | 0        | 0  | 1  | Data byte will be transmitted and ACK will be received          |

| B0h            | Arbitration lost in SLA+R/W as master; own SLA+R has been | Load data byte or | х                 | 0        | 0  | 0  | Last data byte will be transmitted and NOT ACK will be received |

| BUII           | received; ACK has been returned                           | Load data byte    | х                 | 0        | 0  | 1  | Data byte will be transmitted and ACK will be received          |

| B8h            | Data byte in SSDAT has been                               | Load data byte or | х                 | 0        | 0  | 0  | Last data byte will be transmitted and NOT ACK will be received |

| DOII           | transmitted; NOT ACK has been received                    | Load data byte    | х                 | 0        | 0  | 1  | Data byte will be transmitted and ACK will be received          |

# AT89C51ID2

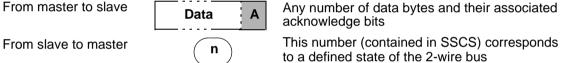

## Figure 42. SPI Interrupt Requests Generation

#### Registers

Serial Peripheral Control Register (SPCON) There are three registers in the Module that provide control, status and data storage functions. These registers are describes in the following paragraphs.

- The Serial Peripheral Control Register does the following:

- Selects one of the Master clock rates

- Configure the SPI Module as Master or Slave

- Selects serial clock polarity and phase

- Enables the SPI Module

- Frees the SS pin for a general-purpose

Table 79 describes this register and explains the use of each bit

#### Table 79. SPCON Register

SPCON - Serial Peripheral Control Register (0C3H)

Table 1.

| 7          | 6       | 5      | 4                                                                                                                                                                                                                                                                     | 3              | 2               | 1    | 0    |

|------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|------|------|

| SPR2       | SPEN    | SSDIS  | MSTR                                                                                                                                                                                                                                                                  | CPOL           | СРНА            | SPR1 | SPR0 |

| Bit Number | Bit Mne | emonic | Description                                                                                                                                                                                                                                                           |                |                 |      |      |

| 7          | SF      | PR2    | Serial Periphe<br>Bit with SPR1 a                                                                                                                                                                                                                                     |                | ine the clock r | ate. |      |

| 6          | SF      | PEN    | Serial Peripheral Enable<br>Cleared to disable the SPI interface.<br>Set to enable the SPI interface.                                                                                                                                                                 |                |                 |      |      |

| 5          | SS      | DIS    | <b>SS Disable</b><br>Cleared to enable $\overline{SS}$ in both Master and Slave modes.<br>Set to disable $\overline{SS}$ in both Master and Slave modes. In Slave<br>this bit has no effect if CPHA ='0'. When SSDIS is set, no Me<br>interrupt request is generated. |                |                 |      |      |

| 4          | MS      | STR    | Serial Periphe<br>Cleared to con<br>Set to configure                                                                                                                                                                                                                  | figure the SPI |                 |      |      |

| 3          | CPOL    |        | Clock Polarity                                                                                                                                                                                                                                                        |                |                 |      |      |

| 2          | CF      | РНА    | Clock Phase<br>Cleared to hav<br>state (see CPC<br>Set to have the<br>CPOL).                                                                                                                                                                                          | DL).           |                 |      |      |

# **Reduced EMI Mode**

The ALE signal is used to demultiplex address and data buses on port 0 when used with external program or data memory. Nevertheless, during internal code execution, ALE signal is still generated. In order to reduce EMI, ALE signal can be disabled by setting AO bit.

The AO bit is located in AUXR register at bit location 0. As soon as AO is set, ALE is no longer output but remains active during MOVX and MOVC instructions and external fetches. During ALE disabling, ALE pin is weakly pulled high.

#### Table 87. AUXR Register

AUXR - Auxiliary Register (8Eh)

| 7 | 6 | 5  | 4    | 3    | 2    | 1      | 0  |

|---|---|----|------|------|------|--------|----|

| - | - | MO | XRS2 | XRS1 | XRS0 | EXTRAM | AO |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                       |

| 6             | -               | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                                                       |

| 5             | МО              | Pulse length<br>Cleared to stretch MOVX control: the RD/ and the WR/ pulse length is 6 clock<br>periods (default).<br>Set to stretch MOVX control: the RD/ and the WR/ pulse length is 30 clock<br>periods.                  |

| 4             | XRS2            | XRAM Size                                                                                                                                                                                                                    |

| 3             | XRS1            | XRS2 XRS1XRS0XRAM size<br>0 0 0 256 bytes                                                                                                                                                                                    |

| 2             | XRS0            | 0 0 1 512 bytes<br>0 1 0 768 bytes(default)<br>0 1 1 1024 bytes<br>1 0 0 1792 bytes                                                                                                                                          |

| 1             | EXTRAM          | EXTRAM bit<br>Cleared to access internal XRAM using movx @ Ri/ @ DPTR.<br>Set to access external memory.<br>Programmed by hardware after Power-up regarding Hardware Security Byte<br>(HSB), default setting, XRAM selected. |

| 0             | AO              | ALE Output bit<br>Cleared, ALE is emitted at a constant rate of 1/6 the oscillator frequency (or 1/3 if<br>X2 mode is used). (default) Set, ALE is active only during a MOVX or MOVC<br>instruction is used.                 |

Reset Value = XX00 10'HSB. XRAM'0b Not bit addressable

| Table 93. | Program | Lock bits | of the SSB |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

| Program           | n Lock I | Bits |                                                                       |

|-------------------|----------|------|-----------------------------------------------------------------------|

| Security<br>level | LB0      | LB1  | Protection description                                                |

| 1                 | U        | U    | No program lock features enabled.                                     |

| 2                 | Р        | U    | ISP programming of the Flash is disabled.                             |

| 3                 | Х        | Р    | Same as 2, also verify through ISP programming interface is disabled. |

Note: U: unprogrammed or "one" level.

P: programmed or "zero" level.

X: do not care

WARNING: Security level 2 and 3 should only be programmed after Flash and code verification.

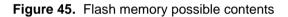

Flash Memory StatusAT89C51ID2 parts are delivered in standard with the ISP rom bootloader.

After ISP or parallel programming, the possible contents of the Flash memory are summarized on the figure below:

# **Memory Organization**

When the  $\overline{EA}$  pin high, the processor fetches instructions from internal program Flash. . If the  $\overline{EA}$  pin is tied low, all program memory fetches are from external memory.

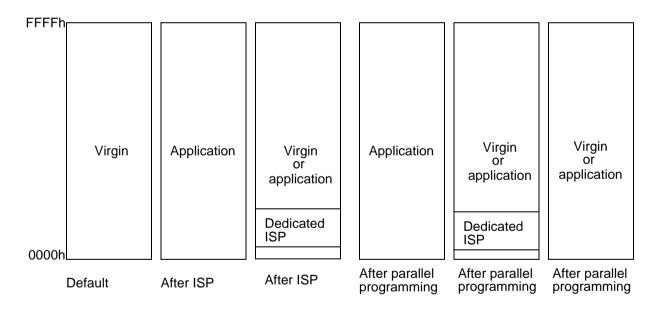

## **Boot Process**

# **ISP Protocol Description**

## **Physical Layer**

The UART used to transmit information has the following configuration:

- Character: 8-bit data

- Parity: none

- Stop: 2 bits

- Flow control: none

- Baudrate: autobaud is performed by the bootloader to compute the baudrate choosen by the host.

## Frame Description The Serial Protocol is based on the Intel Hex-type records.

Intel Hex records consist of ASCII characters used to represent hexadecimal values and are summarized below

#### Figure 50. Intel Hex Type Frame

| Record<br>Mark | Reclen | Load<br>Offset | Record<br>Type | Data<br>or<br>Info | Checksum |

|----------------|--------|----------------|----------------|--------------------|----------|

| 1-byte         | 1-byte | 2-bytes        | 1-byte         | n-bytes            | 1-byte   |

Record Mark:

Record Mark is the start of frame. This field must contain ':'.

Reclen:

Reclen specifies the number of bytes of information or data which follows the Record Type field of the record.

Load Offset:

Load Offset specifies the 16-bit starting load offset of the data bytes, therefore this field is used only for

Data Program Record (see Section "ISP Commands Summary").

Record Type:

Record Type specifies the command type. This field is used to interpret the remaining information within the frame. The encoding for all the current record types is described in Section "ISP Commands Summary".

• Data/Info:

Data/Info is a variable length field. It consists of zero or more bytes encoded as pairs of hexadecimal digits. The meaning of data depends on the **Record Type**.

Checksum:

The two's complement of the 8-bit bytes that result from converting each pair of ASCII hexadecimal digits to one byte of binary, and including the **Reclen** field to and including the last byte of the **Data/Info** field. Therefore, the sum of all the ASCII pairs in a record after converting to binary, from the **Reclen** field to and including the **Checksum** field, is zero.

# **Electrical Characteristics**

# Absolute Maximum Ratings

| I = industrial                                                   | 40°C to 85°C                    |

|------------------------------------------------------------------|---------------------------------|

| Storage Temperature                                              | 65°C to + 150°C                 |

| Voltage on V <sub>CC</sub> to V <sub>SS</sub> (standard voltage) | 0.5V to + 6.5V                  |

| Voltage on V <sub>CC</sub> to V <sub>SS</sub> (low voltage)      | 0.5V to + 4.5V                  |

| Voltage on Any Pin to V <sub>SS</sub>                            | -0.5V to V <sub>CC</sub> + 0.5V |

| Power Dissipation                                                | 1 W <sup>(2)</sup>              |

|                                                                  |                                 |

Note: Stresses at or above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Power dissipation is based on the maximum allowable die temperature and the thermal resistance of the package.

# **DC Parameters**

$T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ;  $V_{SS} = 0V$ ;

$V_{CC}$  =2.7V to 5.5V and F = 0 to 40 MHz (both internal and external code execution)

| Symbol           | Parameter                                            | Min                                                                     | Тур | Мах                       | Unit        | Test Conditions                                                                                                                                        |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------|-----|---------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage                                    | -0.5                                                                    |     | 0.2 V <sub>CC</sub> - 0.1 | V           |                                                                                                                                                        |

| V <sub>IH</sub>  | Input High Voltage except RST, XTAL1                 | 0.2 V <sub>CC</sub> + 0.9                                               |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                                                        |

| V <sub>IH1</sub> | Input High Voltage RST, XTAL1                        | 0.7 V <sub>CC</sub>                                                     |     | V <sub>CC</sub> + 0.5     | V           |                                                                                                                                                        |

| V <sub>OL</sub>  | Output Low Voltage, ports 1, 2, 3, 4 <sup>(6)</sup>  |                                                                         |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} V_{CC} &= 4.5 V \text{ to } 5.5 V \\ I_{OL} &= 100 \ \mu A^{(4)} \\ I_{OL} &= 1.6 \ m A^{(4)} \\ I_{OL} &= 3.5 \ m A^{(4)} \end{split}$ |

|                  |                                                      |                                                                         |     | 0.45                      | V           | $V_{CC} = 2.7V \text{ to } 5.5V$<br>$I_{OL} = 0.8 \text{ mA}^{(4)}$                                                                                    |

| V <sub>OL1</sub> | Output Low Voltage, port 0, ALE, PSEN <sup>(6)</sup> |                                                                         |     | 0.3<br>0.45<br>1.0        | V<br>V<br>V | $\begin{split} V_{CC} &= 4.5 V \text{ to } 5.5 V \\ I_{OL} &= 200 \ \mu A^{(4)} \\ I_{OL} &= 3.2 \ m A^{(4)} \\ I_{OL} &= 7.0 \ m A^{(4)} \end{split}$ |

|                  |                                                      |                                                                         |     | 0.45                      | V           | $V_{CC} = 2.7V \text{ to } 5.5V$<br>$I_{OL} = 1.6 \text{ mA}^{(4)}$                                                                                    |

| V <sub>OH</sub>  | Output High Voltage, ports 1, 2, 3, 4                | V <sub>CC</sub> - 0.3<br>V <sub>CC</sub> - 0.7<br>V <sub>CC</sub> - 1.5 |     |                           | V<br>V<br>V | $V_{CC} = 5V \pm 10\%$<br>$I_{OH} = -10 \ \mu A$<br>$I_{OH} = -30 \ \mu A$<br>$I_{OH} = -60 \ \mu A$                                                   |

|                  |                                                      | 0.9 V <sub>CC</sub>                                                     |     |                           | V           | $V_{CC}$ = 2.7V to 5.5V<br>$I_{OH}$ = -10 $\mu$ A                                                                                                      |

$V_{CC}$  =4.5V to 5.5V and F = 0 to 60 MHz (internal code execution only)

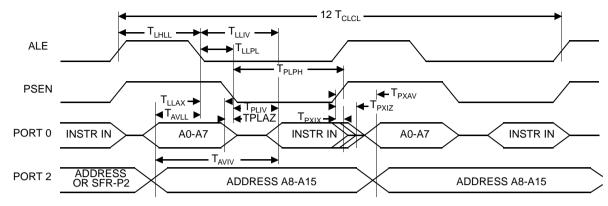

## External Program Memory Read Cycle

#### External Data Memory Characteristics

Table 101. Symbol Description

| Symbol            | Parameter                                   |  |

|-------------------|---------------------------------------------|--|

| T <sub>RLRH</sub> | RD Pulse Width                              |  |

| T <sub>WLWH</sub> | WR Pulse Width                              |  |

| T <sub>RLDV</sub> | RD to Valid Data In                         |  |

| T <sub>RHDX</sub> | Data Hold After RD                          |  |

| T <sub>RHDZ</sub> | Data Float After RD                         |  |

| T <sub>LLDV</sub> | ALE to Valid Data In                        |  |

| T <sub>AVDV</sub> | Address to Valid Data In                    |  |

| T <sub>LLWL</sub> | ALE to WR or RD                             |  |

| T <sub>AVWL</sub> | Address to WR or RD                         |  |

| T <sub>QVWX</sub> | Data Valid to WR Transition                 |  |

| T <sub>QVWH</sub> | T <sub>QVWH</sub> Data Set-up to WR High    |  |

| T <sub>WHQX</sub> | T <sub>WHQX</sub> Data Hold After WR        |  |

| T <sub>RLAZ</sub> | LAZ RD Low to Address Float                 |  |

| T <sub>WHLH</sub> | T <sub>WHLH</sub> RD or WR High to ALE high |  |

## **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

## **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

## **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

© Atmel Corporation 2005. All rights reserved. Atmel<sup>®</sup> and combinations thereof are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be the trademarks of others.