# E·XFL

## Atmel - AT89C51ID2-RLTUM Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | 80C51                                                       |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 60MHz                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                           |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 34                                                          |

| Program Memory Size        | 64KB (64K x 8)                                              |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 2K x 8                                                      |

| RAM Size                   | 2K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 44-LQFP                                                     |

| Supplier Device Package    | 44-VQFP (10x10)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at89c51id2-rltum |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The AT89C51ID2 retains all features of the Atmel 80C52 with 256 bytes of internal RAM, a 10-source 4-level interrupt controller and three timer/counters.

In addition, the AT89C51ID2 has a Programmable Counter Array, an XRAM of 1792 bytes, a Hardware Watchdog Timer, SPI and Keyboard, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a speed improvement mechanism (X2 mode).

The fully static design of the AT89C51ID2 allows to reduce system power consumption by bringing the clock frequency down to any value, even DC, without loss of data.

The AT89C51ID2 has 2 software-selectable modes of reduced activity and 8-bit clock prescaler for further reduction in power consumption. In the Idle mode the CPU is frozen while the peripherals and the interrupt system are still operating. In the power-down mode the RAM is saved and all other functions are inoperative.

The added features of the AT89C51ID2 make it more powerful for applications that need pulse width modulation, high speed I/O and counting capabilities such as alarms, motor control, corded phones, smart card readers.

| AT89C51ID2    | Flash (bytes) | XRAM (bytes) | TOTAL RAM<br>(bytes) | I/O |

|---------------|---------------|--------------|----------------------|-----|

| PLCC44/VQFP44 | 64K           | 1792         | 2048                 | 34  |

Table 1. Memory Size and I/O pins

2

#### Table 11. Two-Wire Interface Controller SFRs

| Mnemonic | Add | Name                       | 7     | 6    | 5     | 4     | 3    | 2    | 1     | 0     |

|----------|-----|----------------------------|-------|------|-------|-------|------|------|-------|-------|

| SSCON    | 93h | Synchronous Serial control | SSCR2 | SSPE | SSSTA | SSSTO | SSI  | SSAA | SSCR1 | SSCR0 |

| SSCS     | 94h | Synchronous Serial Status  | SSC4  | SSC3 | SSC2  | SSC1  | SSC0 | 0    | 0     | 0     |

| SSDAT    | 95h | Synchronous Serial Data    | SSD7  | SSD6 | SSD5  | SSD4  | SSD3 | SSD2 | SSD1  | SSD0  |

| SSADR    | 96h | Synchronous Serial Address | SSA7  | SSA6 | SSA5  | SSA4  | SSA3 | SSA2 | SSA1  | SSGC  |

## Table 12. Keyboard Interface SFRs

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

#### Table 13. EEPROM data Memory SFR

| Mnemonic | Add | Name                | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0      |

|----------|-----|---------------------|---|---|---|---|---|---|-----|--------|

| EECON    | D2h | EEPROM Data Control |   |   |   |   |   |   | EEE | EEBUSY |

#### Table below shows all SFRs with their address and their reset value.

## Table 14. SFR Mapping

|     | Bit<br>addressable                 |                       |                     | Nc                  | on Bit addressat    | ble                 |                     |                                     |     |

|-----|------------------------------------|-----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------------------------|-----|

|     | 0/8                                | 1/9                   | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                                 |     |

| F8h | PI2<br>XXXX XX11                   | CH<br>0000 0000       | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAP2H<br>XXXX XXXX | CCAP3H<br>XXXX XXXX | CCAP4H<br>XXXX XXXX |                                     | FFh |

| F0h | B<br>0000 0000                     |                       |                     |                     |                     |                     |                     |                                     | F7h |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000       | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAP2L<br>XXXX XXXX | CCAP3L<br>XXXX XXXX | CCAP4L<br>XXXX XXXX |                                     | EFh |

| E0h | ACC<br>0000 0000                   |                       |                     |                     |                     |                     |                     |                                     | E7h |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000     | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000 | CCAPM3<br>X000 0000 | CCAPM4<br>X000 0000 |                                     | DFh |

| D0h | PSW<br>0000 0000                   | FCON (1)<br>XXXX 0000 | EECON<br>xxxx xx00  |                     |                     |                     |                     |                                     | D7h |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00    | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000    | TH2<br>0000 0000    |                     |                                     | CFh |

| C0h | P4<br>1111 1111                    |                       |                     | SPCON<br>0001 0100  | SPSTA<br>0000 0000  | SPDAT<br>XXXX XXXX  |                     | P5 byte<br>Addressable<br>1111 1111 | C7h |

| B8h | IPL0<br>X000 000                   | SADEN<br>0000 0000    |                     |                     |                     |                     |                     |                                     | BFh |

| B0h | P3<br>1111 1111                    | IEN1<br>XXXX X000     | IPL1<br>XXXX X000   | IPH1<br>XXXX X111   |                     |                     |                     | IPH0<br>X000 0000                   | B7h |

| A8h | IEN0<br>0000 0000                  | SADDR<br>0000 0000    |                     |                     |                     |                     |                     | CKCON1<br>XXXX XXX0                 | AFh |

| A0h | P2<br>1111 1111                    |                       | AUXR1<br>XXXX X0X0  |                     |                     |                     | WDTRST<br>XXXX XXXX | WDTPRG<br>XXXX X000                 | A7h |

| 98h | SCON<br>0000 0000                  | SBUF<br>XXXX XXXX     | BRL<br>0000 0000    | BDRCON<br>XXX0 0000 | KBLS<br>0000 0000   | KBE<br>0000 0000    | KBF<br>0000 0000    |                                     | 9Fh |

| 90h | P1<br>1111 1111                    |                       |                     | SSCON<br>0000 0000  | SSCS<br>1111 1000   | SSDAT<br>1111 1111  | SSADR<br>1111 1110  | CKRL<br>1111 1111                   | 97h |

| 88h | TCON<br>0000 0000                  | TMOD<br>0000 0000     | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000    | TH1<br>0000 0000    | AUXR<br>XX00 1000   | CKCON0<br>0000 0000                 | 8Fh |

| 80h | P0<br>1111 1111                    | SP<br>0000 0111       | DPL<br>0000 0000    | DPH<br>0000 0000    |                     | CKSEL<br>XXXX XXX0  | OSSCON<br>XXXX X001 | PCON<br>00X1 0000                   | 87h |

|     | 0/8                                | 1/9                   | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                                 |     |

Reserved

## 9 AT89C51ID2 -

#### Table 23. AUXR1 register

AUXR1- Auxiliary Register 1(0A2h)

| 7             | 6               | 5                                                                               | 4                                                                                                    | 3                | 2               | 1            | 0 |  |  |  |

|---------------|-----------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|-----------------|--------------|---|--|--|--|

| -             | -               | ENBOOT                                                                          | ENBOOT - GF3 0 - DPS                                                                                 |                  |                 |              |   |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                     | Description                                                                                          |                  |                 |              |   |  |  |  |

| 7             | -               | Reserved<br>The value rea                                                       | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                      |                  |                 |              |   |  |  |  |

| 6             | -               | Reserved<br>The value rea                                                       | ad from this b                                                                                       | it is indetermir | nate. Do not se | et this bit. |   |  |  |  |

| 5             | ENBOOT          | Cleared to dis                                                                  | Enable Boot Flash<br>Cleared to disable boot ROM.<br>Set to map the boot ROM between F800h - 0FFFFh. |                  |                 |              |   |  |  |  |

| 4             | -               | Reserved<br>The value rea                                                       | ad from this b                                                                                       | it is indetermir | nate. Do not se | et this bit. |   |  |  |  |

| 3             | GF3             | This bit is a                                                                   | general purp                                                                                         | oose user flag   | g. *            |              |   |  |  |  |

| 2             | 0               | Always clear                                                                    | ed.                                                                                                  |                  |                 |              |   |  |  |  |

| 1             | -               | Reserved<br>The value read from this bit is indeterminate. Do not set this bit. |                                                                                                      |                  |                 |              |   |  |  |  |

| 0             | DPS             | Data Pointer<br>Cleared to se<br>Set to select                                  | lect DPTR0.                                                                                          |                  |                 |              |   |  |  |  |

Reset Value: XXXX XX0X0b

#### Not bit addressable

Note: \*Bit 2 stuck at 0; this allows to use INC AUXR1 to toggle DPS without changing GF3.

#### ASSEMBLY LANGUAGE

; Block move using dual data pointers ; Modifies DPTR0, DPTR1, A and PSW ; note: DPS exits opposite of entry state ; unless an extra INC AUXR1 is added 00A2 AUXR1 EQU 0A2H 0000 909000MOV DPTR,#SOURCE ; address of SOURCE 0003 05A2 INC AUXR1 ; switch data pointers 0005 90A000 MOV DPTR,#DEST ; address of DEST 0008 LOOP: 0008 05A2 INC AUXR1 ; switch data pointers 000A E0 MOVX A,@DPTR ; get a byte from SOURCE 000B A3 INC DPTR ; increment SOURCE address 000C 05A2 INC AUXR1 ; switch data pointers 000E F0 MOVX @DPTR,A ; write the byte to DEST 000F A3 INC DPTR ; increment DEST address 0010 70F6JNZ LOOP ; check for 0 terminator 0012 05A2 INC AUXR1 ; (optional) restore DPS

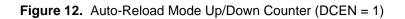

(UP COUNTING RELOAD VALUE)

## Programmable Clock-Output

In the clock-out mode, Timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 13). The input clock increments TL2 at frequency  $F_{CLK PERIPH}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, Timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$Clock-OutFrequency = \frac{F_{CLKPERIPH}}{4 \times (65536 - RCAP2H/RCAP2L)}$

For a 16 MHz system clock, Timer 2 has a programmable frequency range of 61 Hz  $(F_{CLK PERIPH}/2^{16})$  to 4 MHz  $(F_{CLK PERIPH}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear C/T2 bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2.It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use Timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

#### Table 27. CMOD Register

CMOD - PCA Counter Mode Register (D9h)

| 7             | 6               | 5                               | 4                                                                                                                                                                    | 3               | 2              | 1            | 0   |  |  |  |  |

|---------------|-----------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|-----|--|--|--|--|

| CIDL          | WDTE            | -                               | -                                                                                                                                                                    | -               | CPS1           | CPS0         | ECF |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     | Description                                                                                                                                                          |                 |                |              |     |  |  |  |  |

| 7             | CIDL            | Cleared to p                    | <b>Counter Idle Control</b><br>Cleared to program the PCA Counter to continue functioning during idle Mode.<br>Set to program PCA to be gated off during idle.       |                 |                |              |     |  |  |  |  |

| 6             | WDTE            | Cleared to di                   | Vatchdog Timer Enable<br>Cleared to disable Watchdog Timer function on PCA Module 4.<br>Set to enable Watchdog Timer function on PCA Module 4.                       |                 |                |              |     |  |  |  |  |

| 5             | -               | Reserved<br>The value re        | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                                      |                 |                |              |     |  |  |  |  |

| 4             | -               | Reserved<br>The value re        | ad from this b                                                                                                                                                       | it is indetermi | nate. Do not s | et this bit. |     |  |  |  |  |

| 3             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                                                                                                       | it is indetermi | nate. Do not s | et this bit. |     |  |  |  |  |

| 2             | CPS1            | PCA Count                       | Pulse Select                                                                                                                                                         |                 |                |              |     |  |  |  |  |

| 1             | CPS0            | 0 0 I<br>0 1lr<br>1 0T          | 0       0 Internal clock fCLK PERIPH/6         0       1Internal clock fCLK PERIPH/2         1       0Timer 0 Overflow                                               |                 |                |              |     |  |  |  |  |

| 0             | ECF             | Cleared to di                   | <b>PCA Enable Counter Overflow Interrupt</b><br>Cleared to disable CF bit in CCON to inhibit an interrupt.<br>Set to enable CF bit in CCON to generate an interrupt. |                 |                |              |     |  |  |  |  |

Reset Value = 00XX X000b Not bit addressable

The CMOD register includes three additional bits associated with the PCA (See Figure 14 and Table 27).

- The CIDL bit which allows the PCA to stop during idle mode.

- The WDTE bit which enables or disables the watchdog function on module 4.

- The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 28).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

| Baud Rates | F <sub>osc</sub> = 16 | . 384 MHz | F <sub>osc</sub> = 24MHz |           |  |

|------------|-----------------------|-----------|--------------------------|-----------|--|

|            | BRL                   | Error (%) | BRL                      | Error (%) |  |

| 115200     | 247                   | 1.23      | 243                      | 0.16      |  |

| 57600      | 238                   | 1.23      | 230                      | 0.16      |  |

| 38400      | 229                   | 1.23      | 217                      | 0.16      |  |

| 28800      | 220                   | 1.23      | 204                      | 0.16      |  |

| 19200      | 203                   | 0.63      | 178                      | 0.16      |  |

| 9600       | 149                   | 0.31      | 100                      | 0.16      |  |

| 4800       | 43                    | 1.23      | -                        | -         |  |

Table 39.

Example of Computed Value When X2=1, SMOD1=1, SPD=1

Table 40. Example of Computed Value When X2=0, SMOD1=0, SPD=0

| Baud Rates | F <sub>OSC</sub> = 16 | . 384 MHz | F <sub>OSC</sub> = 24MHz |           |  |

|------------|-----------------------|-----------|--------------------------|-----------|--|

|            | BRL                   | Error (%) | BRL                      | Error (%) |  |

| 4800       | 247                   | 1.23      | 243                      | 0.16      |  |

| 2400       | 238                   | 1.23      | 230                      | 0.16      |  |

| 1200       | 220                   | 1.23      | 202                      | 3.55      |  |

| 600        | 185                   | 0.16      | 152                      | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (refer to Figure 23.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 47.)

## **UART Registers**

#### Table 41. SADEN Register

SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

#### Table 42. SADDR Register

SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

## Registers

The PCA interrupt vector is located at address 0033H, the SPI interrupt vector is located at address 0043H and Keyboard interrupt vector is located at address 004BH. All other vectors addresses are the same as standard C52 devices.

#### Table 48. Priority Level Bit Values

| IPH. x | IPL. x | Interrupt Level Priority |

|--------|--------|--------------------------|

| 0      | 0      | 0 (Lowest)               |

| 0      | 1      | 1                        |

| 1      | 0      | 2                        |

| 1      | 1      | 3 (Highest)              |

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

## Table 60. KBE Register

KBE-Keyboard Input Enable Register (9Dh)

| 7             | 6               | 5             | 4                                                                                                                                                      | 3          | 2              | 1               | 0     |  |  |

|---------------|-----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|-----------------|-------|--|--|

| KBE7          | KBE6            | KBE5          | KBE4                                                                                                                                                   | KBE3       | KBE2           | KBE1            | KBE0  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   |                                                                                                                                                        |            |                |                 |       |  |  |

| 7             | KBE7            | Cleared to en | n <b>e 7 Enable k</b><br>nable standar<br>e KBF. 7 bit in                                                                                              | d I/O pin. | to generate ar | n interrupt req | uest. |  |  |

| 6             | KBE6            | Cleared to en | ne 6 Enable k<br>nable standar<br>e KBF. 6 bit in                                                                                                      | d I/O pin. | to generate ar | n interrupt req | uest. |  |  |

| 5             | KBE5            | Cleared to en | Keyboard line 5 Enable bit<br>Cleared to enable standard I/O pin.<br>Set to enable KBF. 5 bit in KBF register to generate an interrupt request.        |            |                |                 |       |  |  |

| 4             | KBE4            | Cleared to en | ne 4 Enable k<br>nable standar<br>e KBF. 4 bit in                                                                                                      | d I/O pin. | to generate ar | n interrupt req | uest. |  |  |

| 3             | KBE3            | Cleared to en | ne 3 Enable k<br>nable standar<br>e KBF. 3 bit in                                                                                                      | d I/O pin. | to generate ar | n interrupt req | uest. |  |  |

| 2             | KBE2            | Cleared to en | Keyboard line 2 Enable bit<br>Cleared to enable standard I/O pin.<br>Set to enable KBF. 2 bit in KBF register to generate an interrupt request.        |            |                |                 |       |  |  |

| 1             | KBE1            | Cleared to en | <b>Keyboard line 1 Enable bit</b><br>Cleared to enable standard I/O pin.<br>Set to enable KBF. 1 bit in KBF register to generate an interrupt request. |            |                |                 |       |  |  |

| 0             | KBE0            | Cleared to en | ne 0 Enable k<br>nable standar<br>e KBF. 0 bit in                                                                                                      | d I/O pin. | to generate ar | n interrupt req | uest. |  |  |

Reset Value= 0000 0000b

#### Table 67. Status in Master Receiver Mode

|                |                                         | Appli           | cation soft       | ware respo | nse  |                                        |                                                                                                |

|----------------|-----------------------------------------|-----------------|-------------------|------------|------|----------------------------------------|------------------------------------------------------------------------------------------------|

| Status<br>Code | Status of the Two-<br>wire Bus and Two- |                 |                   | To SSC     | ON   |                                        |                                                                                                |

| SSSTA          | wire Hardware                           | To/From SSDAT   | SSSTA SSSTO SSI S |            | SSAA | Next Action Taken by Two-wire Hardware |                                                                                                |

| 08h            | A START condition has been transmitted  | Write SLA+R     | х                 | 0          | 0    | x                                      | SLA+R will be transmitted.                                                                     |

|                | A repeated START                        | Write SLA+R     | х                 | 0          | 0    | x                                      | SLA+R will be transmitted.                                                                     |

| 10h            | condition has been<br>transmitted       | Write SLA+W     | х                 | 0          | 0    | x                                      | SLA+W will be transmitted.<br>Logic will switch to master transmitter mode.                    |

| 38h            | Arbitration lost in<br>SLA+R or NOT ACK | No SSDAT action | 0                 | 0          | 0    | x                                      | Two-wire bus will be released and not addressed slave mode will be entered.                    |

| 3011           | bit                                     | No SSDAT action | 1                 | 0          | 0    | х                                      | A START condition will be transmitted when the bus becomes free.                               |

| 40h            | SLA+R has been<br>transmitted; ACK has  | No SSDAT action | 0                 | 0          | 0    | 0                                      | Data byte will be received and NOT ACK will be returned.                                       |

|                | been received                           | No SSDAT action | 0                 | 0          | 0    | 1                                      | Data byte will be received and ACK will be returned.                                           |

|                |                                         | No SSDAT action | 1                 | 0          | 0    | х                                      | Repeated START will be transmitted.                                                            |

| 48h            | SLA+R has been<br>transmitted; NOT ACK  | No SSDAT action | 0                 | 1          | 0    | Х                                      | STOP condition will be transmitted and SSSTO flag will be reset.                               |

|                | has been received                       | No SSDAT action | 1                 | 1          | 0    | x                                      | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |

| 50h            | Data byte has been<br>received; ACK has | Read data byte  | 0                 | 0          | 0    | 0                                      | Data byte will be received and NOT ACK will be returned.                                       |

|                | been returned                           | Read data byte  | 0                 | 0          | 0    | 1                                      | Data byte will be received and ACK will be returned.                                           |

|                |                                         | Read data byte  | 1                 | 0          | 0    | х                                      | Repeated START will be transmitted.                                                            |

| 58h            | Data byte has been received; NOT ACK    | Read data byte  | 0                 | 1          | 0    | х                                      | STOP condition will be transmitted and SSSTO flag will be reset.                               |

|                | has been returned                       | Read data byte  | 1                 | 1          | 0    | x                                      | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |

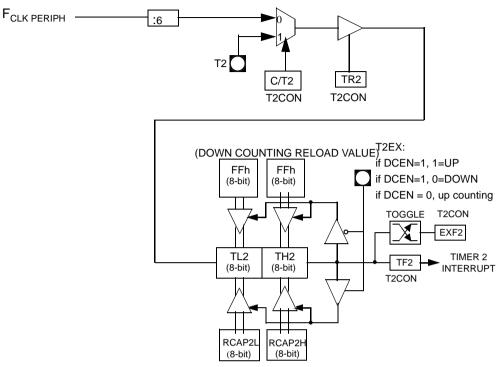

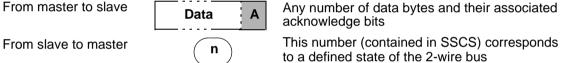

#### Figure 35. Format and State in the Slave Transmitter Mode

#### Table 69. Status in Slave Transmitter Mode

|                |                                                           | Application S          | Software | e Respo | nse |    |                                                                 |

|----------------|-----------------------------------------------------------|------------------------|----------|---------|-----|----|-----------------------------------------------------------------|

| Status         |                                                           | To/from SSDAT To SSCON |          |         |     |    |                                                                 |

| Code<br>(SSCS) | Status of the 2-wire bus and 2-wire hardware              |                        | STA      | ѕто     | SI  | АА | Next Action Taken By 2-wire Software                            |

| AOL            | Own SLA+R has been                                        | Load data byte or      | х        | 0       | 0   | 0  | Last data byte will be transmitted and NOT ACK will be received |

| A8h            | received; ACK has been<br>returned                        | Load data byte         | х        | 0       | 0   | 1  | Data byte will be transmitted and ACK will be received          |

| B0h            | Arbitration lost in SLA+R/W as master; own SLA+R has been | Load data byte or      | х        | 0       | 0   | 0  | Last data byte will be transmitted and NOT ACK will be received |

| BUII           | received; ACK has been returned                           | Load data byte         | х        | 0       | 0   | 1  | Data byte will be transmitted and ACK will be received          |

| B8h            | Data byte in SSDAT has been                               | Load data byte or      | х        | 0       | 0   | 0  | Last data byte will be transmitted and NOT ACK will be received |

| DOII           | transmitted; NOT ACK has been received                    | Load data byte         | х        | 0       | 0   | 1  | Data byte will be transmitted and ACK will be received          |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                       |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0             | GC              | General Call bit<br>Clear to disable the general call address recognition.<br>Set to enable the general call address recognition. |

8-bit Shift register

MISO

MISC

8-bit Shift register

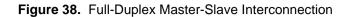

- 2. The SPI Module should be configured as a Slave before it is enabled (SPEN set).

- 3. The maximum frequency of the SCK for an SPI configured as a Slave is the bus clock speed.

- 4. Before writing to the CPOL and CPHA bits, the SPI should be disabled (SPEN = '0').

| Error Conditions       | The following flags in the SPSTA signal SPI error conditions:                                                                                                                                                                                                                                                                                                                     |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode Fault (MODF)      | Mode Fault error in Master mode SPI indicates that the level on the Slave Select $(\overline{SS})$ pin is inconsistent with the actual mode of the device. MODF is set to warn that there may be a multi-master conflict for system control. In this case, the SPI system is affected in the following ways:                                                                      |

|                        | An SPI receiver/error CPU interrupt request is generated                                                                                                                                                                                                                                                                                                                          |

|                        | <ul> <li>The SPEN bit in SPCON is cleared. This disables the SPI</li> </ul>                                                                                                                                                                                                                                                                                                       |

|                        | The MSTR bit in SPCON is cleared                                                                                                                                                                                                                                                                                                                                                  |

|                        | When $\overline{SS}$ Disable (SSDIS) bit in the SPCON register is cleared, the MODF flag is set when the $\overline{SS}$ signal becomes '0'.                                                                                                                                                                                                                                      |

|                        | However, as stated before, for a system with one Master, if the $\overline{SS}$ pin of the Master device is pulled low, there is no way that another Master attempts to drive the network. In this case, to prevent the MODF flag from being set, software can set the SSDIS bit in the SPCON register and therefore making the $\overline{SS}$ pin as a general-purpose I/O pin. |

|                        | Clearing the MODF bit is accomplished by a read of SPSTA register with MODF bit set, followed by a write to the SPCON register. SPEN Control bit may be restored to its original set state after the MODF bit has been cleared.                                                                                                                                                   |

| Write Collision (WCOL) | A Write Collision (WCOL) flag in the SPSTA is set when a write to the SPDAT register is done during a transmit sequence.                                                                                                                                                                                                                                                          |

|                        | WCOL does not cause an interruption, and the transfer continues uninterrupted.                                                                                                                                                                                                                                                                                                    |

|                        | Clearing the WCOL bit is done through a software sequence of an access to SPSTA and an access to SPDAT.                                                                                                                                                                                                                                                                           |

| Overrun Condition      | An overrun condition occurs when the Master device tries to send several data Bytes<br>and the Slave devise has not cleared the SPIF bit issuing from the previous data Byte<br>transmitted. In this case, the receiver buffer contains the Byte sent after the SPIF bit was<br>last cleared. A read of the SPDAT returns this Byte. All others Bytes are lost.                   |

|                        | This condition is not detected by the SPI peripheral.                                                                                                                                                                                                                                                                                                                             |

| SS Error Flag (SSERR)  | A Synchronous Serial Slave Error occurs when $\overline{SS}$ goes high before the end of a received data in slave mode. SSERR does not cause in interruption, this bit is cleared by writing 0 to SPEN bit (reset of the SPI state machine).                                                                                                                                      |

| Interrupts             | Two SPI status flags can generate a CPU interrupt requests:                                                                                                                                                                                                                                                                                                                       |

#### Table 78. SPI Interrupts

| Flag                    | Request                                               |

|-------------------------|-------------------------------------------------------|

| SPIF (SP data transfer) | SPI Transmitter Interrupt request                     |

| MODF (Mode Fault)       | SPI Receiver/Error Interrupt Request (if SSDIS = '0') |

Serial Peripheral data transfer flag, SPIF: This bit is set by hardware when a transfer has been completed. SPIF bit generates transmitter CPU interrupt requests.

Mode Fault flag, MODF: This bit becomes set to indicate that the level on the SS is inconsistent with the mode of the SPI. MODF with SSDIS reset, generates receiver/error CPU interrupt requests. When SSDIS is set, no MODF interrupt request is generated.

Figure 42 gives a logical view of the above statements.

## Example

#### Read function (read SBV)

| HOST                                          | : | 02 | 0000 | 05 | 07 | 02 | FO |       |    |            |

|-----------------------------------------------|---|----|------|----|----|----|----|-------|----|------------|

| BOOTLOADER                                    | : | 02 | 0000 | 05 | 07 | 02 | FO | Value | CR | $_{ m LF}$ |

| Atmel Read function (read Bootloader version) |   |    |      |    |    |    |    |       |    |            |

| HOST                                          | : | 02 | 0000 | 01 | 02 | 00 | FB |       |    |            |

| BOOTLOADER                                    | : | 02 | 0000 | 01 | 02 | 00 | FB | Value | CR | $_{ m LF}$ |

#### Table 96. ISP Commands Summary (Continued)

| Command | Command Name        | data[0] | data[1] | Command Effect                                     |

|---------|---------------------|---------|---------|----------------------------------------------------|

| Jonana  |                     | aa.a[0] |         |                                                    |

|         |                     |         | 00h     | Manufacturer Id                                    |

|         |                     | 00h     | 01h     | Device Id #1                                       |

|         |                     | 0011    | 02h     | Device Id #2                                       |

|         |                     |         | 03h     | Device Id #3                                       |

|         |                     |         | 00h     | Read SSB                                           |

| 05h     | Read Function       | 07h     | 01h     | Read BSB                                           |

|         |                     |         | 02h     | Read SBV                                           |

|         |                     |         | 06h     | Read Extra Byte                                    |

|         |                     | 0Bh     | 00h     | Read Hardware Byte                                 |

|         |                     | 0Eh     | 00h     | Read Device Boot ID1                               |

|         |                     | 0En     | 01h     | Read Device Boot ID2                               |

|         |                     | 0Fh     | 00h     | Read Bootloader Version                            |

|         |                     |         |         | Program Nb EEProm Data Byte.                       |

| 07h     | Program EEPROM data |         |         | Bootloader will accept up to 128 (80h) data bytes. |

## **AC Parameters**

| Explanation of the AC<br>Symbols | Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for. |  |  |  |  |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                  | Example:T <sub>AVLL</sub> = Time for Addr <u>ess V</u> alid to ALE Low.<br>T <sub>LLPL</sub> = Time for ALE Low to PSEN Low.                                                                                                                                                                |  |  |  |  |  |  |

|                                  | (Load Capacitance for port 0, ALE and PSEN = 100 pF; Load Capacitance for all other outputs = 80 pF.)                                                                                                                                                                                       |  |  |  |  |  |  |

|                                  | Table 98 Table 101, and Table 104 give the description of each AC symbols.                                                                                                                                                                                                                  |  |  |  |  |  |  |

|                                  | Table 99, Table 100, Table 102 and Table 105 gives the range for each AC parameter.                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                  | Table 99, Table 100 and Table 106 give the frequency derating formula of the AC parameter for each speed range description. To calculate each AC symbols. take the x value in the correponding column (-M or -L) and use this value in the formula.                                         |  |  |  |  |  |  |

|                                  | Example: T <sub>LLIU</sub> for -M and 20 MHz, Standard clock.<br>x = 35 ns<br>T 50 ns<br>T <sub>CCIV</sub> = 4T - x = 165 ns                                                                                                                                                                |  |  |  |  |  |  |

| External Program Memory          | Table 98. Symbol Description                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Characteristics                  | Sumbal Denemeter                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Symbol            | Parameter                          |

|-------------------|------------------------------------|

| Т                 | Oscillator clock period            |

| T <sub>LHLL</sub> | ALE pulse width                    |

| T <sub>AVLL</sub> | Address Valid to ALE               |

| T <sub>LLAX</sub> | Address Hold After ALE             |

| T <sub>LLIV</sub> | ALE to Valid Instruction In        |

| T <sub>LLPL</sub> | ALE to PSEN                        |

| T <sub>PLPH</sub> | PSEN Pulse Width                   |

| T <sub>PLIV</sub> | PSEN to Valid Instruction In       |

| T <sub>PXIX</sub> | Input Instruction Hold After PSEN  |

| T <sub>PXIZ</sub> | Input Instruction Float After PSEN |

| T <sub>AVIV</sub> | Address to Valid Instruction In    |

| T <sub>PLAZ</sub> | PSEN Low to Address Float          |

|                   | -М  |     |     | -L  |       |  |  |

|-------------------|-----|-----|-----|-----|-------|--|--|

| Symbol            | Min | Max | Min | Мах | Units |  |  |

| T <sub>RLRH</sub> | 125 |     | 125 |     | ns    |  |  |

| T <sub>WLWH</sub> | 125 |     | 125 |     | ns    |  |  |

| T <sub>RLDV</sub> |     | 95  |     | 95  | ns    |  |  |

| T <sub>RHDX</sub> | 0   |     | 0   |     | ns    |  |  |

| T <sub>RHDZ</sub> |     | 25  |     | 25  | ns    |  |  |

| T <sub>LLDV</sub> |     | 155 |     | 155 | ns    |  |  |

| T <sub>AVDV</sub> |     | 160 |     | 160 | ns    |  |  |

| T <sub>LLWL</sub> | 45  | 105 | 45  | 105 | ns    |  |  |

| T <sub>AVWL</sub> | 70  |     | 70  |     | ns    |  |  |

| T <sub>QVWX</sub> | 5   |     | 5   |     | ns    |  |  |

| T <sub>QVWH</sub> | 155 |     | 155 |     | ns    |  |  |

| T <sub>WHQX</sub> | 10  |     | 10  |     | ns    |  |  |

| T <sub>RLAZ</sub> | 0   |     | 0   |     | ns    |  |  |

| T <sub>WHLH</sub> | 5   | 45  | 5   | 45  | ns    |  |  |

Table 102. AC Parameters for a Fix Clock

Table 103.

AC Parameters for a Variable Clock

| Symbol            | Туре | Standard<br>Clock | X2 Clock  | X parameter for<br>-M range | X parameter for<br>-L range | Units |

|-------------------|------|-------------------|-----------|-----------------------------|-----------------------------|-------|

| T <sub>RLRH</sub> | Min  | 6 T - x           | 3 T - x   | 25                          | 25                          | ns    |

| T <sub>WLWH</sub> | Min  | 6 T - x           | 3 T - x   | 25                          | 25                          | ns    |

| T <sub>RLDV</sub> | Max  | 5 T - x           | 2.5 T - x | 30                          | 30                          | ns    |

| T <sub>RHDX</sub> | Min  | х                 | х         | 0                           | 0                           | ns    |

| T <sub>RHDZ</sub> | Max  | 2 T - x           | T - x     | 25                          | 25                          | ns    |

| T <sub>LLDV</sub> | Max  | 8 T - x           | 4T -x     | 45                          | 45                          | ns    |

| T <sub>AVDV</sub> | Max  | 9 T - x           | 4.5 T - x | 65                          | 65                          | ns    |

| T <sub>LLWL</sub> | Min  | 3 T - x           | 1.5 T - x | 30                          | 30                          | ns    |

| T <sub>LLWL</sub> | Max  | 3 T + x           | 1.5 T + x | 30                          | 30                          | ns    |

| T <sub>AVWL</sub> | Min  | 4 T - x           | 2 T - x   | 30                          | 30                          | ns    |

| T <sub>QVWX</sub> | Min  | T - x             | 0.5 T - x | 20                          | 20                          | ns    |

| T <sub>QVWH</sub> | Min  | 7 T - x           | 3.5 T - x | 20                          | 20                          | ns    |

| T <sub>WHQX</sub> | Min  | T - x             | 0.5 T - x | 15                          | 15                          | ns    |

| T <sub>RLAZ</sub> | Max  | х                 | х         | 0                           | 0                           | ns    |

| T <sub>WHLH</sub> | Min  | T - x             | 0.5 T - x | 20                          | 20                          | ns    |

| T <sub>WHLH</sub> | Max  | T + x             | 0.5 T + x | 20                          | 20                          | ns    |

AT89C51ID2

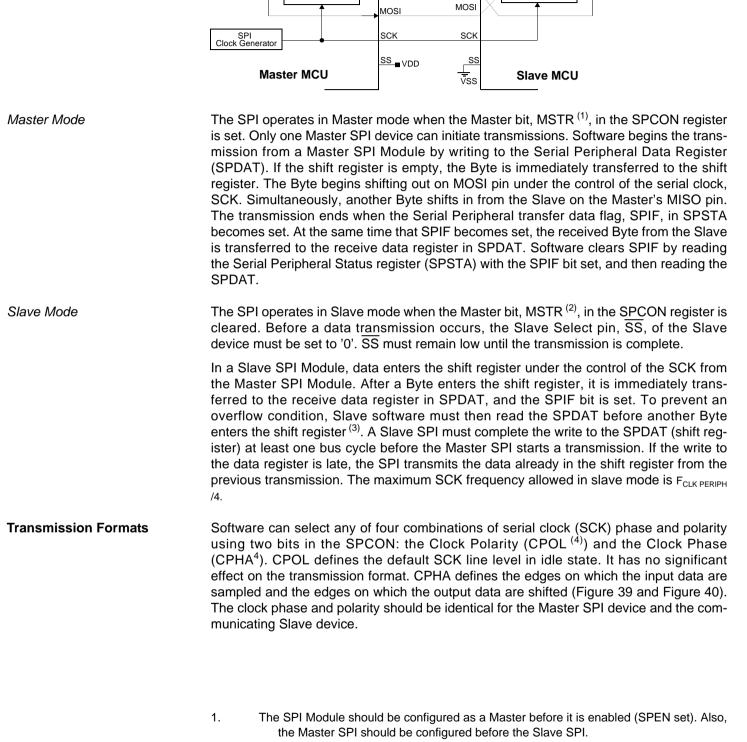

Figure 61. Internal Clock Signals

This diagram indicates when signals are clocked internally. The time it takes the signals to propagate to the pins, however, ranges from 25 to 125 ns. This propagation delay is dependent on variables such as temperature and pin loading. Propagation also varies from output to output and component. Typically though ( $T_A = 25^{\circ}C$  fully loaded) RD and WR propagation delays are approximately 50 ns. The other signals are typically 85 ns. Propagation delays are incorporated in the AC specifications.

## **Ordering Information**

Table 107. Possible Order Entries

| Part Number      | Supply<br>Voltage | Temperature<br>Range  | Package | Packing | Product Marking |

|------------------|-------------------|-----------------------|---------|---------|-----------------|

| AT89C51ID2-SLSIM |                   | Industrial            | PLCC44  | Stick   | AT89C51ID2-IM   |

| AT89C51ID2-RLTIM | 2.7V-5.5V         |                       | VQFP44  | Tray    | AT89C51ID2-IM   |

| AT89C51ID2-SLSUM | 2.7 - 5.5 -       | Industrial &<br>Green | PLCC44  | Stick   | AT89C51ID2-UM   |

| AT89C51ID2-RLTUM |                   |                       | VQFP44  | Tray    | AT89C51ID2-UM   |

Change Log for 4289A -09/03 to 4289B - 12/03

1. Improvement of explanations throughout the document.

4289B - 12/03 to 4289C -11/05

1. Added 'Industrial & Green" product versions.