Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | 80C51                                                                      |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 60MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89c51id2-slsum |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 15. Pin Description (Continued)

|               | Pin N          | umber        | Tuno |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|----------------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic      | PLCC44         | VQFP44       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |                |              | I/O  | MOSI: SPI Master Output Slave Input line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |                |              |      | When SPI is in master mode, MOSI outputs data to the slave peripheral. When SPI is in slave mode, MOSI receives data from the master controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| XTALA1        | 21             | 15           | Ι    | Crystal A 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| XTALA2        | 20             | 14           | 0    | Crystal A 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTALB1        | 2              | 40           | I    | Crystal B 1: (Sub Clock) Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XTALB2        | 1              | 39           | 0    | Crystal B 2: (Sub Clock) Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P2.0 - P2.7   | 24 - 31        | 18 - 25      | I/O  | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. |

| P3.0 - P3.7   | 11,<br>13 - 19 | 5,<br>7 - 13 | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                     |

|               | 11             | 5            | I    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               | 13             | 7            | 0    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|               | 14             | 8            | I    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | 15             | 9            | I    | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | 16             | 10           | I    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | 17             | 11           | I    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               | 18             | 12           | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 19             | 13           | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P4.0 - P4.7   | -              | -            | I/O  | <b>Port 4:</b> Port 4 is an 8-bit bidirectional I/O port with internal pull-ups. Port 5 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 4 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |

| P5.0 - P5.7   | -              | -            | I/O  | <b>Port 5:</b> Port 5 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 5 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |

| Pl2.0 - Pl2.1 | 34, 12         | 28, 6        |      | <b>Port 12:</b> Port 12 is an open drain. It can be used as inputs (must be polarized to Vcc with external resistor to prevent any parasitic current consumption).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               | 34             | 28           | I/O  | SCL (PI2.0): 2-wire Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |                |              |      | SCL output the serial clock to slave peripherals<br>SCL input the serial clock from master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

AT89C51ID2

## Table 19. PCON Register

PCON - Power Control Register (87h)

| 7             | 6               | 5                                                                                              | 5 4 3 2 1 0         |                                  |                 |              |             |  |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------|---------------------|----------------------------------|-----------------|--------------|-------------|--|--|--|

| SMOD1         | SMOD0           | -                                                                                              | - POF GF1 GF0 PD ID |                                  |                 |              |             |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                    |                     |                                  |                 |              |             |  |  |  |

| 7             | SMOD1           | Serial port N<br>Set to select                                                                 |                     | rate in mode 1                   | l, 2 or 3.      |              |             |  |  |  |

| 6             | SMOD0           |                                                                                                |                     | in SCON regis<br>DN register.    | ster.           |              |             |  |  |  |

| 5             | -               | Reserved<br>The value re                                                                       | ad from this b      | it is indetermi                  | nate. Do not se | et this bit. |             |  |  |  |

| 4             | POF             |                                                                                                | cognize next        |                                  | to its nominal  | voltage. Can | also be set |  |  |  |

| 3             | GF1             |                                                                                                | oftware for ge      | eneral purpose<br>al purpose usa |                 |              |             |  |  |  |

| 2             | GF0             |                                                                                                | oftware for ge      | eneral purpose<br>al purpose usa |                 |              |             |  |  |  |

| 1             | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode. |                     |                                  |                 |              |             |  |  |  |

| 0             | IDL             | Idle mode b<br>Cleared by h<br>Set to enter                                                    | ardware whe         | n interrupt or r                 | eset occurs.    |              |             |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

## Reset

Introduction

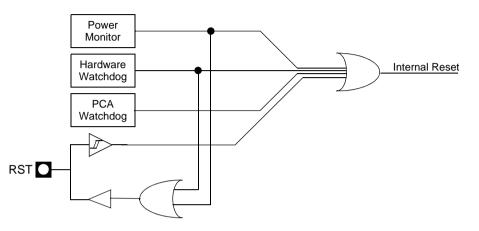

The reset sources are : Power Management, Hardware Watchdog, PCA Watchdog and Reset input.

Figure 7. Reset schematic

## **Reset Input**

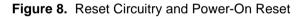

The Reset input can be used to force a reset pulse longer than the internal reset controlled by the Power Monitor. RST input has a pull-down resistor allowing power-on reset by simply connecting an external capacitor to  $V_{CC}$  as shown in Figure 8. Resistor value and input characteristics are discussed in the Section "DC Characteristics" of the AT89C51ID2 datasheet.

AT89C51ID2

#### Table 27. CMOD Register

CMOD - PCA Counter Mode Register (D9h)

| 7             | 6               | 5                               | 4                                                                                                                                                             | 3                            | 2                            | 1              | 0          |  |  |

|---------------|-----------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|----------------|------------|--|--|

| CIDL          | WDTE            | -                               | -                                                                                                                                                             | -                            | CPS1                         | CPS0           | ECF        |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                     |                                                                                                                                                               |                              |                              |                |            |  |  |

| 7             | CIDL            |                                 | rogram the P0                                                                                                                                                 | CA Counter to gated off duri | continue func<br>ng idle.    | tioning during | idle Mode. |  |  |

| 6             | WDTE            | Cleared to di                   |                                                                                                                                                               | 0                            | tion on PCA N<br>on PCA Modu |                |            |  |  |

| 5             | -               | Reserved<br>The value re        | ad from this b                                                                                                                                                | it is indetermi              | nate. Do not s               | et this bit.   |            |  |  |

| 4             | -               | Reserved<br>The value re        | ad from this b                                                                                                                                                | it is indetermi              | nate. Do not s               | et this bit.   |            |  |  |

| 3             | -               | <b>Reserved</b><br>The value re | ad from this b                                                                                                                                                | it is indetermi              | nate. Do not s               | et this bit.   |            |  |  |

| 2             | CPS1            | PCA Count                       | Pulse Select                                                                                                                                                  |                              |                              |                |            |  |  |

| 1             | CPS0            | 0 0 I<br>0 1lr<br>1 0T          | 0       0 Internal clock fCLK PERIPH/6         0       1Internal clock fCLK PERIPH/2         1       0Timer 0 Overflow                                        |                              |                              |                |            |  |  |

| 0             | ECF             | Cleared to di                   | PCA Enable Counter Overflow Interrupt<br>Cleared to disable CF bit in CCON to inhibit an interrupt.<br>Set to enable CF bit in CCON to generate an interrupt. |                              |                              |                |            |  |  |

Reset Value = 00XX X000b Not bit addressable

The CMOD register includes three additional bits associated with the PCA (See Figure 14 and Table 27).

- The CIDL bit which allows the PCA to stop during idle mode.

- The WDTE bit which enables or disables the watchdog function on module 4.

- The ECF bit which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows.

The CCON register contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (Refer to Table 28).

- Bit CR (CCON.6) must be set by software to run the PCA. The PCA is shut off by clearing this bit.

- Bit CF: The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software.

• Bits 0 through 4 are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software.

### Table 28. CCON Register

CCON - PCA Counter Control Register (D8h)

| 7             | 6               | 5                                                                                                              | 4                                                        | 3                                         | 2              | 1            | 0 |  |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------|----------------|--------------|---|--|--|--|

| CF            | CR              | -                                                                                                              | - CCF4 CCF3 CCF2 CCF1 CCF0                               |                                           |                |              |   |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                    |                                                          |                                           |                |              |   |  |  |  |

| 7             | CF              | Set by hardw<br>CMOD is set                                                                                    | . CF                                                     | ag<br>counter rolls<br>ware or softwa     |                |              |   |  |  |  |

| 6             | CR              | Must be clea                                                                                                   | ,                                                        | ol bit<br>re to turn the l<br>PCA counter |                | off.         |   |  |  |  |

| 5             | -               | Reserved<br>The value re                                                                                       | ad from this b                                           | it is indetermi                           | nate. Do not s | et this bit. |   |  |  |  |

| 4             | CCF4            | Must be clea                                                                                                   | <b>e 4 interrupt</b> f<br>red by softwa<br>vare when a n | •                                         | re occurs.     |              |   |  |  |  |

| 3             | CCF3            | Must be clea                                                                                                   | <b>a 3 interrupt</b> f<br>red by softwa<br>vare when a n | •                                         | re occurs.     |              |   |  |  |  |

| 2             | CCF2            | Must be clea                                                                                                   | e 2 interrupt f<br>red by softwa<br>vare when a n        | •                                         | re occurs.     |              |   |  |  |  |

| 1             | CCF1            | PCA Module 1 interrupt flag<br>Must be cleared by software.<br>Set by hardware when a match or capture occurs. |                                                          |                                           |                |              |   |  |  |  |

| 0             | CCF0            | Must be clea                                                                                                   | e <b>0 interrupt</b> f<br>red by softwa<br>vare when a n | -                                         | re occurs.     |              |   |  |  |  |

Reset Value = 00X0 0000b Not bit addressable

The watchdog timer function is implemented in module 4 (See Figure 17).

The PCA interrupt system is shown in Figure 15.

The SADEN byte is selected so that each slave may be addressed separately. For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1.To communicate with slave A only, the master must send an address where bit 0 is clear (e. g. 1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e. g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e. g. 1111 0001b).

#### **Broadcast Address**

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e. g. :

SADDR0101 0110b SADEN1111 1100b Broadcast =SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

Slave A:SADDR1111 0001b SADEN1111 1010b Broadcast1111 1X11b,

Slave B:SADDR1111 0011b SADEN1111 1001b Broadcast1111 1X11B,

Slave C:SADDR=1111 0011b <u>SADEN1111 1101b</u> Broadcast1111 1111b

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

Reset AddressesOn reset, the SADDR and SADEN registers are initialized to 00h, i. e. the given and<br/>broadcast addresses are xxxx xxxxb (all don't-care bits). This ensures that the serial<br/>port will reply to any address, and so, that it is backwards compatible with the 80C51<br/>microcontrollers that do not support automatic address recognition.

| Baud Rates | F <sub>osc</sub> = 16 | . 384 MHz | F <sub>osc</sub> = 24MHz |           |  |

|------------|-----------------------|-----------|--------------------------|-----------|--|

|            | BRL                   | Error (%) | BRL                      | Error (%) |  |

| 115200     | 247                   | 1.23      | 243                      | 0.16      |  |

| 57600      | 238                   | 1.23      | 230                      | 0.16      |  |

| 38400      | 229                   | 1.23      | 217                      | 0.16      |  |

| 28800      | 220                   | 1.23      | 204                      | 0.16      |  |

| 19200      | 203                   | 0.63      | 178                      | 0.16      |  |

| 9600       | 149                   | 0.31      | 100                      | 0.16      |  |

| 4800       | 43                    | 1.23      | -                        | -         |  |

Table 39.

Example of Computed Value When X2=1, SMOD1=1, SPD=1

Table 40. Example of Computed Value When X2=0, SMOD1=0, SPD=0

| Baud Rates | F <sub>OSC</sub> = 16 | . 384 MHz | F <sub>OSC</sub> = 24MHz |           |  |

|------------|-----------------------|-----------|--------------------------|-----------|--|

|            | BRL                   | Error (%) | BRL                      | Error (%) |  |

| 4800       | 247                   | 1.23      | 243                      | 0.16      |  |

| 2400       | 238                   | 1.23      | 230                      | 0.16      |  |

| 1200       | 220                   | 1.23      | 202                      | 3.55      |  |

| 600        | 185                   | 0.16      | 152                      | 0.16      |  |

The baud rate generator can be used for mode 1 or 3 (refer to Figure 23.), but also for mode 0 for UART, thanks to the bit SRC located in BDRCON register (Table 47.)

### **UART Registers**

#### Table 41. SADEN Register

SADEN - Slave Address Mask Register for UART (B9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

#### Table 42. SADDR Register

SADDR - Slave Address Register for UART (A9h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b

## Registers

The PCA interrupt vector is located at address 0033H, the SPI interrupt vector is located at address 0043H and Keyboard interrupt vector is located at address 004BH. All other vectors addresses are the same as standard C52 devices.

#### Table 48. Priority Level Bit Values

| IPH. x | IPL. x | Interrupt Level Priority |

|--------|--------|--------------------------|

| 0      | 0      | 0 (Lowest)               |

| 0      | 1      | 1                        |

| 1      | 0      | 2                        |

| 1      | 1      | 3 (Highest)              |

A low-priority interrupt can be interrupted by a high priority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

## Table 61. KBLS Register

KBLS-Keyboard Level Selector Register (9Ch)

| 7             | 6               | 5             | 5 4 3 2 1 0                                                                                                                                                   |                                                    |  |  |  |  |  |  |

|---------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|

| KBLS7         | KBLS6           | KBLS5         | KBLS1                                                                                                                                                         | KBLS0                                              |  |  |  |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description   |                                                                                                                                                               |                                                    |  |  |  |  |  |  |

| 7             | KBLS7           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on F |  |  |  |  |  |  |

| 6             | KBLS6           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection on<br>detection on F |  |  |  |  |  |  |

| 5             | KBLS5           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on F |  |  |  |  |  |  |

| 4             | KBLS4           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection on<br>detection on F |  |  |  |  |  |  |

| 3             | KBLS3           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection on<br>detection on F |  |  |  |  |  |  |

| 2             | KBLS2           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on F |  |  |  |  |  |  |

| 1             | KBLS1           | Cleared to en | <b>Keyboard line 1 Level Selection bit</b><br>Cleared to enable a low level detection on Port line 1.<br>Set to enable a high level detection on Port line 1. |                                                    |  |  |  |  |  |  |

| 0             | KBLS0           | Cleared to en |                                                                                                                                                               | election bit<br>vel detection of<br>detection on F |  |  |  |  |  |  |

Reset Value= 0000 0000b

## Table 66. Status in Master Transmitter Mode

|               |                                                                 | Application software response                                            |                  |                  |                  |                  |                                                                                                                                                                                                                                                   |

|---------------|-----------------------------------------------------------------|--------------------------------------------------------------------------|------------------|------------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status        | Status of the Two-                                              |                                                                          |                  | To SSC           | CON              |                  |                                                                                                                                                                                                                                                   |

| Code<br>SSSTA | wire Bus and Two-<br>wire Hardware                              | To/From SSDAT                                                            | SSSTA            | SSSTO            | SSI              | SSAA             | Next Action Taken by Two-wire Hardware                                                                                                                                                                                                            |

| 08h           | A START condition has been transmitted                          | Write SLA+W                                                              | x                | 0                | 0                | x                | SLA+W will be transmitted.                                                                                                                                                                                                                        |

| 10            | A repeated START                                                | Write SLA+W                                                              | х                | 0                | 0                | x                | SLA+W will be transmitted.                                                                                                                                                                                                                        |

| 10h           | condition has been<br>transmitted                               | Write SLA+R                                                              | х                | 0                | 0                | x                | SLA+R will be transmitted.<br>Logic will switch to master receiver mode                                                                                                                                                                           |

| 401           | SLA+W has been                                                  | Write data byte<br>No SSDAT action                                       | 0                | 0                | 0                | X<br>X           | Data byte will be transmitted.<br>Repeated START will be transmitted.<br>STOP condition will be transmitted and SSSTO flag                                                                                                                        |

| 18h           | transmitted; ACK has<br>been received                           | No SSDAT action                                                          | 0                | 1                | 0                | x<br>x           | will be reset.<br>STOP condition followed by a START condition will<br>be transmitted and SSSTO flag will be reset.                                                                                                                               |

| 20h           | SLA+W has been<br>transmitted; NOT ACK<br>has been received     | Write data byte<br>No SSDAT action<br>No SSDAT action<br>No SSDAT action | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1 | 0<br>0<br>0<br>0 | x<br>x<br>x<br>x | Data byte will be transmitted.<br>Repeated START will be transmitted.<br>STOP condition will be transmitted and SSSTO flag<br>will be reset.<br>STOP condition followed by a START condition will<br>be transmitted and SSSTO flag will be reset. |

| 28h           | Data byte has been<br>transmitted; ACK has<br>been received     | Write data byte<br>No SSDAT action<br>No SSDAT action<br>No SSDAT action | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1 | 0<br>0<br>0<br>0 | x<br>x<br>x<br>x | Data byte will be transmitted.<br>Repeated START will be transmitted.<br>STOP condition will be transmitted and SSSTO flag<br>will be reset.<br>STOP condition followed by a START condition will<br>be transmitted and SSSTO flag will be reset. |

| 30h           | Data byte has been<br>transmitted; NOT ACK<br>has been received | Write data byte<br>No SSDAT action<br>No SSDAT action<br>No SSDAT action | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1 | 0<br>0<br>0<br>0 | x<br>x<br>x<br>x | Data byte will be transmitted.<br>Repeated START will be transmitted.<br>STOP condition will be transmitted and SSSTO flag<br>will be reset.<br>STOP condition followed by a START condition will<br>be transmitted and SSSTO flag will be reset. |

| 38h           | Arbitration lost in                                             | No SSDAT action                                                          | 0                | 0                | 0                | x                | Two-wire bus will be released and not addressed slave mode will be entered.                                                                                                                                                                       |

| 2011          | SLA+W or data bytes                                             | No SSDAT action                                                          | 1                | 0                | 0                | х                | A START condition will be transmitted when the bus becomes free.                                                                                                                                                                                  |

#### Table 67. Status in Master Receiver Mode

|                |                                         | Appli           | cation soft | ware respo | nse |      |                                                                                                |

|----------------|-----------------------------------------|-----------------|-------------|------------|-----|------|------------------------------------------------------------------------------------------------|

| Status<br>Code | Status of the Two-<br>wire Bus and Two- |                 |             | To SSC     | CON |      |                                                                                                |

| SSSTA          | wire Hardware                           | To/From SSDAT   | SSSTA       | SSSTO      | SSI | SSAA | Next Action Taken by Two-wire Hardware                                                         |

| 08h            | A START condition has been transmitted  | Write SLA+R     | х           | 0          | 0   | x    | SLA+R will be transmitted.                                                                     |

|                | A repeated START                        | Write SLA+R     | х           | 0          | 0   | x    | SLA+R will be transmitted.                                                                     |

| 10h            | condition has been<br>transmitted       | Write SLA+W     | х           | 0          | 0   | x    | SLA+W will be transmitted.<br>Logic will switch to master transmitter mode.                    |

| 38h            | Arbitration lost in<br>SLA+R or NOT ACK | No SSDAT action | 0           | 0          | 0   | x    | Two-wire bus will be released and not addressed slave mode will be entered.                    |

| 301            | bit                                     | No SSDAT action | 1           | 0          | 0   | х    | A START condition will be transmitted when the bus becomes free.                               |

| 40h            | SLA+R has been<br>transmitted; ACK has  | No SSDAT action | 0           | 0          | 0   | 0    | Data byte will be received and NOT ACK will be returned.                                       |

|                | been received                           | No SSDAT action | 0           | 0          | 0   | 1    | Data byte will be received and ACK will be returned.                                           |

|                |                                         | No SSDAT action | 1           | 0          | 0   | х    | Repeated START will be transmitted.                                                            |

| 48h            | SLA+R has been<br>transmitted; NOT ACK  | No SSDAT action | 0           | 1          | 0   | Х    | STOP condition will be transmitted and SSSTO flag will be reset.                               |

|                | has been received                       | No SSDAT action | 1           | 1          | 0   | x    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |

| 50h            | Data byte has been<br>received: ACK has | Read data byte  | 0           | 0          | 0   | 0    | Data byte will be received and NOT ACK will be returned.                                       |

|                | been returned                           | Read data byte  | 0           | 0          | 0   | 1    | Data byte will be received and ACK will be returned.                                           |

|                |                                         | Read data byte  | 1           | 0          | 0   | х    | Repeated START will be transmitted.                                                            |

| 58h            | Data byte has been received; NOT ACK    | Read data byte  | 0           | 1          | 0   | Х    | STOP condition will be transmitted and SSSTO flag will be reset.                               |

|                | has been returned                       | Read data byte  | 1           | 1          | 0   | x    | STOP condition followed by a START condition will be transmitted and SSSTO flag will be reset. |

AT89C51ID2

## **Functional Description**

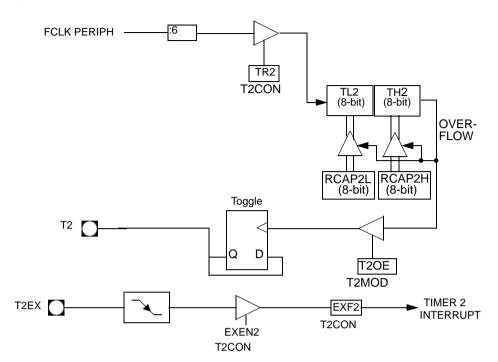

Figure 37 shows a detailed structure of the SPI Module.

Figure 37. SPI Module Block Diagram

#### **Operating Modes**

The Serial Peripheral Interface can be configured in one of the two modes: Master mode or Slave mode. The configuration and initialization of the SPI Module is made through one register:

• The Serial Peripheral Control register (SPCON)

Once the SPI is configured, the data exchange is made using:

- SPCON

- The Serial Peripheral STAtus register (SPSTA)

- The Serial Peripheral DATa register (SPDAT)

During an SPI transmission, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (SCK) synchronizes shifting and sampling on the two serial data lines (MOSI and MISO). A Slave Select line (SS) allows individual selection of a Slave SPI device; Slave devices that are not selected do not interfere with SPI bus activities.

When the Master device transmits data to the Slave device via the MOSI line, the Slave device responds by sending data to the Master device via the MISO line. This implies full-duplex transmission with both data out and data in synchronized with the same clock (Figure 38).

## Hardware Watchdog Timer

The WDT is intended as a recovery method in situations where the CPU may be subjected to software upset. The WDT consists of a 14-bit counter and the WatchDog Timer ReSeT (WDTRST) SFR. The WDT is by default disabled from exiting reset. To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, it will increment every machine cycle while the oscillator is running and there is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive an output RESET HIGH pulse at the RST-pin.

**Using the WDT** To enable the WDT, user must write 01EH and 0E1H in sequence to the WDTRST, SFR location 0A6H. When WDT is enabled, the user needs to service it by writing to 01EH and 0E1H to WDTRST to avoid WDT overflow. The 14-bit counter overflows when it reaches 16383 (3FFFH) and this will reset the device. When WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 16383 machine cycle. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST-pin. The RESET pulse duration is 96 x T<sub>CLK PERIPH</sub>, where T<sub>CLK PERIPH</sub> = 1/F<sub>CLK</sub> PERIPH. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.

To have a more powerful WDT, a  $2^7$  counter has been added to extend the Time-out capability, ranking from 16ms to 2s @  $F_{OSCA}$  = 12MHz. To manage this feature, refer to WDTPRG register description, Table 82.

Table 82.

WDTRST Register

WDTRST - Watchdog Reset Register (0A6h)

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - |

Reset Value = XXXX XXXXb

Write only, this SFR is used to reset/enable the WDT by writing 01EH then 0E1H in sequence.

#### Table 83. WDTPRG Register

WDTPRG - Watchdog Timer Out Register (0A7h)

| 7             | 6               | 5                                                                                                                                                                         | 4                                                                                                                                | 3                                                                                                                                                       | 2                                                                                            | 1                                                                                      | 0  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----|

| -             | -               | -                                                                                                                                                                         | -                                                                                                                                | -                                                                                                                                                       | S2                                                                                           | <b>S</b> 1                                                                             | S0 |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                               |                                                                                                                                  |                                                                                                                                                         |                                                                                              |                                                                                        |    |

| 7             | -               |                                                                                                                                                                           |                                                                                                                                  |                                                                                                                                                         |                                                                                              |                                                                                        |    |

| 6             | -               |                                                                                                                                                                           |                                                                                                                                  |                                                                                                                                                         |                                                                                              |                                                                                        |    |

| 5             | -               | Reserved<br>The value rea                                                                                                                                                 | ad from this bi                                                                                                                  | t is undetermi                                                                                                                                          | ned. Do not try                                                                              | / to set this bit                                                                      |    |

| 4             | -               |                                                                                                                                                                           |                                                                                                                                  |                                                                                                                                                         |                                                                                              |                                                                                        |    |

| 3             | -               |                                                                                                                                                                           |                                                                                                                                  |                                                                                                                                                         |                                                                                              |                                                                                        |    |

| 2             | S2              | WDT Time-o                                                                                                                                                                | ut select bit                                                                                                                    | 2                                                                                                                                                       |                                                                                              |                                                                                        |    |

| 1             | S1              | WDT Time-o                                                                                                                                                                | ut select bit                                                                                                                    | 1                                                                                                                                                       |                                                                                              |                                                                                        |    |

| 0             | S0              | WDT Time-o                                                                                                                                                                | ut select bit                                                                                                                    | 0                                                                                                                                                       |                                                                                              |                                                                                        |    |

|               |                 | S2S1         S0           0         0           0         1           0         1           1         0           1         1           1         1           1         1 | 1 $(2^{15} - 1)$ m<br>0 $(2^{16} - 1)$ m<br>1 $(2^{17} - 1)$ m<br>0 $(2^{18} - 1)$ m<br>1 $(2^{19} - 1)$ m<br>0 $(2^{20} - 1)$ m | ime-out<br>achine cycles,<br>achine cycles,<br>achine cycles,<br>achine cycles,<br>achine cycles,<br>achine cycles,<br>achine cycles,<br>achine cycles, | 32.7 ms @ F,<br>65.5 ms @ F<br>131 ms @ F_c<br>262 ms @ F_c<br>542 ms @ F_c<br>1.05 s @ F_os | OSCA=12 MHz<br>OSCA=12 MHz<br>OSCA=12 MHz<br>OSCA=12 MHz<br>OSCA=12 MHz<br>OSCA=12 MHz |    |

Reset value = XXXX X000

# WDT During Power Down and Idle

In Power Down mode the oscillator stops, which means the WDT also stops. While in Power Down mode the user does not need to service the WDT. There are 2 methods of exiting Power Down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power Down mode. When Power Down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the AT89C51ID2 is reset. Exiting Power Down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is better to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the AT89C51ID2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

| Table 93. | Program | Lock bits | of the SSB |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

| Program           | n Lock I | Bits |                                                                       |

|-------------------|----------|------|-----------------------------------------------------------------------|

| Security<br>level | LB0      | LB1  | Protection description                                                |

| 1                 | U        | U    | No program lock features enabled.                                     |

| 2                 | Р        | U    | ISP programming of the Flash is disabled.                             |

| 3                 | Х        | Р    | Same as 2, also verify through ISP programming interface is disabled. |

Note: U: unprogrammed or "one" level.

P: programmed or "zero" level.

X: do not care

WARNING: Security level 2 and 3 should only be programmed after Flash and code verification.

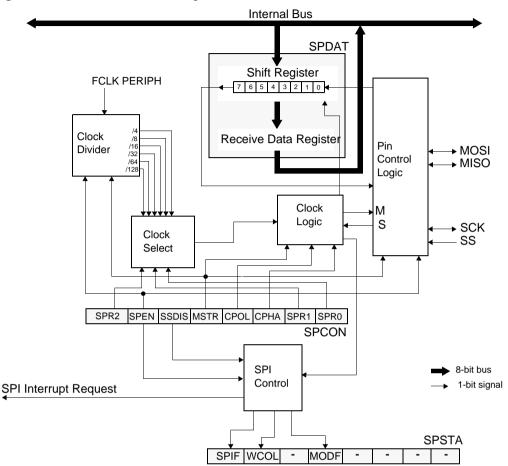

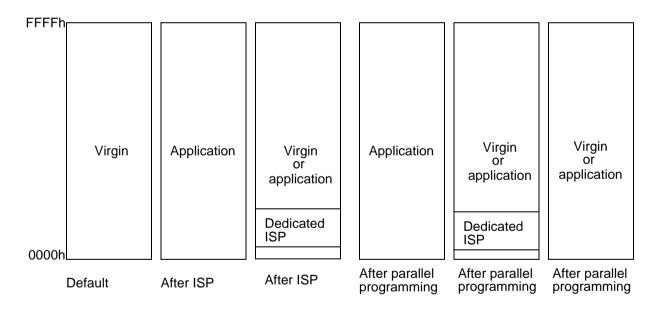

Flash Memory StatusAT89C51ID2 parts are delivered in standard with the ISP rom bootloader.

After ISP or parallel programming, the possible contents of the Flash memory are summarized on the figure below:

## **Memory Organization**

When the  $\overline{EA}$  pin high, the processor fetches instructions from internal program Flash. . If the  $\overline{EA}$  pin is tied low, all program memory fetches are from external memory.

## AT89C51ID2

#### **Functional Description**

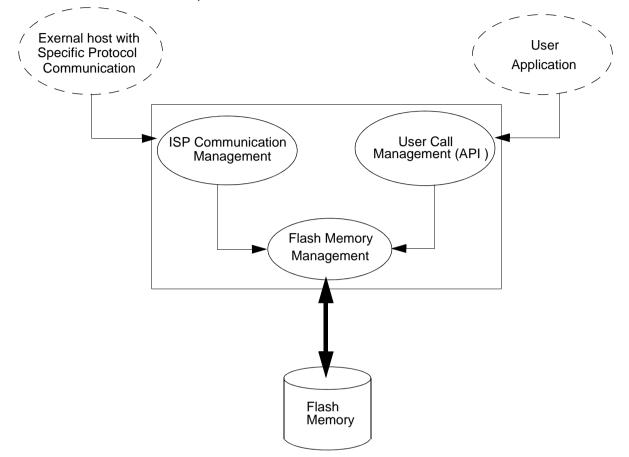

Figure 47. Bootloader Functional Description

On the above diagram, the on chip bootloader processes are:

ISP Communication Management

The purpose of this process is to manage the communication and its protocol between the on-chip bootloader and a external device. The on-chip ROM implement a serial protocol (see section Bootloader Protocol). This process translate serial communication frame (UART) into flash memory acess (read, write, erase ...).

User Call Management

Several Application Program Interface (API) calls are available for use by an application program to permit selective erasing and programming of Flash pages. All calls are made through a common interface (API calls), included in the ROM bootloader. The programming functions are selected by setting up the microcontroller's registers before making a call to a common entry point (0xFFF0). Results are returned in the registers. The purpose on this process is to translate the registers values into internal Flash Memory Management.

Flash Memory Management

This process manages low level access to flash memory (performs read and write access).

#### Table 95. Autobaud Performances (Continued)

| Frequency (MHz)<br>Baudrate (kHz) | 1.8432 | 2  | 2.4576 | 3  | 3.6864 | 4  | 5  | 6  | 7.3728 |

|-----------------------------------|--------|----|--------|----|--------|----|----|----|--------|

| 4800                              | ОК     | ОК | ОК     | ОК | ОК     | ОК | ОК | ОК | ОК     |

| 9600                              | ОК     | ОК | ОК     | ОК | ОК     | ОК | ОК | ОК | ОК     |

| 19200                             | ОК     | ОК | ОК     | ОК | ОК     | ОК | ОК | ОК | ОК     |

| 38400                             | -      | -  | ОК     | ОК | ОК     | ОК | ОК | ОК | ОК     |

| 57600                             | -      | -  | ОК     | -  | ОК     | ОК | ОК | ОК | ОК     |

| 115200                            | -      | -  | ОК     | -  | ОК     | -  | -  | -  | -      |

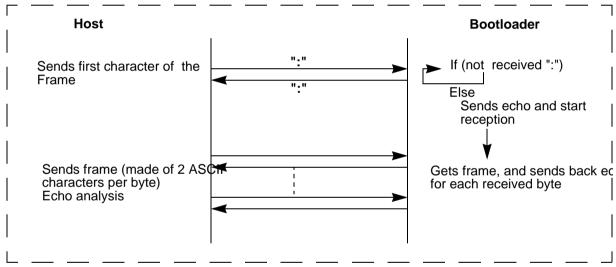

## Command Data Stream Protocol

All commands are sent using the same flow. Each frame sent by the host is echoed by the bootloader.

Figure 52. Command Flow

| Table 99. AC Parameters for a Fix | Clock |

|-----------------------------------|-------|

|-----------------------------------|-------|

| -М  |                                           |                              | -L                                                                                                                                                                                                                                                                                                              | Units                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|-------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Min | Мах                                       | Min                          | Мах                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 25  |                                           | 25                           |                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 35  |                                           | 35                           |                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   |                                           | 5                            |                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   |                                           | 5                            |                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | n 65                                      |                              | 65                                                                                                                                                                                                                                                                                                              | ns                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   |                                           | 5                            |                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 50  |                                           | 50                           |                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                         |