# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 84MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SDIO, SPI, UART/USART, USB OTG        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT          |

| Number of I/O              | 36                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 96K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                           |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f401ceu6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.9 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 62 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\$}$ -M4 with FPU.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

# 3.10 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 21 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 81 GPIOs can be connected to the 16 external interrupt lines.

# 3.11 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy at 25 °C. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 84 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 84 MHz while the maximum frequency of the high-speed APB domains is 84 MHz. The maximum allowed frequency of the low-speed APB domain is 42 MHz.

The devices embed a dedicated PLL (PLLI2S) which allows to achieve audio class performance. In this case, the I<sup>2</sup>S master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run) In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption.

- LPR is used in the Stop modes

The LP regulator mode is configured by software when entering Stop mode.

• Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Depending on the package, one or two external ceramic capacitors should be connected on the  $V_{CAP_1}$  and  $V_{CAP_2}$  pins. The  $V_{CAP_2}$  pin is only available for the LQFP100 and UFBGA100 packages.

All packages have the regulator ON feature.

#### 3.15.2 Regulator OFF

The Regulator OFF is available only on the UFBGA100, which features the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V12 voltage source through  $V_{CAP-1}$  and  $V_{CAP-2}$  pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 14: General operating conditions*.

The two 2.2  $\mu$ F V<sub>CAP</sub> ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 18: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V12 logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

|        | Pin     | Nun    | nber    |          |                                                      |          | e.            | -     | · ·                                                                          |                         |

|--------|---------|--------|---------|----------|------------------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------|-------------------------|

| UQFN48 | WLCSP49 | LQFP64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                          | Additional<br>functions |

| -      | -       | 39     | 65      | E10      | PC8                                                  | I/O      | FT            | -     | USART6_CK, TIM3_CH3,<br>SDIO_D0, EVENTOUT                                    | -                       |

| -      | -       | 40     | 66      | D12      | PC9                                                  | I/O      | FT            | -     | I2S_CKIN, I2C3_SDA,<br>TIM3_CH4, SDIO_D1,<br>MCO_2, EVENTOUT                 | -                       |

| 29     | D1      | 41     | 67      | D11      | PA8                                                  | I/O      | FT            | -     | I2C3_SCL, USART1_CK,<br>TIM1_CH1, OTG_FS_SOF,<br>MCO_1, EVENTOUT             | -                       |

| 30     | D2      | 42     | 68      | D10      | PA9                                                  | I/O      | FT            | -     | I2C3_SMBA, USART1_TX,<br>TIM1_CH2, EVENTOUT                                  | OTG_FS_VBUS             |

| 31     | C2      | 43     | 69      | C12      | PA10                                                 | I/O      | FT            | -     | USART1_RX, TIM1_CH3,<br>OTG_FS_ID, EVENTOUT                                  | -                       |

| 32     | C1      | 44     | 70      | B12      | PA11                                                 | I/O      | FT            | -     | USART1_CTS, USART6_TX,<br>TIM1_CH4, OTG_FS_DM,<br>EVENTOUT                   | -                       |

| 33     | C3      | 45     | 71      | A12      | PA12                                                 | I/O      | FT            | -     | USART1_RTS, USART6_RX,<br>TIM1_ETR, OTG_FS_DP,<br>EVENTOUT                   | -                       |

| 34     | B3      | 46     | 72      | A11      | PA13 (JTMS-<br>SWDIO)                                | I/O      | FT            | -     | JTMS-SWDIO, EVENTOUT                                                         | -                       |

| -      | -       | -      | 73      | C11      | VCAP2                                                | S        | -             | -     | -                                                                            | -                       |

| 35     | B1      | 47     | 74      | F11      | VSS                                                  | S        | -             | -     | -                                                                            | -                       |

| 36     | -       | 48     | 75      | G11      | VDD                                                  | S        | -             | -     | -                                                                            | -                       |

| -      | B2      | -      | -       | -        | VDD                                                  | S        | -             | -     | -                                                                            | -                       |

| 37     | A1      | 49     | 76      | A10      | PA14 (JTCK-<br>SWCLK)                                | I/O      | FT            | -     | JTCK-SWCLK, EVENTOUT                                                         | -                       |

| 38     | A2      | 50     | 77      | A9       | PA15 (JTDI)                                          | I/O      | FT            | -     | JTDI, SPI1_NSS,<br>SPI3_NSS/I2S3_WS,<br>TIM2_CH1/TIM2_ETR, JTDI,<br>EVENTOUT | -                       |

| -      | -       | 51     | 78      | B11      | PC10                                                 | I/O      | FT            | -     | SPI3_SCK/I2S3_CK,<br>SDIO_D2, EVENTOUT                                       | -                       |

| -      | -       | 52     | 79      | C10      | PC11                                                 | I/O      | FT            | -     | I2S3ext_SD, SPI3_MISO,<br>SDIO_D3, EVENTOUT                                  | -                       |

| -      | -       | 53     | 80      | B10      | PC12                                                 | I/O      | FT            | -     | SPI3_MOSI/I2S3_SD,<br>SDIO_CK, EVENTOUT                                      | -                       |

| -      | -       | -      | 81      | C9       | PD0                                                  | I/O      | FT            | -     | EVENTOUT                                                                     | -                       |

Table 8. STM32F401xD/xE pin definitions (continued)

|        | Pir     | n Nur                                    | nber |          |                                                      |          | re            |       |                     |                         |

|--------|---------|------------------------------------------|------|----------|------------------------------------------------------|----------|---------------|-------|---------------------|-------------------------|

| UQFN48 | WLCSP49 | WLCSP49<br>LQFP64<br>LQFP100<br>UFBGA100 |      | UFBGA100 | Pin name<br>(function<br>after reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions | Additional<br>functions |

| 47     | A6      | 63                                       | 99   | -        | VSS                                                  | S        | -             | -     | -                   | -                       |

| -      | B6      | -                                        | -    | H3       | PDR_ON                                               | I        | FT -          |       | -                   | -                       |

| 48     | A7      | 64                                       | 100  | -        | VDD                                                  | S        | -             | -     | -                   | -                       |

Table 8. STM32F401xD/xE pin definitions (continued)

1. Function availability depends on the chosen device.

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

The speed should not exceed 2 MHz with a maximum load of 30 pF.

These I/Os must not be used as a current source (e.g. to drive an LED).

Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F401xx reference manual.

4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

5. If the device is delivered in an UFBGA100 and the BYPASS\_REG pin is set to VDD (Regulator off/internal reset ON mode), then PA0 is used as an internal Reset (active low)

5

DocID025644 Rev 3

| 4          |

|------------|

| Ġ          |

| Ň          |

| <u> </u>   |

| ω          |

| <b>U</b> I |

|        |      |              |           |                     |                          |                    |                                       |                          |                                 |        | · ·           |         |      |             |      |      |              |

|--------|------|--------------|-----------|---------------------|--------------------------|--------------------|---------------------------------------|--------------------------|---------------------------------|--------|---------------|---------|------|-------------|------|------|--------------|

|        | Port | AF00         | AF01      | AF02                | AF03                     | AF04               | AF05                                  | AF06                     | AF07                            | AF08   | AF09          | AF10    | AF11 | AF12        | AF13 | AF14 | AF15         |

|        | Ton  | SYS_AF       | TIM1/TIM2 | TIM3/<br>TIM4/ TIM5 | TIM9/<br>TIM10/<br>TIM11 | I2C1/I2C2/<br>I2C3 | SPI1/SPI2/<br>I2S2/SPI3/<br>I2S3/SPI4 | SPI2/I2S2/<br>SPI3/ I2S3 | SPI3/I2S3/<br>USART1/<br>USART2 | USART6 | 12C2/<br>12C3 | OTG1_FS |      | SDIO        |      |      |              |

|        | PB0  | -            | TIM1_CH2N | TIM3_CH3            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB1  | -            | TIM1_CH3N | TIM3_CH4            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB2  | -            | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB3  | JTDO-<br>SWO | TIM2_CH2  | -                   | -                        | -                  | SPI1_SCK                              | SPI3_SCK/<br>I2S3_CK     | -                               | -      | I2C2_SDA      | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB4  | JTRST        | -         | TIM3_CH1            | -                        | -                  | SPI1_<br>MISO                         | SPI3_MISO                | I2S3ext_S<br>D                  | -      | I2C3_SDA      | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB5  | -            | -         | TIM3_CH2            | -                        | I2C1_<br>SMBA      | SPI1<br>_MOSI                         | SPI3_MOSI/<br>I2S3_SD    | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB6  | -            | -         | TIM4_CH1            | -                        | I2C1_SCL           | -                                     | -                        | USART1_<br>TX                   | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

| Port B | PB7  | -            | -         | TIM4_CH2            | -                        | I2C1_SDA           | -                                     | -                        | USART1_<br>RX                   | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB8  | -            | -         | TIM4_CH3            | TIM10_CH1                | I2C1_SCL           | -                                     | -                        | -                               | -      | -             | -       | -    | SDIO_<br>D4 | -    | -    | EVENT<br>OUT |

|        | PB9  | -            | -         | TIM4_CH4            | TIM11_CH1                | I2C1_SDA           | SPI2_NSS/I<br>2S2_WS                  | -                        | -                               | -      | -             | -       | -    | SDIO_<br>D5 | -    | -    | EVENT<br>OUT |

|        | PB10 | -            | TIM2_CH3  | -                   | -                        | I2C2_SCL           | SPI2_SCK/I<br>2S2_CK                  | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB12 | -            | TIM1_BKIN | -                   | -                        | I2C2_<br>SMBA      | SPI2_NSS/I<br>2S2_WS                  | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB13 | -            | TIM1_CH1N | -                   | -                        | -                  | SPI2_SCK/I<br>2S2_CK                  | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB14 | -            | TIM1_CH2N | -                   | -                        | -                  | SPI2_MISO                             | I2S2ext_SD               | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

|        | PB15 | RTC_<br>REFN | TIM1_CH3N | -                   | -                        | -                  | SPI2_MOSI<br>/I2S2_SD                 | -                        | -                               | -      | -             | -       | -    | -           | -    | -    | EVENT<br>OUT |

Table 9. Alternate function mapping (continued)

STM32F401xD STM32F401xE

Pinouts and pin description

5

| 4        |

|----------|

| <u>%</u> |

| 3        |

| Οī       |

|        |      |        |           |                     |                          |                    |                                       |                          |                                 |        | ,             |         |      |              |      |      |              |

|--------|------|--------|-----------|---------------------|--------------------------|--------------------|---------------------------------------|--------------------------|---------------------------------|--------|---------------|---------|------|--------------|------|------|--------------|

|        |      | AF00   | AF01      | AF02                | AF03                     | AF04               | AF05                                  | AF06                     | AF07                            | AF08   | AF09          | AF10    | AF11 | AF12         | AF13 | AF14 | AF15         |

| Port   | Port | SYS_AF | TIM1/TIM2 | TIM3/<br>TIM4/ TIM5 | TIM9/<br>TIM10/<br>TIM11 | I2C1/I2C2/<br>I2C3 | SPI1/SPI2/<br>I2S2/SPI3/<br>I2S3/SPI4 | SPI2/I2S2/<br>SPI3/ I2S3 | SPI3/I2S3/<br>USART1/<br>USART2 | USART6 | 12C2/<br>12C3 | OTG1_FS |      | SDIO         |      |      |              |

|        | PD0  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD1  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD2  | -      | -         | TIM3_ETR            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | SDIO_<br>CMD | -    | -    | EVENT<br>OUT |

|        | PD3  | -      | -         | -                   | -                        | -                  | SPI2_SCK/<br>I2S2_CK                  | -                        | USART2_<br>CTS                  |        | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD4  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>RTS                  |        | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD5  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>TX                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD6  | -      | -         | -                   | -                        | -                  | SPI3_MOSI<br>/I2S3_SD                 | -                        | USART2_<br>RX                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

| Q      | PD7  | -      | -         | -                   | -                        | -                  | -                                     | -                        | USART2_<br>CK                   | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

| Port D | PD8  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD9  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD10 | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD11 | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD12 | -      | -         | TIM4_CH1            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD13 | -      | -         | TIM4_CH2            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD14 | -      | -         | TIM4_CH3            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

|        | PD15 | -      | -         | TIM4_CH4            | -                        | -                  | -                                     | -                        | -                               | -      | -             | -       | -    | -            | -    | -    | EVENT<br>OUT |

STM32F401xD STM32F401xE

Pinouts and pin description

| _ |      |        |           |                     | Т                        | able 9. A          | lternate f                            | unction ma               | apping (c                       | ontinue | d)            |         |      |      |      |      |              |

|---|------|--------|-----------|---------------------|--------------------------|--------------------|---------------------------------------|--------------------------|---------------------------------|---------|---------------|---------|------|------|------|------|--------------|

|   | AF00 | AF01   | AF02      | AF03                | AF04                     | AF05               | AF06                                  | AF07                     | AF08                            | AF09    | AF10          | AF11    | AF12 | AF13 | AF14 | AF15 |              |

|   | Port | SYS_AF | TIM1/TIM2 | TIM3/<br>TIM4/ TIM5 | TIM9/<br>TIM10/<br>TIM11 | I2C1/I2C2/<br>I2C3 | SPI1/SPI2/<br>I2S2/SPI3/<br>I2S3/SPI4 | SPI2/I2S2/<br>SPI3/ I2S3 | SPI3/I2S3/<br>USART1/<br>USART2 | USART6  | 12C2/<br>12C3 | OTG1_FS |      | SDIO |      |      |              |

|   | PHO  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -       | -             | -       | -    | -    | -    | -    | EVENT<br>OUT |

|   | PH1  | -      | -         | -                   | -                        | -                  | -                                     | -                        | -                               | -       | -             | -       | -    | -    | -    | -    | EVENT<br>OUT |

# 6.3 Operating conditions

# 6.3.1 General operating conditions

| Table 14 | General | operating | conditions |

|----------|---------|-----------|------------|

|----------|---------|-----------|------------|

| Symbol                     | Parameter                                                                                                      | Conditions                                                                                                          | Min                 | Тур  | Max                 | Unit |

|----------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------|------|---------------------|------|

| £                          |                                                                                                                | Power Scale3: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x01                                              | 0                   | -    | 60                  |      |

| f <sub>HCLK</sub>          | Internal AHB clock frequency                                                                                   | Power Scale2: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x10                                              | 0                   | -    | 84                  | MHz  |

| f <sub>PCLK1</sub>         | Internal APB1 clock frequency                                                                                  |                                                                                                                     | 0                   | -    | 42                  |      |

| f <sub>PCLK2</sub>         | Internal APB2 clock frequency                                                                                  |                                                                                                                     | 0                   | -    | 84                  |      |

| $V_{DD}$                   | Standard operating voltage                                                                                     |                                                                                                                     | 1.7 <sup>(1)</sup>  | -    | 3.6                 |      |

| V <sub>DDA</sub><br>(2)(3) | Analog operating voltage<br>(ADC limited to 1.2 M samples)                                                     | Must be the same potential as $V_{DD}^{(4)}$                                                                        | 1.7 <sup>(1)</sup>  | -    | 2.4                 |      |

| (2)(3)                     | Analog operating voltage<br>ADC limited to 2.4 M samples)                                                      |                                                                                                                     | 2.4                 | -    | 3.6                 |      |

| V <sub>BAT</sub>           | Backup operating voltage                                                                                       |                                                                                                                     | 1.65                | -    | 3.6                 |      |

| M                          | Regulator ON: 1.2 V internal                                                                                   | VOS[1:0] bits in PWR_CR register = 0x01<br>Max frequency 60 MHz                                                     | 1.08 <sup>(5)</sup> | 1.14 | 1.20 <sup>(5)</sup> | V    |

| V <sub>12</sub>            | voltage on $V_{CAP_1}/V_{CAP_2}$ pins                                                                          | tage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins VOS[1:0] bits in PWR_CR register = 0x10<br>Max frequency 84 MHz |                     | 1.26 | 1.32 <sup>(5)</sup> |      |

|                            | Regulator OFF: 1.2 V external                                                                                  | Max. frequency 60 MHz.                                                                                              | 1.1                 | 1.14 | 1.2                 |      |

| V <sub>12</sub>            | voltage must be supplied on $V_{CAP_1}/V_{CAP_2}$ pins                                                         | Max. frequency 84 MHz.                                                                                              | 1.2                 | 1.26 | 1.32                |      |

|                            | Input voltage on RST and FT                                                                                    | $2 \text{ V} \leq \text{ V}_{DD} \leq 3.6 \text{ V}$                                                                | -0.3                | -    | 5.5                 |      |

| $V_{IN}$                   | pins <sup>(6)</sup>                                                                                            | $V_{DD} \leq 2 V$                                                                                                   | -0.3                | -    | 5.2                 |      |

|                            | Input voltage on BOOT0 pin                                                                                     |                                                                                                                     | 0                   | -    | 9                   |      |

|                            |                                                                                                                | UFQFPN48                                                                                                            | -                   | -    | 625                 |      |

|                            |                                                                                                                | WLCSP49                                                                                                             | -                   | -    | 392                 | mW   |

| PD                         | Maximum allowed package power dissipation for suffix 7 <sup>(7)</sup>                                          | LQFP64                                                                                                              | -                   | -    | 313                 |      |

|                            | The second s | LQFP100                                                                                                             | -                   | -    | 465                 |      |

|                            |                                                                                                                | UFBGA100                                                                                                            | -                   | -    | 323                 |      |

### 6.3.5 Embedded reset and power control block characteristics

The parameters given in *Table 19* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage @ 3.3V.

| Symbol                              | Parameter                | Conditions                  | Min                 | Тур  | Max  | Unit |  |

|-------------------------------------|--------------------------|-----------------------------|---------------------|------|------|------|--|

|                                     |                          | PLS[2:0]=000 (rising edge)  | 2.09                | 2.14 | 2.19 |      |  |

|                                     |                          | PLS[2:0]=000 (falling edge) | 1.98                | 2.04 | 2.08 |      |  |

|                                     |                          | PLS[2:0]=001 (rising edge)  | 2.23                | 2.30 | 2.37 |      |  |

|                                     |                          | PLS[2:0]=001 (falling edge) | 2.13                | 2.19 | 2.25 |      |  |

|                                     |                          | PLS[2:0]=010 (rising edge)  | 2.39                | 2.45 | 2.51 |      |  |

|                                     |                          | PLS[2:0]=010 (falling edge) | 2.29                | 2.35 | 2.39 |      |  |

|                                     |                          | PLS[2:0]=011 (rising edge)  | 2.54                | 2.60 | 2.65 |      |  |

| M                                   | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.44                | 2.51 | 2.56 | V    |  |

| V <sub>PVD</sub>                    | detector level selection | PLS[2:0]=100 (rising edge)  | 2.70                | 2.76 | 2.82 | V    |  |

|                                     |                          | PLS[2:0]=100 (falling edge) | 2.59                | 2.66 | 2.71 |      |  |

|                                     |                          | PLS[2:0]=101 (rising edge)  | 2.86                | 2.93 | 2.99 |      |  |

|                                     |                          | PLS[2:0]=101 (falling edge) | 2.65                | 2.84 | 3.02 |      |  |

|                                     |                          | PLS[2:0]=110 (rising edge)  | 2.96                | 3.03 | 3.10 |      |  |

|                                     |                          | PLS[2:0]=110 (falling edge) | 2.85                | 2.93 | 2.99 |      |  |

|                                     |                          | PLS[2:0]=111 (rising edge)  | 3.07                | 3.14 | 3.21 |      |  |

|                                     |                          | PLS[2:0]=111 (falling edge) | 2.95                | 3.03 | 3.09 |      |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup> | PVD hysteresis           |                             | -                   | 100  | -    | mV   |  |

|                                     | Power-on/power-down      | Falling edge                | 1.60 <sup>(1)</sup> | 1.68 | 1.76 | v    |  |

| V <sub>POR/PDR</sub>                | reset threshold          | Rising edge                 | 1.64                | 1.72 | 1.80 | v    |  |

| V <sub>PDRhyst</sub> <sup>(2)</sup> | PDR hysteresis           |                             | -                   | 40   | -    | mV   |  |

|                                     | Brownout level 1         | Falling edge                | 2.13                | 2.19 | 2.24 |      |  |

| V <sub>BOR1</sub>                   | threshold                | Rising edge                 | 2.23                | 2.29 | 2.33 |      |  |

| N/                                  | Brownout level 2         | Falling edge                | 2.44                | 2.50 | 2.56 | V    |  |

| V <sub>BOR2</sub>                   | threshold                | Rising edge                 | 2.53                | 2.59 | 2.63 | V    |  |

| V                                   | Brownout level 3         | Falling edge                | 2.75                | 2.83 | 2.88 |      |  |

| V <sub>BOR3</sub>                   | threshold                | Rising edge                 | 2.85                | 2.92 | 2.97 | 1    |  |

| V <sub>BORhyst</sub> <sup>(2)</sup> | BOR hysteresis           |                             | -                   | 100  | -    | mV   |  |

| T <sub>RSTTEMPO</sub><br>(2)(3)     | POR reset timing         |                             | 0.5                 | 1.5  | 3.0  | ms   |  |

| Table 22. Typical and maximum current consumption in run mode, code with data processing     |  |

|----------------------------------------------------------------------------------------------|--|

| (ART accelerator enabled except prefetch) running from Flash memory- V <sub>DD</sub> = 1.7 V |  |

| Symbol Paramet |                    |                                                           | £                          |      |                           | Max <sup>(1)</sup>        |                            |      |

|----------------|--------------------|-----------------------------------------------------------|----------------------------|------|---------------------------|---------------------------|----------------------------|------|

|                | Parameter          | Conditions                                                | f <sub>HCLK</sub><br>(MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                |                    |                                                           | 84                         | 23.2 | 24.5                      | 25.6                      | 26.6                       |      |

|                |                    |                                                           | 60                         | 15.1 | 16.3                      | 17.4                      | 18.4                       | -    |

|                |                    | External clock, all peripherals enabled <sup>(2)(3)</sup> | 40                         | 10.8 | 12.1                      | 13.2                      | 14.2                       |      |

|                |                    | - F- F                                                    | 30                         | 8.8  | 10.0                      | 11.1                      | 12.2                       |      |

|                | Supply current     |                                                           | 20                         | 6.9  | 8.0                       | 9.0                       | 10.1                       | mA   |

|                | in <b>Run mode</b> |                                                           | 84                         | 12.3 | 13.6                      | 14.7                      | 15.7                       |      |

|                |                    | External clock, all peripherals disabled <sup>(3)</sup>   | 60                         | 8.2  | 9.4                       | 10.5                      | 11.5                       |      |

|                |                    |                                                           | 40                         | 6.0  | 7.3                       | 8.3                       | 9.4                        |      |

|                |                    |                                                           | 30                         | 4.9  | 6.2                       | 7.2                       | 8.3                        |      |

|                |                    |                                                           | 20                         | 4.0  | 5.1                       | 6.1                       | 7.2                        |      |

1. Guaranteed by characterization, not tested in production unless otherwise specified.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

# Table 23. Typical and maximum current consumption in run mode, code with data processing (ART accelerator enabled except prefetch) running from Flash memory - $V_{DD}$ = 3.3 V

|                                                     |                    |                                                              | f                          |      | Max <sup>(1)</sup>        |                           |                            |                                                                          |

|-----------------------------------------------------|--------------------|--------------------------------------------------------------|----------------------------|------|---------------------------|---------------------------|----------------------------|--------------------------------------------------------------------------|

| Symbol                                              | Parameter          | Conditions                                                   | f <sub>HCLK</sub><br>(MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit                                                                     |

|                                                     |                    |                                                              | 84                         | 23.4 | 24.7                      | 25.8                      | 26.8                       |                                                                          |

| Supply currer<br>I <sub>DD</sub> in <b>Run mode</b> |                    | External clock,<br>all peripherals enabled <sup>(2)(3)</sup> | 60                         | 15.3 | 16.5                      | 17.6                      | 18.6                       |                                                                          |

|                                                     |                    |                                                              | 40                         | 11.0 | 12.3                      | 13.4                      | 14.4                       |                                                                          |

|                                                     |                    |                                                              | 30                         | 9.0  | 10.2                      | 11.3                      | 12.4                       |                                                                          |

|                                                     | Supply current     |                                                              | 20                         | 7.1  | 8.2                       | 9.2                       | 10.3                       | mΔ                                                                       |

|                                                     | in <b>Run mode</b> |                                                              | 84                         | 12.5 | 13.8                      | 14.9                      | 12.4<br>10.3<br>15.9       |                                                                          |

|                                                     |                    | External clock,<br>all peripherals disabled <sup>(3)</sup>   |                            | 60   | 8.4                       | 9.6                       | 10.7                       | IA =       105 °C       26.8       18.6       14.4       12.4       10.3 |

|                                                     |                    |                                                              | 40                         | 6.2  | 7.5                       | 8.5                       | 9.6                        |                                                                          |

|                                                     |                    |                                                              | 30                         | 5.1  | 6.4                       | 7.4                       | 8.5                        |                                                                          |

|                                                     |                    |                                                              | 20                         | 4.2  | 5.3                       | 6.3                       | 7.4                        |                                                                          |

1. Guaranteed by characterization, not tested in production unless otherwise specified.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2), add an additional power consumption of 1.6mA per ADC for the analog part.

| Perip                 | heral               | I <sub>DD</sub> (typ) | Unit   |

|-----------------------|---------------------|-----------------------|--------|

|                       | TIM1                | 5.71                  |        |

|                       | TIM9                | 2.86                  | -      |

|                       | TIM10               | 1.79                  |        |

|                       | TIM11               | 2.02                  |        |

|                       | ADC1 <sup>(2)</sup> | 2.98                  |        |

| APB2<br>(up to 84MHz) | SPI1                | 1.19                  | µA/MHz |

|                       | USART1              | 3.10                  |        |

|                       | USART6              | 2.86                  | -      |

|                       | SDIO                | 5.95                  | -      |

|                       | SPI4                | 1.31                  |        |

|                       | SYSCFG              | 0.71                  |        |

1. I2SMOD bit set in SPI\_I2SCFGR register, and then the I2SE bit set to enable I2S peripheral.

2. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

### 6.3.7 Wakeup time from low-power modes

The wakeup times given in *Table 34* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep modes: the wakeup event is WFE.

- WKUP (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$ =3.3 V.

| Table 34. Low-power mode wakeup timings <sup>(1)</sup> | Table 34 | ower | Low- | mode | wakeup | timings <sup>(1)</sup> |

|--------------------------------------------------------|----------|------|------|------|--------|------------------------|

|--------------------------------------------------------|----------|------|------|------|--------|------------------------|

| Symbol                                 | Parameter                                                                                   |   | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                  |

|----------------------------------------|---------------------------------------------------------------------------------------------|---|--------------------|--------------------|-----------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>    | Wakeup from Sleep mode                                                                      |   | 4                  | 6                  | CPU<br>clock<br>cycle |

| t <sub>WUSTOP</sub> <sup>(2)</sup>     | Wakeup from Stop mode, usage of main regulator                                              | - | 13.5               | 14.5               |                       |

|                                        | Wakeup from Stop mode, usage of main regulator, Flash memory in Deep power down mode        | - | 105                | 111                |                       |

|                                        | Wakeup from Stop mode, regulator in low power mode                                          | - | 21                 | 33                 | μs                    |

|                                        | Wakeup from Stop mode, regulator in low power mode,<br>Flash memory in Deep power down mode | - | 113                | 130                |                       |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup> | Wakeup from Standby mode                                                                    | - | 314                | 407                | μs                    |

1. Guaranteed by characterization, not tested in production.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  maximum value is given at -40 °C.

| Symbol                                     | Parameter                                           | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage               |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                |                                  | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>            |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>           |                                  | -                  | -      | 50                 | 113  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>           |                                  | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                          |                                  | 30                 | -      | 70                 | %    |

| ΙL                                         | OSC32_IN Input leakage current                      | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 36. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

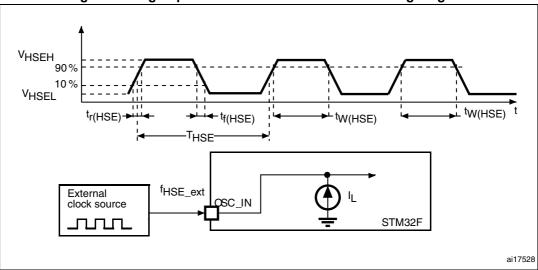

Figure 22. High-speed external clock source AC timing diagram

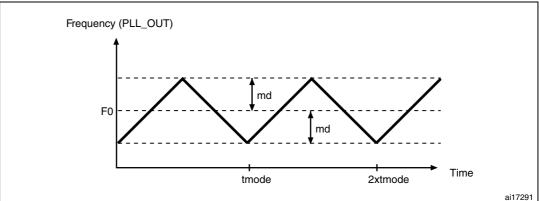

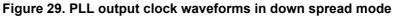

*Figure 28* and *Figure 29* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is  $f_{PLL_OUT}$  nominal.

$T_{mode}$  is the modulation period.

md is the modulation depth.

#### 6.3.12 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Table 44. | Flash   | memory        | characteristics |

|-----------|---------|---------------|-----------------|

|           | 1 14311 | III CIII CI Y | onuluotonotioo  |

| Symbol          | Parameter | Conditions                                         | Min | Тур | Мах | Unit |

|-----------------|-----------|----------------------------------------------------|-----|-----|-----|------|

|                 |           | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V         | -   | 5   | -   |      |

| I <sub>DD</sub> |           | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V        | -   | 8   | -   | mA   |

|                 |           | Write / Erase 32-bit mode, V <sub>DD</sub> = 3.3 V | -   | 12  | -   |      |

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |

|                         | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |

| t <sub>ERASE128KB</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | S    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 8    | 16                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 5.5  | 11                 | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 4    | 8                  |      |

|                         |                            | 32-bit program operation                         | 2.7                | -    | 3.6                | V    |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation                         | 2.1                | -    | 3.6                | V    |

|                         |                            | 8-bit program operation                          | 1.7                | -    | 3.6                | V    |

Table 45. Flash memory programming

1. Guaranteed by characterization, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

| Symbol                  | Parameter                  | Conditions                   | Min <sup>(1)</sup> | Тур   | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|------------------------------|--------------------|-------|--------------------|------|

| t <sub>prog</sub>       | Double word programming    |                              | -                  | 16    | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | T <sub>A</sub> = 0 to +40 °C | -                  | 230   | -                  |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | V <sub>DD</sub> = 3.3 V      | -                  | 490   | -                  | ms   |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | V <sub>PP</sub> = 8.5 V      | -                  | 875   | -                  |      |

| t <sub>ME</sub>         | Mass erase time            |                              | -                  | 1.750 | -                  | s    |

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol | Parameter                 | Conditions                                                                  | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ]<br>8/84 MHz | Unit |

|--------|---------------------------|-----------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------|------|

|        | <sub>EMI</sub> Peak level | ak level $V_{DD}$ = 3.6 V, T <sub>A</sub> = 25 °C, conforming to IEC61967-2 | 0.1 to 30 MHz               | -4                                                           |      |

| 6      |                           |                                                                             | 30 to 130 MHz               | -4                                                           | dBµV |

| SEMI   |                           |                                                                             | 130 MHz to 1 GHz            | -2                                                           |      |

|        |                           |                                                                             | SAE EMI Level               | 1.5                                                          | -    |

#### Table 49. EMI characteristics for WLCSP49

#### Table 50. EMI characteristics for LQFP100

| Symbol           | Parameter   | Conditions                                              | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ]<br>8/84 MHz | Unit |

|------------------|-------------|---------------------------------------------------------|-----------------------------|--------------------------------------------------------------|------|

|                  |             |                                                         | 0.1 to 30 MHz               | 19                                                           |      |

| 6                | Deels level | $V_{DD}$ = 3.6 V, T <sub>A</sub> = 25 °C, conforming to | 30 to 130 MHz               | 19                                                           | dBµV |

| S <sub>EMI</sub> | Peak level  | IEC61967-2                                              | 130 MHz to 1 GHz            | 11                                                           |      |

|                  |             |                                                         | SAE EMI Level               | 3.5                                                          | -    |

### 6.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

|                  |                                                                                                                                                                       | Functional s       |                    |      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                                                                                           | Negative injection | Positive injection | Unit |

| I <sub>INJ</sub> | Injected current on BOOT0 pin                                                                                                                                         | -0                 | NA                 |      |

|                  | Injected current on NRST pin                                                                                                                                          | -0                 | NA                 |      |

|                  | Injected current on PB3, PB4, PB5, PB6,<br>PB7, PB8, PB9, PC13, PC14, PC15, PH1,<br>PDR_ON, PC0, PC1,PC2, PC3, PD1,<br>PD5, PD6, PD7, PE0, PE2, PE3, PE4,<br>PE5, PE6 | -0                 | NA                 | mA   |

|                  | Injected current on any other FT pin                                                                                                                                  | -5                 | NA                 |      |

|                  | Injected current on any other pins                                                                                                                                    | -5                 | +5                 |      |

| Table 53. I/O current in | jection susce | ptibility <sup>(1)</sup> |

|--------------------------|---------------|--------------------------|

|--------------------------|---------------|--------------------------|

1. NA = not applicable.

*Note:* It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

### 6.3.16 I/O port characteristics

#### General input/output characteristics

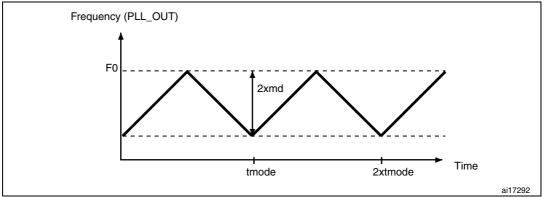

Unless otherwise specified, the parameters given in *Table 54* are derived from tests performed under the conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol          | Parameter                                                                                | Conditions                                                                                                                                                                        | Min                                     | Тур | Мах                                      | Unit |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|------------------------------------------|------|--|--|--|--|

| V <sub>IL</sub> | FT, and NRST I/O input low                                                               | 17//// 28//                                                                                                                                                                       |                                         |     | 0.35V <sub>DD</sub> -0.04 <sup>(1)</sup> |      |  |  |  |  |

|                 | level voltage                                                                            | 1.7 V≤ V <sub>DD</sub> ≤ 3.6 V                                                                                                                                                    | -                                       | -   | 0.3V <sub>DD</sub> <sup>(2)</sup>        |      |  |  |  |  |

|                 | BOOT0 I/O input low level voltage                                                        | $1.75 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V},$<br>-40 °C $\le \text{T}_{A} \le 105 \text{ °C}$                                                                             | -                                       | -   |                                          | V    |  |  |  |  |

|                 |                                                                                          | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V},$<br>0 °C ≤ T <sub>A</sub> ≤ 105 °C                                                                                     | -                                       | -   | 0.1V <sub>DD</sub> +0.1                  |      |  |  |  |  |

|                 | FT and NRST I/O input high<br>level voltage <sup>(5)</sup><br>BOOT0 I/O input high level | $\begin{array}{c} 1.7 \ V {\leq} \ V_{DD} {\leq} \ 3.6 \ V \\ \\ 1.75 \ V {\leq} \ V_{DD} {\leq} \ 3.6 \ V, \\ -40 \ ^{\circ}C {\leq} \ T_A {\leq} \ 105 \ ^{\circ}C \end{array}$ | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup> | -   | -                                        |      |  |  |  |  |

|                 |                                                                                          |                                                                                                                                                                                   | 0.4V <sub>DD</sub> <sup>(2)</sup>       |     |                                          |      |  |  |  |  |

| V <sub>IH</sub> |                                                                                          |                                                                                                                                                                                   | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup> | _   | _                                        | V    |  |  |  |  |

|                 | voltage                                                                                  | $1.7 V \le V_{DD} \le 3.6 V$ ,<br>0 °C $\le T_A \le 105 °C$                                                                                                                       | 0.17 0.7                                | _   |                                          |      |  |  |  |  |

| Table | 54  | 1/0 | static  | characteristics |

|-------|-----|-----|---------|-----------------|

| lable | 54. | 1/0 | ้อเลเเบ | characteristics |

#### Figure 30. FT I/O input characteristics

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 12*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 12*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 55* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

#### STM32F401xD STM32F401xE

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                                      | Parameter                                                                                 | Conditions                                       | Min | Тур | Мах                | Unit |

|-----------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------|-----|-----|--------------------|------|

|                                               |                                                             |                                                                                           | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 25                 |      |

|                                               | f                                                           | Maximum frequency <sup>(3)</sup>                                                          | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 12.5               | MHz  |

|                                               | <sup>I</sup> max(IO)out                                     |                                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 50                 |      |

| 01                                            |                                                             |                                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 20                 |      |

| 01                                            |                                                             |                                                                                           | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥2.7 V   | -   | -   | 10                 |      |

|                                               | t <sub>f(IO)out</sub> /                                     | Output high to low level fall time and output low to high                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 20                 | ne   |

|                                               | t <sub>r(IO)out</sub>                                       | level rise time                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 6                  | ns   |

|                                               |                                                             |                                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 10                 |      |

|                                               |                                                             |                                                                                           | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 50 <sup>(4)</sup>  |      |

|                                               | f <sub>max(IO)out</sub>                                     | Maximum frequency <sup>(3)</sup>                                                          | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 25                 | MHz  |

|                                               |                                                             |                                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 100 <sup>(4)</sup> |      |

| 10                                            |                                                             |                                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 50 <sup>(4)</sup>  |      |

| 10                                            | <sup>t</sup> f(IO)out <sup>/</sup><br><sup>t</sup> r(IO)out | $t_{f(IO)out}'$ Output high to low level fall time and output low to high level rise time | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 6                  | ns   |

|                                               |                                                             |                                                                                           | C <sub>L</sub> = 40 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 10                 |      |

|                                               |                                                             |                                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.70 V | -   | -   | 4                  |      |

|                                               |                                                             |                                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V  | -   | -   | 6                  |      |