Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M4                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 84MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SDIO, SPI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 50                                                                      |

| Program Memory Size        | 384KB (384K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 96K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f401rdt6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.  | Device summary                                                                                | . 1 |

|-----------|-----------------------------------------------------------------------------------------------|-----|

| Table 2.  | STM32F401xD/xE features and peripheral counts                                                 | 11  |

| Table 3.  | Regulator ON/OFF and internal power supply supervisor availability.                           |     |

| Table 4.  | Timer feature comparison                                                                      |     |

| Table 5.  | Comparison of I2C analog and digital filters                                                  | 29  |

| Table 6.  | USART feature comparison                                                                      |     |

| Table 7.  | Legend/abbreviations used in the pinout table                                                 | 38  |

| Table 8.  | STM32F401xD/xE pin definitions                                                                | 38  |

| Table 9.  | Alternate function mapping                                                                    | 45  |

| Table 10. | STM32F401xD register boundary addresses                                                       | 52  |

| Table 11. | Voltage characteristics                                                                       | 58  |

| Table 12. | Current characteristics                                                                       | 59  |

| Table 13. | Thermal characteristics.                                                                      | 59  |

| Table 14. | General operating conditions                                                                  | 60  |

| Table 15. | Features depending on the operating power supply range                                        | 61  |

| Table 16. | VCAP1/VCAP2 operating conditions                                                              |     |

| Table 17. | Operating conditions at power-up / power-down (regulator ON)                                  | 63  |

| Table 18. | Operating conditions at power-up / power-down (regulator OFF).                                |     |

| Table 19. | Embedded reset and power control block characteristics.                                       | 64  |

| Table 20. | Typical and maximum current consumption, code with data processing (ART                       |     |

|           | accelerator disabled) running from SRAM - V <sub>DD</sub> = 1.7 V                             | 66  |

| Table 21. | Typical and maximum current consumption, code with data processing (ART                       |     |

|           | accelerator disabled) running from SRAM                                                       | 66  |

| Table 22. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator enabled except prefetch) running from Flash memory- V <sub>DD</sub> = 1.7 V  | 67  |

| Table 23. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator enabled except prefetch) running from Flash memory - V <sub>DD</sub> = 3.3 V | 67  |

| Table 24. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator disabled) running from Flash memory                                          | 68  |

| Table 25. | Typical and maximum current consumption in run mode, code with data processing                |     |

|           | (ART accelerator enabled with prefetch) running from Flash memory                             | 68  |

| Table 26. | Typical and maximum current consumption in Sleep mode                                         | 69  |

| Table 27. | Typical and maximum current consumptions in Stop mode - V <sub>DD</sub> =1.8 V                | 69  |

| Table 28. | Typical and maximum current consumption in Stop mode - V <sub>DD</sub> =3.3 V                 | 70  |

| Table 29. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> =1.8 V              | 70  |

| Table 30. | Typical and maximum current consumption in Standby mode - V <sub>DD</sub> =3.3 V              | 70  |

| Table 31. | Typical and maximum current consumptions in V <sub>BAT</sub> mode                             | 71  |

| Table 32. | Switching output I/O current consumption                                                      | 73  |

| Table 33. | Peripheral current consumption                                                                | 74  |

| Table 34. | Peripheral current consumption<br>Low-power mode wakeup timings <sup>(1)</sup>                | 75  |

| Table 35. | High-speed external user clock characteristics.                                               | 76  |

| Table 36. | Low-speed external user clock characteristics                                                 |     |

| Table 37. | HSE 4-26 MHz oscillator characteristics.                                                      | 78  |

| Table 38. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                                | 79  |

| Table 39. | HSI oscillator characteristics                                                                | 80  |

| Table 40. | LSI oscillator characteristics                                                                | 81  |

| Table 41. | Main PLL characteristics.                                                                     |     |

| Table 42. | PLLI2S (audio PLL) characteristics                                                            | 83  |

# 3 Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU core with embedded Flash and SRAM

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices. The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution. Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F401xD/xE devices are compatible with all ARM tools and software.

Figure 3 shows the general block diagram of the STM32F401xD/xE.

Note: Cortex<sup>®</sup>-M4 with FPU is binary compatible with Cortex<sup>®</sup>-M3.

### 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 105 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 84 MHz.

### 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

DocID025644 Rev 3

### 3.14 Power supply supervisor

### 3.14.1 Internal reset ON

This feature is available for  $V_{DD}$  operating voltage range 1.8 V to 3.6 V.

The internal power supply supervisor is enabled by holding PDR\_ON high.

The device has an integrated power-on reset (POR) / power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR is always active, and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently. Three BOR thresholds are available through option bytes.

The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

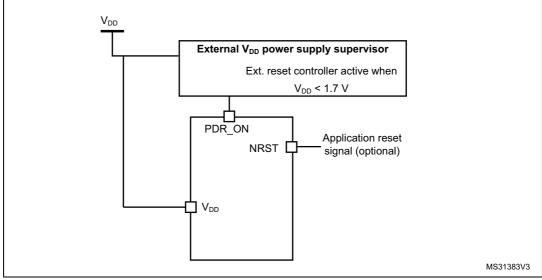

### 3.14.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled by setting the PDR\_ON pin to low.

An external power supply supervisor should monitor  $V_{DD}$  and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to this external power supply supervisor. Refer to *Figure 5: Power supply supervisor interconnection with internal reset OFF*.

Figure 5. Power supply supervisor interconnection with internal reset OFF<sup>(1)</sup>

1. The PRD\_ON pin is only available in the WLCSP49 and UFBGA100 packages.

The RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or from the  $V_{BAT}$  pin.

### 3.17 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

### • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm/ wakeup/ tamper/ time stamp events).

### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm/ wakeup/ tamper/time stamp event occurs.

Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

## 3.18 V<sub>BAT</sub> operation

The VBAT pin allows to power the device  $V_{BAT}$  domain from an external battery, an external super-capacitor, or from  $V_{DD}$  when no external battery and an external super-capacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC and the backup registers.

Note: When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation. When PDR\_ON pin is not connected to  $V_{DD}$  (internal Reset OFF), the  $V_{BAT}$  functionality is no more available and VBAT pin should be connected to  $V_{DD}$ .

If configured as standard 16-bit timers, it has the same features as the general-purpose TIMx timers. If configured as a 16-bit PWM generator, it has full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 supports independent DMA request generation.

### 3.19.2 General-purpose timers (TIMx)

There are seven synchronizable general-purpose timers embedded in the STM32F401xD/xE (see *Table 4* for differences).

### • TIM2, TIM3, TIM4, TIM5

The STM32F401xD/xE devices are 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature four independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 15 input capture/output compare/PWMs.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

### • TIM9, TIM10 and TIM11

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

### 3.19.3 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

### 3.19.4 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

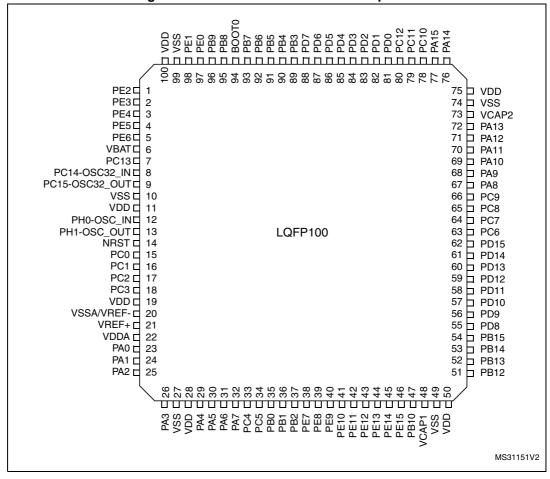

Figure 13. STM32F401xD/xE LQFP100 pinout

1. The above figure shows the package top view.

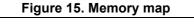

# 5 Memory mapping

The memory map is shown in *Figure 15*.

DocID025644 Rev 3

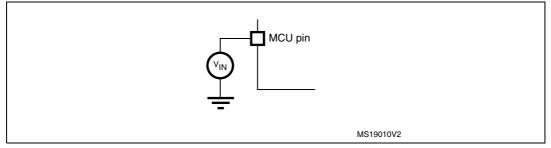

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 17*.

### Figure 17. Input voltage measurement

# 6.3 Operating conditions

# 6.3.1 General operating conditions

| Table 14 | General | operating | conditions |

|----------|---------|-----------|------------|

|----------|---------|-----------|------------|

| Symbol                     | Parameter                                                                                                      | Conditions                                                             | Min                 | Тур  | Max                 | Unit |

|----------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|------|---------------------|------|

| £                          |                                                                                                                | Power Scale3: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x01 | 0                   | -    | 60                  |      |

| f <sub>HCLK</sub>          | Internal AHB clock frequency                                                                                   | Power Scale2: Regulator ON,<br>VOS[1:0] bits in PWR_CR register = 0x10 | 0                   | -    | 84                  | MHz  |

| f <sub>PCLK1</sub>         | Internal APB1 clock frequency                                                                                  |                                                                        | 0                   | -    | 42                  |      |

| f <sub>PCLK2</sub>         | Internal APB2 clock frequency                                                                                  |                                                                        | 0                   | -    | 84                  |      |

| $V_{DD}$                   | Standard operating voltage                                                                                     |                                                                        | 1.7 <sup>(1)</sup>  | -    | 3.6                 |      |

| V <sub>DDA</sub><br>(2)(3) | Analog operating voltage<br>(ADC limited to 1.2 M samples)                                                     | Must be the same potential as $V_{DD}^{(4)}$                           | 1.7 <sup>(1)</sup>  | -    | 2.4                 |      |

| (2)(3)                     | Analog operating voltage<br>(ADC limited to 2.4 M samples)                                                     |                                                                        | 2.4                 | -    | 3.6                 |      |

| V <sub>BAT</sub>           | Backup operating voltage                                                                                       |                                                                        | 1.65                | -    | 3.6                 |      |

|                            | Regulator ON: 1.2 V internal voltage on V <sub>CAP_1</sub> /V <sub>CAP_2</sub> pins                            | VOS[1:0] bits in PWR_CR register = 0x01<br>Max frequency 60 MHz        | 1.08 <sup>(5)</sup> | 1.14 | 1.20 <sup>(5)</sup> | V    |

| V <sub>12</sub>            |                                                                                                                | VOS[1:0] bits in PWR_CR register = 0x10<br>Max frequency 84 MHz        | 1.20 <sup>(5)</sup> | 1.26 | 1.32 <sup>(5)</sup> |      |

|                            | Regulator OFF: 1.2 V external                                                                                  | Max. frequency 60 MHz.                                                 | 1.1                 | 1.14 | 1.2                 |      |

| V <sub>12</sub>            | voltage must be supplied on $V_{CAP_1}/V_{CAP_2}$ pins                                                         | Max. frequency 84 MHz.                                                 | 1.2                 | 1.26 | 1.32                |      |

|                            | Input voltage on RST and FT                                                                                    | $2 \text{ V} \leq \text{ V}_{DD} \leq 3.6 \text{ V}$                   | -0.3                | -    | 5.5                 |      |

| $V_{IN}$                   | pins <sup>(6)</sup>                                                                                            | $V_{DD} \leq 2 V$                                                      | -0.3                | -    | 5.2                 |      |

|                            | Input voltage on BOOT0 pin                                                                                     |                                                                        | 0                   | -    | 9                   |      |

|                            |                                                                                                                | UFQFPN48                                                               | -                   | -    | 625                 |      |

|                            |                                                                                                                | WLCSP49                                                                | -                   | -    | 392                 | mW   |

| PD                         | Maximum allowed package power dissipation for suffix 7 <sup>(7)</sup>                                          | LQFP64                                                                 | -                   | -    | 313                 |      |

|                            | The second s | LQFP100                                                                | -                   | -    | 465                 |      |

|                            |                                                                                                                | UFBGA100                                                               | -                   | -    | 323                 | ]    |

| Symbol          |                                                        | Conditions                                 | £                          | Тур                       |                        |                       |                        |      |

|-----------------|--------------------------------------------------------|--------------------------------------------|----------------------------|---------------------------|------------------------|-----------------------|------------------------|------|

|                 | Parameter                                              |                                            | f <sub>HCLK</sub><br>(MHz) | Т <sub>А</sub> =<br>25 °С | T <sub>A</sub> = 25 °C | T <sub>A</sub> =85 °C | T <sub>A</sub> =105 °C | Unit |

|                 |                                                        |                                            | 84                         | 21.8                      | 23.1                   | 24.1                  | 25.3 <sup>(4)</sup>    |      |

|                 | ai<br>Supply current<br>in <b>Run mode</b><br>E:<br>ai | External clock,<br>all peripherals         | 60                         | 15.8                      | 16.5                   | 17.5                  | 18.7                   |      |

|                 |                                                        | enabled <sup>(2)(3)</sup>                  | 40                         | 11.4                      | 11.9                   | 12.9                  | 13.9                   |      |

|                 |                                                        |                                            | 20                         | 6.0                       | 6.3                    | 7.3                   | 8.3                    | mA   |

| I <sub>DD</sub> |                                                        |                                            | 84                         | 12.7                      | 13.5                   | 14.5                  | 16.3 <sup>(4)</sup>    | ША   |

|                 |                                                        | External clock,                            | 60                         | 9.2                       | 10.5                   | 11.5                  | 12.8                   |      |

|                 |                                                        | all peripherals<br>disabled <sup>(3)</sup> | 40                         | 6.7                       | 7.1                    | 8.1                   | 9.1                    |      |

|                 |                                                        | disabled                                   | 20                         | 3.6                       | 3.8                    | 4.8                   | 5.8                    |      |

Table 20. Typical and maximum current consumption, code with data processing (ARTaccelerator disabled) running from SRAM - V<sub>DD</sub> = 1.7 V

1. Guaranteed by characterization, not tested in production unless otherwise specified

2. When analog peripheral blocks such as ADC, HSE, LSE, HSI, or LSI are ON, an additional power consumption has to be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

4. Tested in production.

# Table 21. Typical and maximum current consumption, code with data processing (ARTaccelerator disabled) running from SRAM

| Symbol          | Deremeter          | Parameter Conditions                                                                | f <sub>HCLK</sub> | True |                        | Unit                  |                        |      |

|-----------------|--------------------|-------------------------------------------------------------------------------------|-------------------|------|------------------------|-----------------------|------------------------|------|

| Symbol          | Parameter          |                                                                                     | (MHz)             | Тур  | T <sub>A</sub> = 25 °C | T <sub>A</sub> =85 °C | T <sub>A</sub> =105 °C | Unit |

|                 |                    |                                                                                     | 84                | 22.0 | 23.1                   | 24.1                  | 25.3                   |      |

|                 |                    | External clock,<br>all peripherals<br>enabled <sup>(2)(3)</sup>                     | 60                | 16.0 | 16.9                   | 17.9                  | 19.8                   |      |

|                 |                    |                                                                                     | 40                | 11.6 | 12.1                   | 13.1                  | 14.1                   |      |

|                 | Supply current     |                                                                                     |                   | 20   | 6.2                    | 6.5                   | 7.5                    | 8.5  |

| I <sub>DD</sub> | in <b>Run mode</b> | in <b>Run mode</b><br>External clock,<br>all peripherals<br>disabled <sup>(3)</sup> | 84                | 12.9 | 14.0                   | 15.0                  | 16.3                   | ША   |

|                 |                    |                                                                                     | 60                | 9.5  | 10.5                   | 11.5                  | 12.8                   |      |

|                 |                    |                                                                                     | 40                | 6.9  | 7.3                    | 8.3                   | 9.3                    |      |

|                 |                    |                                                                                     | 20                | 3.8  | 4.0                    | 5.0                   | 6.0                    |      |

1. Guaranteed by characterization, not tested in production unless otherwise specified

2. When analog peripheral blocks such as ADC, HSE, LSE, HSI, or LSI are ON, an additional power consumption has to be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

| Symbol          |                      |                                                               |                            |      |                           |                           |                            |      |  |  |  |  |  |    |     |     |     |      |      |  |

|-----------------|----------------------|---------------------------------------------------------------|----------------------------|------|---------------------------|---------------------------|----------------------------|------|--|--|--|--|--|----|-----|-----|-----|------|------|--|

|                 | Parameter            | Conditions                                                    | f <sub>HCLK</sub><br>(MHz) | Тур  | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |  |  |  |  |    |     |     |     |      |      |  |

|                 |                      |                                                               | 84                         | 16.6 | 17.4                      | 18.4                      | 19.5                       |      |  |  |  |  |  |    |     |     |     |      |      |  |

|                 |                      |                                                               | 60                         | 10.8 | 11.2                      | 12.3                      | 13.3                       |      |  |  |  |  |  |    |     |     |     |      |      |  |

|                 |                      | External clock,<br>all peripherals enabled <sup>(2)(3)</sup>  |                            |      |                           |                           |                            |      |  |  |  |  |  |    | 40  | 8.3 | 9.0 | 10.0 | 11.0 |  |

|                 |                      |                                                               |                            |      |                           |                           |                            |      |  |  |  |  |  | 30 | 6.8 | 7.1 | 8.1 | 9.1  |      |  |

|                 | Supply current       |                                                               | 20                         | 5.9  | 6.1                       | 7.1                       | 8.1                        | mA   |  |  |  |  |  |    |     |     |     |      |      |  |

| I <sub>DD</sub> | in <b>Sleep</b> mode |                                                               | 84                         | 5.3  | 6.1                       | 7.1                       | 8.2                        | ШA   |  |  |  |  |  |    |     |     |     |      |      |  |

|                 |                      |                                                               |                            | 60   | 3.7                       | 4.1                       | 5.1                        | 6.1  |  |  |  |  |  |    |     |     |     |      |      |  |

|                 |                      | External clock,<br>all peripherals disabled <sup>(3)(4)</sup> | 40                         | 2.9  | 3.1                       | 4.1                       | 5.1                        |      |  |  |  |  |  |    |     |     |     |      |      |  |

|                 |                      |                                                               | 30                         | 2.7  | 3.1                       | 4.1                       | 5.1                        |      |  |  |  |  |  |    |     |     |     |      |      |  |

|                 |                      |                                                               | 20                         | 2.7  | 3.1                       | 4.1                       | 5.1                        |      |  |  |  |  |  |    |     |     |     |      |      |  |

1. Guaranteed by characterization, not tested in production unless otherwise specified.

2. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA for the analog part.

4. Same current consumption for  $f_{\mbox{HCLK}}$  at 30 MHz and 20 MHz due to VCO running slower at 30 MHz.

| Symbol               |                                       |                                                                          | Тур | Max <sup>(1)</sup>        |                           |                            |      |

|----------------------|---------------------------------------|--------------------------------------------------------------------------|-----|---------------------------|---------------------------|----------------------------|------|

|                      | Parameter                             | er Conditions                                                            |     | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      | Main regulator usage                  | Flash in Stop mode, all                                                  | 109 | 135                       | 440                       | 650                        |      |

|                      | Low power regulator usage             | oscillators OFF, no<br>independent watchdog                              | 41  | 65                        | 310                       | 530 <sup>(2)</sup>         |      |

| I <sub>DD_STOP</sub> | Main regulator usage                  | Flash in Deep power<br>down mode, all oscillators<br>OFF, no independent | 72  | 95                        | 345                       | 530                        | μA   |

|                      | Low power regulator usage             |                                                                          | 12  | 36                        | 260                       | 510 <sup>(2)</sup>         |      |

|                      | Low power low voltage regulator usage | watchdog                                                                 | 10  | 27                        | 230                       | 460                        |      |

### Table 27. Typical and maximum current consumptions in Stop mode - $V_{DD}$ =1.8 V

1. Guaranteed by characterization, not tested in production.

2. Guaranteed by test in production.

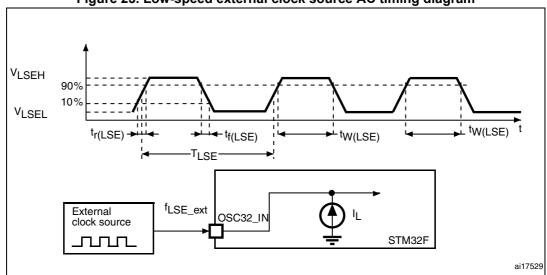

Figure 23. Low-speed external clock source AC timing diagram

### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 37*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                                                             | Min | Тур | Max | Unit |

|-------------------------------------|-----------------------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                    |                                                                        | 4   | -   | 26  | MHz  |

| R <sub>F</sub>                      | Feedback resistor                       |                                                                        | -   | 200 | -   | kΩ   |

| 1                                   | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF @25 MHz  | -   | 450 | -   |      |

| I <sub>DD</sub>                     | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF @25 MHz | -   | 530 | -   | μΑ   |

| G <sub>m_crit_max</sub>             | Maximum critical crystal g <sub>m</sub> | Startup                                                                | -   | -   | 1   | mA/V |

| t <sub>SU(HSE)</sub> <sup>(2)</sup> | Startup time                            | $V_{DD}$ is stabilized                                                 | -   | 2   | -   | ms   |

| Table 37. HSE 4-26 MHz oscillator characteristics <sup>(1)</sup> | ) |

|------------------------------------------------------------------|---|

|------------------------------------------------------------------|---|

1. Guaranteed by design, not tested in production.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 24*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the

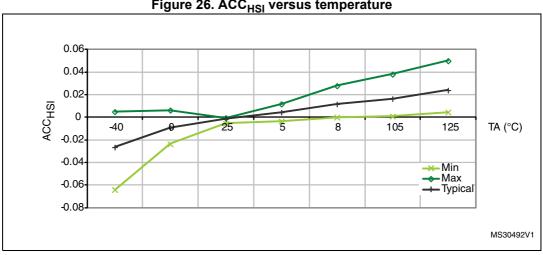

Figure 26. ACC<sub>HSI</sub> versus temperature

1. Guaranteed by characterization, not tested in production.

### Low-speed internal (LSI) RC oscillator

| Table 40. | LSI oscillator | characteristics | (1) |

|-----------|----------------|-----------------|-----|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V, T<sub>A</sub> = -40 to 105 °C unless otherwise specified.

2. Guaranteed by characterization, not tested in production.

3. Guaranteed by design, not tested in production.

| Symbol                               | Parameter                     | Conditions                               | Min          | Тур | Max          | Unit |

|--------------------------------------|-------------------------------|------------------------------------------|--------------|-----|--------------|------|

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD  | VCO freq = 192 MHz<br>VCO freq = 432 MHz | 0.15<br>0.45 | -   | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA | VCO freq = 192 MHz<br>VCO freq = 432 MHz | 0.30<br>0.55 | -   | 0.40<br>0.85 |      |

### Table 41. Main PLL characteristics (continued)

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design, not tested in production.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization, not tested in production.

| Symbol                                  | Parameter                             | Conditions                                                              | Conditions                               |              | Тур  | Мах          | Unit |

|-----------------------------------------|---------------------------------------|-------------------------------------------------------------------------|------------------------------------------|--------------|------|--------------|------|

| f <sub>PLLI2S_IN</sub>                  | PLLI2S input clock <sup>(1)</sup>     |                                                                         |                                          |              | 1    | 2.10         |      |

| f <sub>PLLI2S_OUT</sub>                 | PLLI2S multiplier output clock        |                                                                         |                                          | -            | -    | 216          | MHz  |

| f <sub>VCO_OUT</sub>                    | PLLI2S VCO output                     |                                                                         |                                          | 192          | -    | 432          |      |

| +                                       | PLLI2S lock time                      | VCO freq = 192 MHz                                                      | 2                                        | 75           | -    | 200          |      |

| t <sub>LOCK</sub>                       |                                       | VCO freq = 432 MHz                                                      |                                          | 100          | -    | 300          | μs   |

| Jitter <sup>(3)</sup>                   |                                       | Cycle to cycle at                                                       | RMS                                      | -            | 90   | -            |      |

|                                         | Master I2S clock jitter               | 12.288 MHz on<br>48 KHz period,<br>N=432, R=5                           | peak<br>to<br>peak                       | -            | ±280 | -            |      |

|                                         |                                       | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples |                                          | -            | 90   | -            | ps   |

| WS I2S CIOCK litter                     |                                       | Cycle to cycle at 48 on 1000 samples                                    | KHz                                      | -            | 400  | -            |      |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$  | VCO freq = 192 MHz<br>VCO freq = 432 MHz                                |                                          | 0.15<br>0.45 | -    | 0.40<br>0.75 | m 4  |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{DDA}$ |                                                                         | VCO freq = 192 MHz<br>VCO freq = 432 MHz |              | -    | 0.40<br>0.85 | mA   |

### Table 42. PLLI2S (audio PLL) characteristics

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design, not tested in production.

3. Value given with main PLL running.

4. Guaranteed by characterization, not tested in production.

| Symbol                  | Parameter                                                             | Conditions                                  | Min <sup>(1)</sup> | Тур       | Max <sup>(1)</sup> | Unit |

|-------------------------|-----------------------------------------------------------------------|---------------------------------------------|--------------------|-----------|--------------------|------|

| t <sub>prog</sub>       | Word programming timeProgram/erase parallelism<br>(PSIZE) = x 8/16/32 |                                             | -                  | 16        | 100 <sup>(2)</sup> | μs   |

|                         |                                                                       | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 400       | 800                | ms   |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time                                             | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 300       | 600                |      |

|                         |                                                                       | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 250       | 500                |      |

|                         |                                                                       | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 1200      | 2400               | ms   |

| t <sub>erase64kb</sub>  | Sector (64 KB) erase time                                             | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 700       | 1400               |      |

|                         |                                                                       | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 550       | 1100               |      |

|                         |                                                                       | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 2 4       |                    |      |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time                                            | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | - 1.3 2.6 | 2.6                | S    |

|                         |                                                                       | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 1         | 2                  |      |

|                         |                                                                       | Program/erase parallelism<br>(PSIZE) = x 8  | - 8 16             |           |                    |      |

| t <sub>ME</sub>         | Mass erase time                                                       | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 5.5       | 11                 | s    |

|                         |                                                                       | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 4         | 8                  |      |

|                         |                                                                       | 32-bit program operation                    | 2.7                | -         | 3.6                | V    |

| V <sub>prog</sub>       | Programming voltage                                                   | 16-bit program operation                    | 2.1                | -         | 3.6                | V    |

|                         |                                                                       | 8-bit program operation                     | 1.7 - 3.6          |           | 3.6                | V    |

Table 45. Flash memory programming

1. Guaranteed by characterization, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

| Symbol                  | Parameter                  | Conditions                   | Min <sup>(1)</sup> | Тур   | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|------------------------------|--------------------|-------|--------------------|------|

| t <sub>prog</sub>       | Double word programming    |                              | -                  | 16    | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | T <sub>A</sub> = 0 to +40 °C | -                  | 230   | -                  |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | V <sub>DD</sub> = 3.3 V      | -                  | 490   | -                  | ms   |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | V <sub>PP</sub> = 8.5 V      | -                  | 875   | -                  |      |

| t <sub>ME</sub>         | Mass erase time            |                              | -                  | 1.750 | -                  | s    |

| -                 |                                                                                                                                   |                                                                                                                                                          |                 |  |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                               | Level/<br>Class |  |  |  |  |  |  |

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, WLCSP49,<br>T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> = 84 MHz,<br>conforms to IEC 61000-4-2                                 | 2B              |  |  |  |  |  |  |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, \text{LQFP100}, \text{WLCSP49}, T_A = +25 ^{\circ}\text{C}, f_{\text{HCLK}} = 84 \text{ MHz}, \text{conforms to IEC 61000-4-4}$ | 4A              |  |  |  |  |  |  |

Table 48. EMS characteristics for LQFP100 package

When the application is exposed to a noisy environment, it is recommended to avoid pin exposition to disturbances. The pins showing a middle range robustness are: PA0, PA1, PA2, on LQFP100 packages and PDR ON on WLCSP49.

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$  maximum) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

# 7 Package characteristics

# 7.1 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

| Symbol |       | millimeters |                | -      | inches <sup>(1)</sup> | -      |

|--------|-------|-------------|----------------|--------|-----------------------|--------|

| Symbol | Min.  | Тур.        | Typ. Max. Min. |        | Тур.                  | Max.   |

| Т      | -     | 0.152       | -              | -      | 0.0060                | -      |

| b      | 0.200 | 0.250       | 0.300          | 0.0079 | 0.0098                | 0.0118 |

| е      | -     | 0.500       | -              | -      | 0.0197                | -      |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

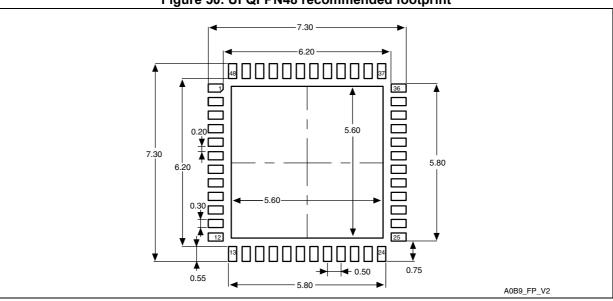

### Figure 50. UFQFPN48 recommended footprint

1. Dimensions are in millimeters.

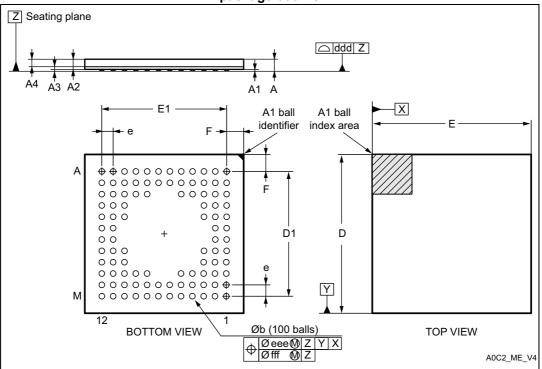

### 7.1.5 UFBGA100, 7 x 7 mm, 0.5 mm pitch package

Figure 58. UFBGA100, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 84. UFBGA100, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package |

|---------------------------------------------------------------------------------------|

| mechanical data                                                                       |

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |

| А      | 0.460 | 0.530       | 0.600 | 0.0181 | 0.0209                | 0.0236 |

| A1     | 0.050 | 0.080       | 0.110 | 0.0020 | 0.0031                | 0.0043 |

| A2     | 0.400 | 0.450       | 0.500 | 0.0157 | 0.0177                | 0.0197 |

| A3     | -     | 0.130       | -     | -      | 0.0051                | -      |

| A4     | 0.270 | 0.320       | 0.370 | 0.0106 | 0.0126                | 0.0146 |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098                | 0.0118 |

| D      | 6.950 | 7.000       | 7.050 | 0.2736 | 0.2756                | 0.2776 |

| D1     | 5.450 | 5.500       | 5.550 | 0.2146 | 0.2165                | 0.2185 |

| E      | 6.950 | 7.000       | 7.050 | 0.2736 | 0.2756                | 0.2776 |

| E1     | 5.450 | 5.500       | 5.550 | 0.2146 | 0.2165                | 0.2185 |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| F      | 0.700 | 0.750       | 0.800 | 0.0276 | 0.0295                | 0.0315 |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved

DocID025644 Rev 3